VIVADO FIFO (同步和异步) IP 核详细使用配置步骤

VIVADO FIFO (同步和异步) IP 核详细使用配置步骤

目录

前言

一、同步FIFO的使用

1、配置

2、仿真

二、异步FIFO的使用

1、配置

2、仿真

前言

在系统设计中,利用FIFO(first in first out)进行数据处理是再普遍不过的应用了,使用FIFO实现不同域时钟的数据同步,总线位宽调整,数据缓存等。本文以xilinx vivado中的FIFO IP 核为例,详细介绍其配置步骤,并给出详细的仿真,本文包含同步和异步(不同时钟)FIFO的详细使用步骤。

提示:以下是本篇文章正文内容,转载请附上原文链接

一、同步FIFO的使用

1、配置

在IP Catalog 界面搜索FIFO并双击FIFO Generator开始配置IP 核。对IP核命名,不妨取test_synchronous_fifo(同步FIFO的测试)。

首先,配置Basic界面:

Interface Type 保持默认即可,一般不选AXI接口。

FIFO Implementation 选用什么资源生成FIFO,这里选择 Common Clock Block RAM,即用块RAM资源生成一个同步FIFO。

该界面下面显示的是在选定方式生成的FIFO具有的特点。

然后,配置Native Ports界面:

Read Mode 默认选Standard FIFO,First FIFO Fall Through 会在没有读的时候就在读端口放置第一个数据,如手册中的下图所示,只要写入一个数据 D1 后,在rd_en为低电平的时候,dout就会变成D1且valid一直拉高。大家可以根据自己的需求选择对应的读模式。

Data Port Parameters 用来配置读写的深度和数据位宽,这里示例配置4bit宽度,16的深度。

!!!要留意一下配置的深度和实际的深度,手册中提及了选择不同实现方式(Basic 界面)实际深度与配置的深度是有差异的,实际深度才是可以使用的深度。

ECC,Output... 是IP核纠错,输出端加寄存器的功能,在配置时其实不用管,不用勾选任何东西。

Initialization 勾选复位,类型选择同步复位,Full Flags Reset Value 是复位时满标志的默认电平,Dout Reset Value 是复位时默认的读端口输出。

再然后,配置Status Flags界面:

Optional Flags中的Almost Full Flag是快要写满标志,即再写一个数据就满了的提示, Almost Empty Flag是快要读空标志,即再读一个数据就空了的提示。

Write Acknowledge 是写数据的标志,如果勾选高电平有效,则其拉高表示数据被写入。

Overflow 是溢出标志,如果满了,继续写数据是写不了的,溢出了。

valid Flag 读数据时输出数据有效的标志。

Underflow Flag 下溢标志,如果选择高电平有效,也就是读空了继续读该标志就会拉高。

Programmable Flags 是自定义一个数据写多少个就算满的标志信号和数据还剩多少个就算空的标志信号,可以在IP核界面配置固定的值,也可以引入两个输入端口由程序编程设置。需要用到该功能的可自行配置。

此处,按下图配置届时仿真可观察这些信号。

最后,配置Data Counts界面:

可以勾选Data Count,指示FIFO中还有多少个数据。由于此时是同步FIFO,所以只有一个Data Count。

至此,同步 FIFO 配置完成,下面进行仿真。

2、仿真

创建一个名为 tb_synchronous_fifo 的 testbench 文件,测试以上配置的FIFO。

`timescale 1ns / 1ps

//

// Company:

// Engineer:

//

// Create Date: 2025/01/15 11:36:36

// Design Name:

// Module Name: tb_synchronous_fifo

// Project Name:

// Target Devices:

// Tool Versions:

// Description:

//

// Dependencies:

//

// Revision:

// Revision 0.01 - File Created

// Additional Comments:

//

//module tb_synchronous_fifo();parameter PERIOD = 2;reg clk=1;

reg rst_n=0;

reg [3 : 0] din=0;

reg wr_en=0;

reg rd_en=0;wire [3 : 0] dout;

wire full;

wire almost_full;

wire wr_ack;

wire overflow;

wire empty;

wire almost_empty;

wire valid;

wire underflow;

wire [3 : 0] data_count;initial

beginforever #(PERIOD/2) clk=~clk;

endinitial

begin#(PERIOD*5) rst_n = 1;

endreg [4:0] cnt;

always @(posedge clk or negedge rst_n)

beginif(!rst_n)beginwr_en<=0;cnt<=0;endelse if(cnt<16)begincnt<=cnt+1;wr_en<=1;din<=din+1;endelsebeginwr_en<=0;end

endalways @(posedge clk or negedge rst_n)

beginif(!rst_n)beginrd_en<=0;endelse if(cnt==16)beginrd_en<=1;end

endtest_synchronous_fifo u_test_synchronous_fifo (.clk(clk), // input wire clk .srst(!rst_n), // input wire srst ip核本身是高电平复位.din(din), // input wire [3 : 0] din.wr_en(wr_en), // input wire wr_en.rd_en(rd_en), // input wire rd_en.dout(dout), // output wire [3 : 0] dout.full(full), // output wire full.almost_full(almost_full), // output wire almost_full.wr_ack(wr_ack), // output wire wr_ack.overflow(overflow), // output wire overflow.empty(empty), // output wire empty.almost_empty(almost_empty), // output wire almost_empty.valid(valid), // output wire valid.underflow(underflow), // output wire underflow.data_count(data_count) // output wire [3 : 0] data_count

);endmodule

从以上结果可以看出写入16个数据,读出16个数据,谁先写入就先被读出。大家可自行观察其他信号的变化是否和自己理解的一致。

上面配置FIFO的深度只有16,如果写入数据个数大于16,数据能写进去吗?答案是写不进去,并不是我们理解的满了再进就会将最开始进的挤出去。VIVADO FIFO IP就是这样这样设置的,没有办法改变,那么如果某些场景下需要这种满了再进就会将最开始进的挤出去的这种功能,光调用IP还无法实现。

例如,将上面代码中的 else if(cnt<16) 和 else if(cnt==16) 两句代码中的16改成20再仿真,结果如下,分析结果可以得出,满了继续写不会将最开始写的挤出去,而是直接忽视掉再写的数据。

二、异步FIFO的使用

1、配置

在IP Catalog 界面搜索FIFO并双击FIFO Generator开始配置IP 核。对IP核命名,不妨取test_asynchronous_fifo(异步FIFO的测试)。

首先,配置Basic界面:

Interface Type 保持默认即可,一般不选AXI接口。

FIFO Implementation 选用什么资源生成FIFO,这里选择 Independent Clocks Block RAM,即用块RAM资源生成一个异步FIFO。

相比于同步FIFO,多了synchronization Stages的配置,这个相当于写时钟域里面的数据经过多少个时钟周期同步到读时钟区域,可以理解成延时打拍同步。

该界面下面显示的是在选定方式生成的FIFO具有的特点。

然后,配置Native Ports界面:

Read Mode 同步FIFO配置有介绍,此处默认选Standard FIFO。

Data Port Parameters 用来配置读写的深度和数据位宽,这里示例配置4bit宽度,16的深度。

!!!要留意一下配置的深度和实际的深度,手册中提及了选择不同实现方式(Basic 界面)实际深度与配置的深度是有差异的,实际深度才是可以使用的深度。异步FIFO此时实际可使用的深度就比我们配置的少了一个。

ECC,Output... 是IP核自己纠错,输出端加寄存器的功能,在配置时其实不用管,不用勾选任何东西。

Initialization 勾选复位,Reset Type 固定了只能异步复位,是相对于整个IP而言。Full Flags Reset Value 是复位后满标志的默认电平,Dout Reset Value 是复位后默认的读端口输出。

相比于同步FIFO,多了Enable Reset Synchronization,该选项是读写时钟域分开来看时,在各自的时钟域里面使用同步复位。Enable Safety Circuit 手册说是一个保护电路,默认勾选即可,不用过多纠结。

Full Flags Reset Value 是复位时满标志默认电平,Dout Reset Value 是复位时默认读端口输出。

再然后,配置Status Flags界面:

同步FIFO配置界面已一 一说明。此处,按下图配置届时仿真可观察这些信号。

最后,配置Data Counts界面:

Data Count,指示FIFO中还有多少个数据。由于此时是异步FIFO,所以读写各有一个Data Count。

至此,异步 FIFO 配置完成,下面进行仿真。

2、仿真

创建一个名为 tb_asynchronous_fifo 的 testbench 文件,测试以上配置的异步FIFO。

`timescale 1ns / 1ps

//

// Company:

// Engineer:

//

// Create Date: 2025/01/15 12:20:08

// Design Name:

// Module Name: tb_asynchronous_fifo

// Project Name:

// Target Devices:

// Tool Versions:

// Description:

//

// Dependencies:

//

// Revision:

// Revision 0.01 - File Created

// Additional Comments:

//

//module tb_asynchronous_fifo();parameter PERIOD = 2;reg rst_n=0;

reg wr_clk=1;

reg rd_clk=1;

reg [3 : 0] din=0;

reg wr_en=0;

reg rd_en=0;wire [3 : 0] dout;

wire full;

wire almost_full;

wire wr_ack;

wire overflow;

wire empty;

wire almost_empty;

wire valid;

wire underflow;

wire [3 : 0] rd_data_count;

wire [3 : 0] wr_data_count;

wire wr_rst_busy;

wire rd_rst_busy;initial

beginforever #(PERIOD/2) wr_clk=~wr_clk;

endinitial

beginforever #(PERIOD) rd_clk=~rd_clk;

endinitial

begin#(PERIOD*5) rst_n = 1;

endreg flag=0;initial

begin#(PERIOD*28) flag = 1;#(PERIOD) flag = 0;

endreg [4:0] cnt;

always @(posedge wr_clk or negedge rst_n)

beginif(!rst_n)beginwr_en<=0;cnt<=0;endelse if(flag)begincnt<=cnt+1;wr_en<=1;din<=din+1;endelse if(1<=cnt&&cnt<16)begincnt<=cnt+1;wr_en<=1;din<=din+1;endelsebeginwr_en<=0;end

endalways @(posedge rd_clk or negedge rst_n)

beginif(!rst_n)beginrd_en<=0;endelse if(cnt==16)beginrd_en<=1;end

endtest_asynchronous_fifo u_test_asynchronous_fifo (.rst(!rst_n), // input wire rst.wr_clk(wr_clk), // input wire wr_clk.rd_clk(rd_clk), // input wire rd_clk.din(din), // input wire [3 : 0] din.wr_en(wr_en), // input wire wr_en.rd_en(rd_en), // input wire rd_en.dout(dout), // output wire [3 : 0] dout.full(full), // output wire full.almost_full(almost_full), // output wire almost_full.wr_ack(wr_ack), // output wire wr_ack.overflow(overflow), // output wire overflow.empty(empty), // output wire empty.almost_empty(almost_empty), // output wire almost_empty.valid(valid), // output wire valid.underflow(underflow), // output wire underflow.rd_data_count(rd_data_count), // output wire [3 : 0] rd_data_count.wr_data_count(wr_data_count), // output wire [3 : 0] wr_data_count.wr_rst_busy(wr_rst_busy), // output wire wr_rst_busy.rd_rst_busy(rd_rst_busy) // output wire rd_rst_busy

);endmodule

观察上面的仿真结果,第一,复位时满信号为1,与我们IP配置界面相吻合;第二,因为本身实际容量只有15个数据,我们写16个数据,溢出了一个,图中overflow拉高了一个电平,与同步FIFO一样,写满了就写不进去了;第三,图中两条黄色线之间相差4个读时钟周期,就是我们前面配置提到的延迟打拍保证时钟区域同步,那明明前面配置的是2,为什么这里为4呢?这是因为下图中的数字2造成的,2+2=4。

接下来将IP配置界面的同步拍数改为3,那么仿真图中两条黄色线之间则会有5个读时钟周期,以保证数据同步到读时钟域,如下面仿真图所示。

至此,本文结束。说明一下,如果自己想设置写到一定数量就有满标志提示,还剩多少个就有空标志提示,就需要去配置Status Flags界面的Programmable Flags。

相关文章:

VIVADO FIFO (同步和异步) IP 核详细使用配置步骤

VIVADO FIFO (同步和异步) IP 核详细使用配置步骤 目录 前言 一、同步FIFO的使用 1、配置 2、仿真 二、异步FIFO的使用 1、配置 2、仿真 前言 在系统设计中,利用FIFO(first in first out)进行数据处理是再普遍不过的应用了,…...

tcp粘包原理和解决

tcp粘包原理和解决 咱们先通过展示基于tcp 的cs端消息通信时的现象,带着问题再解释下面的tcp粘包问题。 一、原始代码 tcp 服务端代码 // socket_stick/server/main.gofunc process(conn net.Conn) {defer conn.Close()reader : bufio.NewReader(conn)var bu…...

C语言预处理艺术:编译前的魔法之旅

大家好,这里是小编的博客频道 小编的博客:就爱学编程 很高兴在CSDN这个大家庭与大家相识,希望能在这里与大家共同进步,共同收获更好的自己!!! 本文目录 引言正文一、预处理的作用与流程…...

C++算法第十六天

本篇文章我们继续学习动态规划 第一题 题目链接 978. 最长湍流子数组 - 力扣(LeetCode) 题目解析 从上图可见其实有三个状态 代码原理 注意:我们在分析题目的时候分析出来的是三个状态,分别是上升、下降、平坦,但是…...

计算机网络 (45)动态主机配置协议DHCP

前言 计算机网络中的动态主机配置协议(DHCP,Dynamic Host Configuration Protocol)是一种网络管理协议,主要用于自动分配IP地址和其他网络配置参数给连接到网络的设备。 一、基本概念 定义:DHCP是一种网络协议…...

归子莫的科技周刊#2:白天搬砖,夜里读诗

归子莫的科技周刊#2:白天搬砖,夜里读诗 本周刊开源,欢迎投稿。 刊期:2025.1.5 - 2025.1.11。原文地址。 封面图 下班在深圳看到的夕阳,能遇到是一种偶然的机会,能拍下更是一种幸运。 白天搬砖,…...

平滑算法 效果比较

目录 高斯平滑 效果对比 移动平均效果比较: 高斯平滑 效果对比 右边两个参数是1.5 2 代码: smooth_demo.py import numpy as np import cv2 from scipy.ndimage import gaussian_filter1ddef gaussian_smooth_array(arr, sigma):smoothed_arr = gaussian_filter1d(arr, s…...

Elasticsearch容器启动报错:AccessDeniedException[/usr/share/elasticsearch/data/nodes];

AccessDeniedException 表明 Elasticsearch 容器无法访问或写入数据目录 /usr/share/elasticsearch/data/nodes。这是一个权限问题。 问题原因: 1、宿主机目录权限不足:映射到容器的数据目录 /data/es/data 在宿主机上可能没有足够的权限供容器访问。 …...

【Linux系统编程】——深入理解 GCC/G++ 编译过程及常用选项详解

文章目录 1. GCC/G 编译过程预处理(Preprocessing)编译(Compilation)汇编(Assembly)连接(Linking) 静态链接与动态链接静态链接动态链接静态库和动态库 GCC 常用选项关于编译器的周边…...

Mac安装配置使用nginx的一系列问题

brew安装nginx https://juejin.cn/post/6986190222241464350 使用brew安装nginx,如下命令所示: brew install nginx 如下图所示: 2.查看nginx的配置信息,如下命令: brew info nginxFrom:xxx 这样的,是n…...

Vue3中使用组合式API通过路由传值详解

在Vue 3中,使用组合式API来传递路由参数是一种常见的需求。Vue Router 是 Vue.js 的官方路由管理工具,可以在不同的场景下通过多种方式传递和接收路由参数。下面将详细讲解几种常见的路由传值方式,并提供相应的代码示例。 1. 通过路由参数传…...

两分钟解决 :![rejected] master -> master (fetch first) , 无法正常push到远端库

目录 分析问题的原因解决 分析问题的原因 在git push的时候莫名遇到这种情况 若你在git上修改了如README.md的文件。由于本地是没有README.md文件的,所以导致 远端仓库git和本地不同步。 将远端、本地进行合并就可以很好的解决这个问题 注意:直接git pu…...

)

浏览器安全(同源策略及浏览器沙箱)

一、同源策略(Same Origin Policy) 1.定义 同源策略(Same - origin Policy)是一种浏览器的安全机制。它规定一个网页的脚本只能访问和操作与它同源的资源。这里的 “源” 包括协议(如 http、https)、域名&…...

w~Transformer~合集11

我自己的原文哦~ https://blog.51cto.com/whaosoft/12472192 #LightSeq 最高加速9倍!字节跳动开源8比特混合精度Transformer引擎,近年来,Transformer 已经成为了 NLP 和 CV 等领域的主流模型,但庞大的模型参数限制了它的高效训练和推理。…...

Coursera四门课备考入学考试

某学校入学考试复习用,刷到的话纯靠缘分,不方便回答多余问题 (博主本人waive掉了没有考过,但还是基本都学完了) 记录学习coursera的四门课(顺序Py在DS前,其他无所谓) Mathematics fo…...

Flink(八):DataStream API (五) Join

1. Window Join Window join 作用在两个流中有相同 key 且处于相同窗口的元素上。这些窗口可以通过 window assigner 定义,并且两个流中的元素都会被用于计算窗口的结果。两个流中的元素在组合之后,会被传递给用户定义的 JoinFunction 或 FlatJoinFunct…...

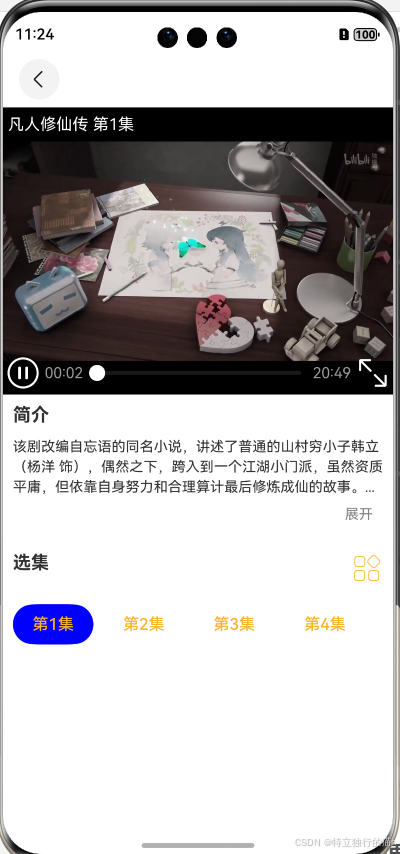

HarmonyOS NEXT边学边玩:从零实现一个影视App(六、视频播放页的实现)

在HarmonyOS NEXT中,ArkUI是一个非常强大的UI框架,能够帮助开发者快速构建出美观且功能丰富的用户界面。本文将详细介绍如何使用ArkUI实现一个影视App的视频播放页面。将从零开始,逐步构建一个功能完善的视频播放页面,并解释每一部…...

salesforce实现一个字段的默认初始值根据另一个字段的值来自动确定

在 Salesforce 中,可以通过 公式字段 或 触发器 (Trigger) 实现字段的默认初始值根据另一个字段的值来自动确定,具体实现方法如下: 1. 使用公式字段 公式字段是一种动态字段,值会根据公式实时计算。 步骤: 导航到字段…...

Linux 文件权限详解

目录 前言 查看文件权限 修改文件权限 符号方式 数字方式 前言 Linux 文件权限是系统中非常重要的概念之一,用于控制对文件和目录的访问。权限分为读(Read)、写(Write)、执行(Execute)三个…...

【混合开发】CefSharp+Vue桌面应用程序开发

为什么选择CefSharpVue做桌面应用程序 CefSharp 基于 Chromium Embedded Framework (CEF) ,它可以将 Chromium 浏览器的功能嵌入到 .NET 应用程序中。通过 CefSharp,开发者可以在桌面应用程序中集成 Web 技术,包括 HTML、JavaScript、CSS 等…...

从三角函数到雷达滤波:三角窗的DSP实现与性能测试全记录

从三角函数到雷达滤波:三角窗的DSP实现与性能测试全记录 1. 三角窗的数学本质与信号处理价值 在数字信号处理领域,窗函数就像是一位精密的调音师,能够对原始信号进行细致的修饰和调整。三角窗作为其中最基础却又最富特色的成员之一࿰…...

QuickSnap:Blender智能捕捉引擎提升40%建模效率

QuickSnap:Blender智能捕捉引擎提升40%建模效率 【免费下载链接】quicksnap Blender addon to quickly snap objects/vertices/points to object origins/vertices/points 项目地址: https://gitcode.com/gh_mirrors/qu/quicksnap 在三维建模领域,…...

大厂面试秘籍:AI岗位必问的10道题解析

在人工智能技术迅猛发展的今天,AI测试开发岗位已成为大厂竞相争夺的热门领域。对于软件测试从业者而言,转型AI岗位不仅是职业跃迁的机遇,更是技术深化的挑战。一、基础概念题:AI、ML、DL的区别及测试意义这道题考察对人工智能生态…...

文脉定序详细步骤:自定义prompt模板提升BGE-m3在垂直领域表现

文脉定序详细步骤:自定义prompt模板提升BGE-m3在垂直领域表现 1. 理解文脉定序与BGE-m3的核心价值 文脉定序是一款基于BGE-m3模型的智能语义重排序系统,专门解决传统搜索引擎"搜得到但排不准"的痛点。它通过全交叉注意机制,对问题…...

C语言入门避坑指南:从雨课堂高频错题解析编程新手常见误区

C语言入门避坑指南:从雨课堂高频错题解析编程新手常见误区 刚接触C语言时,很多同学会被看似简单的语法规则绊倒。那些在课堂上反复强调的细节,往往成为考试中最容易丢分的陷阱。本文将结合电子科技大学《程序设计与算法基础I》课程的真实错题…...

)

保姆级教程:在Android项目中集成微信Matrix性能监控框架(含避坑指南)

Android性能监控实战:微信Matrix框架深度集成指南 在移动应用开发领域,性能优化始终是开发者面临的核心挑战之一。微信开源的Matrix框架作为一套全平台性能监控工具链,为Android开发者提供了从方法耗时、ANR检测到内存泄漏分析等全方位的监控…...

JAVA-- 突破默认限制:在Java8 Parallel Stream中高效管理自定义线程池

1. 为什么需要自定义线程池管理Parallel Stream Java8引入的Parallel Stream确实让并行编程变得简单,但很多开发者在使用过程中会发现一个尴尬的事实:所有并行流操作默认共享同一个ForkJoinPool公共线程池。这就好比小区里所有住户共用一个电表ÿ…...

Arduino-IRremote代码调试技巧:10个高效解决开发难题的方法

Arduino-IRremote代码调试技巧:10个高效解决开发难题的方法 【免费下载链接】Arduino-IRremote Infrared remote library for Arduino: send and receive infrared signals with multiple protocols 项目地址: https://gitcode.com/gh_mirrors/ar/Arduino-IRremot…...

手把手教你用RK3576开发板驱动RC522读卡器:一个SPI实战项目的完整配置流程

手把手教你用RK3576开发板驱动RC522读卡器:一个SPI实战项目的完整配置流程 在嵌入式开发领域,能够独立完成一个从硬件连接到软件驱动的完整项目,是每个开发者成长的必经之路。RK3576作为一款性能强劲的开发板,搭配常见的RC522读卡…...

「码动四季·开源同行」golang:负载均衡如何提高系统可用性?

负载均衡能够将大量的请求,根据负载均衡算法,分发到多台服务器上进行处理,使得所有服务器负载都维持在高效稳定的状态,以提高系统的吞吐量。此外,多个服务实例组成的服务集群,消除了单点问题,当…...