复位信号的同步与释放(同步复位、异步复位、异步复位同步释放)

文章目录

- 背景

- 前言

- 一、复位信号的同步与释放

- 1.1 ··· 同步复位

- 1.1.1 ··· 综述

- 1.1.2 ··· 优缺点

- 1.2 ··· recovery time和removal time

- 1.3 ··· 异步复位

- 1.3.1 ··· 综述

- 1.3.2 ··· 优缺点

- 1.4 ··· 同步复位 与 异步复位

- 1.5 ··· 异步复位、同步释放

- 1.5.1 ··· 总述

- 1.5.2 ··· 机理

- 1.5.3 ··· 复位网络

- 二、思考与补充

- 2.1 ··· 复位信号是否被需要

- 2.2 ··· 关于第一级触发器的数据端口

- 2.3 ··· 第二个dff是否存在亚稳态

- 2.4 ··· 异步复位去毛刺

- 2.5 ··· PLL配置后的复位设计

- 2.6 ··· 复位的消耗的资源比你想象的要多

- 参考文献

说明1:在查阅相关资料过程中,发现一些关于有趣的知识点,本文有尝试对其进行整合,力求详尽。

说明2:如果文章有误,欢迎大家指出、讨论,笔者也会积极改正,希望大家一起进步!

背景

笔者前一阵子在写Verilog代码时,关于rst_N信号,用的是如下片段。

input Clk;

input rst_N;

reg rst_N_d;

always @(posedge Clk or negedge rst_N) beginif (!rst_N) beginrst_N_d <= 1'b0;end else beginrst_N_d <= 1'b1;end

end

// 将rst_N_d作为整个工程的复位信号,接到顶层模块下面的各个子模块中。

但是,实际将代码下载到开发板后,发现将输入信号rst_N反复置0、置1切换时,输出的效果相比于预期效果,不是很稳定,百思不得其解。随后,一个经验丰富的大佬告诉我,可以考虑异步复位、同步释放的方式来控制所有子模块的rst_N_d 信号,如下所示。

input Clk;

input rst_N;

reg rst_N_d1,rst_N_d2;

always @(posedge Clk or negedge rst_N)if (!rst_N) beginrst_N_d1 <= 1'b0;rst_N_d2 <= 1'b0;end else beginrst_N_d1 <= 1'b1;rst_N_d2 <= rst_N_d1;

end

// 将rst_N_d2作为整个工程的复位信号,接到顶层模块下面的各个子模块中。

改完后,发现代码下载到开发板后的效果比较不错,稳定了很多。

基于此,考虑到自身学FPGA是野路子,决定好好研究一下同步与释放,记作此文。

前言

-

复位的作用:

可以使代码或者是器件恢复到一个已知、确定的状态,如初始状态;

可以寄存器、计数器等内部的数据置为预设的值。 -

复位的目的:

1、通过控制复位信号,确保电路从已知的初始状态开始运行。

2、通过控制复位信号,使电路从某个错误状态回到已知状态。 -

在FPGA设计中,复位信号的同步与释放是确保系统稳定性和可靠性的关键。几种常见的复位信号,如下:

1、同步复位

2、异步复位

3、异步复位、同步释放 -

关于触发器,已在前文《7系列 之 存储单元(Storage Elements)》中有过介绍,诸位道友可点击链接进行传送。

-

本文所查看得RTL、Synthesis视图,是基于xc7a100tfgg676-2 (active)进行的。

一、复位信号的同步与释放

1.1 ··· 同步复位

1.1.1 ··· 综述

-

诸位道友经常提及的 同步复位 ,

即同步复位、同步释放,Synchronous Reset and Synchronous Release。 -

复位信号的复位、释放都是与时钟信号同步进行的,

这意味着,复位信号的变化只在特定的时钟边沿(通常是上升沿)发生。 -

Verilog代码,如下:

input Clk;

input rst_N;

reg rst_N_d;

always @(posedge Clk ) beginif (!rst_N) beginrst_N_d <= 1'b0;end else beginrst_N_d <= 1'b1;end

end

- 其RTL视图为:

- 其综合后的电路为:

从RTL视图来看,同步复位的代码过程就是一次触发器过程。

而其综合的结果为,FDRE。

注:FDRE,为Xilinx的触发器的Primitive之一;功能描述为:同步使能、同步复位。

1.1.2 ··· 优缺点

-

优点:

1、复位、释放操作是在时钟边沿同步进行的,因此可以确保所有的寄存器和逻辑单元在同一个时钟周期内被正确地复位、释放,从而给了寄存器足够的时间来稳定状态来减少复位信号引起的亚稳态问题、避免了由于复位信号不同步导致的时序不确定性。

2、同步复位使得电路是同步的,可使静态时序分析更加简单,减少时序分析难度。 -

缺点:

1、采用同步复位,需要在数据输入端增加组合逻辑,消耗额外的逻辑资源;

2、同步复位比较依赖于时钟信号,且复位信号的脉冲宽度必须要大于一个时钟周期,才能确保同步复位。

2、同步复位比较依赖于时钟信号,且复位信号的脉冲宽度必须要大于一个时钟周期,才能确保同步复位。

3、如下图所示,博文《异步复位 & 同步释放》在同步复位的缺点中提及到:“一些三态总线的初始化过程中,要求最好异步复位。”。

4、当复位信号的撤销时间在建立时间和保持时间以内时,也会产生亚稳态。

1.2 ··· recovery time和removal time

信号的本身不稳定、或者信号采样时刻不确定,都可能会带来亚稳态。

在同步电路中,输入数据需要与时钟满足setup time和hold time才能进行数据的正常传输,防止亚稳态。同样的道理,对于一个异步复位寄存器来说,异步复位信号同样需要和时钟满足recovery time和removal time 才能有效进行复位操作和复位释放操作,防止输出亚稳态。(《异步复位和同步释放》)

- recovery time(恢复时间),指撤销复位状态时,在时钟有效沿来临之前,复位信号保持无效电平的最短时间,即复位释放与下一个时钟有效沿之间需要间隔的最小时间,类似于setup time。

- removal time(去除时间),指进入复位状态时,在时钟有效沿来临之后,复位信号保持有效电平的最短时间,即复位信号与上一个时钟有效沿之间需要间隔的最小时间,类似于hold time。

无论是复位信号的电平,

必须要满足recovery time和removal time这两个要求,否则可能会造成亚稳态。

另外,并不是复位信号撤销时才可能出现亚稳态,复位信号一开始出现时,同样可能会存在亚稳态,只不过异步复位信号持续时间长,即使第一个周期出现了亚稳态(即第一个周期复位未成功),下一个时钟周期也不会再出现亚稳态了。如果复位信号的变化只持续刚刚一个时钟周期,那么复位信号开始和撤销时都可能会出现亚稳态。(《异步复位,同步释放》)

1.3 ··· 异步复位

- 诸位道友所经常提及的 异步复位 ,

即,异步复位、异步释放,Asynchronous Reset and Asynchronous Release。

复位信号,不随着系统时钟的边沿触发起作用,而是可独立于时钟信号起作用。

1.3.1 ··· 综述

- Verilog代码,如下:

input Clk;

input rst_N;

reg rst_N_d;

always @(posedge Clk or negedge rst_N) beginif (!rst_N) beginrst_N_d <= 1'b0;end else beginrst_N_d <= 1'b1;end

end

-

其RTL视图为:

相比于同步复位,拥有异步复位的寄存器在设计过程中就多了一个引脚(复位引脚)。

相比于同步复位,拥有异步复位的寄存器在设计过程中就多了一个引脚(复位引脚)。 -

其综合后的电路为:

而其综合的结果为,FDCE。

而其综合的结果为,FDCE。

注:FDCE,为Xilinx的触发器的Primitive之一;功能描述为:同步使能、异步复位。

1.3.2 ··· 优缺点

-

优点:

1、大多数的触发器都有异步复位端口,能保证数据路径上是干净的,不用消耗额外的逻辑资源。

2、复位信号不依赖于时钟,不管有没有时钟信号,复位信号都能使电路复位。 -

缺点:

1、当异步复位信号的撤销时间在Trecovery(恢复时间)和Tremoval(移除时间)之间时,输出结果就会出现亚稳态,造成复位失败。

recovery time和removal time都是检查异步信号(reset或preset或set)的释放沿,释放沿必须在时钟沿前面提前recovery time释放,或者在时钟沿后removal time之后释放。由于异步复位信号与时钟无必然联系,两者都是独立的,所以复位信号的释放将有一定的概率导致电路出现亚稳态。(《异步复位同步释放》)

2、系统所产生的的噪声或毛刺会引发伪复位,需要设计过滤器来消除复位电路上毛刺的影响。

3、异步复位需要确保满足时序要求。(补充:“复位信号和时钟信号一样,都是大扇出,所以无论同步或异步,在后端版图设计时需要分析复位树的时序确保满足时序要求。尽管存在复位 buffer tree,但最好要对复位信号少做逻辑。”(《异步复位,同步释放》))

1.4 ··· 同步复位 与 异步复位

只能说,各有优缺点。同步复位的好在于它只在时钟信号clk的上升沿触发进行系统是否复位的判断,这降低了亚稳态出现的概率;它的不好上面也说了,在于它需要消耗更多的器件资源,这是我们不希望看到的。FPGA的寄存器有支持异步复位专用的端口,采用异步复位的端口无需额外增加器件资源的消耗,但是异步复位也存在着隐患。异步时钟域的亚稳态问题同样的存在与异步复位信号和系统时钟信号之间。(《异步复位同步释放—关于复位的问题》)

ADD:

对于xilinx 7系列的FPGA而言,flip-flop支持高有效的异步复/置位和同步复位/置位。对普通逻辑设计,同步复位和异步复位没有区别,当然由于器件内部信号均为高有效,因此推荐使用高有效的控制信号,最好使用高有效的同步复位。输入复位信号的低有效在顶层放置反相器可以被吸收到IOB中。(《xilinx FPGA复位浅析》)

经过上述分析,同步复位和异步复位都有优缺点,那么是否能将连着结合、取长补短呢?

1.5 ··· 异步复位、同步释放

-

其实,阅读到这里,

不难看出异步复位、同步释放是同步释放和异步复位相结合的产物,

而不是同步异步与复位释放两两相组合的结果。 -

异步复位、同步释放,即

复位信号的复位状态有效时不受时钟信号的同步控制,

而在复位信号释放时(复位状态无效时)受到时钟信号的同步控制。 -

异步复位、同步释放的目的是在于:防止复位信号释放时产生亚稳态,且节省逻辑资源。

1.5.1 ··· 总述

- Verilog代码,如下:

input Clk;

input rst_N;

reg rst_N_d1,rst_N_d2;

always @(posedge Clk or negedge rst_N)if (!rst_N) beginrst_N_d1 <= 1'b0;rst_N_d2 <= 1'b0;end else beginrst_N_d1 <= 1'b1;rst_N_d2 <= rst_N_d1;

end

- 其RTL视图为:

- 其综合后的电路为:

- 其综合后的电路为:

1.5.2 ··· 机理

-

异步复位:当复位信号拉低时,rst_N拉低,直接进入复位状态。

-

同步释放:当复位信号释放时,由于加入了两级同步缓存器,复位状态不会立即释放,而是等到同步时钟的有效沿时再进行释放;且,rst_N的释放信号不会随着rst_N的撤销而撤销。

-

同步释放的具体过程,如下:

1 第一个有效时钟沿到来时:当异步复位信号rst_N释放时,用来同步的第二级寄存器 rst_N_d2 的数据仍然是0,因此第二级寄存器 rst_N_d2 是不会出现亚稳态的。即便第一级寄存器 rst_N_d1 可能会出现亚稳态,但这个亚稳态并不是直接经过第二级寄存器 rst_N_d2 进行输出 ,需要等待下一个时钟有效沿的到来,相当于被打了节拍。

2 第二个有效时钟沿到来时:当第一级寄存器 rst_N_d1 上一个时刻的这个亚稳态经过第二级寄存器时,基本已经稳定下来了;即便稳定下来不为无效电平,那也就相当于复位信号的有效电平多持续了一个周期。因此我们可以看出,使用异步复位同步释放时,异步复位撤销后需要额外等待一个时钟周期。

简单理解:第2级DFF释放信号与时钟clk边沿同步,所以释放信号在clk上升沿后需经过Tco(Tsu+thd)才能到达下一级DFF的复位端口,所以可以满足下一级DFF的recovery time和removal time,从而不会出现亚稳态。(《异步复位同步释放》)

- 思考:

1、第一级触发器的输出,存在亚稳态的可能,这是毋庸置疑的,而且第一级触发器输出的亚稳状态是在逐渐衰减的,且可以持续一个时钟周期;正常情况下,第二级触发器的输出是非亚稳态。但是,如果在第二级触发器的采样时保持时间不够长,且这时第一级触发器的输出依旧处于亚稳态,那么,第二级触发器的输出也会是亚稳态的。不过,这属于小概率事件。

2、在目前的同步化设计中,用两级触发器进行同步可以消除绝大部分可能的亚稳态了。那么,是不是三级同步操作,会使输出的复位信号更加稳定呢;当然,这样会多消耗一个触发器。

3、《2级同步引发的思考》,关于两级触发器的思考,可以深入了解下。

既解决了同步复位的资源消耗问题,也解决了异步复位的亚稳态问题。其根本思想,也是将异步信号同步化。(《异步复位同步释放—关于复位的问题》)

不同的复位方式有各自的优缺点。但是在工程中,一般都用异步复位的方法,最好是异步复位同步释放的方法。(《异步复位,同步释放》)

1.5.3 ··· 复位网络

《异步复位 & 同步释放》提及到了复位分发技术,用两级触发器对复位信号打了两次节拍,这也算是异步复位、同步释放的应用了。

二、思考与补充

逛博客的时候,看到了一些有趣的问题与思考,截图放在文中了,供诸位道友参考学习。

也可以直接到 参考文献 这一章节,直接点击文章名称进行转跳。

2.1 ··· 复位信号是否被需要

实际上,在写Verilog代码时,写了过多的复位信号反而会对Fmax产生限制。

笔者感觉《同步复位和异步复位》这篇博客的这段解释,如下图所示,似乎更为细致。

同时,在一博客下面有看到对Xilinx官方文档《UltraFast Design Methodology Guide for FPGAs and SoCs (UG949)》的描述:

2.2 ··· 关于第一级触发器的数据端口

2.3 ··· 第二个dff是否存在亚稳态

《异步复位,同步释放的理解》,通过引用文献,对复位同步器得第二个dff是否存在亚稳态进行了解答,如下图所示。这也算是对本文章节《2.2.2 ··· 机理》中思考的一个解答吧。

2.4 ··· 异步复位去毛刺

《同步复位和异步复位》,这篇博客也有提到这么一个操作,截图给诸位道友看一下。

2.5 ··· PLL配置后的复位设计

文章《异步复位同步释放(Synchronized Asynchronous Reset)》中,提到了一种PLL配置后的复位设计,感觉有点眼熟,截个图放下面,供诸位道友观摩、讨论。

文字描述如下:

代码综合后的RTL如下:

代码综合后的RTL如下:

2.6 ··· 复位的消耗的资源比你想象的要多

以下截图出自博客《你真的会Xilinx FPGA的复位吗?》。

嗯,这部分实际上和前文中的 “复位信号是否被需要 ”这部分倒是挺相似的,道友们可以多留意下。

参考文献

1、《异步复位和同步释放》

2、《异步复位,同步释放》

3、《异步复位同步释放—关于复位的问题》

4、《异步复位 & 同步释放》

5、《异步复位,同步释放的理解》,这篇不错,安利一波。

6、《异步复位同步释放原理》

7、《同步复位和异步复位》

8、《异步复位同步释放》

9、《同步复位和异步复位》,这篇也不错。

10、《2级同步引发的思考》

11、《异步复位同步释放(Synchronized Asynchronous Reset)》

12、《xilinx FPGA复位浅析》

13、《你真的会Xilinx FPGA的复位吗?》,这篇也很不错。

14、《How do I reset my FPGA?》(笔者对这篇文章进行了翻译,《翻译:How do I reset my FPGA?》)

15、《RTL设计- 多时钟域按顺序复位释放》

相关文章:

复位信号的同步与释放(同步复位、异步复位、异步复位同步释放)

文章目录 背景前言一、复位信号的同步与释放1.1 同步复位1.1.1 综述1.1.2 优缺点 1.2 recovery time和removal time1.3 异步复位1.3.1 综述1.3.2 优缺点 1.4 同步复位 与 异步复位1.5 异步复位、同步释放1.5.1 总述1.5.2 机理1.5.3 复位网络 二、思考与补充2.1 复…...

Gartner发布2025年网络治理、风险与合规战略路线图

新型网络风险和合规义务,日益成为网络治理、风险与合规实践面临的问题。安全和风险管理领导者可以参考本文,实现从被动、专注于合规的方法到主动、进一步自动化方法的转型。 主要发现 不断变化的监管环境和不断扩大的攻击面,使企业机构难以实…...

基于STM32的智能空气质量监测与净化系统设计

目录 引言系统设计 硬件设计软件设计 系统功能模块 空气质量检测模块自动净化模块数据显示与用户交互模块远程监控与数据上传模块 控制算法 空气质量检测与判断算法净化设备控制算法数据记录与远程反馈算法 代码实现 空气质量检测与显示代码自动净化与调节代码数据上传与远程控…...

人工智能之数学基础:线性代数中的线性相关和线性无关

本文重点 在线性代数的广阔领域中,线性相关与线性无关是两个核心概念,它们对于理解向量空间、矩阵运算、线性方程组以及人工智能等问题具有至关重要的作用。 定义与直观理解 当存在一组不全为0的数x1,x2,...,xn使得上式成立的时候,那么此时我们可以说向量组a1,a2...,an…...

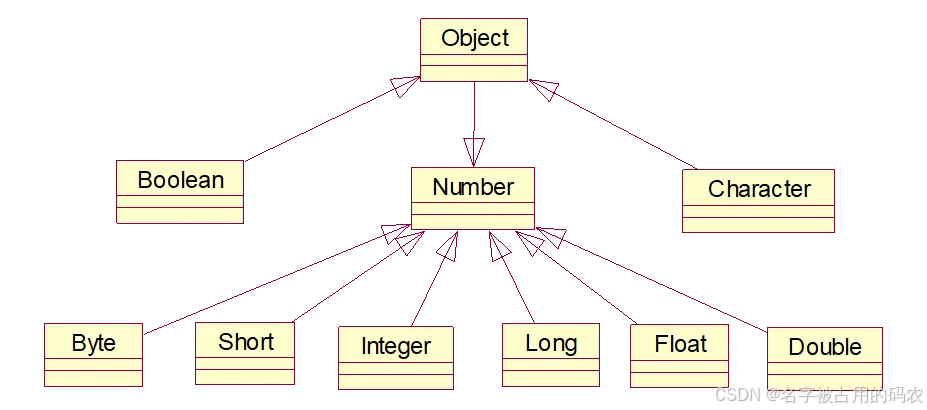

08 工欲善其事必先利其器—常用类

1 字符串相关 1.1 String 所属包:java.lang 代表不可变的字符序列 注意:Java中,String是一个final类 1)创建字符串方式 String a "hello"; // 开辟内存空间 String b new String("hello"); String d…...

Redis实战-初识Redis

初识Redis 1、Redis简介2、 Redis数据结构简介3、 Redis命令3.1 字符串3.2 列表3.3 集合3.4 散列3.5 有序集合3.6 发布与订阅3.7 其他命令3.7.1 排序3.7.2 过期时间 如有侵权,请联系~ 如有错误,也欢迎批评指正~ 本篇文章大部分是来…...

spring boot中实现手动分页

手动分页 UserMapper.xml <?xml version"1.0" encoding"UTF-8"?> <!DOCTYPE mapper PUBLIC "-//mybatis.org//DTD Mapper 3.0//EN" "http://mybatis.org/dtd/mybatis-3-mapper.dtd" > <mapper namespace"cn.m…...

【优选算法】5----有效三角形个数

又是一篇算法题,今天早上刚做的热乎的~ 其实我是想写博客但不知道写些什么(就水一下啦) -------------------------------------begin----------------------------------------- 题目解析: 这道题的题目算是最近几道算法题里面题目最短的&a…...

C++打字模拟

改进于 文宇炽筱_潜水 c版的打字效果_c自动打字-CSDN博客https://blog.csdn.net/2401_84159494/article/details/141023898?ops_request_misc%257B%2522request%255Fid%2522%253A%25227f97863ddc9d1b2ae9526f45765b1744%2522%252C%2522scm%2522%253A%252220140713.1301023…...

最新版pycharm如何配置conda环境

首先在conda prompt里创建虚拟环境,比如 conda create --prefix E:/projects/myenv python3.8然后激活 conda activate E:/projects/myenv往里面安装点自己的包,比如 conda install pytorch1.7.1 torchvision0.8.2 -c pytorch打开pycharm 注意&#x…...

)

UML-对象图(Object Diagram)

一、定义 UML对象图用于描述系统中对象的状态和相互关系,是类图的一个实例化版本,主要展示了类图中定义的关系在特定时间点的实际体现。它帮助开发者在设计阶段理解对象之间的实际关系、属性值和状态,从而支持系统设计的准确性与有效性。 二、组成要素 UML对象图主要由以…...

Jmeter 动态参数压力测试时间段预定接口

🎯 本文档详细介绍了如何使用Apache JMeter进行压力测试,以评估预定接口在高并发场景下的性能表现。通过创建线程组模拟不同数量的用户并发请求,利用CSV文件动态配置时间段ID和用户token,确保了测试数据的真实性和有效性。文档中还…...

超大型集团合并报表数智管理转型

摘要:数字经济时代,数字化技术已成为驱动财务管理价值释放的重要引擎,数智化能力的提升是当前一流财务信息化建设的最新趋势。财务部门是企业的“数据交汇中心”和“信息加工中心”,通过对企业各项财务数据的分类、汇总和清晰呈现…...

[MCAL]Mcu配置

PostBuild: PreCompile: 选择时钟来源; 选择初始McuInitClock() 函数 电路手册里有晶振频率,如上所示;...

Qt基础项目篇——Qt版Word字处理软件

一、核心功能 本软件为多文档型程序,界面是标准的 Windows 主从窗口 拥有:主菜单、工具栏、文档显示区 和 状态栏。 所要实现的东西,均在下图了。 开发该软件,主要分为下面三个阶段 1)界面设计开发 多窗口 MDI 程序…...

算法刷题笔记——图论篇

这里写目录标题 理论基础图的基本概念图的种类度 连通性连通图强连通图连通分量强连通分量 图的构造邻接矩阵邻接表 图的遍历方式 深度优先搜索理论基础dfs 与 bfs 区别dfs 搜索过程深搜三部曲所有可达路径广度优先搜索理论基础广搜的使用场景广搜的过程 岛屿数量孤岛的总面积沉…...

Java空指针异常处理:判空、Optional与Assert解析

在Java编程中,空指针异常(NullPointerException)是最常见的运行时错误之一。本文将深入探讨三种处理空指针异常的方法:传统的判空检查、Java 8引入的Optional类以及使用断言(Assert)。通过代码示例和应用场…...

【vim】vim编辑器如何设置行号

vim编辑器如何设置行号 一、**临时设置行号**二、永久设置行号2.1. **用户配置文件方式(针对当前用户)**2.2. **全局配置文件方式(谨慎使用,会影响所有用户)** 在Vim中设置行号有以下两种常见的方法: 一、…...

MySQL可直接使用的查询表的列信息

文章目录 背景实现方案模板SQL如何查询列如何转大写如何获取字符位置如何拼接字段 SQL适用场景 背景 最近产品找来,想让帮忙出下表的信息,字段驼峰展示,每张表信息show create table全部展示,再逐个粘贴,有点太耗费时…...

在线宠物用品|基于vue的在线宠物用品交易网站(源码+数据库+文档)

|在线宠物用品交易网站 目录 基于springbootvue的在线宠物用品交易网站 一、前言 二、系统设计 三、系统功能设计 四、数据库设计 五、核心代码 六、论文参考 七、最新计算机毕设选题推荐 八、源码获取: 博主介绍:✌️大厂码农|毕设布道师&am…...

OpenClaw+Phi-3-mini-128k-instruct:技术书籍翻译与术语统一系统

OpenClawPhi-3-mini-128k-instruct:技术书籍翻译与术语统一系统 1. 为什么需要自动化翻译工具 作为一名技术书籍的爱好者,我经常需要阅读英文原版的技术文档和书籍。但直接阅读英文原版对很多人来说存在门槛,而现有的机器翻译工具在技术术语…...

PostgreSQL 初体验

PostgreSQL 安装一、核心基础1. 简介PostgreSQL 是开源对象关系型数据库(ORDBMS),源自加州伯克利分校,兼容 SQL 标准,支持事务、复杂查询与扩展。2. 核心特点完全开源,许可宽松高度符合 SQL 标准࿰…...

估计研究附Matlab代码)

用于计算系统状态的卡尔曼最优增益和最小均方误差(MMSE)估计研究附Matlab代码

✅作者简介:热爱科研的Matlab仿真开发者,擅长数据处理、建模仿真、程序设计、完整代码获取、论文复现及科研仿真。🍎 往期回顾关注个人主页:Matlab科研工作室🍊个人信条:格物致知,完整Matlab代码及仿真咨询…...

别再只测电压了!解锁杰理AC632蓝牙芯片ADC的隐藏玩法:电池检测与低功耗设计

杰理AC632蓝牙芯片ADC实战:电池检测与低功耗设计全解析 在蓝牙耳机、智能穿戴等电池供电设备的开发中,精准的电池电量监测和低功耗设计往往是决定产品成败的关键因素。杰理AC632作为一款广泛应用于消费电子领域的蓝牙芯片,其内置的ADC功能为开…...

)

py每日spider案例之某website参数token获取(ob混淆,难度一般)

逆向参数: 请求代码: import requestsheaders = {"accept": "*/*","accept-language": "zh-CN,zh;q=0.9","cache-control": "n...

圆波导圆极化天线的设计与仿真:从理论到实践

1. 圆波导圆极化天线的基础原理 圆极化天线在现代无线通信系统中扮演着重要角色,特别是在卫星通信、雷达和5G毫米波应用中。与传统的线极化天线相比,圆极化天线能够有效减少极化失配带来的信号损失,在复杂传播环境中表现更加稳定。 圆波导作为…...

ha_xiaomi_home:小米智能家居与Home Assistant无缝集成指南

ha_xiaomi_home:小米智能家居与Home Assistant无缝集成指南 【免费下载链接】ha_xiaomi_home Xiaomi Home Integration for Home Assistant 项目地址: https://gitcode.com/GitHub_Trending/ha/ha_xiaomi_home ha_xiaomi_home是一款开源工具,能帮…...

NeuroKit2:神经生理信号处理的全流程解决方案

NeuroKit2:神经生理信号处理的全流程解决方案 【免费下载链接】NeuroKit NeuroKit2: The Python Toolbox for Neurophysiological Signal Processing 项目地址: https://gitcode.com/gh_mirrors/ne/NeuroKit 在神经科学与生理信号研究领域,高效处…...

LightOnOCR-2-1B实战体验:上传图片,秒出文字,简单高效

LightOnOCR-2-1B实战体验:上传图片,秒出文字,简单高效 1. 从“想法”到“文字”,只需要三步 你有没有过这样的经历?手机拍了一张会议白板的照片,想把上面的要点整理成文档,结果对着照片一个字…...

5大维度解析:Label Studio ML Backend如何实现自动化标注效率革命

5大维度解析:Label Studio ML Backend如何实现自动化标注效率革命 【免费下载链接】label-studio-ml-backend Configs and boilerplates for Label Studios Machine Learning backend 项目地址: https://gitcode.com/gh_mirrors/la/label-studio-ml-backend …...