HNU-电路与电子学-实验3

实验三 模型机组合部件的实现(二)(实验报告格式案例)

班级 计XXXXX 姓名 wolf 学号 2021080XXXXX

一、实验目的

1.了解简易模型机的内部结构和工作原理。

2.分析模型机的功能,设计 8 重 3-1 多路复用器。

3.分析模型机的功能,设计移位逻辑。

4.分析模型机的工作原理,设计模型机控制信号产生逻辑。

二、实验内容

1.用 VERILOG 语言设计模型机的 8 重 3-1 多路复用器;

2.用 VERILOG 语言设计模型机的移位模块;

3.用 VERILOG 语言设计模型机的控制信号产生逻辑。

[A]补=2*4-A

三、实验过程

1、8重3-1多路复用器

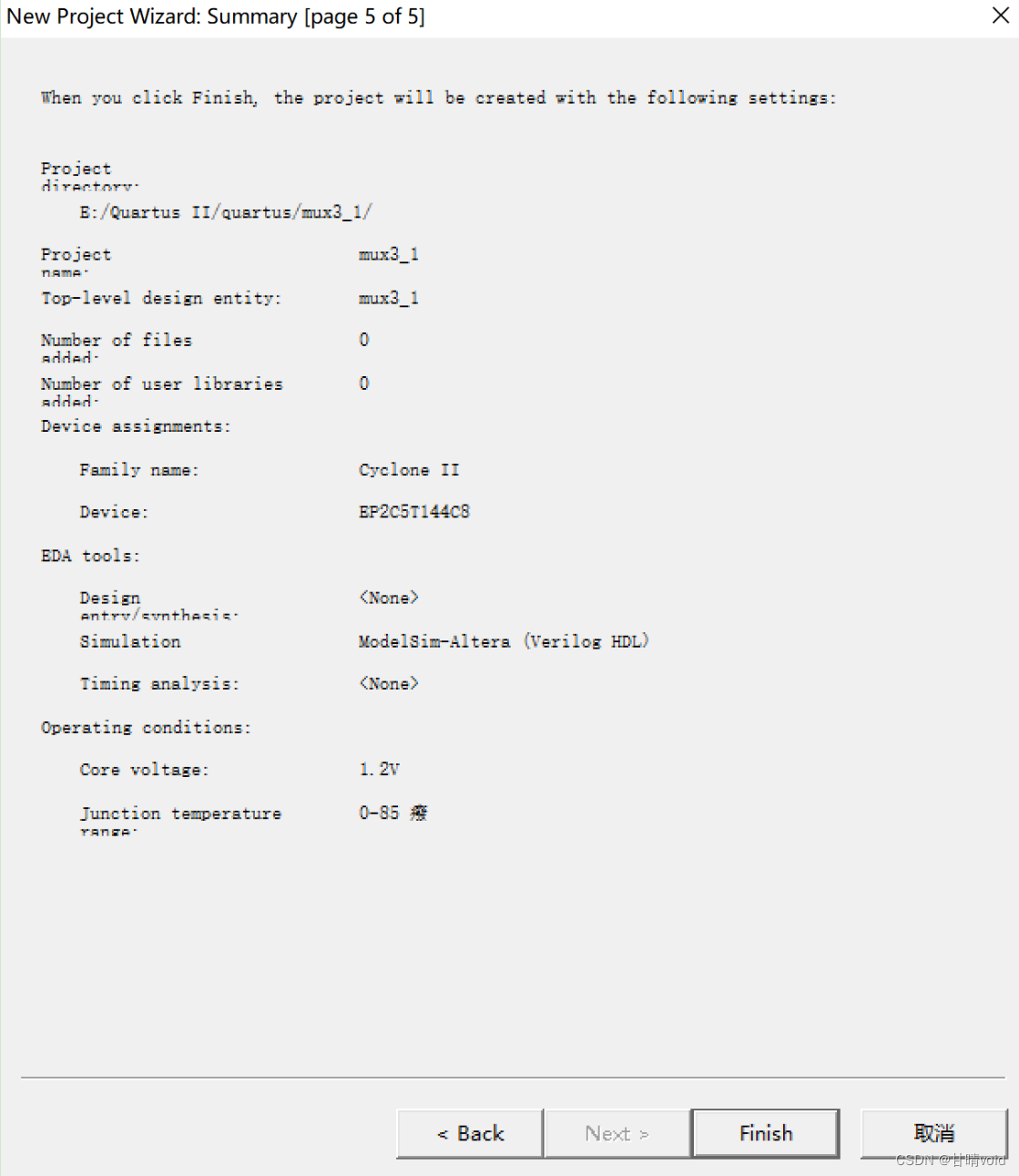

- 创建工程(选择的芯片为family=Cyclone II;name=EP2C5T144C8)

步骤:【File】->【new project wizard】->【next】->【next】->【properties】

->【next】->选择芯片类型 family=Cyclone II,name= EP2C5T144C8->【next】

->【finish】完成工程创建。

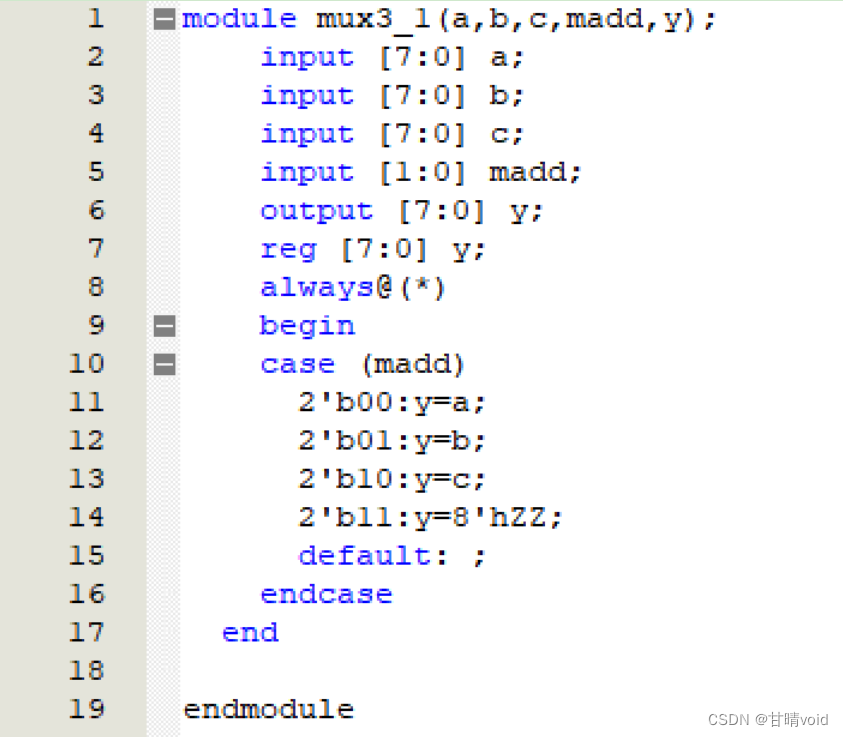

- 编写源代码

【file】->【Verilog HDL】->写好源代码,保存文件

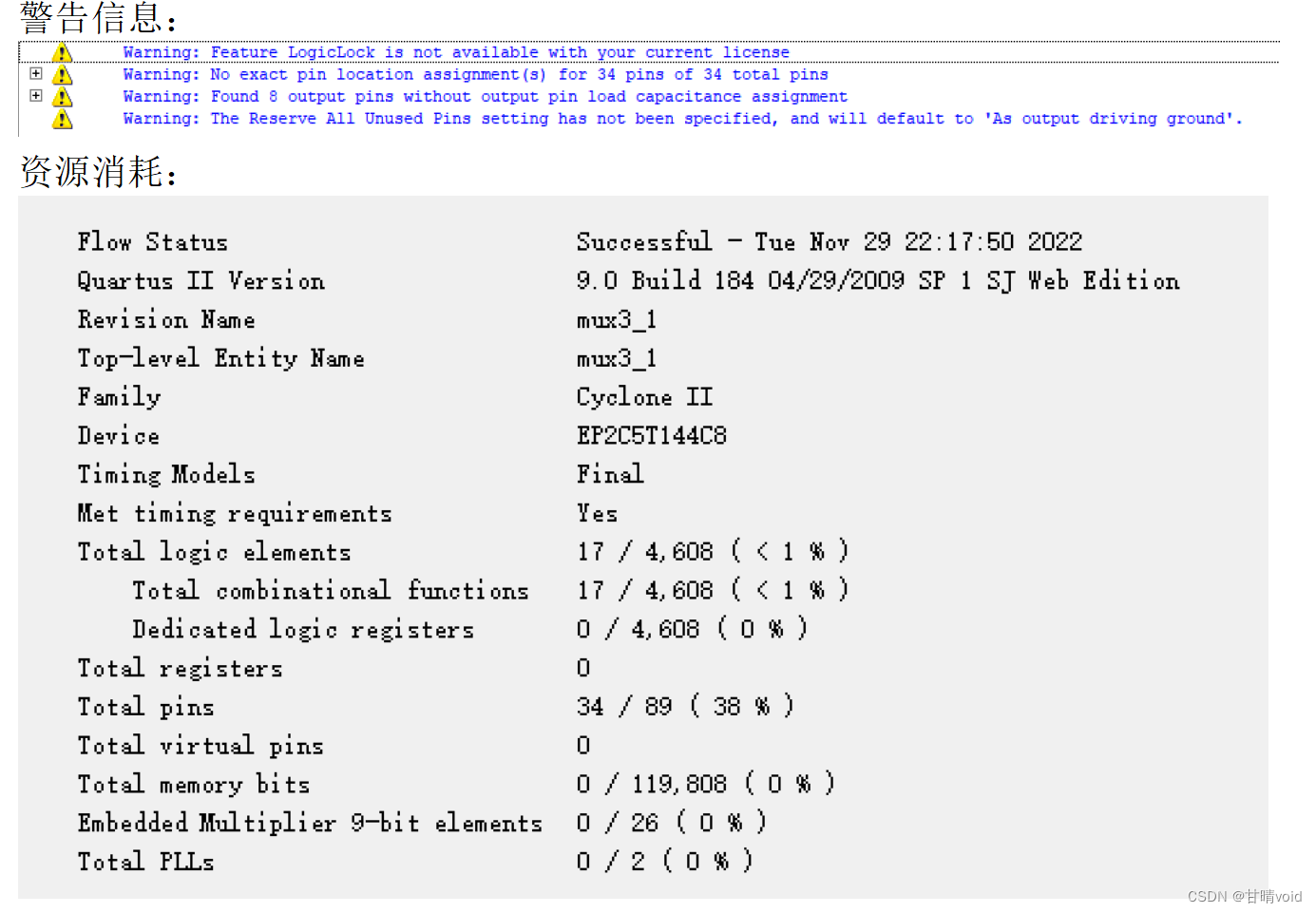

C) 编译与调试(包含编译调试过程中的错误、警告信息以及资源消耗)

D) RTL视图

视图分析:

分析:

由视图可得,视图左边为输入,右边为输出。其中连接有一系列的元器件。比如比较器:当输入相等时输出 1,不相等时输出 0;还有大部分的 2-1 选择器构成,当控制信号为 0 时,输出第一位,控制信号为 1 时,输出第二位。图中输入信号为 madd和 a,b,c,输出信号为 y。各个输出端口之间通过导线相连。

结论:

一个功能的实现需要经过多重门的处理后才能实现,一个元件的内部原理结构图十分复杂。

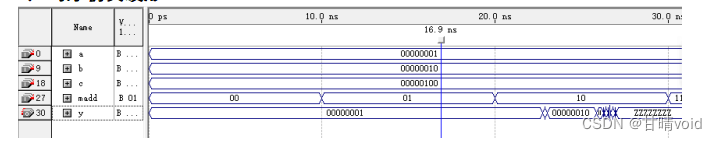

E) 功能仿真波形

结果分析及结论:

分析:

功能仿真是指不考虑器件延时和布线延时的理想情况下对源代码进行逻辑功能的验证。由仿真波形可得,对于输入状态的变化,输出结果实时变化,没有延迟,其结果与电路设计的真值表的结果相对应。

madd=00 时,控制输出 y 等于 a,正确

madd=01 时,控制输出 y 等于 b,正确

Madd=10 时,控制输出 y 等于 c,正确

Madd=11 时,控制输出高阻态,正确

结论:

功能仿真操作简单,能体现和验证实验的功能,但忽略延迟的影响会使结果与实际结果有一定误差。

F) 时序仿真波形

结果分析及结论:

分析:

时序仿真是指在布线后进行,是最接近真实器件运行的仿真,它与特定的器件有关,又包含了器件和布线的延时信息。由波形可得,当输入状态发生改变时,输出结果并未同时改变,而是有一定延迟,同时由于输入状态的改变,导致电路出现“冒险”,导致输出结果并未与预期结果相同。

结论:

时序仿真可以用来验证程序在目标器件中的时序关系。同时考虑了器件的延迟后,其输出结果跟接近实际情况,但是考虑的情况过多,不容易操作,容易产生错误。时序仿真不仅反应出输出和输入的逻辑关系,同时还计算了时间的延时信息,是与实际系统更接近的一种仿真结果。不过,要注意的是,这个时间延时是仿真软件“估算”出来的。

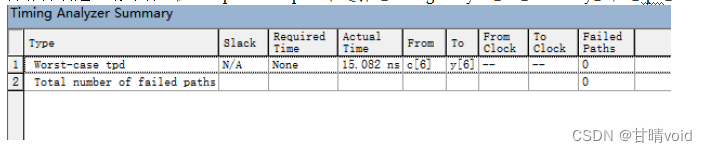

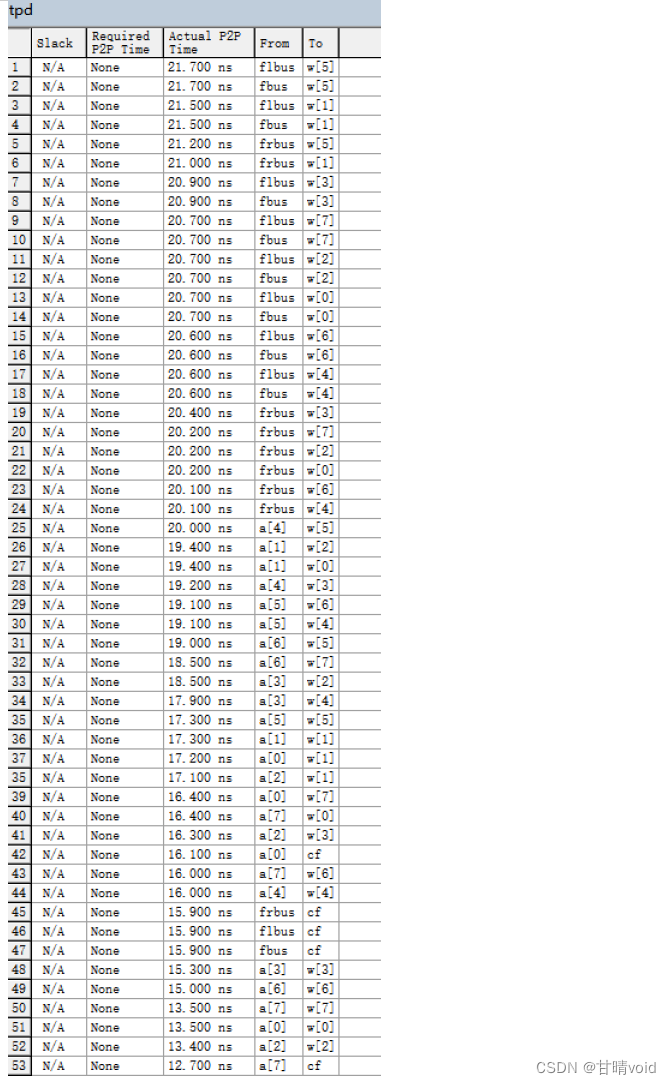

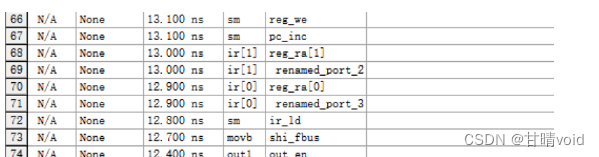

G) 时序分析

操作方法是:编译后,在compilation report中选择【timing analysis】-【summary】和【tpd】

结果分析及结论:

分析:

由图可得,Timing Analyzer Summmary 总结所有经典定时分析的结果,并报告每个定时特性的最坏情况定时。比如从 b[7]到 y[7]的最坏定时情况的 tpd 为 12.852ns。下面的tpd 报告表则给出了源节点和目标节点之间的 tpd 延迟间,比如第二行中 a[7]到 y[7] 的tpd 为 13.820ns。

结论:

实际连接图中个元器件连接之间是存在时间延迟的,而且不同的元器件之间的时间延迟也不相同。

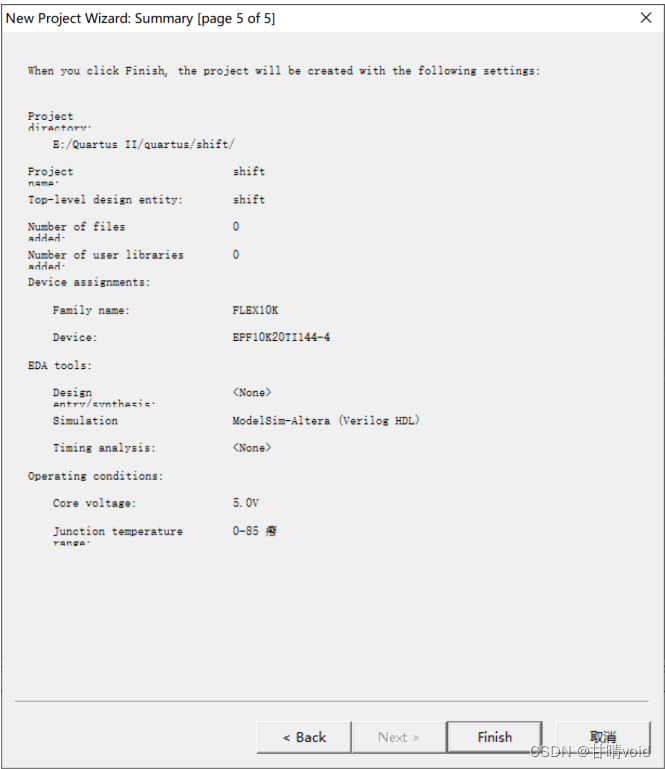

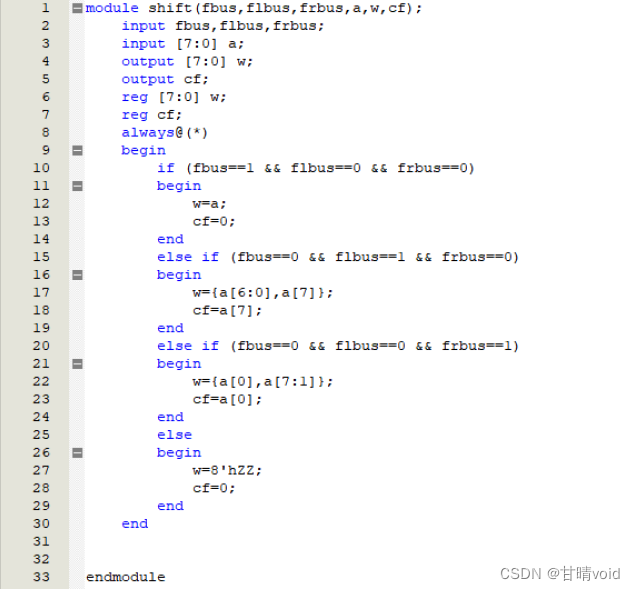

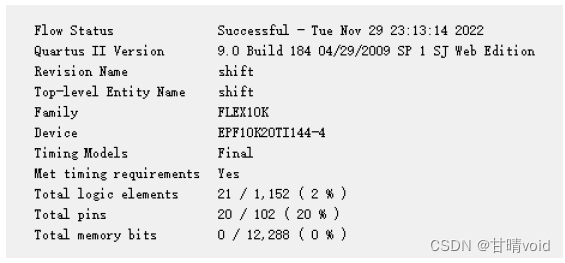

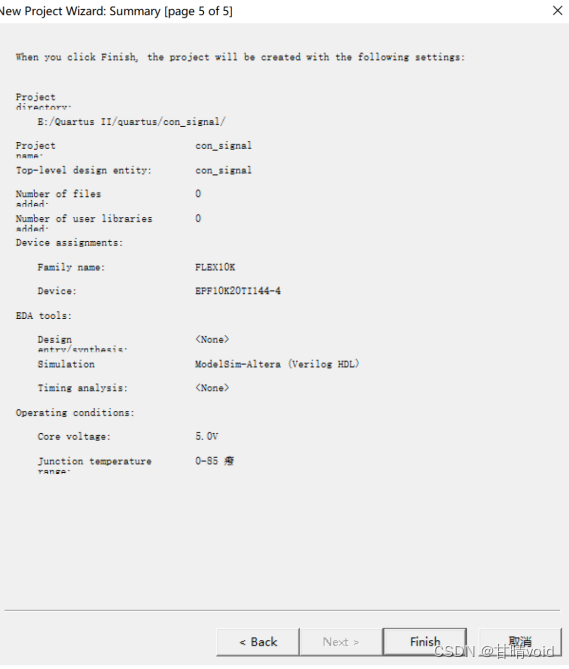

2、移位逻辑

A)创建工程(选择的芯片为family=FLEX10K;name=EPF10K20TI144-4)

B) 编写源代码

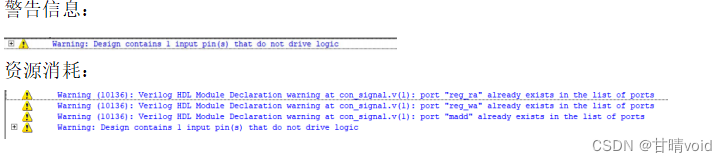

- 编译与调试(包含编译调试过程中的错误、警告信息以及资源消耗)

警告信息:

无警告信息

资源消耗:

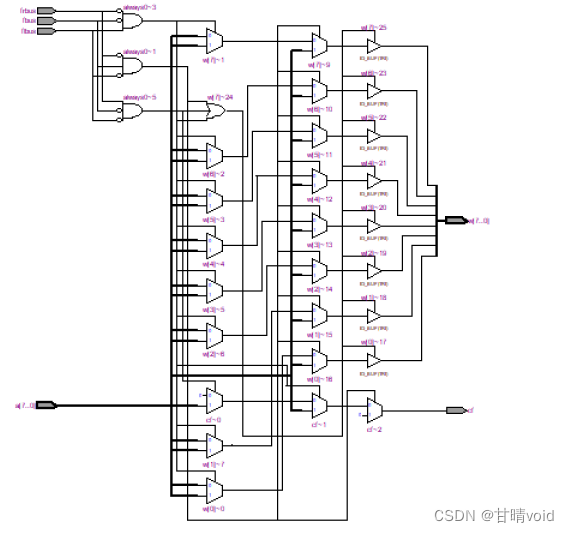

D) RTL视图

结果分析:

分析:

由视图可得,视图左边为输入,右边为输出。其中连接有一系列的元器件。比如比较器:当输入相等时输出 1,不相等时输出 0;还有大部分的 2-1 选择器构成,当控制信号为0 时,输出第一位,控制信号为 1 时,输出第二位。图中输入信号为 fbus,frbus,flbus 和 a,输出信号为 w。各个输出端口之间通过导线相连。

结论:

一个功能的实现需要经过多重门的处理后才能实现,一个元件的内部原理结构图十分复杂。

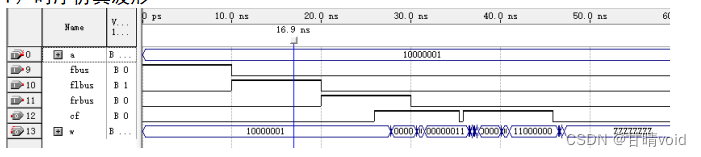

E) 功能仿真波形

结果分析及结论:

分析:

功能仿真是指不考虑器件延时和布线延时的理想情况下对源代码进行逻辑功能的验证。由仿真波形可得,对于输入状态的变化,输出结果实时变化,没有延迟,其结果与电路设计的真值表的结果相对应。

当fbus=1,frbus=0,flbus=0,不执行移位操作,输出等于输入,cf 不改变

当fbus=0,frbus=1,flbus=0,执行右移,输出等于输入右移移位,有进位的话cf为1

当fbus=0,frbus=0,flbus=1,执行左移,输出等于输入左移一位,cf 不改变

当控制信号全为 0 时,输出为高阻态,正确

结论:

功能仿真操作简单,能体现和验证实验的功能,但忽略延迟的影响会使结果与实际结果有一定误差。

F) 时序仿真波形

结果分析及结论:

分析:

时序仿真是指在布线后进行,是最接近真实器件运行的仿真,它与特定的器件有关, 又包含了器件和布线的延时信息。由波形可得,当输入状态发生改变时,输出结果并未同时 改变,而是有一定延迟,同时由于输入状态的改变,导致电路出现“冒险”,导致输出结果并未与预期结果相同。

结论:

时序仿真可以用来验证程序在目标器件中的时序关系。同时考虑了器件的延迟后,其输出结果跟接近实际情况,但是考虑的情况过多,不容易操作,容易产生错误。时序仿真不仅反应出输出和输入的逻辑关系,同时还计算了时间的延时信息,是与实际系统更接近的一种仿真结果。不过,要注意的是,这个时间延时是仿真软件“估算”出来的。

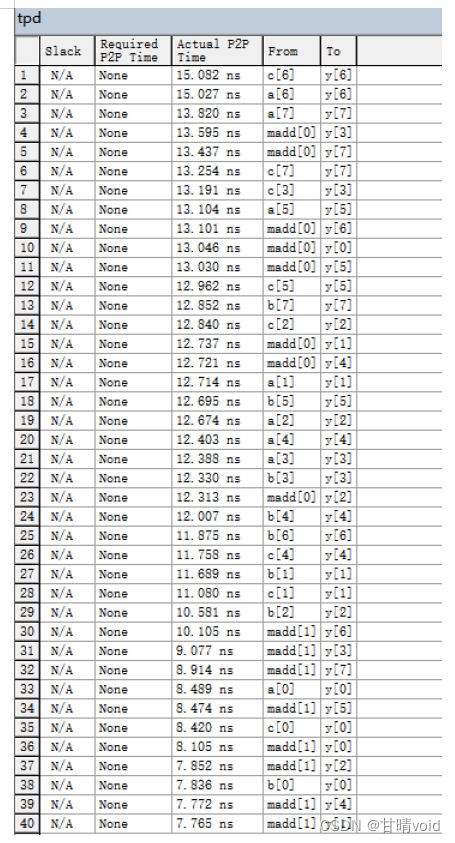

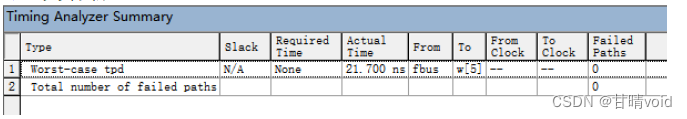

G) 时序分析

结果分析及结论:

分析:

由图可得,Timing Analyzer Summmary 总结所有经典定时分析的结果,并报告每个定时特性的最坏情况定时。比如从 fbus 到 w[0] 的最坏定时情况的 tpd 为 20.700ns。下面的 tpd 报告表则给出了源节点和目标节点之间的 tpd 延迟时间,比如第二行中 fbus 到 w[7] 的tpd 为 20.700ns。

结论:

实际连接图中个元器件连接之间是存在时间延迟的,而且不同的元器件之间的时间延迟也不相同。

3、控制信号产生逻辑

A)创建工程(选择的芯片为family=FLEX10K;name=EPF10K20TI144-4)

B) 编写源代码

- 编译与调试(包含编译调试过程中的错误、警告信息以及资源消耗)

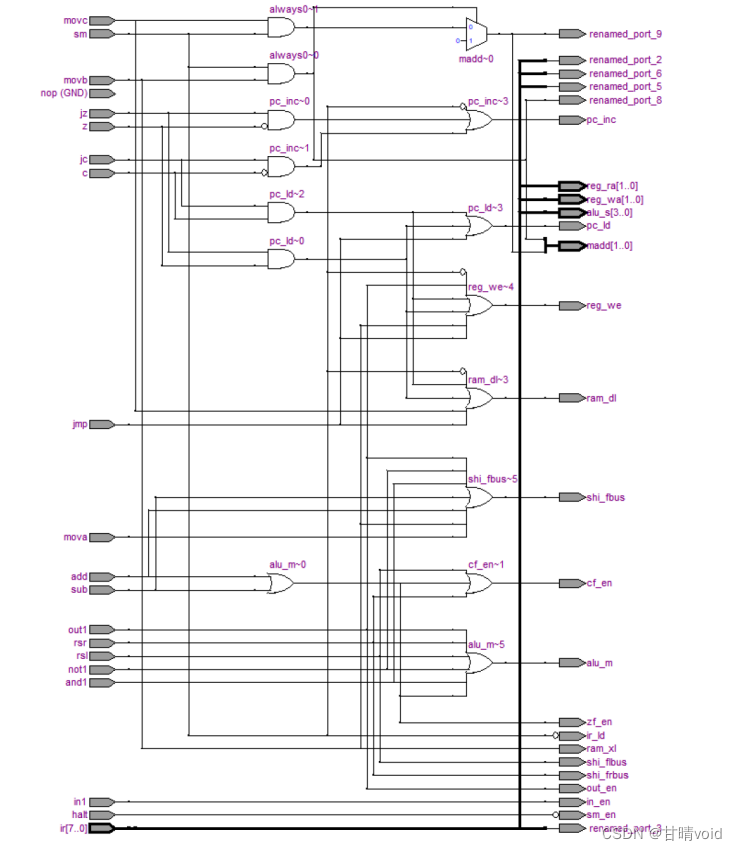

D) RTL视图

结果分析:

由视图可得,视图左边为输入,右边为输出。其中连接有一系列的元器件。比如比较器:当输入相等时输出 1,不相等时输出 0;还有大部分的与或门。图中输入信号为 sm 等20 个,输出信号包括 reg_ra 等 19 种情况。各个输出端口之间通过导线相连。

结论:

一个功能的实现需要经过多重门的处理后才能实现,一个元件的内部原理结构图十分复杂。

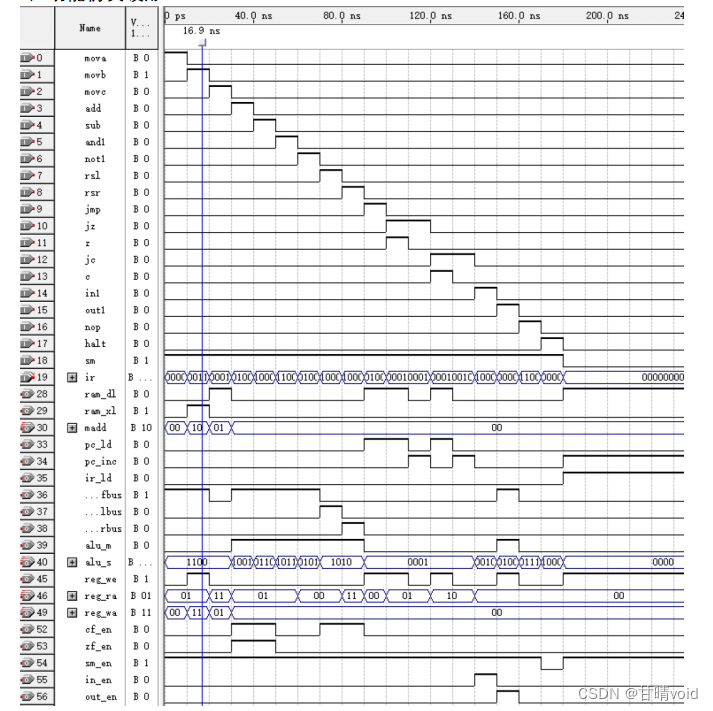

E) 功能仿真波形

结果分析及结论:

分析:

功能仿真是指不考虑器件延时和布线延时的理想情况下对源代码进行逻辑功能的验

证。由仿真波形可得,对于输入状态的变化,输出结果实时变化,没有延迟,其结果与电路

设计的真值表的结果相对应。

(1)当 mova 指令执行时,shi_fbus 和 sm_en 输出 1,其他输出为 0,madd 输出 00,

alu_s 输出为 1100,reg_ra 输出 01,reg_wa 输出 00,正确

(2)当 movb 指令执行时,ram_xl 和 shi_fbus 和 reg_we 和 sm_en 输出为 1,其他输出

为 0,madd 输出为 10,alu_s 输出为 1100,reg_ra 输出 01,reg_wa 输出 11,正确

(3)当 movc 指令执行时,ram_dl 和 sm_en 输出为 1,其他输出为 0,madd 输出 01,

alu_s 输出 1100,reg_ra 输出 11,reg_wa 输出 01,正确

(4)当 add 指令执行时,shi_fbus,alu_en,cf_en,zf_en,sm_en 输出为 1,其他输出

为 0,alu_s 为 1001,reg_ra 输出 01,reg_wa 输出 00,正确

(5)当 sub 指令执行时,shi_fbus 和 alu_m,cf_en,zf_en 和 sm_en 输出为 1,其他输

出为 0,alu_s 输出 0110,reg_ra 输出 01,reg_wa 输出 00,正确

(6)当 and1 指令执行时,shi_fbus 和 alu_m 和 sm_en 输出 1,其他输出 0,alu_s 输出

1011,reg_ra 输出 01,reg_wa 输出 00,正确

(7)not1 指令执行时,shi_fbus 和 alu_m 和 sm_en 输出 1,其他输出 0,alu_s 输出 0101,

reg_ra 输出 00,reg_wa 输出 00,正确

(8)rsl 指令执行时,shi_flbus 和 alu_m 和 cf_en 和 sm_en 输出 0,其他输出 0,alu_s

输出 1010,reg_ra 和 reg_wa 输出 00,正确

(9)rsr 指令执行时,shi_frbus 和 alu_m 和 cf_en 和 sm_en 输出 1,其他输出 0,alu_s

输出 10110,reg_ra 输出 11,reg_wa 输出 00,正确

(10)jmp 指令执行时,ram_dl,pc_ld,reg_we 和 sm_en 输出 1,其他输出 0,alu_s

输出 0001,reg_ra 和 reg_wa 输出 00,正确

(11)jz 指令为 1 和 jc 指令为 1 时,若 z 和 c 为 1 时,ram_dl 和 pc_ld 和 reg_we 和 sm_en输出为 1,其他输出为 0,正确

若 z 和 c 为 0 时,pc_inc 和 reg_we 和 sm_en 输出 1,其他输出 0,正确

(12)in1 指令执行时,sm_en 和 in_en 输出 1,其他输出 0,正确

(13)out1 指令执行时,sm_en 和 out_en 输出 1,其他输出 0,正确

(14)nop 指令执行时,sm_en 输出 1,其他输出 0,正确

(15)halt 指令执行时,输出全为 0,正确

结论:

功能仿真操作简单,能体现和验证实验的功能,但忽略延迟的影响会使结果与实际结

果有一定误差。0,reg_ra 输出 11,reg_wa 输出 00,正确

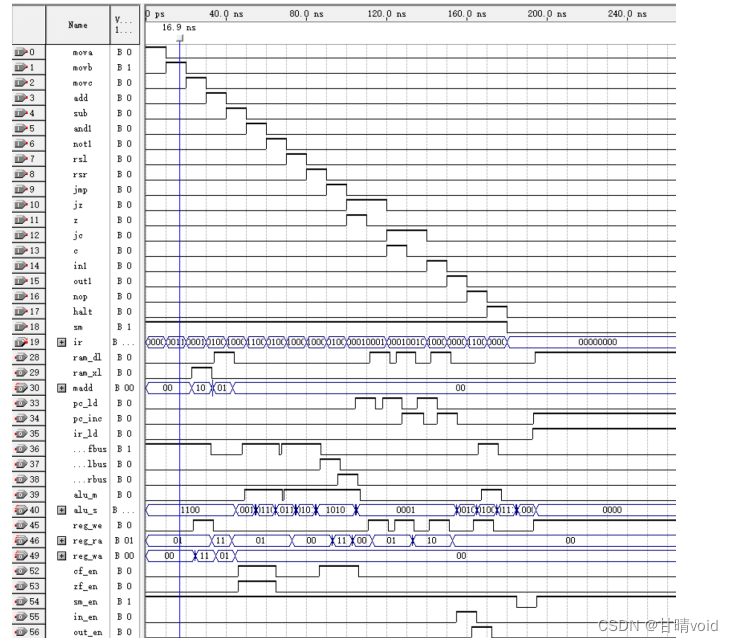

F) 时序仿真波形

分析:

时序仿真是指在布线后进行,是最接近真实器件运行的仿真,它与特定的器件有关,

又包含了器件和布线的延时信息。由波形可得,当输入状态发生改变时,输出结果并未同时

改变,而是有一定延迟,同时由于输入状态的改变,导致电路出现“冒险”,导致输出结果

并未与预期结果相同。

结论:

时序仿真可以用来验证程序在目标器件中的时序关系。同时考虑了器件的延迟后,其

输出结果跟接近实际情况,但是考虑的情况过多,不容易操作,容易产生错误。时序仿真不

仅反应出输出和输入的逻辑关系,同时还计算了时间的延时信息,是与实际系统更接近的一

种仿真结果。不过,要注意的是,这个时间延时是仿真软件“估算”出来的。

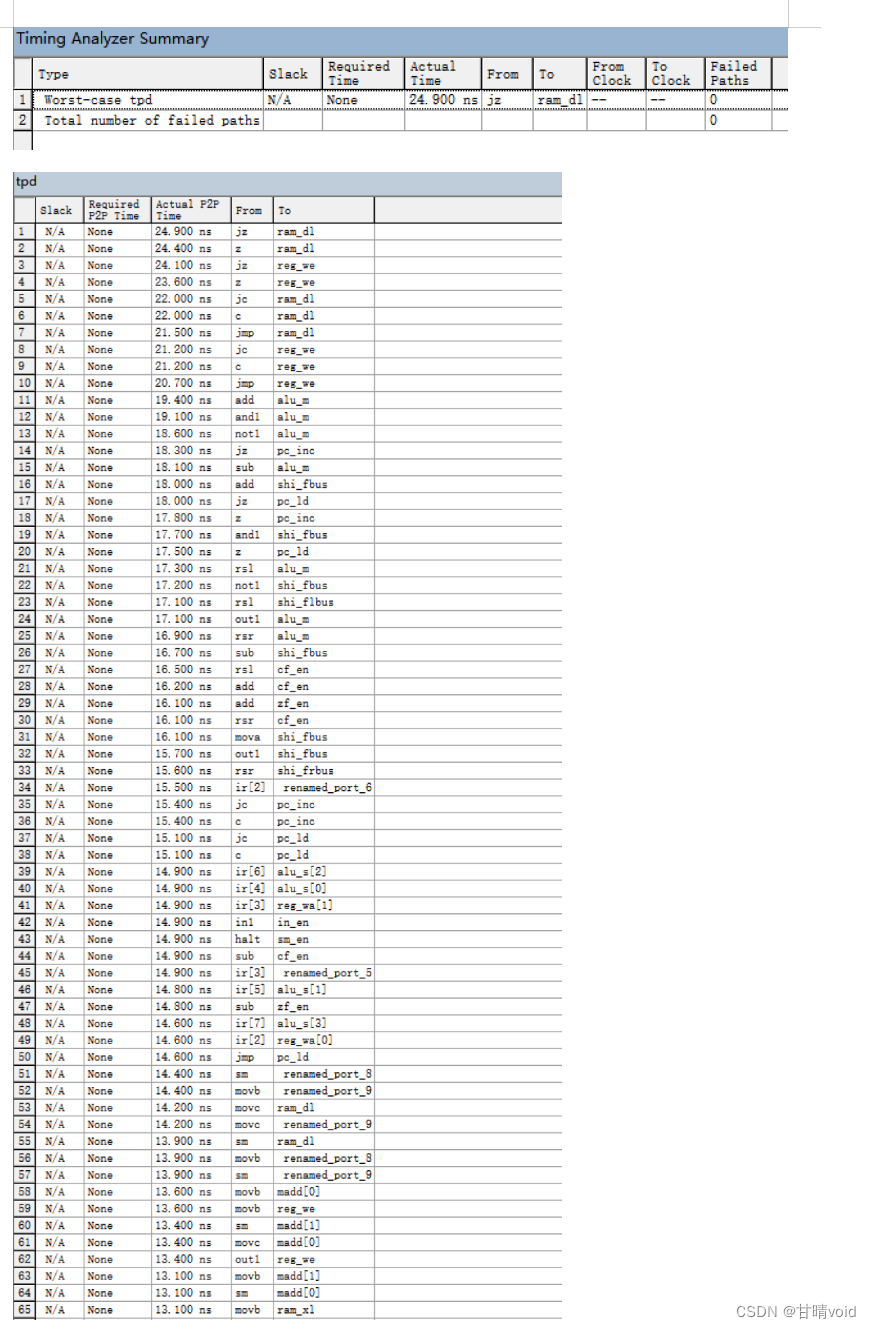

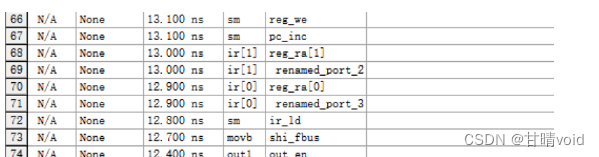

G) 时序分析

结果分析及结论:

分析:

由图可得,Timing Analyzer Summmary 总结所有经典定时分析的结果,并报告每个

定时特性的最坏情况定时。比如从 sub 到 reg_we 的最坏定时情况的 tpd 为 26.600ns。下面 的 tpd 报告表则给出了源节点和目标节点之间的 tpd 延迟时间,比如第二行中 and1 到

reg_we 的 tpd 为 26.300ns。

结论:

实际连接图中个元器件连接之间是存在时间延迟的,而且不同的元器件之间的时间延

迟也不相同。

四、思考题

1.移位逻辑不工作时,输出应该为何值?为什么?

答:输出应成高阻,防止数据通路发生冲突,产生主线竞争。

2.移位逻辑的输出Cf应该如何处理?

答:

当fbus=1,frbus=0,flbus=0,不执行移位操作,输出等于输入,cf 不改变;当fbus=0,frbus=1,flbus=0,执行右移,输出等于输入右移移位,有进位的话cf为1;

当fbus=0,frbus=0,flbus=1,执行左移,输出等于输入左移一位,cf 不改变

当控制信号全为 0 时,输出为高阻态;

3.如何产生正确的控制信号以及具体的编程实现?

答:应当逐个分析每个控制信号在不同的指令下对应的状态,利用逻辑函数进行状态的总和。

五、实验总结、必得体会及建议

1、从需要掌握的理论、遇到的困难、解决的办法以及经验教训等方面进行总结。

(1)需要掌握的理论:基本了解了简易模型机的内部结构和工作原理。同时熟悉了选择器,移位逻辑,控制器的工作原理。学会 使用 Verilog 语言编写电路。

(2)遇到的困难:对于 QuartusII 的使用还不够熟练,特别是进行波形仿真的功能仿真和时许仿真分别怎么操作的方面有一定不足。

(3)解决方法:通过上网查询相关资料和询问同学后得以解决问题,并通过分析报告发现电路中的问题。有不理解的还请教了老师,不仅收获了方法还掌握的技巧。

(4)经验教训:对于电子电路的学习一定要肯动手,光是看是学不会的,一定要落到实处,多自己使用软件进行仿真,才能加深对于这门课程的理解。

2、对本实验内容、过程和方法的改进建议(可选项)。

控制器各个控制信号的输出功能表十分重要,可以先引导同学们列出这个对应表。

相关文章:

HNU-电路与电子学-实验3

实验三 模型机组合部件的实现(二)(实验报告格式案例) 班级 计XXXXX 姓名 wolf 学号 2021080XXXXX 一、实验目的 1.了解简易模型机的内部结构和工作原理。 2.分析模型机的功能&am…...

Hadoop MapReduce各阶段执行过程以及Python代码实现简单的WordCount程序

视频资料:黑马程序员大数据Hadoop入门视频教程,适合零基础自学的大数据Hadoop教程 文章目录Map阶段执行过程Reduce阶段执行过程Python代码实现MapReduce的WordCount实例mapper.pyreducer.py在Hadoop HDFS文件系统中运行Map阶段执行过程 把输入目录下文件…...

GitLab CI/CD 新书发布,助企业降本增效

前言 大家好,我是CSDN的拿我格子衫来, 昨天我的第一本书《GitLab CI/CD 从入门到实战》上架啦,这是业内第一本详细讲解GitLab CI/CD的书籍。 历经无数个日夜,最终开花结果。感触良多,今天就借这篇文章来谈一谈这本书的…...

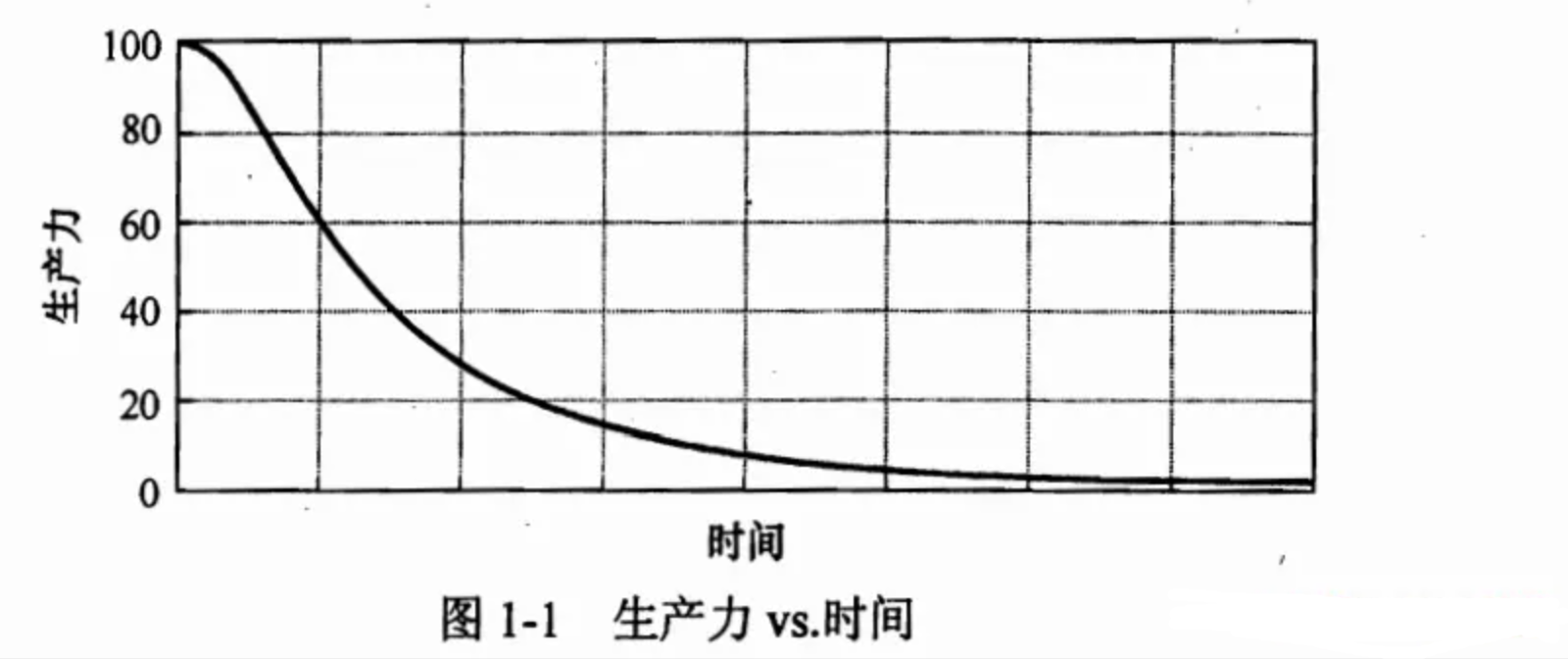

【分享】如何写出整洁的代码?

文章目录前言1.为什么要保持代码整洁?1.1 所以从一开始就要保持整洁1.2 如何写出整洁的代码?2.命名3.类3.1单一职责3.2 开闭原则3.3 内聚4.函数4.1 只做一件事4.2 函数命名4.3 参数4.4 返回值4.5 怎样写出这样的函数?4.6 代码质量扫描工具5.测试5.1 TDD5.2 FIRST原则5.3 测试…...

视频剪辑:教你如何调整视频画面的大小。

大家应该都会调整图片的大小吧,那你们会调整视频画面的大小吗?我想,应该会有人不还不知道要调整的吧,今天就让小编来教大家一个方法怎样去调整视频画面的大小尺寸。 首先,我们要有以下材料: 一台电脑 【…...

操作系统概述

Overview Q1(Why):为什么要学操作系统?Q2(What):到底什么是操作系统?Q3(How):怎么学操作系统? 一.为什么要学操作系统? 学习操作系统…...

记录重启csdn

有太多收藏的链接落灰了,在此重启~ 1、社会 https://mp.weixin.qq.com/s/Uq0koAbMUk8OFZg2nCg_fg https://mp.weixin.qq.com/s/yCtLdEWSKVVAKhvLHxjeig https://zhuanlan.zhihu.com/p/569162335?utm_mediumsocial&utm_oi938179755602853888&ut…...

蓝牙耳机哪个品牌质量最好最耐用?蓝牙耳机排行榜10强推荐

现今,外出佩戴蓝牙耳机的人越来越多,各大品牌厂商对于蓝牙耳机各种性能的设计也愈发用心。那么,无线耳机哪个品牌音质好?下面,我来给大家推荐几款质量好的无线蓝牙耳机,可以当个参考。 一.南卡…...

mysql 双主架构详解

文章目录 一、背景二、MySQL双主(主主)架构方案三、MySQL双主架构图四、MySQL双主架构的优缺点五、MySQL双主架构,会存在什么问题?总结一、背景 MySQL 主从模式优缺点 容灾:主数据库宕机后,启动从数据库,用于故障切换 备份:防止数据丢失 读写分离:主数据库可以只负责…...

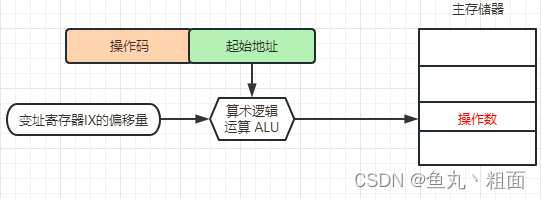

计算机指令系统基础 - 寻址方式详解

文章目录1 概述2 常见寻址方式2.1 立即寻址2.2 直接寻址2.3 间接寻址2.4 寄存器寻址2.5 寄存器间接寻址2.6 相对寻址2.7 变址寻址3 扩展3.1 操作码3.2 常见寄存器1 概述 计算机指令:指挥计算机工作的 指示 和 命令内容:通常一条 指令 包括两方面的内容 …...

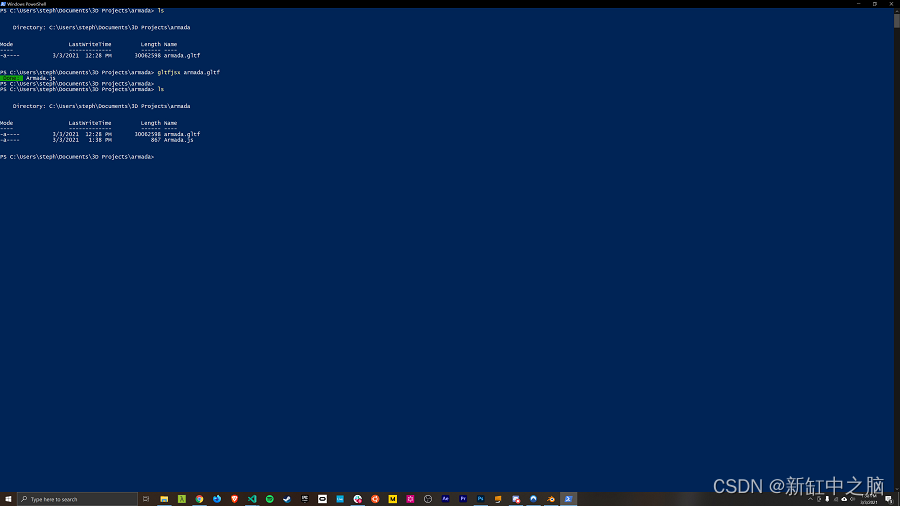

React Three Fiber动画入门

使用静态对象和形状构建 3D 场景非常酷,但是当你可以使用动画使场景栩栩如生时,它会更酷。 在 3D 世界中,有一个称为角色装配的过程,它允许你创建称为骨架的特殊对象,其作用类似于骨骼和关节系统。 这些骨架连接到一块…...

为什么我推荐你使用 systemd timer 替代 cronjob?

概述 前几天在使用 Terraform cloud-init 批量初始化我的实验室 Linux 机器。正好发现有一些定时场景需要使用到 cronjob, 进一步了解到 systemd timer 完全可以替换 cronjob, 并且 systemd timer 有一些非常有趣的功能。 回归话题:为什么我推荐你使用 systemd t…...

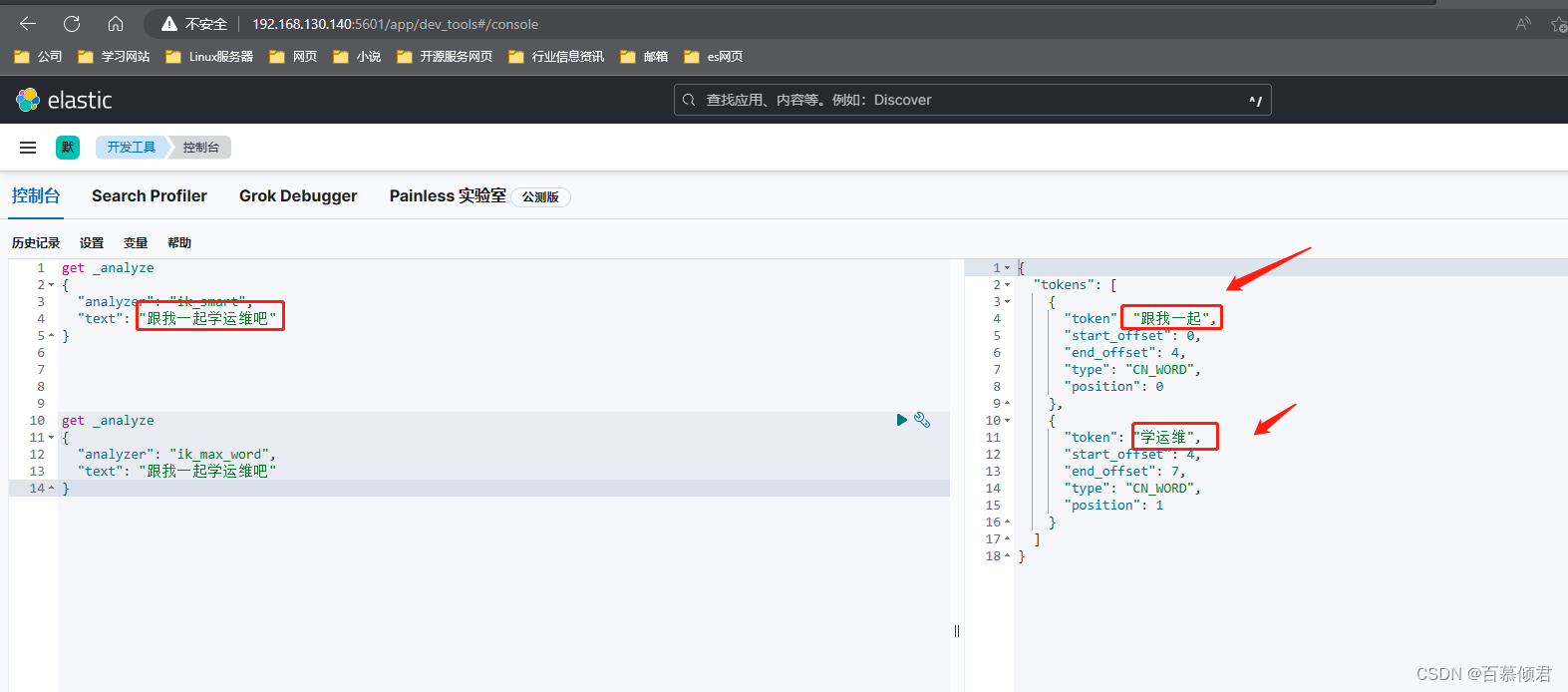

elasticsearch基础6——head插件安装和web页面查询操作使用、ik分词器

文章目录一、基本了解1.1 插件分类1.2 插件管理命令二、分析插件2.1 es中的分析插件2.1.1 官方核心分析插件2.1.2 社区提供分析插件2.2 API扩展插件三、Head 插件3.1 安装3.2 web页面使用3.2.1 概览页3.2.1.1 unassigned问题解决3.2.2 索引页3.2.3 数据浏览页3.2.4 基本查询页3…...

【Linux】七、进程间通信(二)

目录 三、system V(IPC) 3.1 system V共享内存 3.1.1 共享内存的概念 3.1.2 共享内存的原理 3.1.3 创建共享内存(shmget ) 3.1.4 ftok函数 3.1.5 查看共享内存资源 3.1.6 创建共享内存测试代码 3.1.7 再次理解共享内存 3.1.8 释放共享内存(shm…...

Synchronized学习大总结

目录 1.synchronized特性 2.synchronized如何使用 3.synchronized的锁机制 1.synchronized特性 synchronized 是乐观锁,也是悲观锁,是轻量级锁(j基于自旋锁实现),也是重量级锁(基于挂起等待锁实现),它不是读写锁,是互斥锁,当一个线程抢到锁之后,其它线程阻塞等待,进入synchr…...

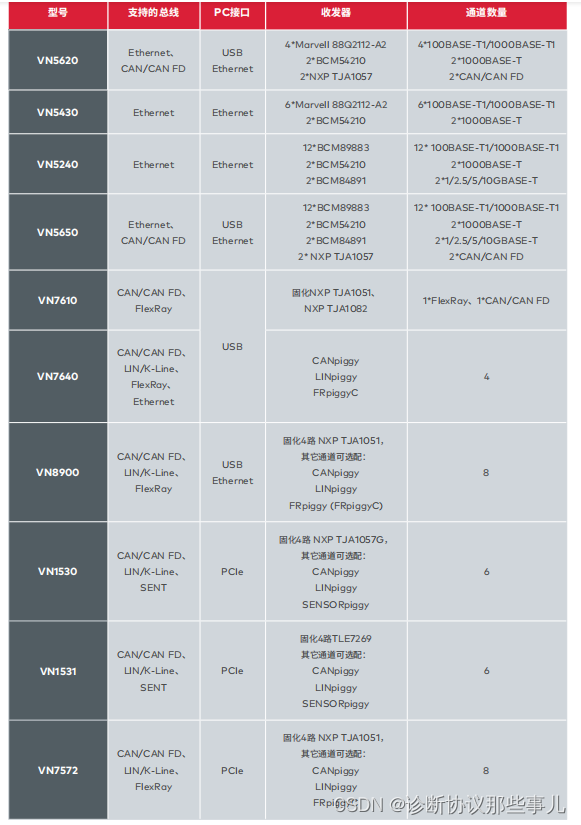

VN5620以太网测试——环境搭建篇

文章目录 前言一、新建以太网工程二、Port Configuration三、Link up四 Trace界面五、添加Ethernet Packet Builder六、添加ARP Packet七、添加Ethernet IG总结前言 CANoe(CAN open environment)VN5620 :是一个紧凑而强大的接口,用于以太网网络的分析、仿真、测试和验证。 …...

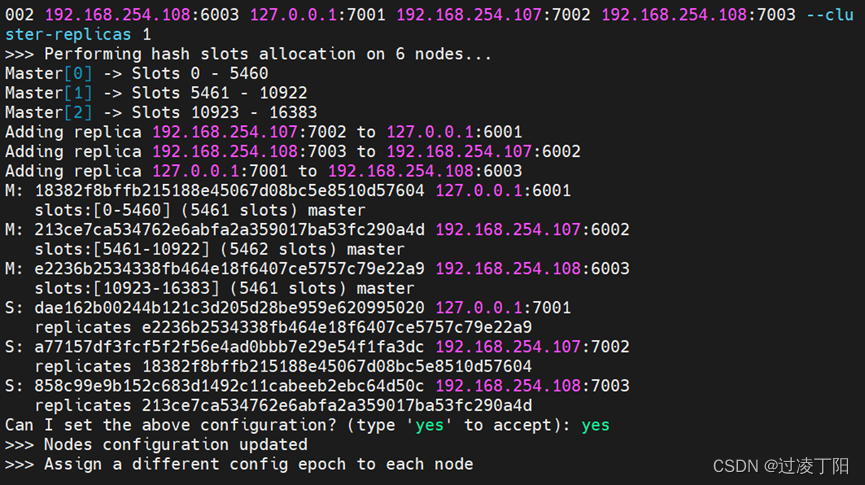

redis哨兵和集群部署手册

一、哨兵模式原理及作用 1.原理 哨兵(sentinel): 是一个分布式系统,用于对主从结构中的每台服务器进行监控,当出现 故障时,通过投票机制选择新的master并将所有slave连接到新的master。所以整个运行哨兵的集…...

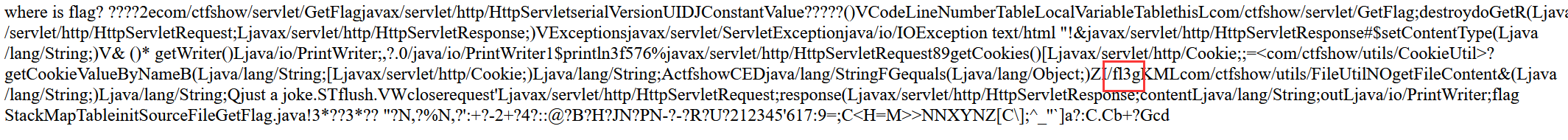

ctfshow web入门 java 295 298-300

其他没啥好讲的,都是工具就通杀了 web295 漏洞地址 http://ip/S2-048/integration/saveGangster.action 这里我们可以看到他是解析了 尝试使用网上的payload %{(#dmognl.OgnlContextDEFAULT_MEMBER_ACCESS).(#_memberAccess?(#_memberAccess#dm):((#container#cont…...

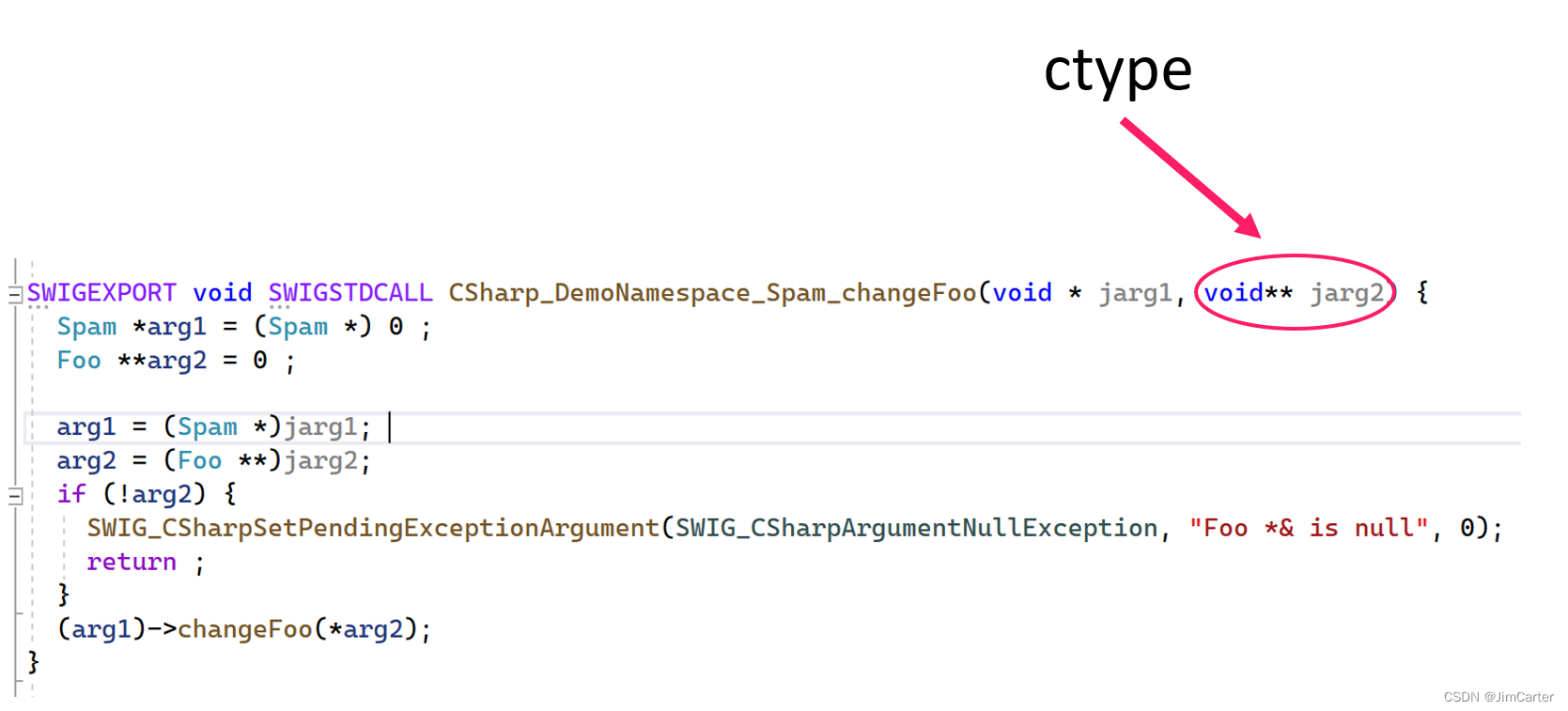

SWIG包装器使用指南——(四)C#使用SWIG简介与实践

SWIG系列:http://t.csdn.cn/cIAcr 文章目录一、简介二、全局函数、变量、常量三、继承四、传递指针、引用、数组与值五、基本类型的指针与引用六、基本类型的数组七、基本类型的默认map规则八、常用的typemap方法九、代码插入十、实践10.1 如何映射Foo*&到ref F…...

HashTable, HashMap 和 ConcurrentHashMap

HashTable, HashMap 和 ConcurrentHashMap 都是 Java 集合框架中的类,用于存储和操作键值对。它们之间存在一些关键区别,如下所示: 1.同步性: HashTable:线程安全,所有的方法都是同步的(synchr…...

Go HTTP Server 性能分析与优化

Go HTTP Server 性能分析与优化 在当今高并发的互联网应用中,HTTP Server的性能直接决定了用户体验和系统稳定性。Go语言凭借其轻量级协程和高效的网络库,成为构建高性能HTTP服务的首选之一。即使使用Go,开发者仍需深入分析性能瓶颈并进行针…...

all-MiniLM-L6-v2问题修复:相似度计算与维度匹配错误处理

all-MiniLM-L6-v2问题修复:相似度计算与维度匹配错误处理 1. 问题概述 all-MiniLM-L6-v2作为轻量级句子嵌入模型,在实际应用中常遇到两类核心问题: 相似度计算异常:结果超出[-1,1]范围或明显不符合语义维度匹配错误:…...

SenseVoice-small语音识别实战案例:教育行业课堂录音自动字幕生成

SenseVoice-small语音识别实战案例:教育行业课堂录音自动字幕生成 1. 项目背景与需求场景 在教育信息化快速发展的今天,越来越多的课堂内容被录制下来用于学生复习、教师培训和质量评估。然而,海量的课堂录音面临着转写效率低、成本高、多语…...

零基础玩转像素幻梦:快速生成《光纹苔藓姑苏幻梦》同款像素画

零基础玩转像素幻梦:快速生成《光纹苔藓姑苏幻梦》同款像素画 1. 像素幻梦初体验 1.1 什么是像素幻梦创意工坊 像素幻梦创意工坊(Pixel Dream Workshop)是一款基于FLUX.1-dev扩散模型构建的AI像素艺术生成工具。它采用明亮的16-bit像素风格…...

解决抖音直播数据实时采集难题的全栈方案:DouyinLiveWebFetcher实战指南

解决抖音直播数据实时采集难题的全栈方案:DouyinLiveWebFetcher实战指南 【免费下载链接】DouyinLiveWebFetcher 抖音直播间网页版的弹幕数据抓取(2024最新版本) 项目地址: https://gitcode.com/gh_mirrors/do/DouyinLiveWebFetcher 副…...

经典游戏现代化:让魔兽争霸III重获新生的适配工具

经典游戏现代化:让魔兽争霸III重获新生的适配工具 【免费下载链接】WarcraftHelper Warcraft III Helper , support 1.20e, 1.24e, 1.26a, 1.27a, 1.27b 项目地址: https://gitcode.com/gh_mirrors/wa/WarcraftHelper 当你在4K显示器上启动魔兽争霸III时&…...

力扣994. 腐烂的橘子

题目:腐烂的橘子https://leetcode.cn/problems/rotting-oranges/description/在给定的 m x n 网格 grid 中,每个单元格可以有以下三个值之一: 0 代表空单元格;1 代表新鲜橘子;2 代表腐烂的橘子。 每分钟,腐…...

AI 模型推理引擎性能对比

AI模型推理引擎性能对比:如何选择最优方案 随着AI技术在各行业的广泛应用,模型推理引擎的性能成为影响落地效果的关键因素。不同的推理引擎在计算效率、资源占用、兼容性等方面表现各异,如何选择最适合的引擎成为开发者关注的焦点。本文将从…...

不只是改IP:群晖Docker版与套件版Gitea配置迁移与地址变更全攻略

群晖NAS上Gitea部署方案对比与地址变更深度指南 在私有云和代码托管领域,群晖NAS凭借其稳定的硬件性能和丰富的软件生态,成为许多开发者和技术团队搭建私有Git服务的首选平台。Gitea作为轻量级的自托管Git服务,因其简洁高效的特点,…...

)

iCalendar文件逆向解析:用Python拆解别人发你的会议邀请(附Outlook兼容性测试)

iCalendar文件逆向解析实战:Python拆解会议邀请的完整指南 收到会议邀请时,那个小小的.ics文件里藏着多少秘密?作为技术人员,我们常常需要从第三方日历文件中提取关键信息、分析重复规则,甚至修复跨时区协作中的时间错…...