FPGA_YOLO(四)用HLS实现循环展开以及存储模块

Vivado HLS(High-Level Synthesis,高层次综合)是赛灵思(Xilinx)在其 Vivado 设计套件 中提供的一款工具,用于将 高级编程语言(如 C、C++、SystemC) 直接转换为 硬件描述语言(HDL,如 VHDL 或 Verilog),从而快速生成可编程逻辑(如 FPGA 或 SoC)的硬件电路设计。

HLS 的核心作用

传统的硬件设计需手动编写 RTL(寄存器传输级)代码(如 Verilog/VHDL),而 HLS 允许开发者:

- 用更抽象的软件语言描述算法或功能。

- 自动生成优化的 RTL 代码,显著提升开发效率。

- 尤其适合算法密集型任务(如信号处理、图像处理、AI加速等)。

HLS 的主要功能与特点

-

支持高级语言

用 C/C++/SystemC 描述硬件行为,无需手动编写 HDL 代码。 -

自动化硬件优化

通过添加编译指令(如#pragma HLS),指导工具优化流水线、并行性、资源分配等。 -

仿真与验证

在软件层面验证功能正确性,减少后期硬件调试时间。 -

与 Vivado 无缝集成

生成的 RTL 可直接用于 Vivado 进行综合、布局布线,并生成比特流文件下载到 FPGA。 -

灵活生成 IP 核

输出为可重用的 IP 核,方便在更大系统中调用。

HLS 的典型应用场景

- 算法加速:将计算密集型算法(如矩阵运算、加密解密)硬件化,提升性能。

- 快速原型开发:软件工程师无需精通 HDL 即可参与 FPGA 开发。

- 异构计算:在 FPGA 上实现与 CPU/GPU 协同的定制加速模块。

- 复杂控制逻辑:简化状态机、接口协议(如 AXI)的开发。

HLS 的优势 vs 传统 RTL 开发

| 优势 | 说明 |

|---|---|

| 开发速度快 | 减少手动编码和调试时间。 |

| 易于维护 | 修改软件代码后重新综合即可。 |

| 跨平台复用 | C/C++ 代码可同时用于软件和硬件。 |

| 降低门槛 | 软件工程师也能参与硬件开发。 |

适用人群

- 需要硬件加速的算法工程师。

- 希望快速实现 FPGA 功能的开发团队。

- 希望减少 HDL 编码工作的硬件工程师。

一:(两个向量对应元素相加工程)

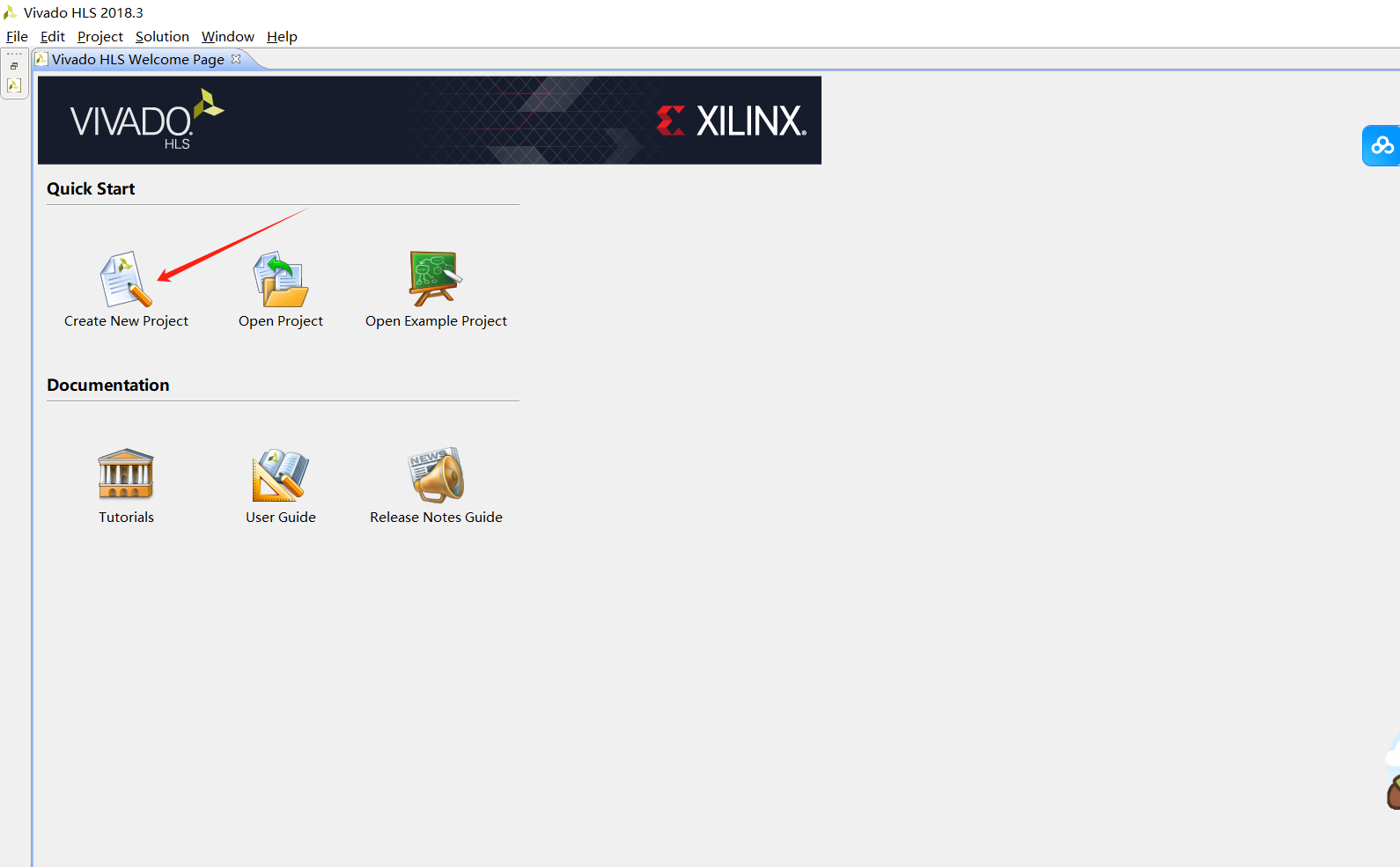

1:创建工程

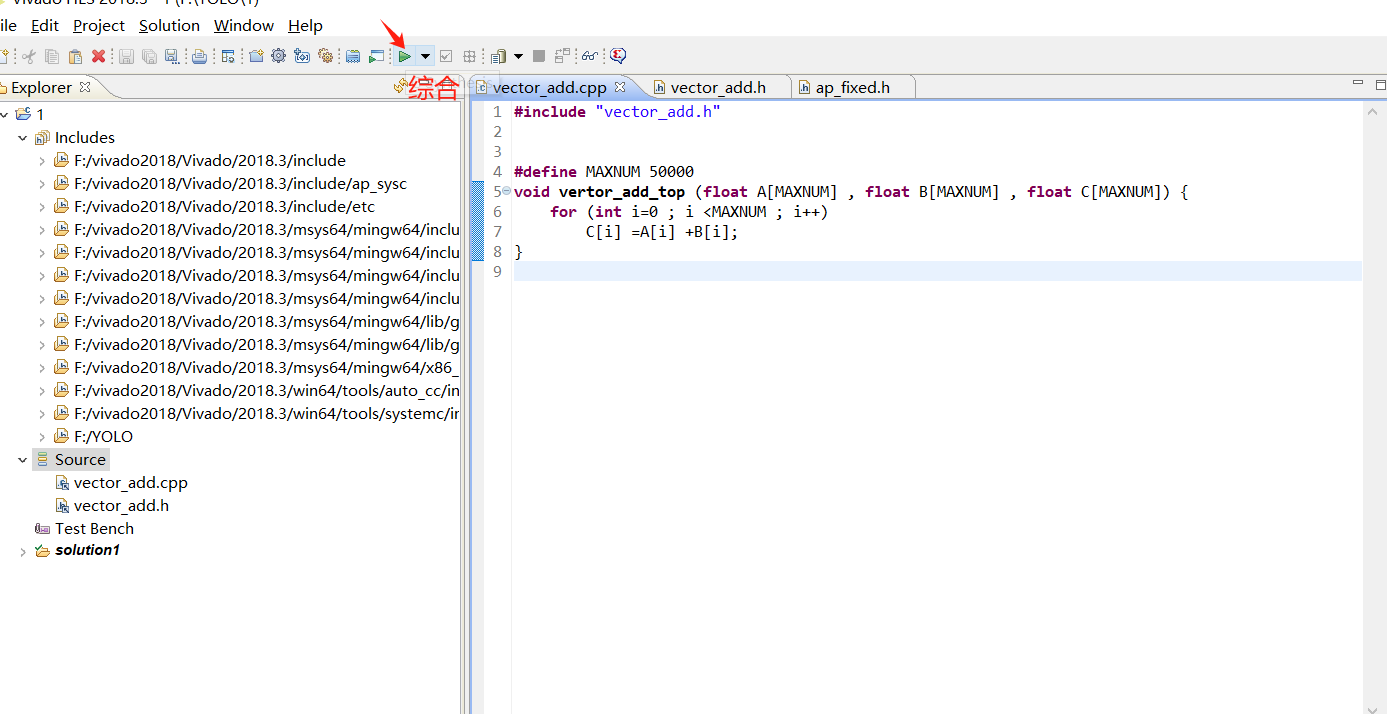

2 加法运算创建文本 写代码

点击综合 将c语言转化成verilog

加法运算代码如下

#include "vector_add.h"#define MAXNUM 50000 void vertor_add_top (float A[MAXNUM] , float B[MAXNUM] , float C[MAXNUM]) {for (int i=0 ; i <MAXNUM ; i++)C[i] =A[i] +B[i]; }

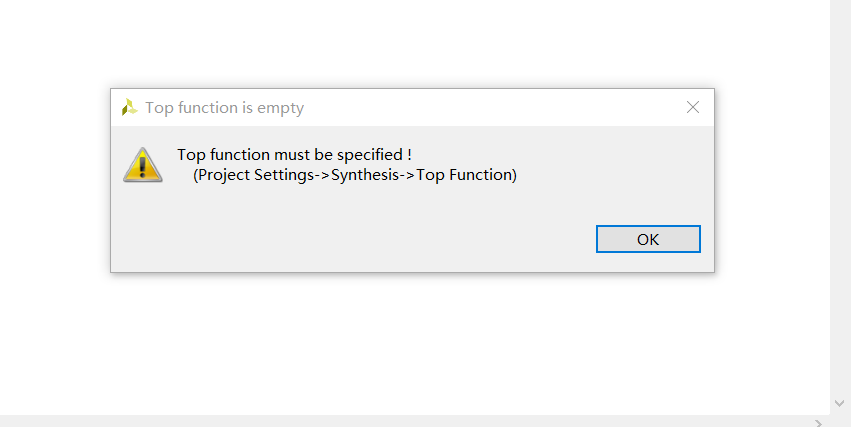

会报错

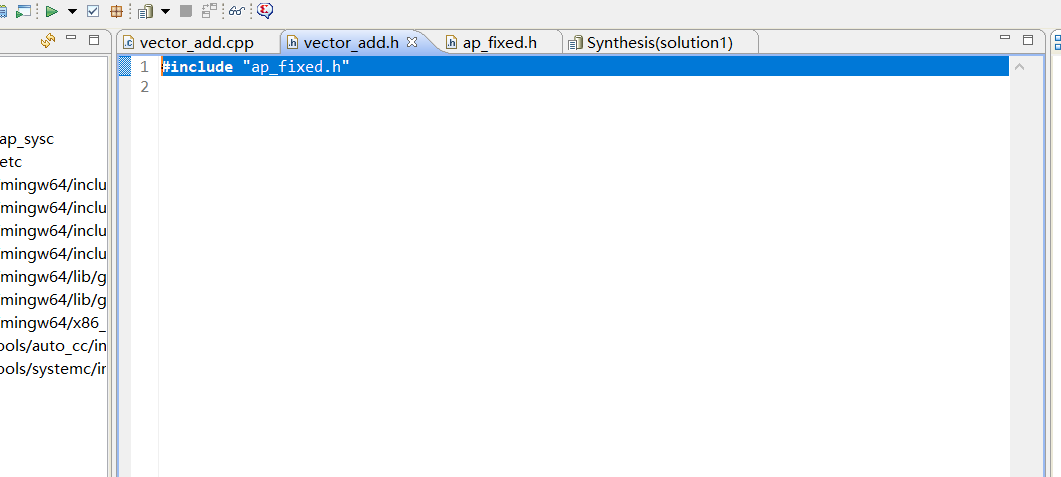

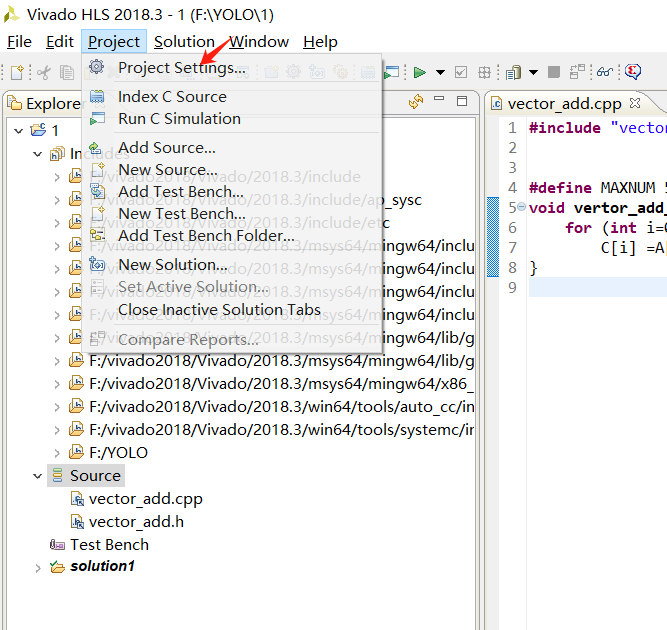

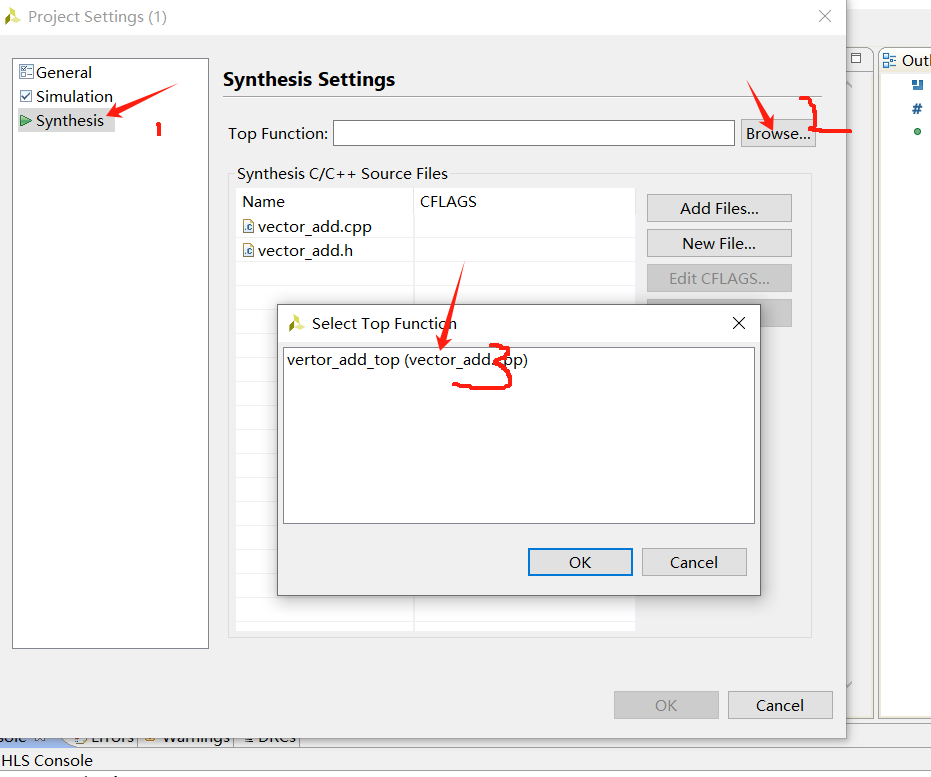

将文件设置为顶层

依次点击即可将刚刚写的设置为顶层

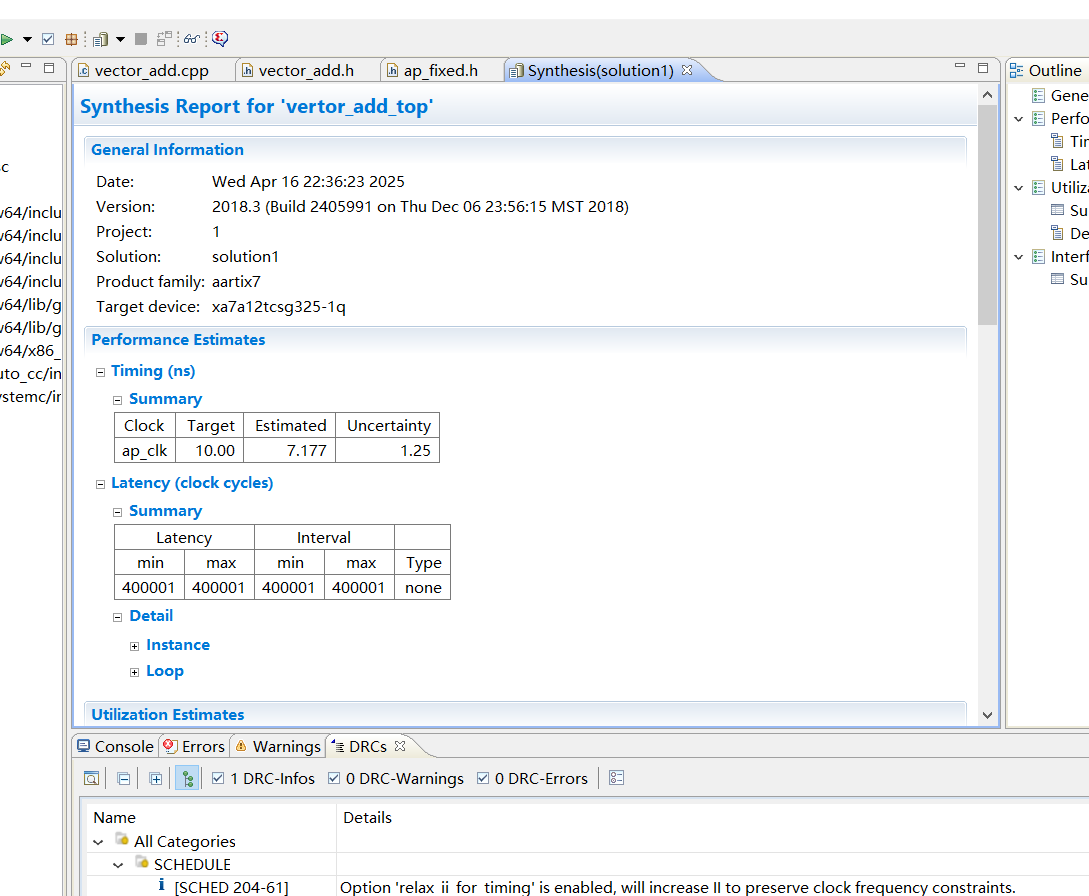

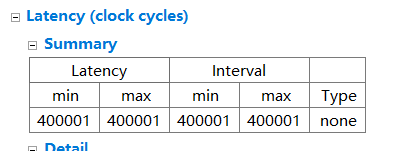

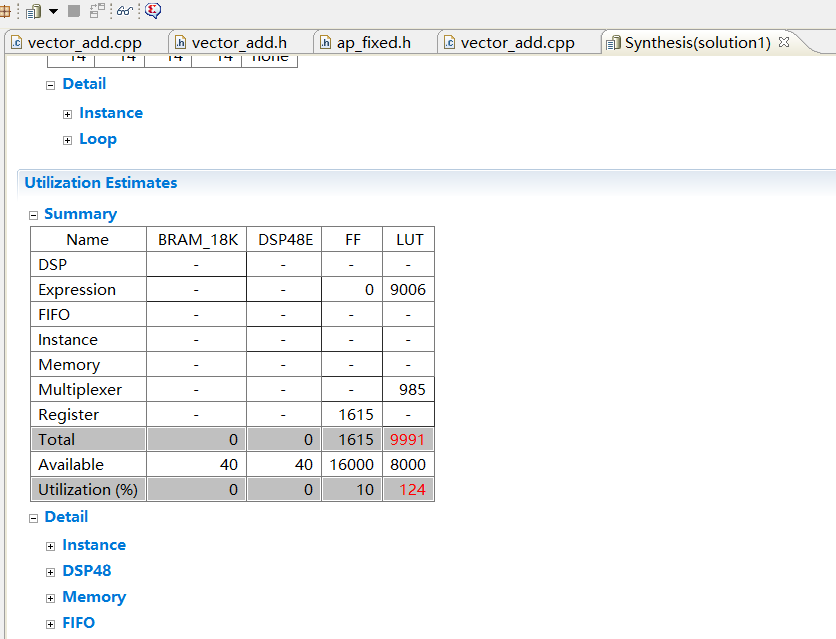

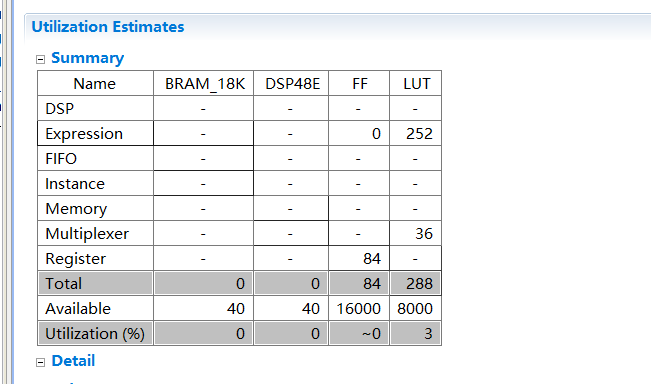

3:分析报告

如上图

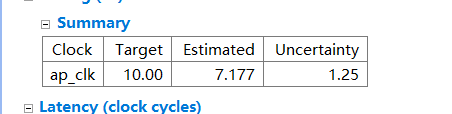

这依次是布局的时钟(我认为就是写代码然后映射verilog的时间),目标的时间10,预估的时间7.177ns

总的时间 从开始输入到输出的时间400001 代表多少个时钟周期,一个时钟周期7.177ns,400001*7.177/10^9 大约3ms能够计算完50000个浮点数相加。

下图是资源占用情况

3.1 DSP、LUT 和 FF是什么

在 FPGA/SoC 设计中,DSP、LUT 和 FF 是三种核心硬件资源的缩写,它们直接影响设计的性能、功耗和资源占用率。以下是它们的定义和作用:

1. DSP(Digital Signal Processor,数字信号处理器块)

-

用途:

专为高效执行 数学运算(乘法、乘累加、浮点运算等) 设计的硬件模块。

适用于信号处理、滤波器、AI加速、矩阵运算等场景。 -

特点:

- 高并行性:单时钟周期完成乘法或乘累加(MAC)。

- 低延迟:比用 LUT/FF 手动搭建等效电路更快更省资源。

-

示例:

实现C = A * B + C的乘累加操作时,优先占用 DSP 资源,而非 LUT/FF。 -

FPGA中的位置:

DSP 块通常以阵列形式分布在 FPGA 的逻辑单元中。

2. LUT(Look-Up Table,查找表)

-

用途:

FPGA 中最基础的 组合逻辑单元,用于实现任意逻辑函数。

相当于一个真值表,通过配置存储的值定义输入到输出的映射关系。 -

结构:

- 通常为 4~6 输入、1 输出的可编程查找表(如 Xilinx 的 6 输入 LUT)。

- 可分割为更小的 LUT 以实现更复杂的逻辑。

-

特点:

- 灵活性高:可配置为实现与、或、非等逻辑功能。

- 资源敏感:复杂逻辑会消耗大量 LUT,可能制约整体设计规模。

-

示例:

实现一个加法器时,除了进位链外,逻辑运算由 LUT 完成。

3. FF(Flip-Flop,触发器)

-

用途:

用于存储 时序逻辑的当前状态(1 比特数据)。

通过时钟信号同步更新数据,是设计 寄存器、状态机、流水线 的关键元件。 -

结构:

与 LUT 常绑定为 Slice(例如 Xilinx 的 CLB 每个 Slice 包含多个 LUT 和 FF)。

FF 包括触发条件(如上升沿/下降沿)和复位/置位功能。 -

特点:

- 时序控制:保证数据在时钟边沿稳定传输。

- 资源平衡:FF 的利用率直接影响时序收敛(如时钟频率)。

-

示例:

流水线架构中,每级流水线需要 FF 暂存中间结果。

4.三者的资源占用关系

-

算法决定资源分配

- 计算密集型任务(如矩阵乘法)会消耗大量 DSP。

- 复杂逻辑和条件判断依赖 LUT。

- 时序控制和数据缓冲需要 FF。

-

资源总量限制

FPGA 芯片中 DSP/LUT/FF 的数量是固定的,设计需确保不超过目标芯片的可用资源。

资源冲突会导致布局布线失败或降低时钟频率。 -

资源优化策略

优化手段 目的 使用 DSP 代替 LUT 实现运算 降低功耗,提升速度 逻辑简化(如状态机优化) 减少 LUT 和 FF 的消耗 流水线设计 平衡 FF 利用率与时钟频率 代码重构(HLS中) 避免生成冗余逻辑

5.在 Vivado HLS 中的应用

-

DSP 的使用:

若代码中的循环或函数包含乘法/累加操作,HLS 会优先调用 DSP,也可通过#pragma HLS BIND_OP强制指定实现方式。 -

LUT 与 FF 的平衡:

HLS 会根据代码生成组合逻辑(LUT)和时序逻辑(FF),通过#pragma HLS PIPELINE或调节时钟频率优化两者的分配。 -

资源报告:

综合后查看资源利用率报告,分析是否需重构代码或调整约束。

6.总结

- DSP 是高性能运算的“加速引擎”,用于数学密集型任务。

- LUT 是实现灵活逻辑的基础单元,但易成为性能瓶颈。

- FF 是时序逻辑的基石,影响设计的时钟频率和稳定性。

合理规划和优化这三者的使用,是 FPGA 设计的关键!

4.修改数据的类型

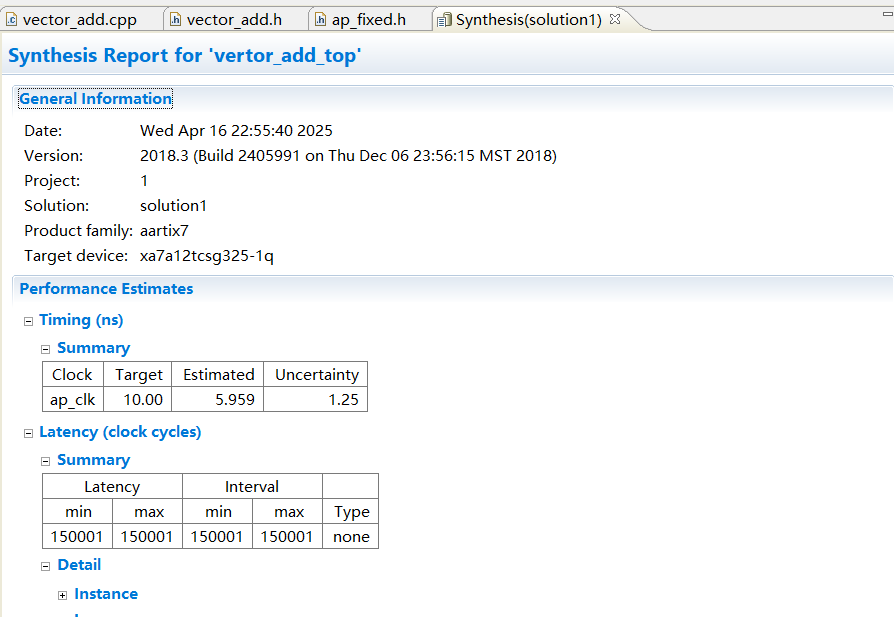

4.1 将float 改为 int

代码如下将float 改为 int

#include "vector_add.h"#define MAXNUM 50000

void vertor_add_top (int A[MAXNUM] , int B[MAXNUM] , int C[MAXNUM]) {for (int i=0 ; i <MAXNUM ; i++)C[i] =A[i] +B[i];

}下面是报告

根据上图可以计算总得时间连1ms都不到

4.2 将int改为自定义的定点型数据

代码如下:

#include "ap_fixed.h"typedef ap_fixed<32 , 16 , AP_RND,AP_SAT> D32;#include "vector_add.h"#define MAXNUM 50000

void vertor_add_top (D32 A[MAXNUM] , D32 B[MAXNUM] , D32 C[MAXNUM]) {for (int i=0 ; i <MAXNUM ; i++)C[i] =A[i] +B[i];

}

这里是 typedef ap_fixed<32 , 16 , AP_RND,AP_SAT> D32;

typedef是自定义类型 名字叫ap_fixed 总共有32为 16位的整数,剩下的AP_RND为小数部分,AP_SAT这个是溢出类型应该,归一。

分析报告

可以算出时间比int多,但是比float少

总结:根据上述实验可以知道,int和自定义的类型没有用到dsp 浮点数用到了dsp、时间dloat > d32>int

二(并行加速)

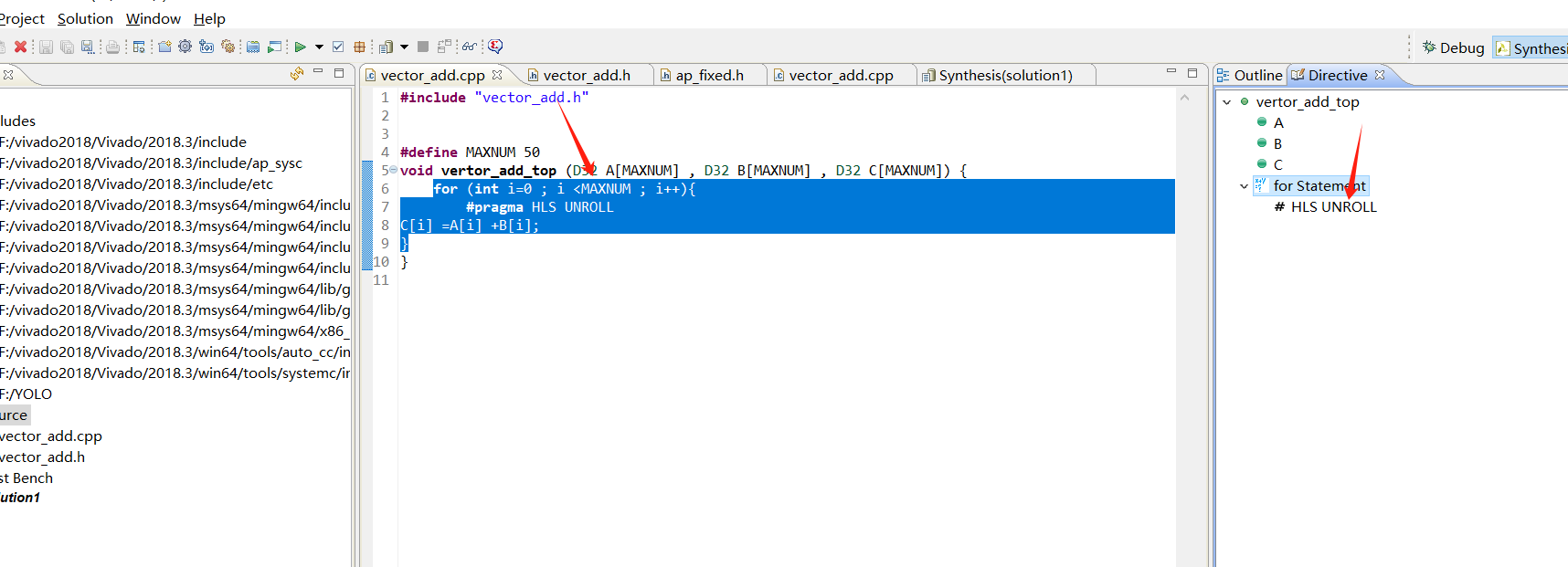

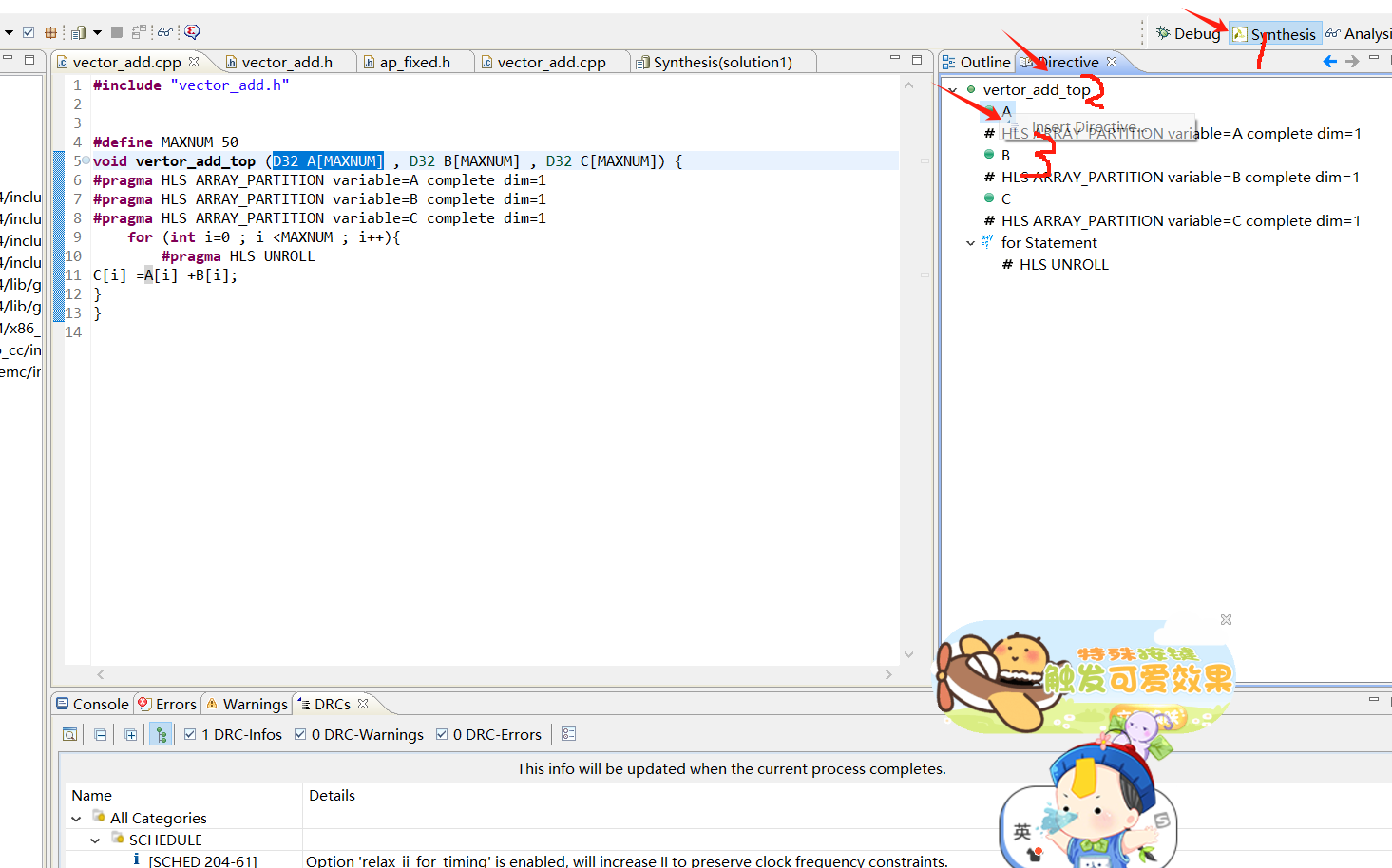

1代码unroll

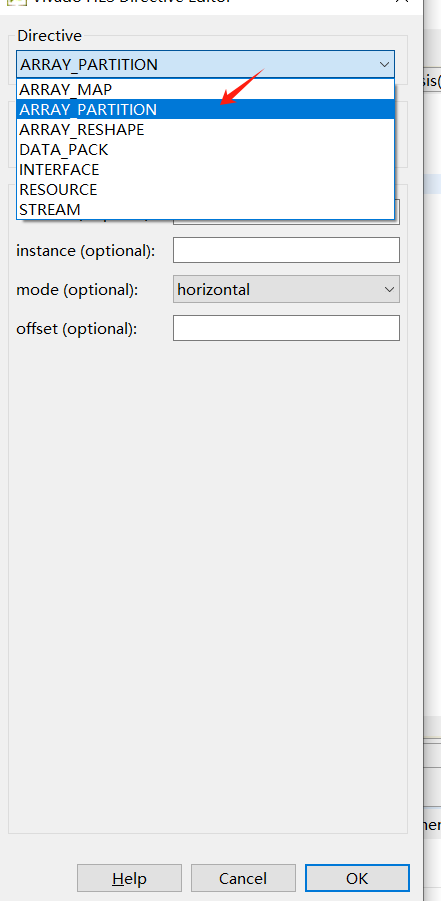

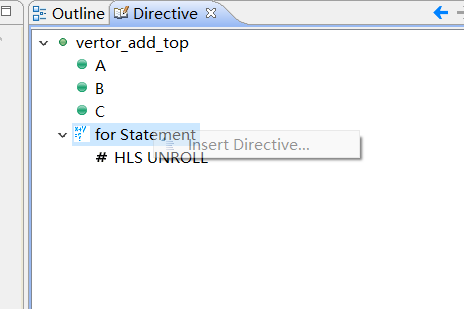

选中代码,然后点开右边的directive

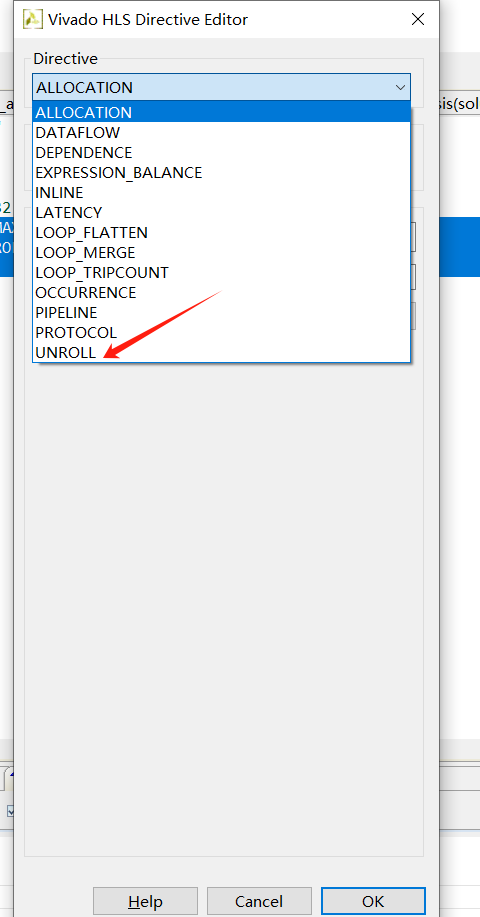

然后找到for statement 右击

选择 将并行插入到代码中点击ok

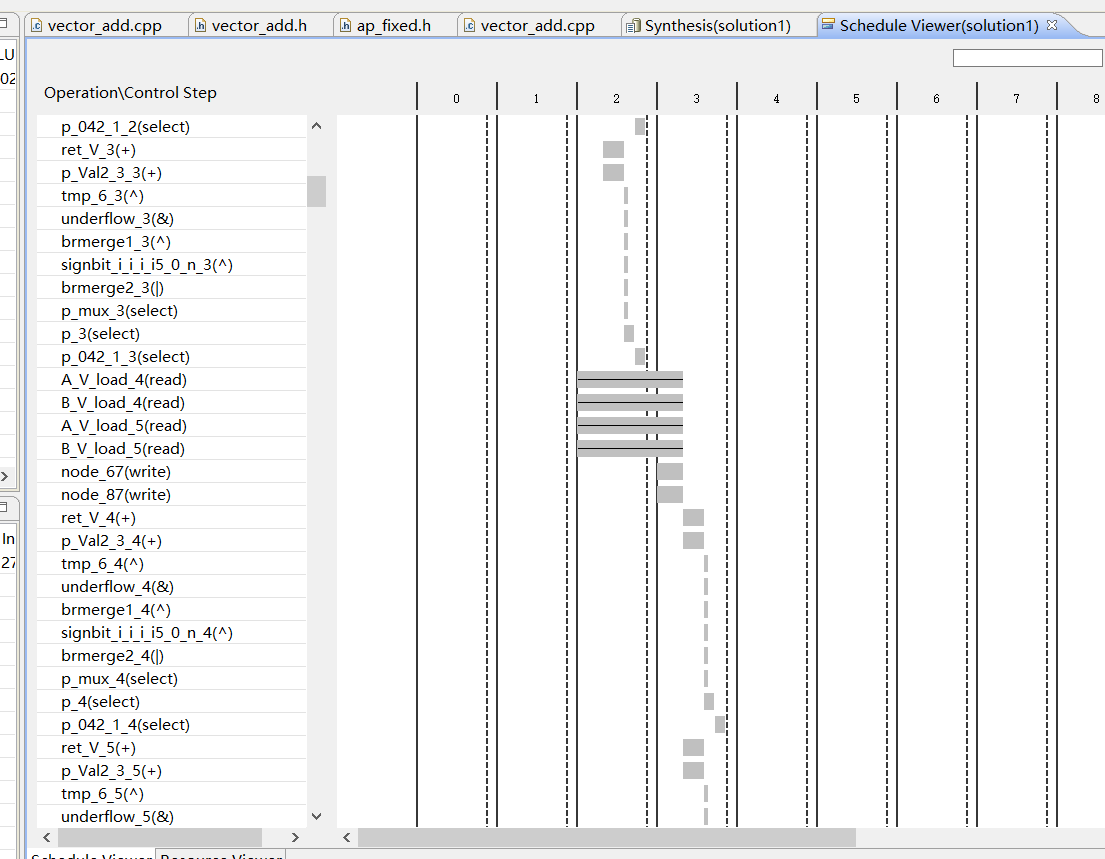

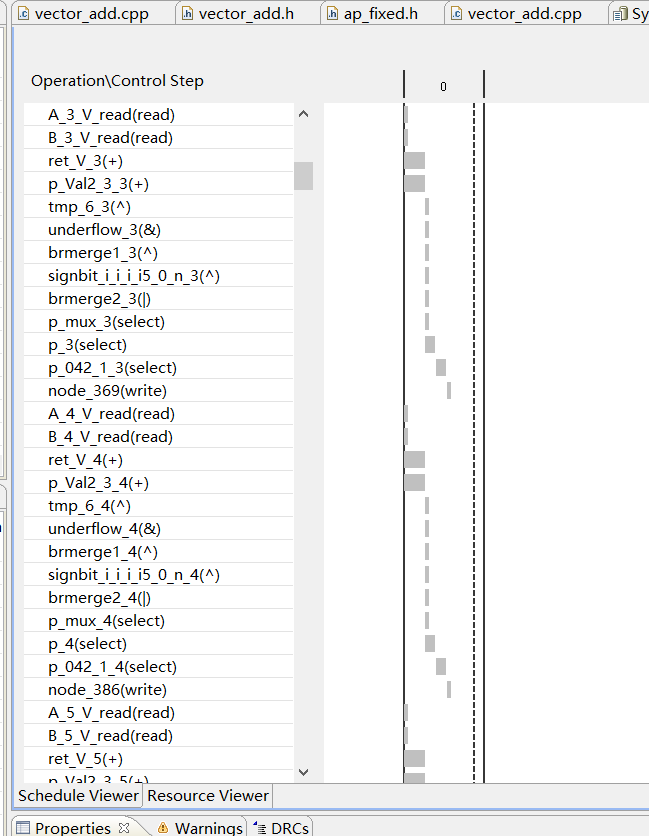

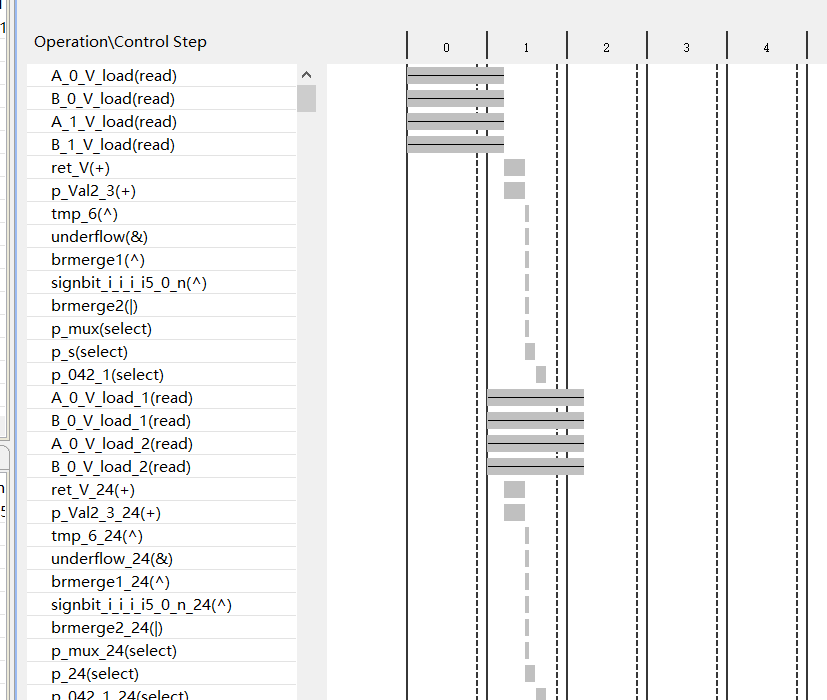

可以看到一部分并行一部分串行还是在串行

可以看到在read还是串行,应为ram 最大就是双端口,50个数很大所以得串行。

多了一个时钟周期

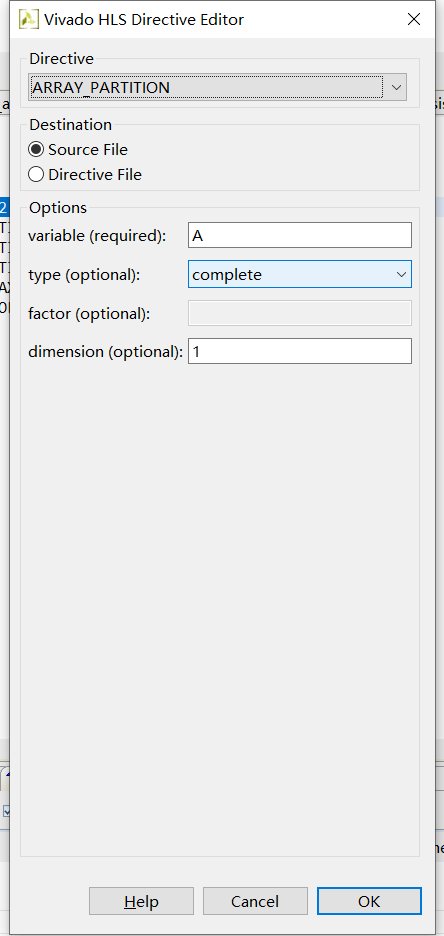

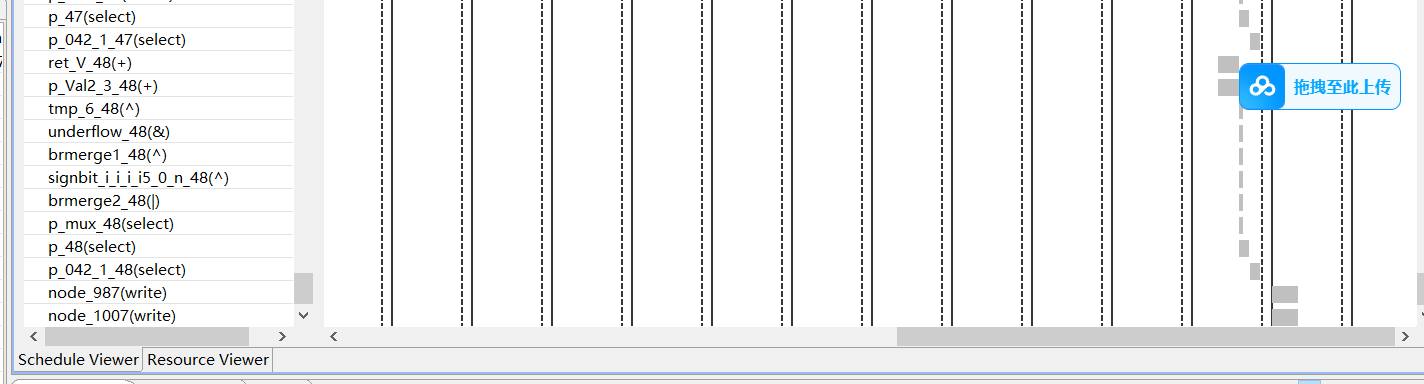

2整个完全展开 代码#pragma HLS ARRAY_PARTITION variable=A complete dim=1

完整代码如下

#include "vector_add.h"#define MAXNUM 50

void vertor_add_top (D32 A[MAXNUM] , D32 B[MAXNUM] , D32 C[MAXNUM]) {

#pragma HLS ARRAY_PARTITION variable=A complete dim=1

#pragma HLS ARRAY_PARTITION variable=B complete dim=1

#pragma HLS ARRAY_PARTITION variable=C complete dim=1for (int i=0 ; i <MAXNUM ; i++){#pragma HLS UNROLL

C[i] =A[i] +B[i];

}

}

操作:

如下找到ABC右击A

找到ARRAY_PARTITION函数 然后compelte是整体展开

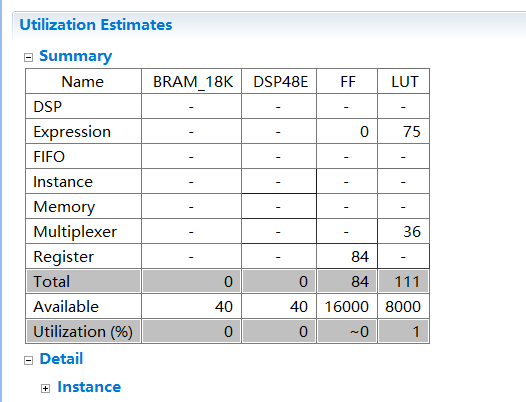

报告分析

我们可以看到只用了组合逻辑电路,其他的都没有用到

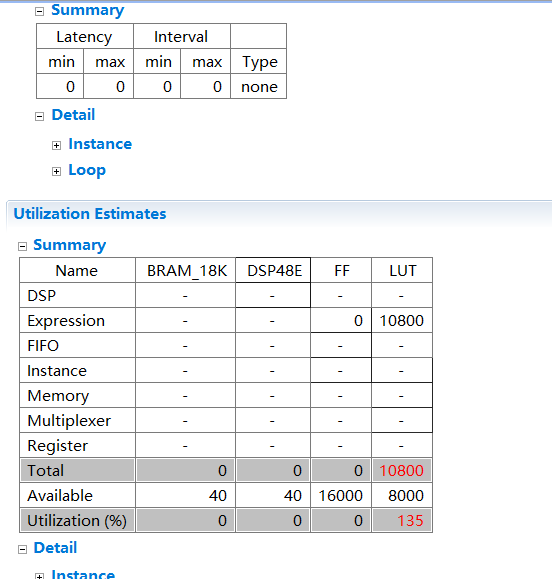

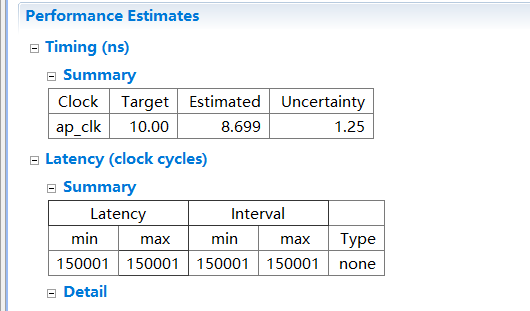

3.分块展开

#pragma HLS ARRAY_PARTITION variable=A block factor=2 dim=1

完整代码

#include "vector_add.h"#define MAXNUM 50 void vertor_add_top (D32 A[MAXNUM] , D32 B[MAXNUM] , D32 C[MAXNUM]) { #pragma HLS ARRAY_PARTITION variable=A block factor=2 dim=1 #pragma HLS ARRAY_PARTITION variable=B block factor=2 dim=1 #pragma HLS ARRAY_PARTITION variable=C block factor=2 dim=1for (int i=0 ; i <MAXNUM ; i++){#pragma HLS UNROLL C[i] =A[i] +B[i]; } }

选择block 分块因子为2

报告分析

并不是只用了组合逻辑

相关文章:

FPGA_YOLO(四)用HLS实现循环展开以及存储模块

Vivado HLS(High-Level Synthesis,高层次综合)是赛灵思(Xilinx)在其 Vivado 设计套件 中提供的一款工具,用于将 高级编程语言(如 C、C、SystemC) 直接转换为 硬件描述语言࿰…...

ASP.NET MVC 实现增删改查(CRUD)操作的完整示例

提供一个完整的 ASP.NET MVC 实现增删改查(CRUD)操作的示例。该示例使用 SQL Server 数据库,以一个简单的 Product 实体为例。 步骤 1:创建 ASP.NET MVC 项目 首先,在 Visual Studio 中创建一个新的 ASP.NET MVC 项目…...

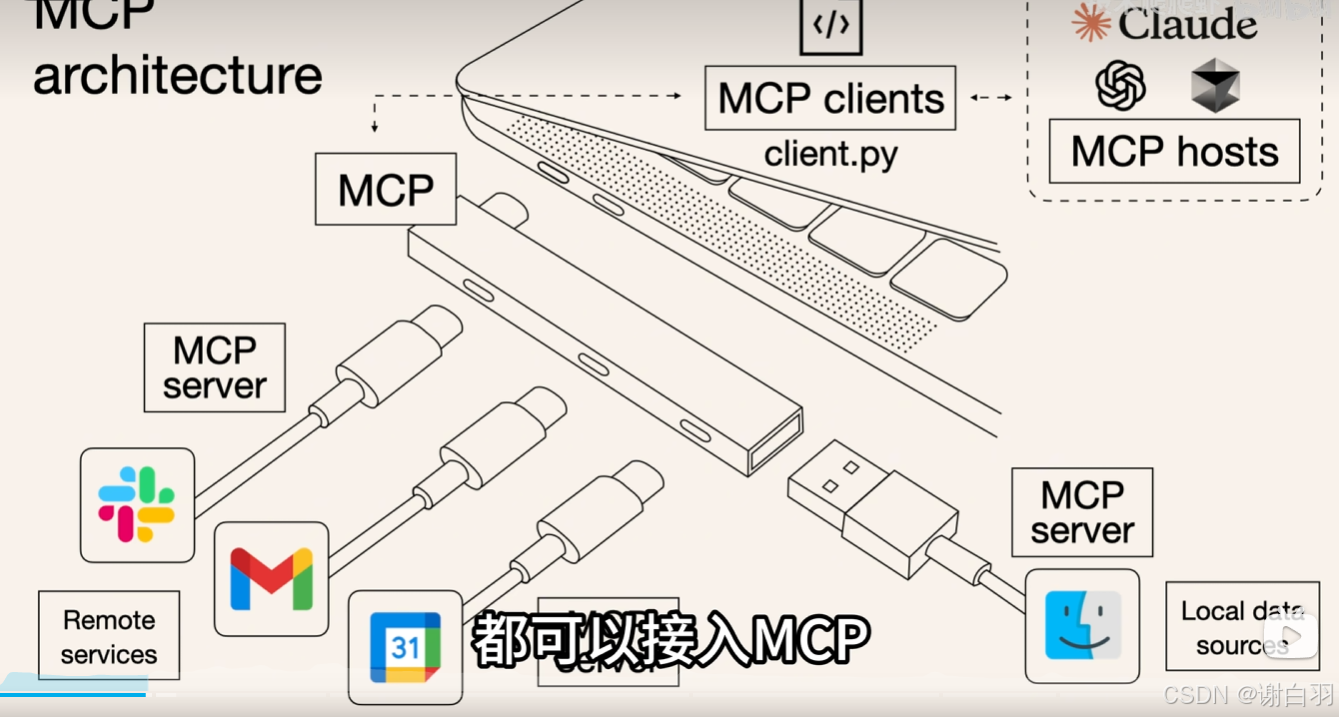

MCP理解笔记及deepseek使用MCP案例介绍

文章目录 一、MCP介绍(1)使用MCP与之前的AI比较(2)原理(3)优点 二、deepseek使用MCP使用案例介绍 一、MCP介绍 全称 模型上下文协议 来源 由Claude母公司Anthropic于24年底开源发布 简介 AI大模型的标准化…...

# 手写数字识别:使用PyTorch构建MNIST分类器

手写数字识别:使用PyTorch构建MNIST分类器 在这篇文章中,我将引导你通过使用PyTorch框架构建一个简单的神经网络模型,用于识别MNIST数据集中的手写数字。MNIST数据集是一个经典的机器学习数据集,包含了60,000张训练图像和10,000张…...

扩展虚拟机磁盘空间并使其在Linux系统中可用的步骤总结

VMware在虚拟机扩展空间时,若想扩展到150G,那么所在盘的空闲空间须大于150G,否则VM将不允许扩展。 1:确认新磁盘空间是否被识别 使用 lsblk 或 fdisk -l 命令检查 /dev/sda 的大小是否已经更新到新的容量(例如从原来的…...

A股周度复盘与下周策略 的deepseek提示词模板

以下是反向整理的股票大盘分析提示词模板,采用结构化框架数据占位符设计,可直接套用每周市场数据: 请根据一下markdown格式的模板,帮我检索整理并输出本周股市复盘和下周投资策略 【A股周度复盘与下周策略提示词模板】 一、市场…...

dev_set_drvdata、dev_get_drvdata使用详解

在Linux内核驱动开发中,dev_set_drvdata() 及相关函数用于管理设备驱动的私有数据,是模块化设计和数据隔离的核心工具。以下从函数定义、使用场景、示例及注意事项等方面进行详细解析: 一、函数定义与作用 核心函数 dev_set_drvdata() 和 dev…...

数据驱动未来:大数据在智能网联汽车中的深度应用

数据驱动未来:大数据在智能网联汽车中的深度应用 引言 随着智能网联汽车(Intelligent Connected Vehicles,ICV)的快速发展,数据已成为其核心驱动力。从实时交通数据到车辆传感器信息,大数据的深度应用正在让智能汽车更安全、更高效、更智能化。那么,大数据如何赋能智能…...

LeetCode:DFS综合练习

简单 1863. 找出所有子集的异或总和再求和 一个数组的 异或总和 定义为数组中所有元素按位 XOR 的结果;如果数组为 空 ,则异或总和为 0 。 例如,数组 [2,5,6] 的 异或总和 为 2 XOR 5 XOR 6 1 。 给你一个数组 nums ,请你求出 n…...

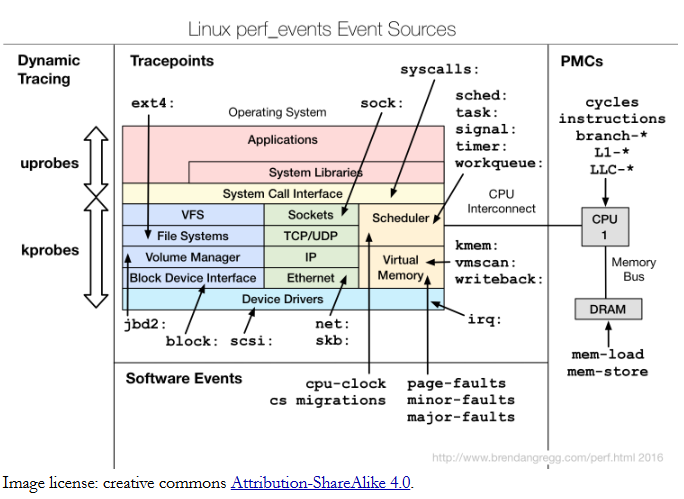

Perf学习

重要的能解决的问题是这些: perf_events is an event-oriented observability tool, which can help you solve advanced performance and troubleshooting functions. Questions that can be answered include: Why is the kernel on-CPU so much? What code-pa…...

齐次坐标变换+Unity矩阵变换

矩阵变换 变换(transform):指的是我们把一些数据,如点,方向向量甚至是颜色,通过某种方式(矩阵运算),进行转换的过程。 变换类型 线性变换:保留矢量加和标量乘的计算 f(x)…...

Pandas取代Excel?

有人在知乎上提问:为什么大公司不用pandas取代excel? 而且列出了几个理由:Pandas功能比Excel强大,运行速度更快,Excel除了简单和可视化界面外,没有其他更多的优势。 有个可怕的现实是,对比Exce…...

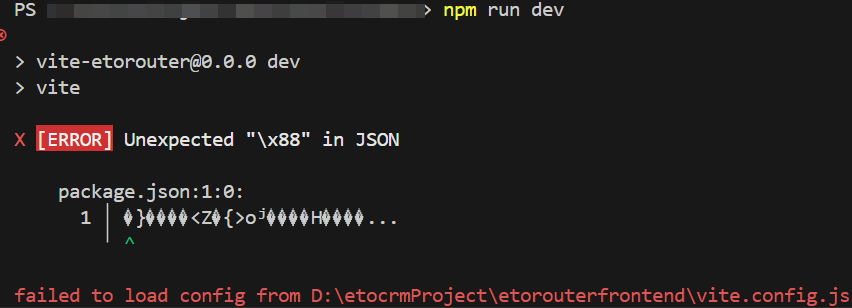

启动vite项目报Unexpected “\x88“ in JSON

启动vite项目报Unexpected “\x88” in JSON 通常是文件被防火墙加密需要寻找运维解决 重启重装npm install...

HTTP测试智能化升级:动态变量管理实战与效能跃迁

在Web应用、API接口测试等领域,测试场景的动态性和复杂性对测试数据的灵活管理提出了极高要求。传统的静态测试数据难以满足多用户并发、参数化请求及响应内容验证等需求。例如,在电商系统性能测试中,若无法动态生成用户ID、订单号或实时提取…...

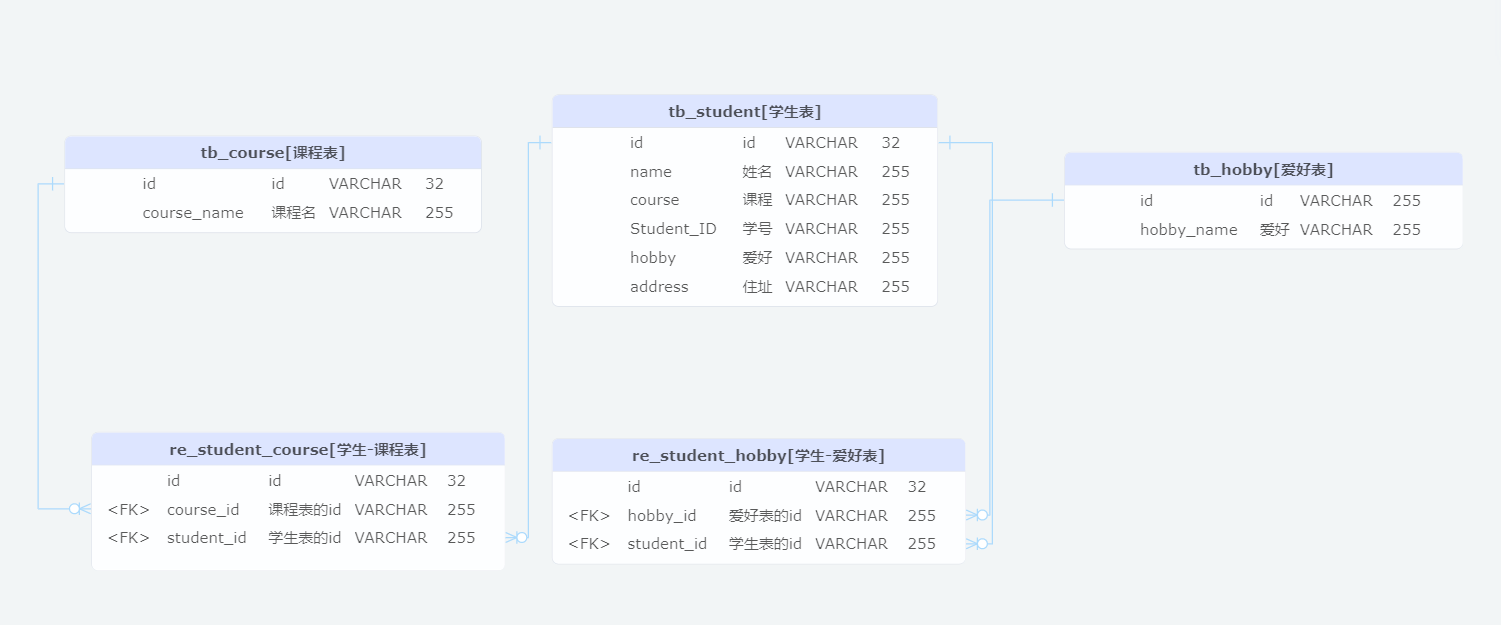

关于一对多关系(即E-R图中1:n)中的界面展示优化和数据库设计

前言 一对多,是常见的数据库关系。在界面设计时,有时为了方便,就展示成逗号分割的字符串。例如:学生和爱好的界面。 存储 如果是简单存储,建立数据库:爱好,课程,存在一张表中。 但…...

【gpt生成-总览】怎样才算开发了一门编程语言,需要通过什么测试

开发一门真正的编程语言需要经历完整的设计、实现和验证过程,并通过系统的测试体系验证其完备性。以下是分阶段开发标准及测试方法: 一、语言开发核心阶段 1. 语言规范设计(ISO/IEC 标准级别) 语法规范:BNF/…...

JVM笔记【一】java和Tomcat类加载机制

JVM笔记一java和Tomcat类加载机制 java和Tomcat类加载机制 Java类加载 * loadClass加载步骤类加载机制类加载器初始化过程双亲委派机制全盘负责委托机制类关系图自定义类加载器打破双亲委派机制 Tomcat类加载器 * 为了解决以上问题,tomcat是如何实现类加载机制的…...

React 组件类型详解:类组件 vs. 函数组件

React 是一个用于构建用户界面的 JavaScript 库,其核心思想是组件化开发。React 组件可以分为类组件(Class Components)和函数组件(Function Components),它们在设计理念、使用方式和适用场景上有所不同。随…...

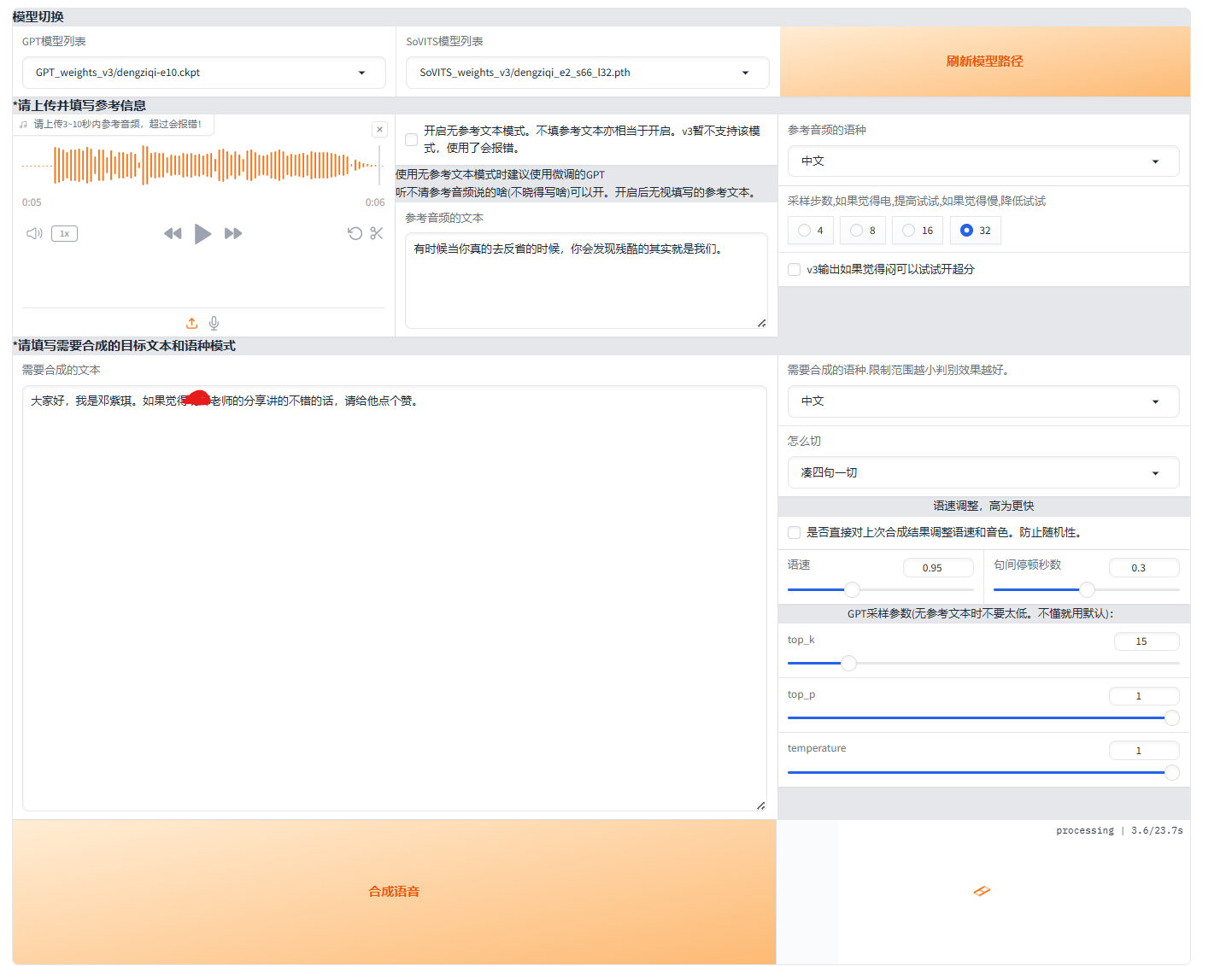

GPT-SoVITS 使用指南

一、简介 TTS(Text-to-Speech,文本转语音):是一种将文字转换为自然语音的技术,通过算法生成人类可听的语音输出,广泛应用于语音助手、无障碍服务、导航系统等场景。类似的还有SVC(歌声转换&…...

美信监控易:数据采集与整合的卓越之选

在当今复杂多变的运维环境中,一款具备强大数据采集与整合能力的运维管理软件对于企业的稳定运行和高效决策至关重要。美信监控易正是这样一款在数据采集与整合方面展现出显著优势的软件,以下是它的一些关键技术优势,值得每一个运维团队深入了…...

基于Redis的3种分布式ID生成策略

在分布式系统设计中,全局唯一ID是一个基础而关键的组件。随着业务规模扩大和系统架构向微服务演进,传统的单机自增ID已无法满足需求。高并发、高可用的分布式ID生成方案成为构建可靠分布式系统的必要条件。 Redis具备高性能、原子操作及简单易用的特性&…...

OCR技术与视觉模型技术的区别、应用及展望

在计算机视觉技术飞速发展的当下,OCR技术与视觉模型技术成为推动各行业智能化变革的重要力量。它们在原理、应用等方面存在诸多差异,在自动化测试领域也展现出不同的表现与潜力,下面将为你详细剖析。 一、技术区别 (一ÿ…...

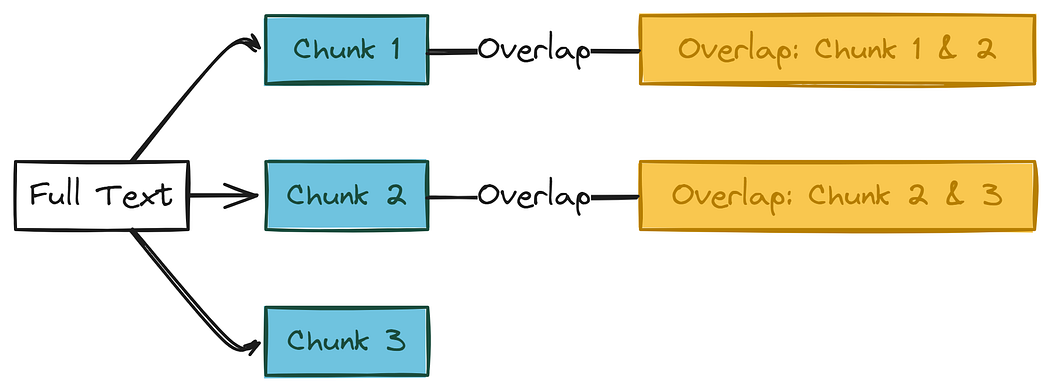

End-to-End从混沌到秩序:基于LLM的Pipeline将非结构化数据转化为知识图谱

摘要:本文介绍了一种将非结构化数据转换为知识图谱的端到端方法。通过使用大型语言模型(LLM)和一系列数据处理技术,我们能够从原始文本中自动提取结构化的知识。这一过程包括文本分块、LLM 提示设计、三元组提取、归一化与去重,最终利用 NetworkX 和 ipycytoscape 构建并可…...

)

比特币的跨输入签名聚合(Cross-Input Signature Aggregation,CISA)

1. 引言 2024 年,人权基金会(Human Rights Foundation,简称 HRF)启动了一项研究奖学金计划,旨在探讨“跨输入签名聚合”(Cross-Input Signature Aggregation,简称 CISA)的潜在影响。…...

)

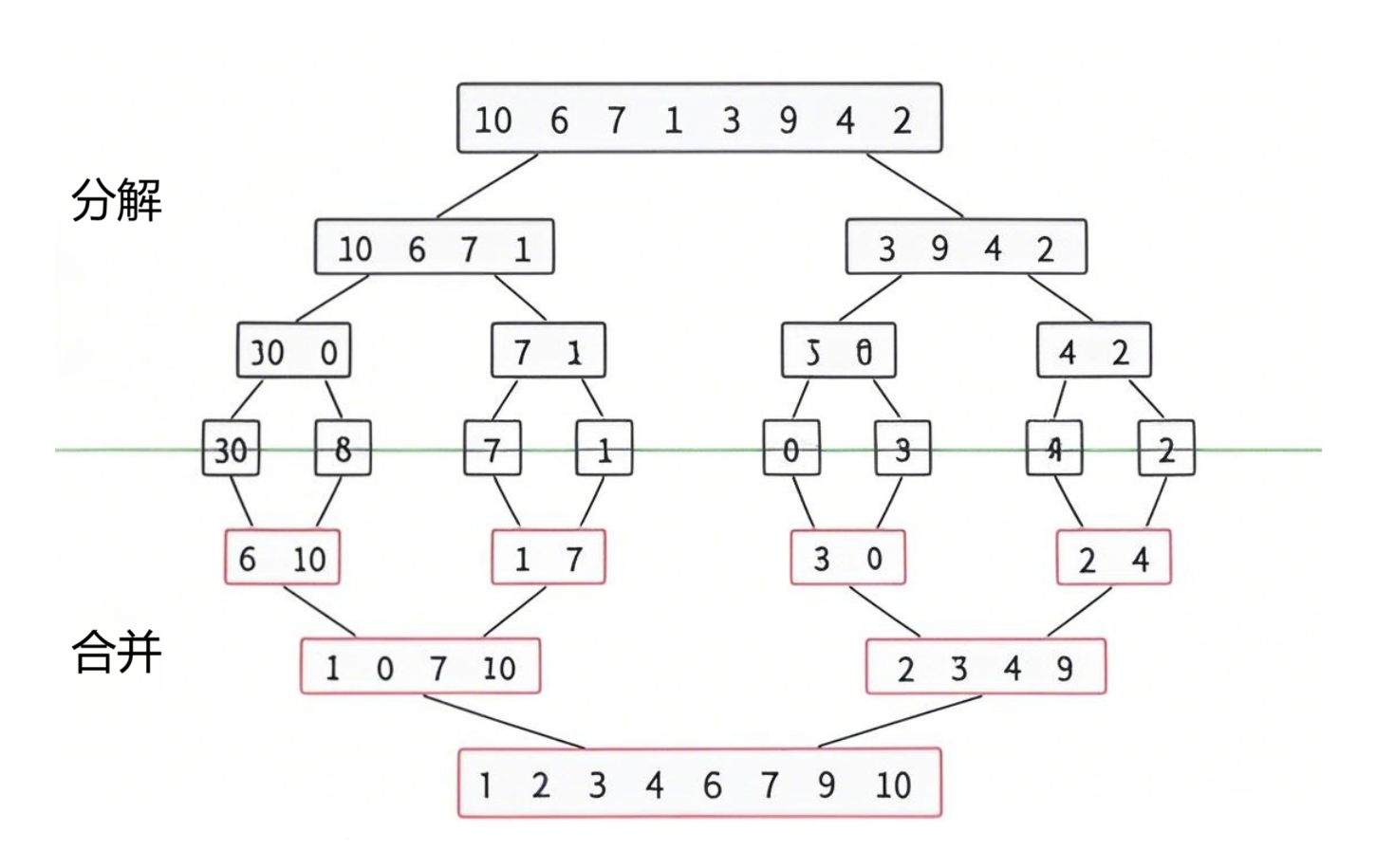

洛谷P1177【模板】排序:十种排序算法全解(2)

我们接着上一篇继续讲【洛谷P1177【模板】排序:十种排序算法全解(1)】 三、计数排序(Counting Sort) 仅适用于数据范围较小的情况 // Java import java.io.*; public class Main {static final int OFFSET 100000;public static void…...

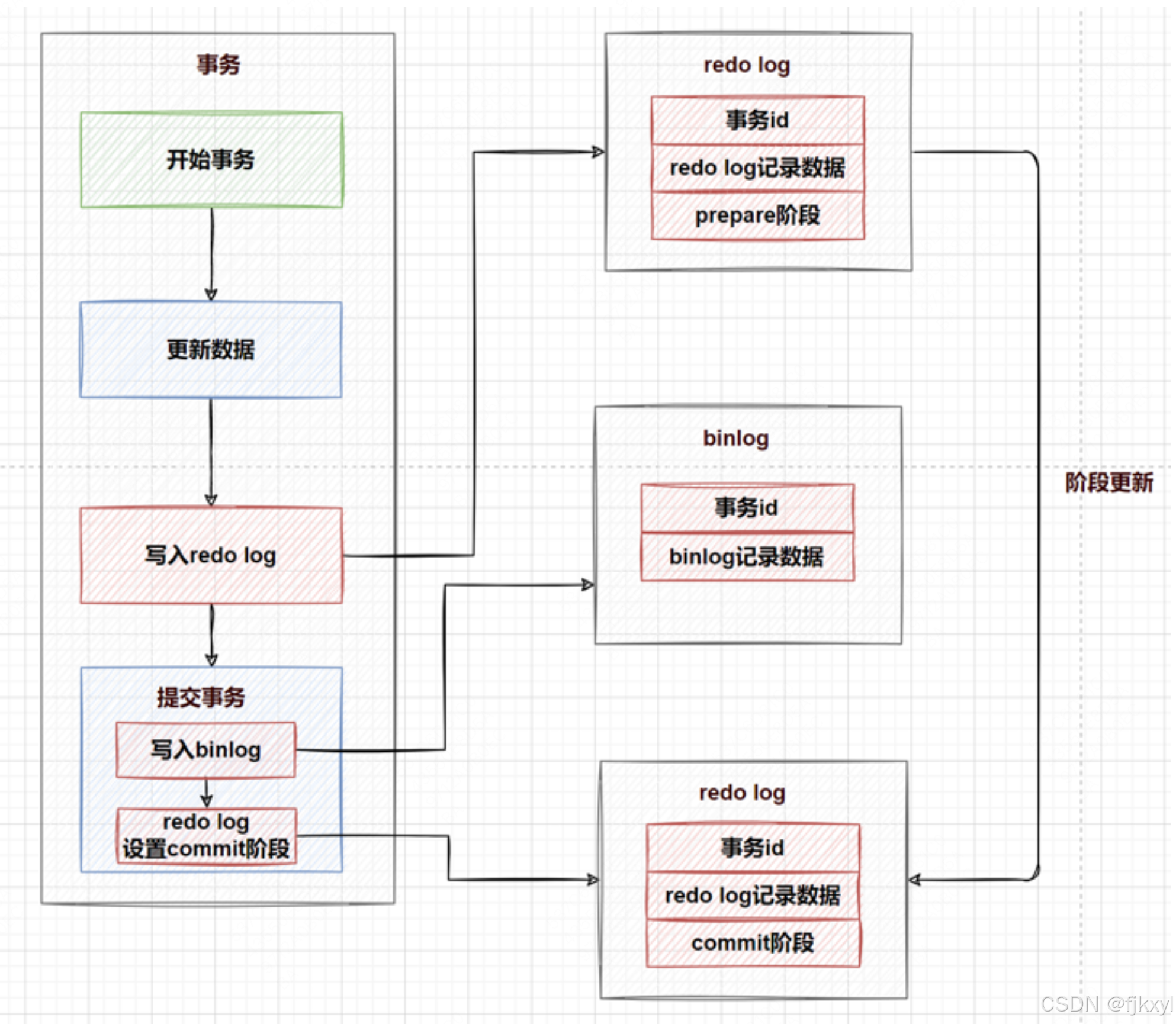

MySql 三大日志(redolog、undolog、binlog)详解

Docker使用、容器迁移

Docker 简介 Docker 是一个开源的容器化平台,用于打包、部署和运行应用程序及其依赖环境。Docker 容器是轻量级的虚拟化单元,运行在宿主机操作系统上,通过隔离机制(如命名空间和控制组)确保应用运行环境的一致性和可移…...

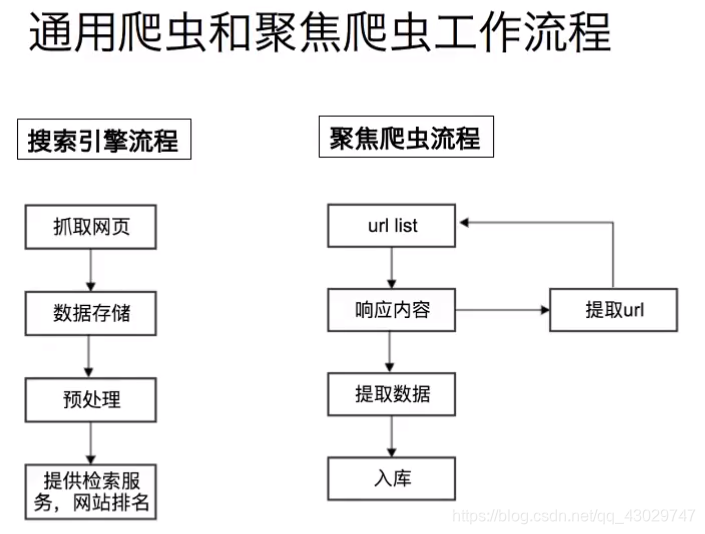

HTTP:九.WEB机器人

概念 Web机器人是能够在无需人类干预的情况下自动进行一系列Web事务处理的软件程序。人们根据这些机器人探查web站点的方式,形象的给它们取了一个饱含特色的名字,比如“爬虫”、“蜘蛛”、“蠕虫”以及“机器人”等!爬虫概述 网络爬虫(英语:web crawler),也叫网络蜘蛛(…...

2025妈妈杯数学建模C题完整分析论文(共36页)(含模型建立、可运行代码、数据)

2025 年第十五届 MathorCup 数学建模C题完整分析论文 目录 摘 要 一、问题分析 二、问题重述 三、模型假设 四、 模型建立与求解 4.1问题1 4.1.1问题1思路分析 4.1.2问题1模型建立 4.1.3问题1代码(仅供参考) 4.1.4问题1求解结果(仅…...

数据结构排序算法全解析:从基础原理到实战应用

在计算机科学领域,排序算法是数据处理的核心技术之一。无论是小规模数据的简单整理,还是大规模数据的高效处理,选择合适的排序算法直接影响着程序的性能。本文将深入解析常见排序算法的核心思想、实现细节、特性对比及适用场景,帮…...