AXI4总线协议 ------ AXI_LITE协议

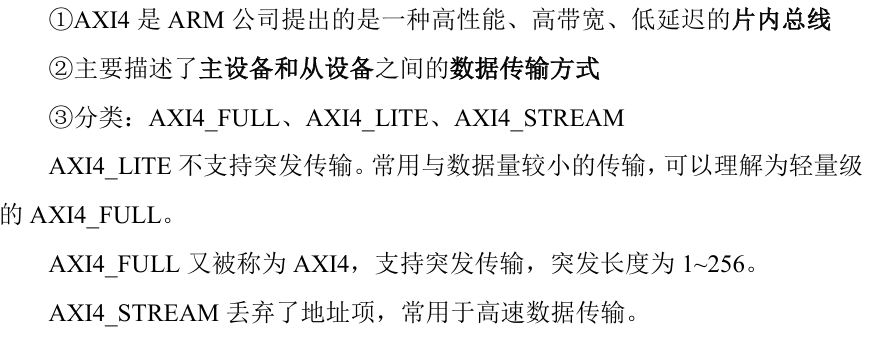

一、AXI 相关知识介绍

https://download.csdn.net/download/mvpkuku/90841873 AXI_LITE

选出部分重点,详细文档见上面链接。

1.AXI4 协议类型

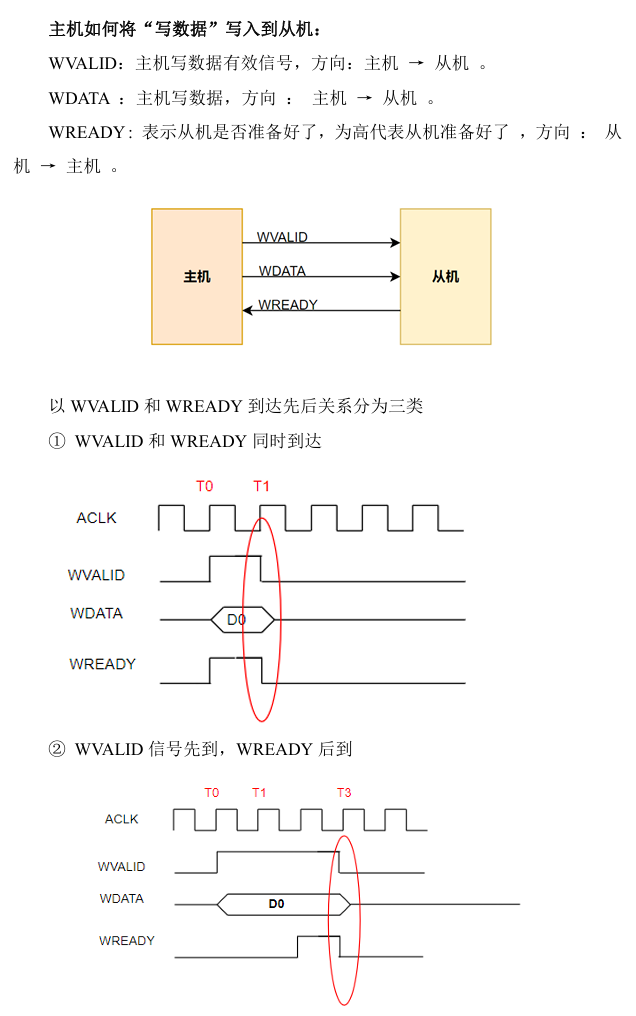

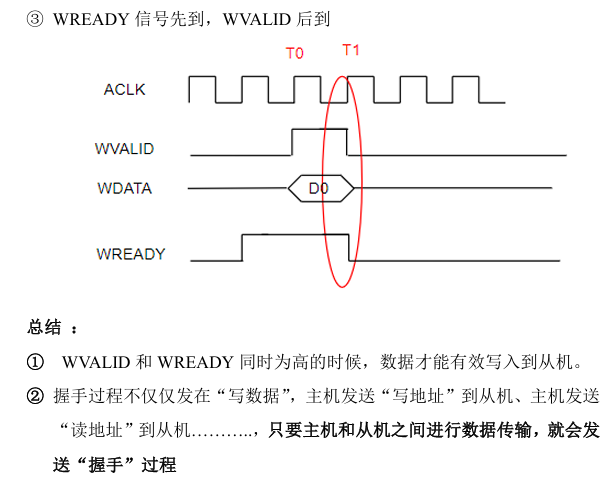

2.握手机制

二、AXI_LITE 协议的实现

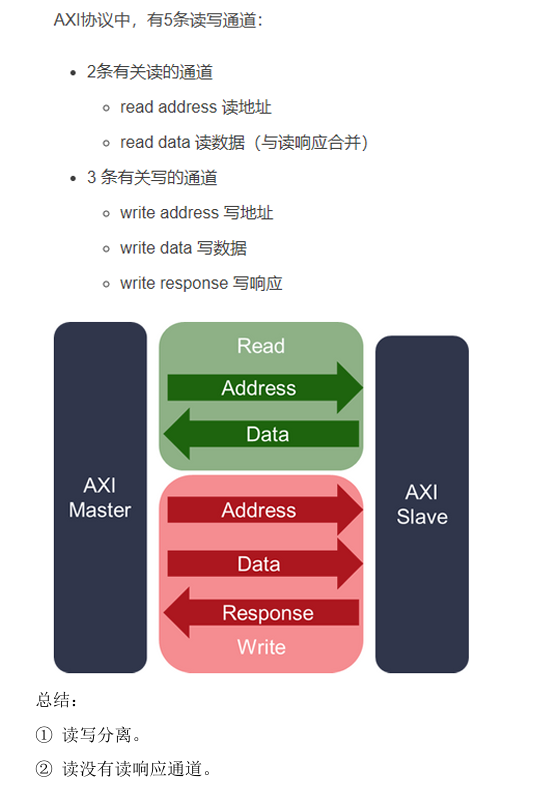

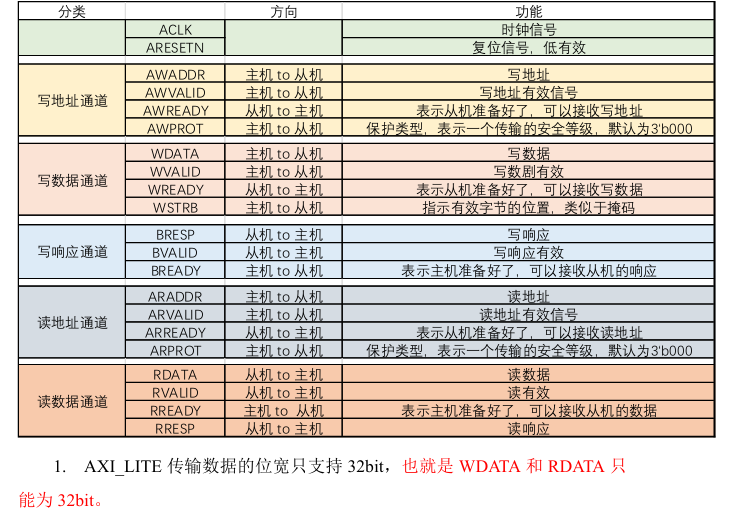

1. AXI_LITE 通道及各通道端口功能介绍

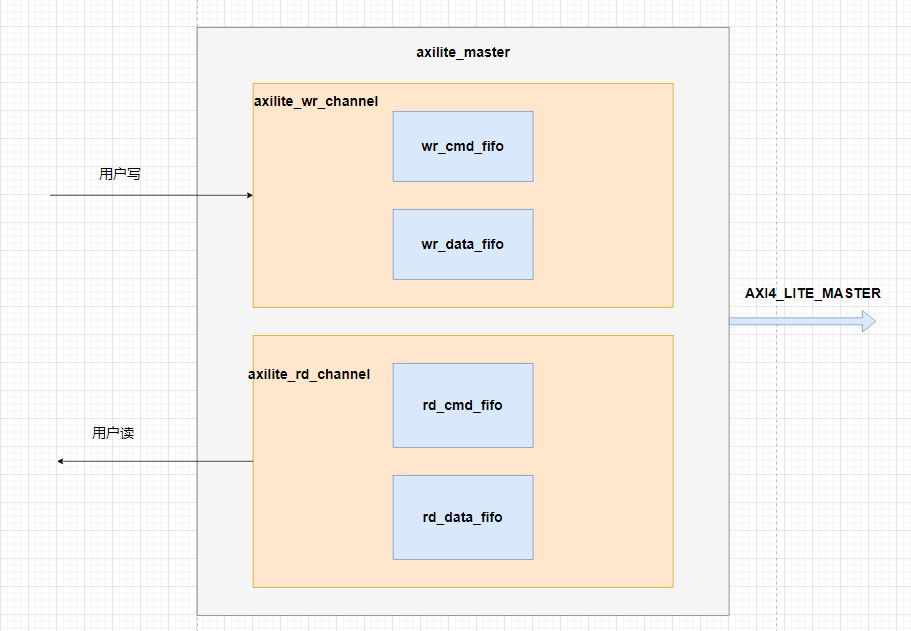

2.实现思路及框架

2.1 总体框架

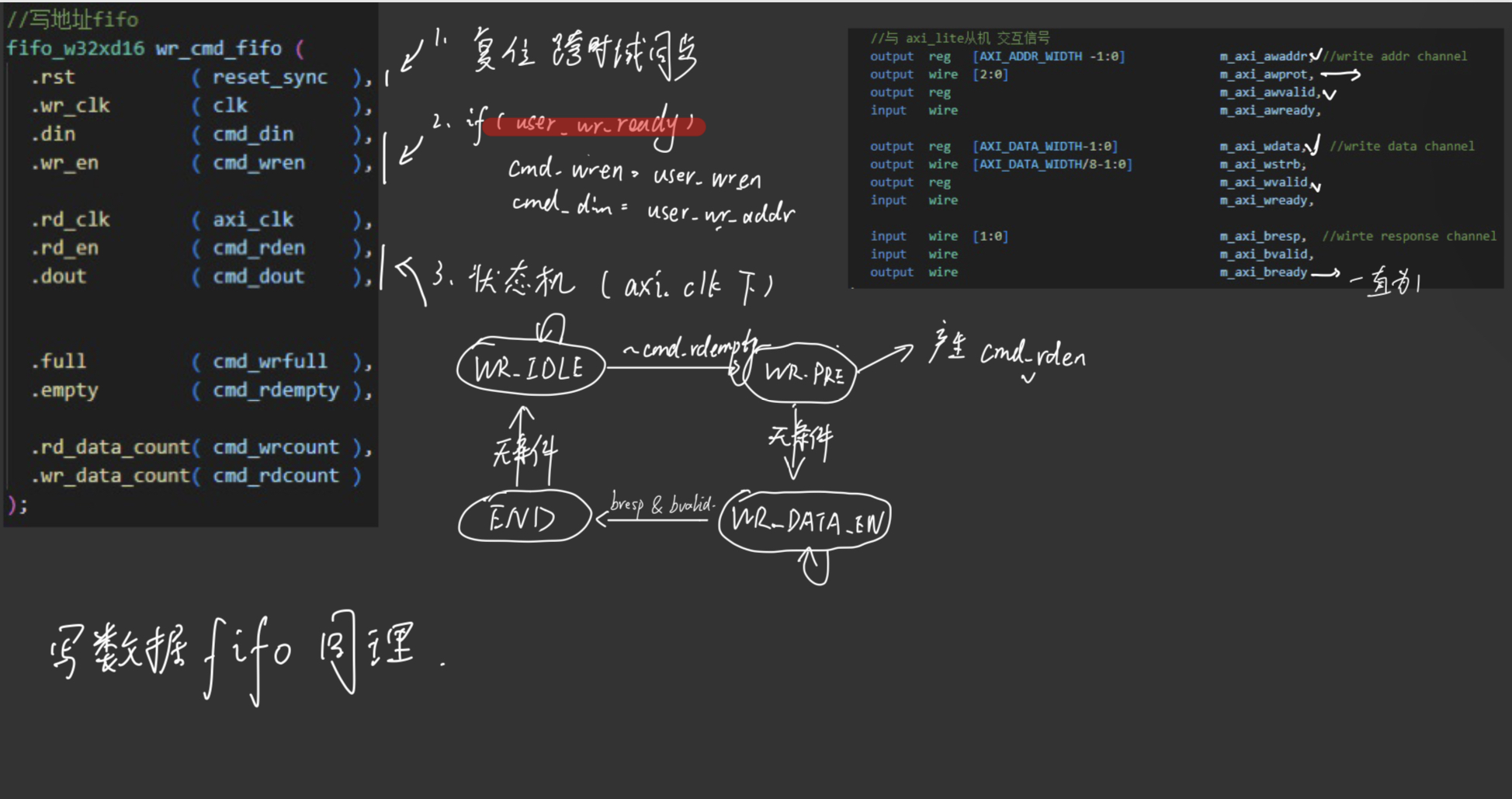

2.2 写通道

1.复位信号进行跨时钟域同步(用户时钟/AXI4时钟)

2.仅当user_wr_ready为高时,用户的写通道是有效的

3.例化两个fifo分别存储用户端传来的地址以及数据用户时钟写入,并通过AXI时钟读出

4.控制AXI_LITE(状态机)接口信号是在AXI时钟下进行 (控制cmd_rden/data_rden并输出对应的相关接口数据)

`timescale 1ns / 1ps

//

// Description: AXI_lite写通道

//

module axlite_wr_channel#(parameter USER_WR_DATA_WIDTH = 32 ,//用户写数据位宽和AXI4—Lite数据位宽保持一致parameter AXI_DATA_WIDTH = 32, //AXI4_LITE总线规定,数据位宽只支持32Bit或者64bitparameter AXI_ADDR_WIDTH = 32

)(input wire clk, //用户写时钟 input wire axi_clk, //从机读时钟 input wire reset,//与 用户端 交互信号input wire user_wr_en,input wire [USER_WR_DATA_WIDTH-1:0] user_wr_data,input wire [AXI_ADDR_WIDTH-1 :0] user_wr_addr,output wire user_wr_ready, //与 axi_lite从机 交互信号output reg [AXI_ADDR_WIDTH -1:0] m_axi_awaddr, //write addr channeloutput wire [2:0] m_axi_awprot, output reg m_axi_awvalid, input wire m_axi_awready,output reg [AXI_DATA_WIDTH-1:0] m_axi_wdata, //write data channeloutput wire [AXI_DATA_WIDTH/8-1:0] m_axi_wstrb,output reg m_axi_wvalid,input wire m_axi_wready,input wire [1:0] m_axi_bresp, //wirte response channelinput wire m_axi_bvalid,output wire m_axi_bready

);(* dont_touch = "true"*) reg reset_sync_d0; //user clk

(* dont_touch = "true"*) reg reset_sync_d1;

(* dont_touch = "true"*) reg reset_sync;

(* dont_touch = "true"*) reg a_reset_sync_d0; //axi clk

(* dont_touch = "true"*) reg a_reset_sync_d1;

(* dont_touch = "true"*) reg a_reset_sync;reg [31:0] cmd_din;

reg cmd_wren;

wire [31:0] cmd_dout;

reg cmd_rden;

wire cmd_wrfull ;

wire cmd_rdempty;

wire [4:0] cmd_wrcount;

wire [4:0] cmd_rdcount;reg [31:0] data_din;

reg data_wren;

wire [31:0] data_dout;

reg data_rden;

wire data_wrfull;

wire data_rdempty;

wire [4:0] data_wrcount;

wire [4:0] data_rdcount;reg [2 : 0] cur_status;

reg [2 : 0] nxt_status;localparam WR_IDLE = 3'b000;

localparam WR_PRE = 3'b001;

localparam WR_DATA_EN = 3'b010;

localparam WR_END = 3'b100;

/*--------------------------------------------------*\assign

\*--------------------------------------------------*/

assign m_axi_bready = 1'b1;

assign m_axi_awprot = 0;

assign m_axi_wstrb = {AXI_DATA_WIDTH/8{1'b1}};assign user_wr_ready = reset_sync ? 1'b0 : cmd_wrcount <= 'd12 ; //留一点余量 //当user_wr_ready为低的时候,用户发送写是无效的

/*--------------------------------------------------*\CDC process

\*--------------------------------------------------*/

always @(posedge clk) beginreset_sync_d0 <= reset;reset_sync_d1 <= reset_sync_d0;reset_sync <= reset_sync_d1;

endalways @(posedge axi_clk) begina_reset_sync_d0 <= reset;a_reset_sync_d1 <= a_reset_sync_d0;a_reset_sync <= a_reset_sync_d1;

end/*--------------------------------------------------*\wirte addr to cmd fifo、write data to data fifo

\*--------------------------------------------------*/

always @(posedge clk) beginif (user_wr_ready) begincmd_wren <= user_wr_en;cmd_din <= user_wr_addr;data_wren <= user_wr_en;data_din <= user_wr_data; endelse begincmd_wren <= 0;cmd_din <= 0;data_wren <= 0;data_din <= 0; end

end/*--------------------------------------------------*\WR state machine (三段式)

\*--------------------------------------------------*/

always@(posedge axi_clk)beginif(a_reset_sync)cur_status <= WR_IDLE;elsecur_status <= nxt_status;

endalways@(*)beginif(a_reset_sync)beginnxt_status <= WR_IDLE;endelse begincase(cur_status)WR_IDLE : beginif(!cmd_rdempty)nxt_status <= WR_PRE;elsenxt_status <= cur_status;endWR_PRE : beginnxt_status <= WR_DATA_EN;endWR_DATA_EN : beginif (m_axi_bvalid && m_axi_bready)nxt_status <= WR_END;else nxt_status <= cur_status;end WR_END : beginnxt_status <= WR_IDLE;enddefault : nxt_status <= WR_IDLE;endcaseend

end

/*-----------------------------------------------------------*\read addr from cmd_fifo 、 read data from data_fifo

\*-----------------------------------------------------------*/

always @(*) beginif (a_reset_sync) begincmd_rden <= 0;data_rden <= 0;endelse begincmd_rden <= cur_status == WR_PRE;data_rden <= cur_status == WR_PRE;end

endalways @(posedge axi_clk) beginif (cmd_rden) m_axi_awaddr <= cmd_dout;else m_axi_awaddr <= m_axi_awaddr;

endalways @(posedge axi_clk) beginif (a_reset_sync) m_axi_awvalid <= 0;else if (cur_status == WR_PRE)m_axi_awvalid <= 1'b1;else if (m_axi_awvalid && m_axi_awready)m_axi_awvalid <= 0;

endalways @(posedge axi_clk) beginif (data_rden) m_axi_wdata <= data_dout;else m_axi_wdata <= m_axi_wdata;

endalways @(posedge axi_clk) beginif (a_reset_sync) m_axi_wvalid <= 0;else if (cur_status == WR_PRE)m_axi_wvalid <= 1'b1;else if (m_axi_wvalid && m_axi_wready)m_axi_wvalid <= 0;

end//写地址fifo

fifo_w32xd16 wr_cmd_fifo (.rst ( reset_sync ), // input wire rst.wr_clk ( clk ), // input wire wr_clk 用户写时钟.din ( cmd_din ), // input wire [31 : 0] din.wr_en ( cmd_wren ), // input wire wr_en.rd_clk ( axi_clk ), // input wire rd_clk 从机读时钟 .rd_en ( cmd_rden ), // input wire rd_en.dout ( cmd_dout ), // output wire [31 : 0] dout.full ( cmd_wrfull ), // output wire full.empty ( cmd_rdempty ), // output wire empty.rd_data_count( cmd_wrcount ), // output wire [4 : 0] rd_data_count.wr_data_count( cmd_rdcount ) // output wire [4 : 0] wr_data_count

);//写数据fifo

fifo_w32xd16 wr_data_fifo (.rst ( reset_sync ), // input wire rst.wr_clk ( clk ), // input wire wr_clk 用户写时钟.din ( data_din ), // input wire [31 : 0] din.wr_en ( data_wren ), // input wire wr_en.rd_clk ( axi_clk ), // input wire rd_clk 从机读时钟 .rd_en ( data_rden ), // input wire rd_en.dout ( data_dout ), // output wire [31 : 0] dout.full ( data_wrfull ), // output wire full.empty ( data_rdempty ), // output wire empty.rd_data_count( data_rdcount ), // output wire [4 : 0] rd_data_count.wr_data_count( data_wrcount ) // output wire [4 : 0] wr_data_count

);

endmodule

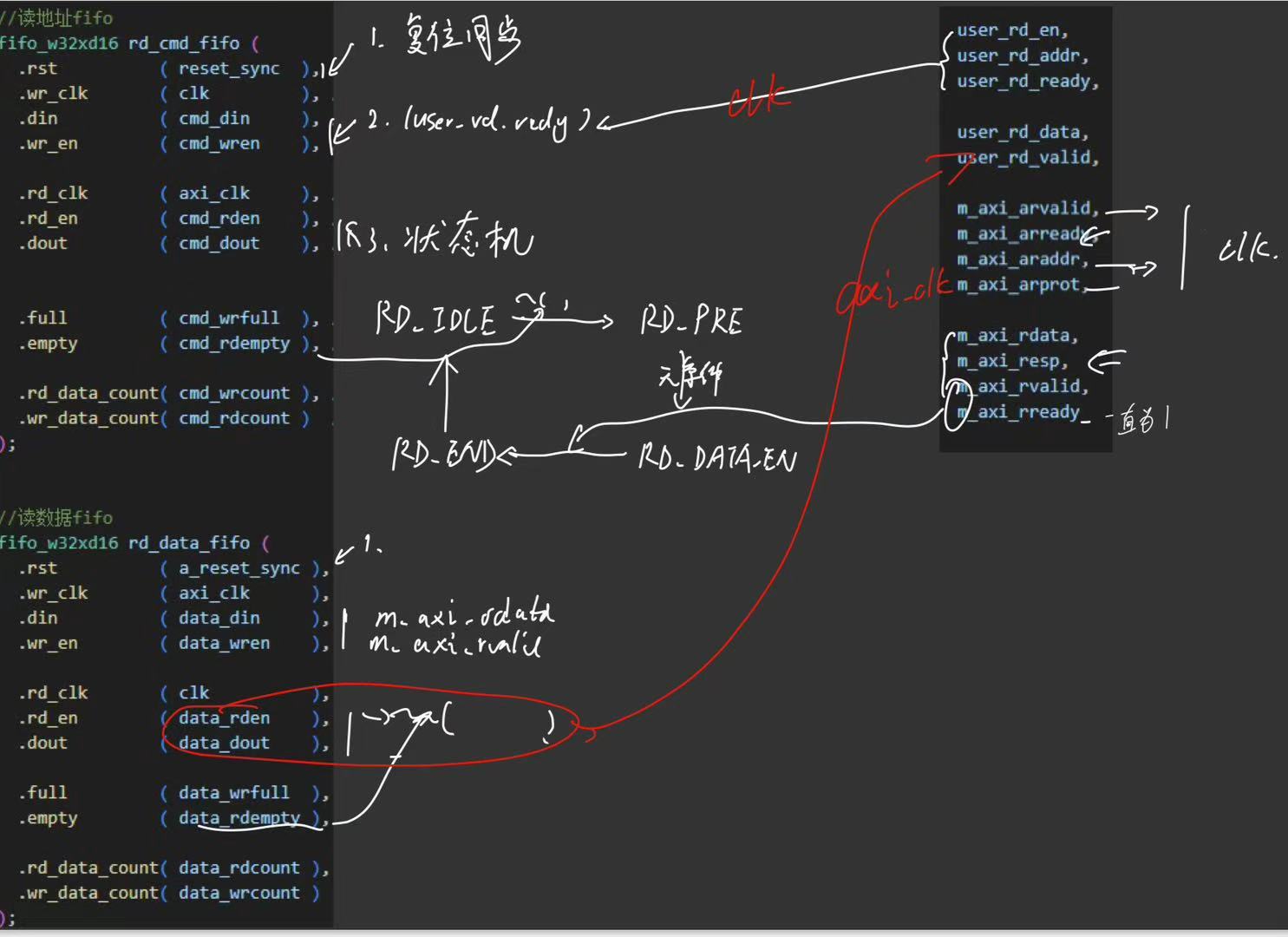

2.3 读通道

读通道的实现分两步,用户端发出读请求并给读的地址,然后从机根据地址发出数据,用户读出。

因此读地址fifo的逻辑部分与写通道一致,只有状态机跳转的RD_DATA_EN的条件根据模块端口有所改变,但是读数据fifo,是在AXI_CLK的时钟域下,端口输入有效及端口输入数据,根据非空开始用户读,然后赋给模块用户端口

`timescale 1ns / 1ps

//

// Description: AXI_LITE读通道

//

module axilite_rd_channel#(parameter USER_RD_DATA_WIDTH = 32 , //用户读数据位宽和AXI4—Lite数据位宽保持一致parameter AXI_DATA_WIDTH = 32, parameter AXI_ADDR_WIDTH = 32

)(input wire clk, input wire axi_clk, input wire reset,//用户端读请求,读地址信号input wire user_rd_en,input wire [AXI_ADDR_WIDTH-1 :0] user_rd_addr,output wire user_rd_ready,output reg [USER_RD_DATA_WIDTH-1:0] user_rd_data,output reg user_rd_valid,//与AXI_LITE从机 交互信号output reg m_axi_arvalid, // axi read address channelinput wire m_axi_arready, output reg [AXI_ADDR_WIDTH-1:0] m_axi_araddr,output wire [2:0] m_axi_arprot, input wire [AXI_DATA_WIDTH-1:0] m_axi_rdata, // axi read data channelinput wire [1:0] m_axi_resp,input wire m_axi_rvalid,output wire m_axi_rready

);(* dont_touch = "true"*) reg reset_sync_d0; //user clk

(* dont_touch = "true"*) reg reset_sync_d1;

(* dont_touch = "true"*) reg reset_sync;

(* dont_touch = "true"*) reg a_reset_sync_d0; //axi clk

(* dont_touch = "true"*) reg a_reset_sync_d1;

(* dont_touch = "true"*) reg a_reset_sync;reg [31:0] cmd_din;

reg cmd_wren;

wire [31:0] cmd_dout;

reg cmd_rden;

wire cmd_wrfull;

wire cmd_rdempty;

wire [4:0] cmd_wrcount;

wire [4:0] cmd_rdcount;reg [31:0] data_din;

reg data_wren;

wire [31:0] data_dout;

wire data_rden;

wire data_wrfull;

wire data_rdempty;

wire [4:0] data_wrcount;

wire [4:0] data_rdcount;reg [2 : 0] cur_status;

reg [2 : 0] nxt_status;localparam RD_IDLE = 3'b000;

localparam RD_PRE = 3'b001;

localparam RD_DATA_EN = 3'b010;

localparam RD_END = 3'b100;

/*--------------------------------------------------*\assign

\*--------------------------------------------------*/

assign user_rd_ready = reset_sync ? 1'b0 : cmd_wrcount <= 'd12 ;

assign m_axi_rready = 1'b1;

assign m_axi_arprot = 0;

/*--------------------------------------------------*\CDC process

\*--------------------------------------------------*/

always @(posedge clk) beginreset_sync_d0 <= reset;reset_sync_d1 <= reset_sync_d0;reset_sync <= reset_sync_d1;

endalways @(posedge axi_clk) begina_reset_sync_d0 <= reset;a_reset_sync_d1 <= a_reset_sync_d0;a_reset_sync <= a_reset_sync_d1;

end/*--------------------------------------------------*\wirte addr to cmd fifo

\*--------------------------------------------------*/

always @(posedge clk) beginif (user_rd_ready) begincmd_wren <= user_rd_en;cmd_din <= user_rd_addr; endelse begincmd_wren <= 0;cmd_din <= 0; end

end/*--------------------------------------------------*\RD state machine

\*--------------------------------------------------*/

always @(posedge axi_clk) beginif (a_reset_sync) begincur_status <= RD_IDLE;endelse begincur_status <= nxt_status;end

endalways @(*) beginif (a_reset_sync) beginnxt_status <= RD_IDLE; endelse begincase(cur_status)RD_IDLE : beginif (~cmd_rdempty)nxt_status <= RD_PRE;else nxt_status <= cur_status;endRD_PRE : beginnxt_status <= RD_DATA_EN;endRD_DATA_EN : beginif (m_axi_rvalid && m_axi_rready)nxt_status <= RD_END;else nxt_status <= cur_status;endRD_END : beginnxt_status <= RD_IDLE;enddefault : nxt_status <= RD_IDLE;endcase end

end/*-----------------------------------------------------------*\read addr from cmd_fifo

\*-----------------------------------------------------------*/

always @(*) beginif (a_reset_sync) cmd_rden <= 0;else cmd_rden <= cur_status == RD_PRE;

endalways @(posedge axi_clk) beginif (cmd_rden) m_axi_araddr <= cmd_dout;else m_axi_araddr <= m_axi_araddr;

endalways @(posedge axi_clk) beginif (a_reset_sync) m_axi_arvalid <= 0;else if (cur_status == RD_PRE)m_axi_arvalid <= 1'b1;else if (m_axi_arvalid && m_axi_arready)m_axi_arvalid <= 0;

end/*-----------------------------------------------------------*\read user data from data fifo

\*-----------------------------------------------------------*/

always @(posedge axi_clk) begindata_din <= m_axi_rdata;data_wren <= m_axi_rvalid;

end assign data_rden = reset_sync ? 1'b0 : ~data_rdempty;always @(posedge clk) beginuser_rd_valid <= data_rden;user_rd_data <= data_dout;

end//读地址fifo

fifo_w32xd16 rd_cmd_fifo (.rst ( reset_sync ), // input wire rst.wr_clk ( clk ), // input wire wr_clk 用户写时钟.din ( cmd_din ), // input wire [31 : 0] din.wr_en ( cmd_wren ), // input wire wr_en.rd_clk ( axi_clk ), // input wire rd_clk 从机读时钟 .rd_en ( cmd_rden ), // input wire rd_en.dout ( cmd_dout ), // output wire [31 : 0] dout.full ( cmd_wrfull ), // output wire full.empty ( cmd_rdempty ), // output wire empty.rd_data_count( cmd_wrcount ), // output wire [4 : 0] rd_data_count.wr_data_count( cmd_rdcount ) // output wire [4 : 0] wr_data_count

);//读数据fifo

fifo_w32xd16 rd_data_fifo (.rst ( a_reset_sync ), // input wire rst.wr_clk ( axi_clk ), // input wire wr_clk 从机写时钟.din ( data_din ), // input wire [31 : 0] din.wr_en ( data_wren ), // input wire wr_en.rd_clk ( clk ), // input wire rd_clk 用户读时钟 .rd_en ( data_rden ), // input wire rd_en.dout ( data_dout ), // output wire [31 : 0] dout.full ( data_wrfull ), // output wire full.empty ( data_rdempty ), // output wire empty.rd_data_count( data_rdcount ), // output wire [4 : 0] rd_data_count.wr_data_count( data_wrcount ) // output wire [4 : 0] wr_data_count

);

endmodule

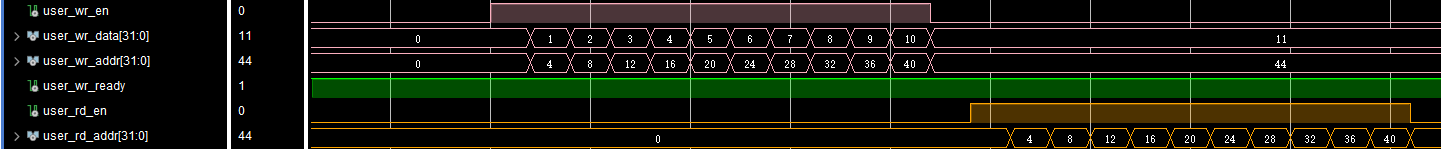

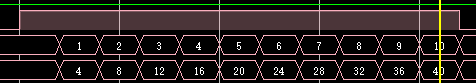

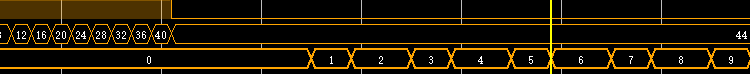

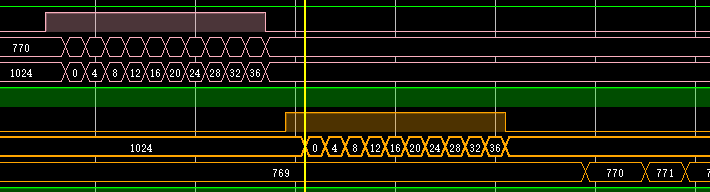

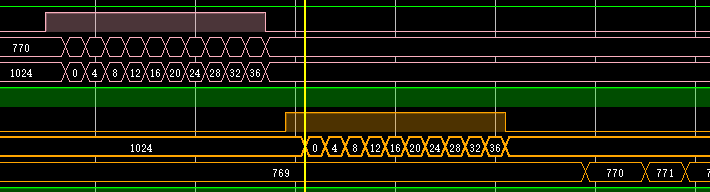

3.仿真

通过调用AXI_LITE接口的BRAM IP核,实/复位结束等一会儿进入写数据状态,读写数据(写10个数据,读10个数据),数据一致累加,地址也不断累加,地址最大为1024。

仿真结果如下,可以看出读写地址和数据完全一样,说明AXI_LITE接口代码实现无误。

![]()

需要工程请私信

相关文章:

AXI4总线协议 ------ AXI_LITE协议

一、AXI 相关知识介绍 https://download.csdn.net/download/mvpkuku/90841873 AXI_LITE 选出部分重点,详细文档见上面链接。 1.AXI4 协议类型 2.握手机制 二、AXI_LITE 协议的实现 1. AXI_LITE 通道及各通道端口功能介绍 2.实现思路及框架 2.1 总体框架 2.2 …...

DATE_FORMAT可以接收date类型,也可以接收String类型!

DATE_FORMAT 是 SQL 函数,主要用于将日期/时间类型的字段按照指定格式转换成字符串。在 MyBatis 的 XML 动态 SQL 中,你看到的这段代码是为了比较数据库中的日期字段和传入参数的日期值,但会忽略时间部分,只比较年月日。 代码解释…...

Ubuntu24.04 安装 5080显卡驱动以及cuda

前言 之前使用Ubuntu22.04版本一直报错,然后换了24.04版本才能正常安装 一. 配置基础环境 Linux系统进行环境开发环境配置-CSDN博客 二. 安装显卡驱动 1.安装驱动 按以下步骤来: sudo apt update && sudo apt upgrade -y#下载最新内核并安装 sudo add…...

华三H3C交换机配置NTP时钟步骤 示例

现场1台H3C 5110交换机 版本:Comware Software, Version 5.20.99, Release 1105 当前没有指定NTP, <H3C-5110>dis ntp-service status Clock status: unsynchronizedClock stratum: 16Reference clock ID: noneNominal frequency: 100.0000 HzAc…...

)

RKNN开发环境搭建(ubuntu22.04)

以下情况在RV1106G3的平台上验证正常。 1、conda安装 1)conda --version//确认是否安装 2)创建一个安装目录,进行下一步 3)wget https://mirrors.tuna.tsinghua.edu.cn/anaconda/miniconda/Miniconda3-4.6.14-Linux-x…...

matlab多项式

1. 多项式表示 多项式用行向量表示,按降幂排列系数。例如,多项式 3x22x1 表示为 [3 2 1]。 2. 创建多项式 直接输入系数:如 p [1 -3 3 -1] 表示 x3−3x23x−1。由根创建:使用 poly 函数。例如,根为 [1, 1, 1]&…...

?)

Sprnig MVC 如何统一异常处理 (Exception Handling)?

主要有以下几种方式来实现统一异常处理,其中 ControllerAdvice (或 RestControllerAdvice) 结合 ExceptionHandler 是最常用的方式。 1. ExceptionHandler 注解 作用: 用于标记一个方法,该方法将处理在同一个 Controller 类中抛出的特定类型…...

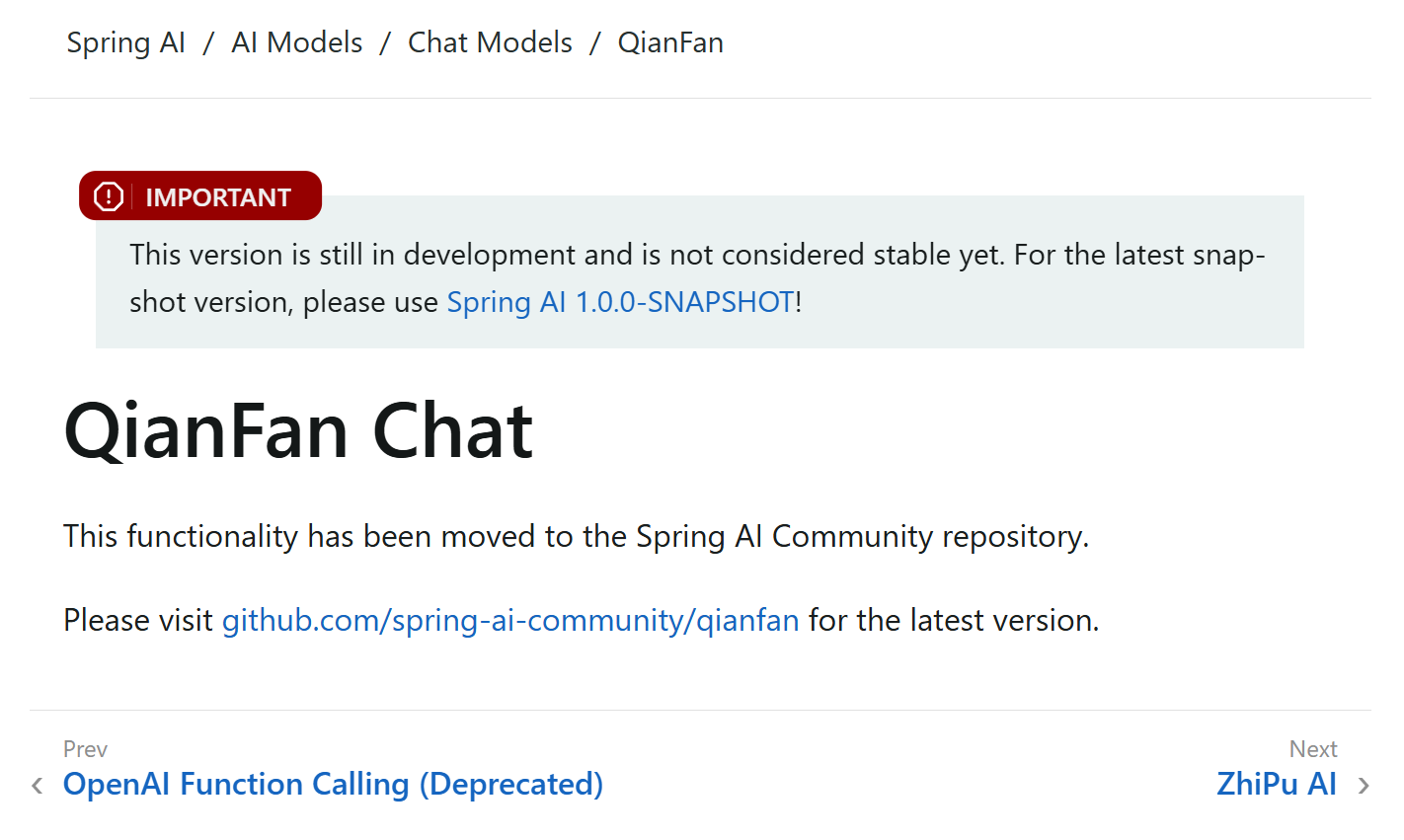

SpringAI-RC1正式发布:移除千帆大模型!

续 Spring AI M8 版本之后(5.1 发布),前几日 Spring AI 悄悄的发布了最新版 Spring AI 1.0.0 RC1(5.13 发布),此版本也将是 GA(Generally Available,正式版)发布前的最后…...

操作系统之进程和线程听课笔记

计算机的上电运行就是构建进程树,进程调度就是在进程树节点进程进行切换 进程间通信的好处 经典模型 生产者和消费者 进程和线程的区别 线程引入带来的问题线程的优势 由于unix70年代产生,90年代有线程,当时数据库系统操作需要线程,操作系统没有来得及重造,出现了用户态线…...

【vue】封装接口,全局字典,表格表头及使用

一、封装接口(API请求) 1. 创建axios实例 // src/utils/request.js import axios from axiosconst service axios.create({baseURL: process.env.VUE_APP_BASE_API,timeout: 10000 })// 请求拦截器 service.interceptors.request.use(config > {co…...

深入解析ZAB协议:ZooKeeper的分布式一致性核心

引言 在分布式系统中,如何高效、可靠地实现多节点间的数据一致性是核心挑战之一。ZAB协议(ZooKeeper Atomic Broadcast)作为 ZooKeeper的核心算法,被广泛应用于分布式协调服务(如Kafka、HBase、Dubbo等)。…...

COMSOL随机参数化表面流体流动模拟

基于粗糙度表面的裂隙流研究对于理解地下水的流动、污染物传输以及与之相关的地质灾害(如滑坡)等方面具有重要意义。本研究通过蒙特卡洛方法生成随机表面形貌,并利用COMSOL Multiphysics对随机参数化表面的微尺度流体流动进行模拟。 参数化…...

大模型笔记-“训练”和“推理”概念

在大模型(如Transformer类模型、LLM)的资源管理和开发流程中,“训练”和“推理”是两个核心概念,分别对应模型的构建和实际应用阶段: 训练是模型的“学习过程”,需要大量资源和时间。推理是模型的“应用过…...

JavaSwing中的容器之--JScrollPane

JavaSwing中的容器之–JScrollPane 在Java Swing中,容器是用于容纳其他组件(如按钮、标签等)的组件。Swing提供了多种容器,它们可以嵌套使用以创建复杂的用户界面。 JScrollPane是一个轻量级组件,提供可滚动视图。JSc…...

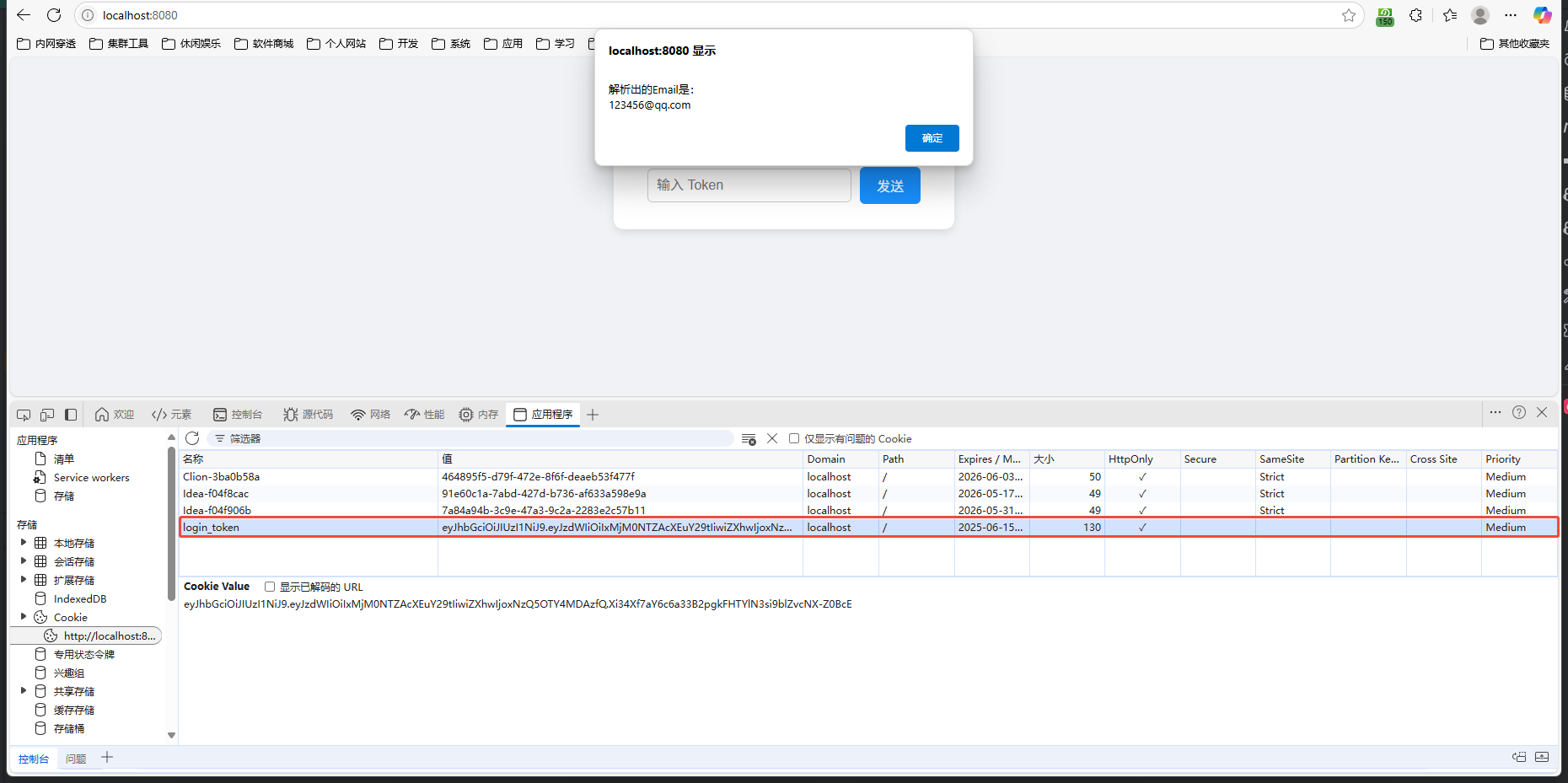

使用 Cookie 实现认证跳转功能

使用 Cookie 实现认证跳转功能的实践与解析 在 Web 开发中,用户身份认证是一个基础而关键的功能点。本文将通过一个简单的前后端示例系统,介绍如何基于 Cookie 实现 Token 保存与自动跳转认证的功能,并结合 Cookie 与 Header 的区别、使用场…...

和Bridge-Aggregation(链路聚合接口)区别)

Reth(冗余以太网接口) 和Bridge-Aggregation(链路聚合接口)区别

Reth(Redundant Ethernet)与Bridge-Aggregation是H3C设备中两种不同的接口技术,主要区别体现在工作原理、应用场景及配置特性上。以下是详细对比分析: 定义与类型 Reth(冗余以太网接口) 类型:…...

Android各版本新特性)

(面试)Android各版本新特性

Android 6.0 (Marshmallow, API 23) 运行时权限管理:用户可在应用运行时动态授予或拒绝权限,取代安装时统一授权4。Doze模式与应用待机:优化后台耗电,延长设备续航5。指纹识别支持:原生API支持指纹身份验证。 Android…...

算法基础 -- 小根堆构建的两种方式:上浮法与下沉法

小根堆构建的两种方式:上浮法与下沉法 在构建小根堆(Min-Heap)时,通常有两种常见的构建方式: 上浮建堆(逐个插入,上浮调整)下沉建堆(Heapify 自底向上,下沉…...

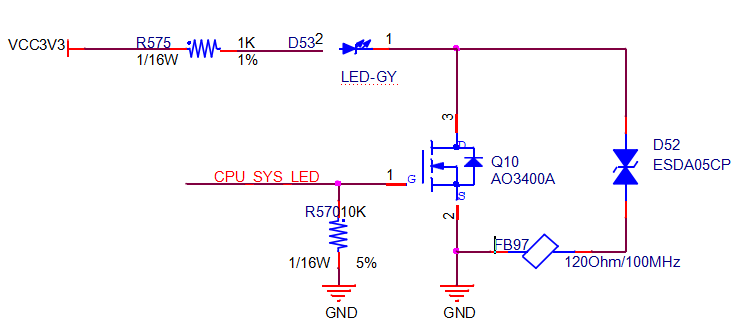

LED接口设计

一个LED灯有3种控制状态,常亮、常灭和闪烁,要做到这种控制最简单的一种方法是使用任何一款处理器的普通IO去控制。 用IO控制方式有两种,一种是高有效,如下图1所示IO口为高电平时LED亮,IO为低电平时LED不亮。IO口出一个…...

西安前端面试

面试1 1.vue2和vue3的原理及区别 2.伪数组 3.对箭头函数怎么理解的 4.vue父子组件传值的几种方式 5.对Promise的理解 面试2 1.两个升序数组实现合并升序排序 2.数组拍平[3, [[7, [1, 5]], 4], 8, [6]] 面试3 1.let var const的区别,什么时候const能改变 …...

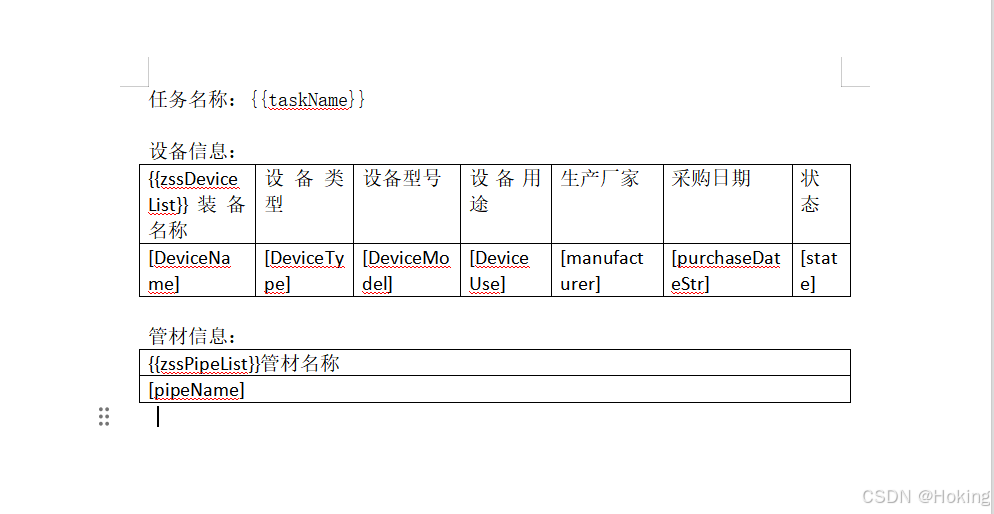

SpringBoot项目使用POI-TL动态生成Word文档

近期项目工作需要动态生成Word文档的需求,特意调研了动态生成Word的技术方案。主要有以下两种: 第一种是FreeMarker模板来进行填充;第二种是POI-TL技术使用Word模板来进行填充; 以下是关于POI-TL的官方介绍 重点关注࿱…...

java高效实现爬虫

一、前言 在Web爬虫技术中,Selenium作为一款强大的浏览器自动化工具,能够模拟真实用户操作,有效应对JavaScript渲染、Ajax加载等复杂场景。而集成代理服务则能够解决IP限制、地域访问限制等问题。本文将详细介绍如何利用JavaSelenium快代理实…...

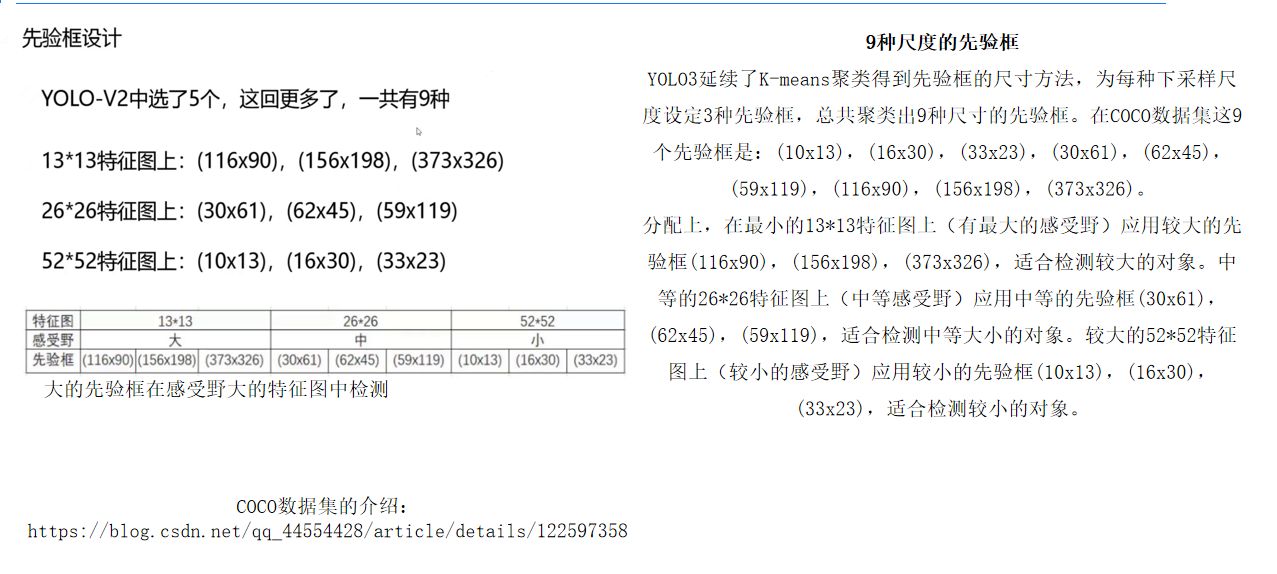

YOLOv3深度解析:多尺度特征融合与实时检测的里程碑

一、YOLOv3的诞生:继承与突破的起点 YOLOv3作为YOLO系列的第三代算法,于2018年由Joseph Redmon等人提出。它在YOLOv2的基础上,针对小目标检测精度低、多类别标签预测受限等问题进行了系统性改进。通过引入多尺度特征图检测、残差网络架构和独…...

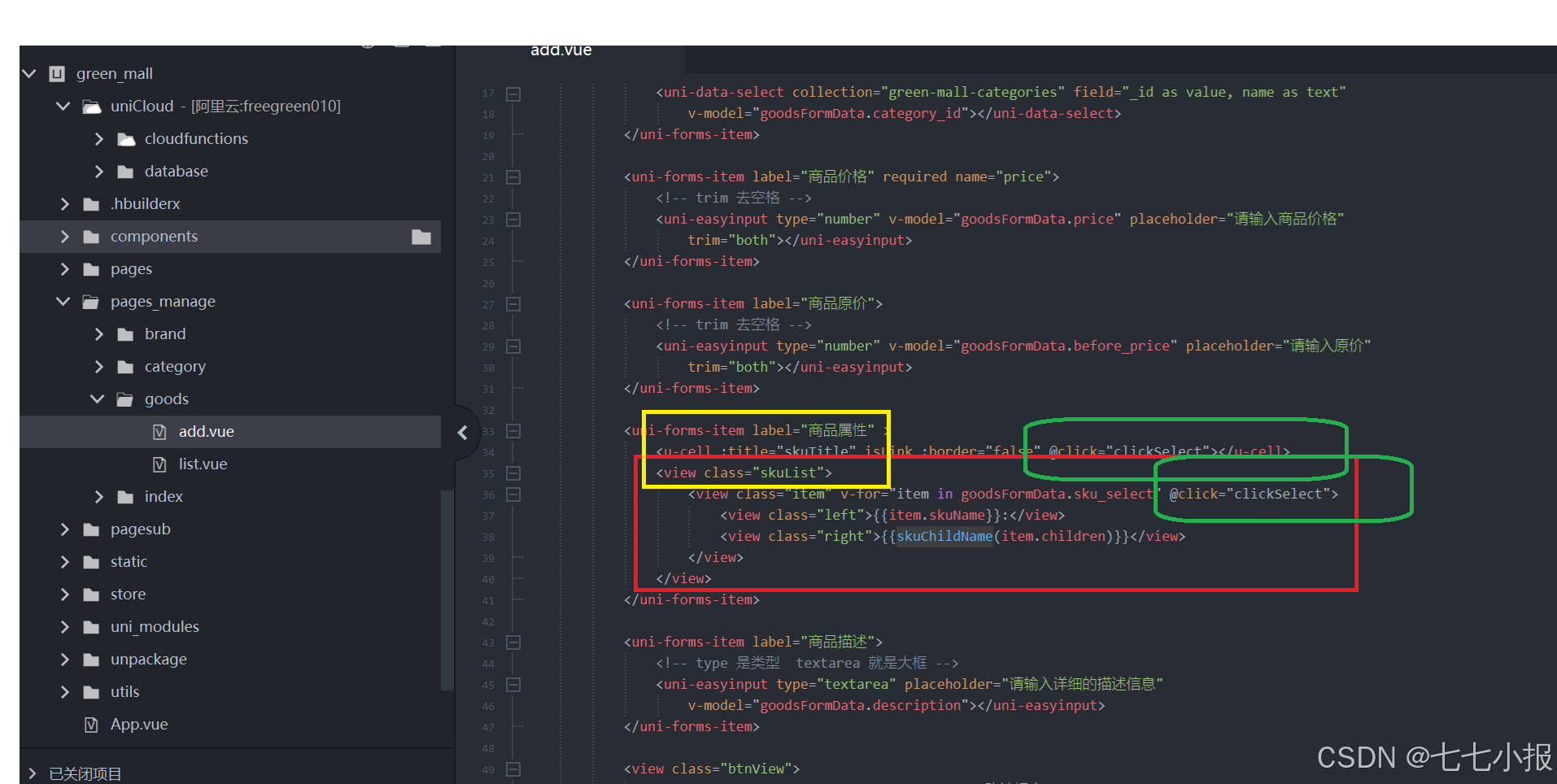

uniapp-商城-60-后台 新增商品(属性的选中和页面显示)

前面添加了属性,添加属性的子级项目。也分析了如何回显,但是在添加新的商品的时,我们也同样需要进行选择,还要能正常的显示在界面上。下面对页面的显示进行分析。 1、界面情况回顾 属性显示其实是个一嵌套的数据显示。 2、选中的…...

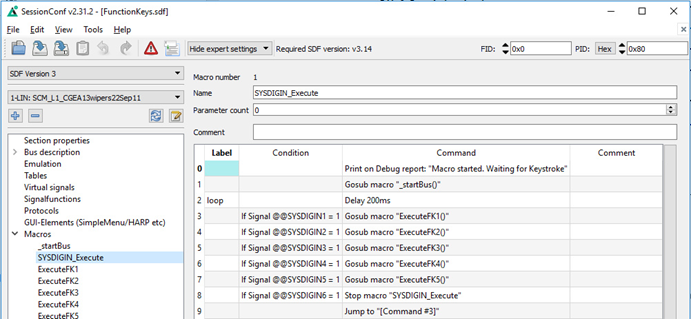

虹科技术 | 简化汽车零部件测试:LIN/CAN总线设备的按键触发功能实现

汽车零部件测试领域对操作的便捷性要求越来越高,虹科Baby-LIN-RC系列产品为这一需求提供了完美的解决方案。从基础的按键设置到高级的Shift键应用,本文将一步步引导您了解虹科Baby-LIN-RC系列产品的智能控制之道。 虹科Baby-LIN-3-RC 想象一下࿰…...

单片机ESP32天气日历闹铃语音播报

自制Arduino Esp32 单片机 可以整点语音播报,闹铃语音播报,农历显示,白天晚上天气,硬件有 Esp32,ST7789显示屏,Max98357 喇叭驱动,小喇叭一枚。有需要源码的私信我。#单片机 #闹钟 #嵌入式 #智能…...

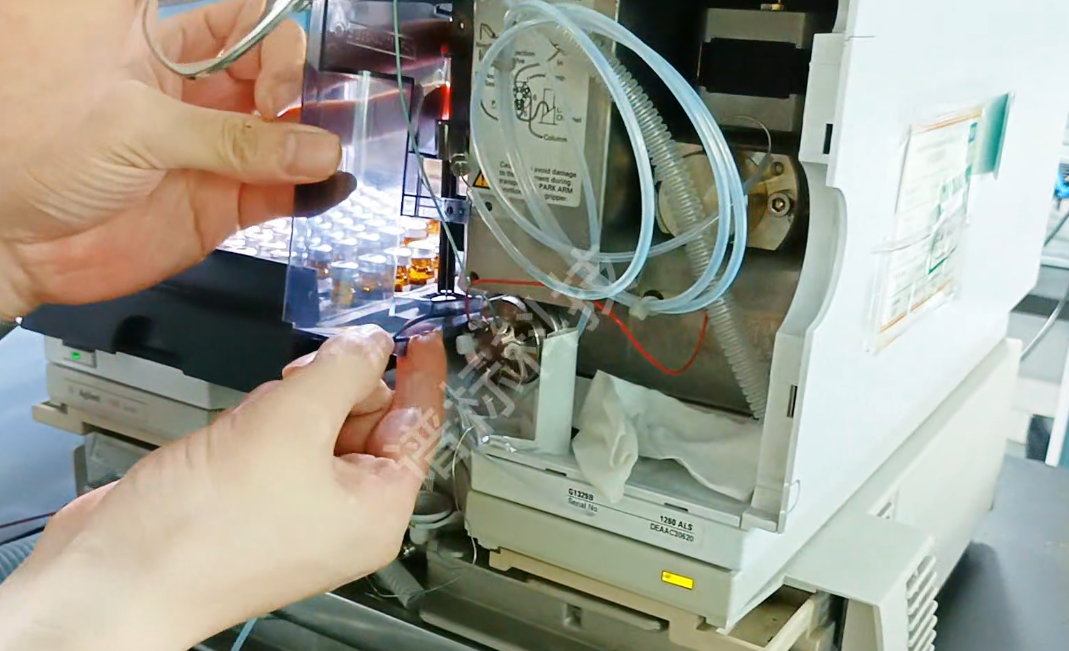

如何解决LCMS 液质联用液相进样器定量环漏液问题

以下是解决安捷伦1260液相色谱仪为例的进样器定量环漏液问题的一些方法:视频操作 检查相关部件 检查定量环本身:观察定量环是否有破损、裂纹或变形等情况。如果发现定量环损坏,需及时更换。检查密封垫:查看进样阀的转子密封垫、计…...

服务器内部可以访问外部网络,docker内部无法访问外部网络,只能docker内部访问

要通过 iptables 将容器中的特定端口请求转发到特定服务器,你需要设置 DNAT(目标地址转换)规则。以下是详细步骤: 假设场景 容器端口: 8080(容器内服务监听的端口)目标服务器: 192.168.1.100(请…...

机器学习中的特征工程:解锁模型性能的关键

在机器学习领域,模型的性能往往取决于数据的质量和特征的有效性。尽管深度学习模型在某些任务中能够自动提取特征,但在大多数传统机器学习任务中,特征工程仍然是提升模型性能的关键环节。本文将深入探讨特征工程的重要性、常用方法以及在实际…...

JAVA:Spring Boot 集成 RDF4J 实现欺诈检测的技术指南

1、简述 在大数据、知识图谱和金融风控等领域,RDF(Resource Description Framework) 是一种用于表示和查询关联数据的强大工具。RDF4J 是一个流行的 Java 库,用于操作 RDF 数据集,并支持 SPARQL 查询,能够帮助我们进行复杂的欺诈检测。 项目的核心功能: RDF 数据存储:…...