error: #5: cannot open source input file “core_cmInstr.h“

GD32F103VET6和STM32F103VET6引脚兼容。

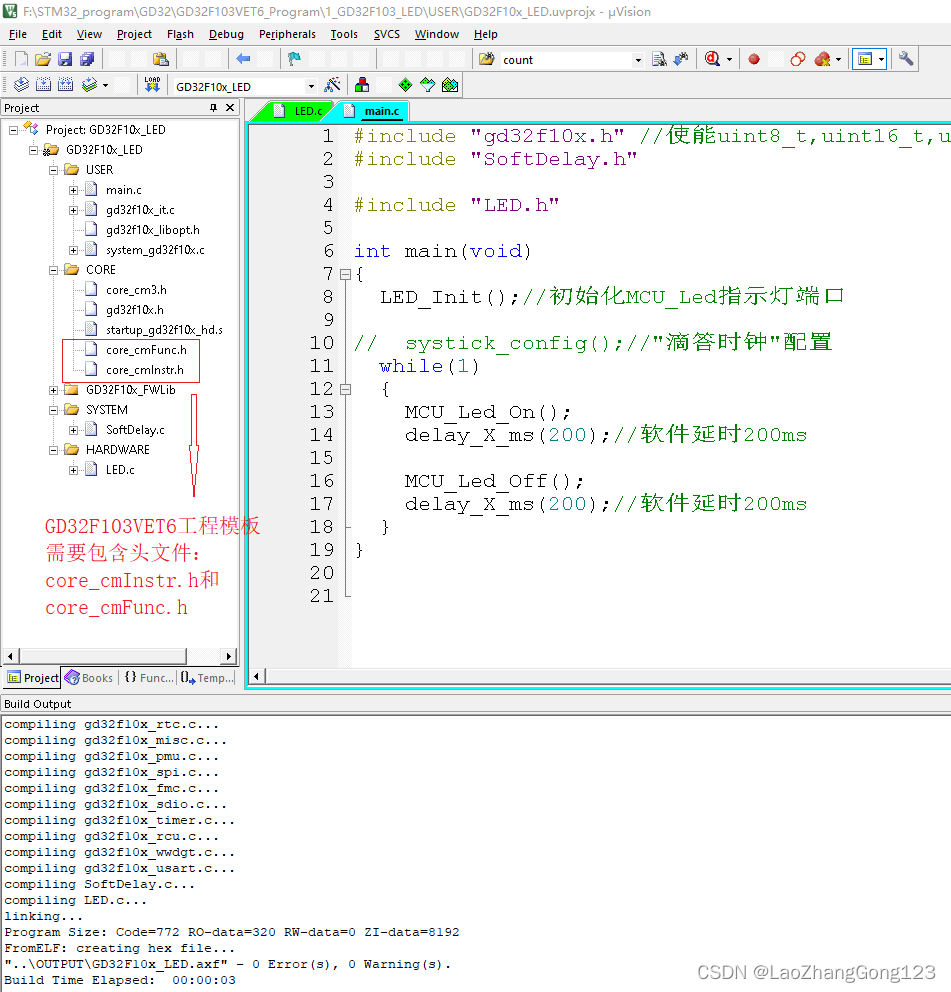

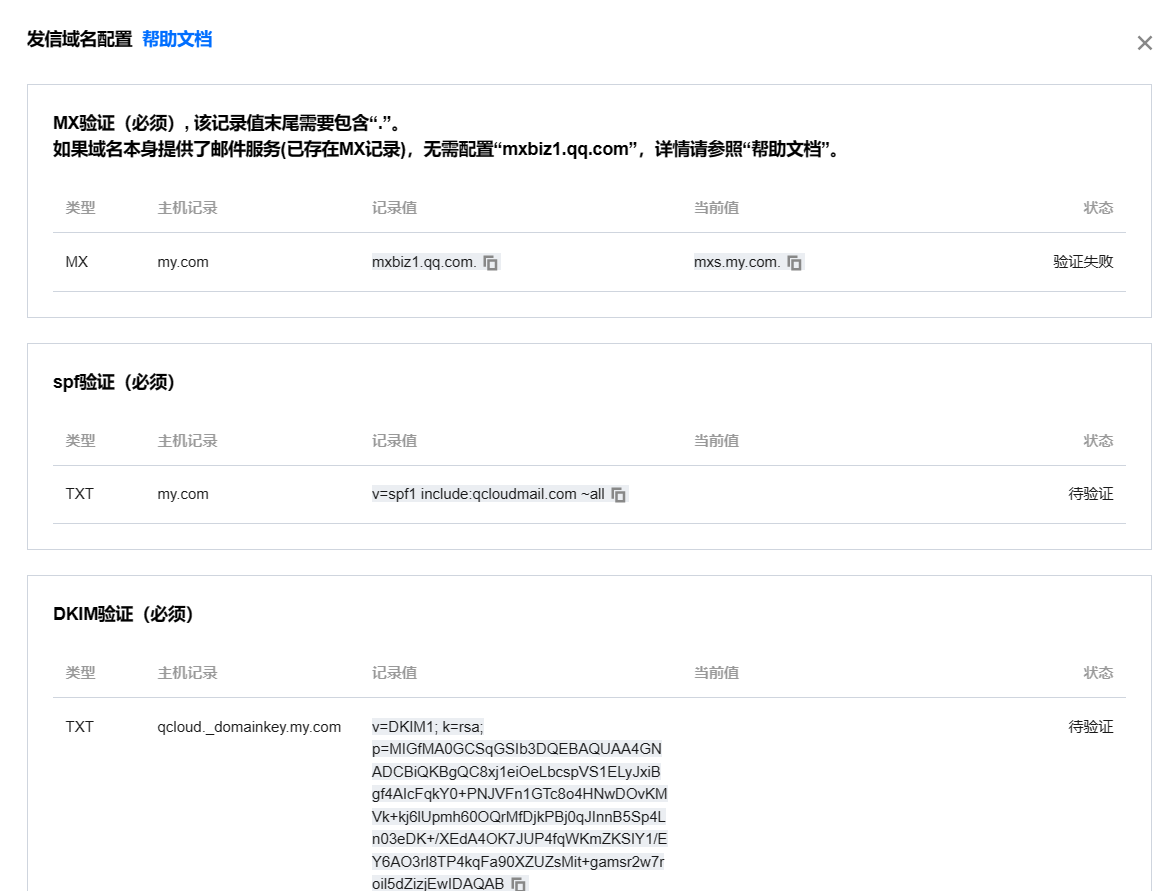

GD32F103VET6工程模板需要包含头文件:core_cmInstr.h和core_cmFunc.h,这个和STM32F103还是有区别的,否则会报错,如下:

error: #5: cannot open source input file "core_cmInstr.h": No such file or directory

贴出来,以便大家去下载,还要积分,找得还辛苦。

/**************************************************************************//*** @file core_cmFunc.h* @brief CMSIS Cortex-M Core Function Access Header File* @version V3.02* @date 24. May 2012** @note* Copyright (C) 2009-2012 ARM Limited. All rights reserved.** @par* ARM Limited (ARM) is supplying this software for use with Cortex-M* processor based microcontrollers. This file can be freely distributed* within development tools that are supporting such ARM based processors.** @par* THIS SOFTWARE IS PROVIDED "AS IS". NO WARRANTIES, WHETHER EXPRESS, IMPLIED* OR STATUTORY, INCLUDING, BUT NOT LIMITED TO, IMPLIED WARRANTIES OF* MERCHANTABILITY AND FITNESS FOR A PARTICULAR PURPOSE APPLY TO THIS SOFTWARE.* ARM SHALL NOT, IN ANY CIRCUMSTANCES, BE LIABLE FOR SPECIAL, INCIDENTAL, OR* CONSEQUENTIAL DAMAGES, FOR ANY REASON WHATSOEVER.*******************************************************************************/#ifndef __CORE_CMFUNC_H

#define __CORE_CMFUNC_H/* ########################### Core Function Access ########################### */

/** \ingroup CMSIS_Core_FunctionInterface\defgroup CMSIS_Core_RegAccFunctions CMSIS Core Register Access Functions@{*/#if defined ( __CC_ARM ) /*------------------RealView Compiler -----------------*/

/* ARM armcc specific functions */#if (__ARMCC_VERSION < 400677)#error "Please use ARM Compiler Toolchain V4.0.677 or later!"

#endif/* intrinsic void __enable_irq(); */

/* intrinsic void __disable_irq(); *//** \brief Get Control RegisterThis function returns the content of the Control Register.\return Control Register value*/

__STATIC_INLINE uint32_t __get_CONTROL(void)

{register uint32_t __regControl __ASM("control");return(__regControl);

}/** \brief Set Control RegisterThis function writes the given value to the Control Register.\param [in] control Control Register value to set*/

__STATIC_INLINE void __set_CONTROL(uint32_t control)

{register uint32_t __regControl __ASM("control");__regControl = control;

}/** \brief Get IPSR RegisterThis function returns the content of the IPSR Register.\return IPSR Register value*/

__STATIC_INLINE uint32_t __get_IPSR(void)

{register uint32_t __regIPSR __ASM("ipsr");return(__regIPSR);

}/** \brief Get APSR RegisterThis function returns the content of the APSR Register.\return APSR Register value*/

__STATIC_INLINE uint32_t __get_APSR(void)

{register uint32_t __regAPSR __ASM("apsr");return(__regAPSR);

}/** \brief Get xPSR RegisterThis function returns the content of the xPSR Register.\return xPSR Register value*/

__STATIC_INLINE uint32_t __get_xPSR(void)

{register uint32_t __regXPSR __ASM("xpsr");return(__regXPSR);

}/** \brief Get Process Stack PointerThis function returns the current value of the Process Stack Pointer (PSP).\return PSP Register value*/

__STATIC_INLINE uint32_t __get_PSP(void)

{register uint32_t __regProcessStackPointer __ASM("psp");return(__regProcessStackPointer);

}/** \brief Set Process Stack PointerThis function assigns the given value to the Process Stack Pointer (PSP).\param [in] topOfProcStack Process Stack Pointer value to set*/

__STATIC_INLINE void __set_PSP(uint32_t topOfProcStack)

{register uint32_t __regProcessStackPointer __ASM("psp");__regProcessStackPointer = topOfProcStack;

}/** \brief Get Main Stack PointerThis function returns the current value of the Main Stack Pointer (MSP).\return MSP Register value*/

__STATIC_INLINE uint32_t __get_MSP(void)

{register uint32_t __regMainStackPointer __ASM("msp");return(__regMainStackPointer);

}/** \brief Set Main Stack PointerThis function assigns the given value to the Main Stack Pointer (MSP).\param [in] topOfMainStack Main Stack Pointer value to set*/

__STATIC_INLINE void __set_MSP(uint32_t topOfMainStack)

{register uint32_t __regMainStackPointer __ASM("msp");__regMainStackPointer = topOfMainStack;

}/** \brief Get Priority MaskThis function returns the current state of the priority mask bit from the Priority Mask Register.\return Priority Mask value*/

__STATIC_INLINE uint32_t __get_PRIMASK(void)

{register uint32_t __regPriMask __ASM("primask");return(__regPriMask);

}/** \brief Set Priority MaskThis function assigns the given value to the Priority Mask Register.\param [in] priMask Priority Mask*/

__STATIC_INLINE void __set_PRIMASK(uint32_t priMask)

{register uint32_t __regPriMask __ASM("primask");__regPriMask = (priMask);

}#if (__CORTEX_M >= 0x03)/** \brief Enable FIQThis function enables FIQ interrupts by clearing the F-bit in the CPSR.Can only be executed in Privileged modes.*/

#define __enable_fault_irq __enable_fiq/** \brief Disable FIQThis function disables FIQ interrupts by setting the F-bit in the CPSR.Can only be executed in Privileged modes.*/

#define __disable_fault_irq __disable_fiq/** \brief Get Base PriorityThis function returns the current value of the Base Priority register.\return Base Priority register value*/

__STATIC_INLINE uint32_t __get_BASEPRI(void)

{register uint32_t __regBasePri __ASM("basepri");return(__regBasePri);

}/** \brief Set Base PriorityThis function assigns the given value to the Base Priority register.\param [in] basePri Base Priority value to set*/

__STATIC_INLINE void __set_BASEPRI(uint32_t basePri)

{register uint32_t __regBasePri __ASM("basepri");__regBasePri = (basePri & 0xff);

}/** \brief Get Fault MaskThis function returns the current value of the Fault Mask register.\return Fault Mask register value*/

__STATIC_INLINE uint32_t __get_FAULTMASK(void)

{register uint32_t __regFaultMask __ASM("faultmask");return(__regFaultMask);

}/** \brief Set Fault MaskThis function assigns the given value to the Fault Mask register.\param [in] faultMask Fault Mask value to set*/

__STATIC_INLINE void __set_FAULTMASK(uint32_t faultMask)

{register uint32_t __regFaultMask __ASM("faultmask");__regFaultMask = (faultMask & (uint32_t)1);

}#endif /* (__CORTEX_M >= 0x03) */#if (__CORTEX_M == 0x04)/** \brief Get FPSCRThis function returns the current value of the Floating Point Status/Control register.\return Floating Point Status/Control register value*/

__STATIC_INLINE uint32_t __get_FPSCR(void)

{

#if (__FPU_PRESENT == 1) && (__FPU_USED == 1)register uint32_t __regfpscr __ASM("fpscr");return(__regfpscr);

#elsereturn(0);

#endif

}/** \brief Set FPSCRThis function assigns the given value to the Floating Point Status/Control register.\param [in] fpscr Floating Point Status/Control value to set*/

__STATIC_INLINE void __set_FPSCR(uint32_t fpscr)

{

#if (__FPU_PRESENT == 1) && (__FPU_USED == 1)register uint32_t __regfpscr __ASM("fpscr");__regfpscr = (fpscr);

#endif

}#endif /* (__CORTEX_M == 0x04) */#elif defined ( __ICCARM__ ) /*------------------ ICC Compiler -------------------*/

/* IAR iccarm specific functions */#include <cmsis_iar.h>#elif defined ( __TMS470__ ) /*---------------- TI CCS Compiler ------------------*/

/* TI CCS specific functions */#include <cmsis_ccs.h>#elif defined ( __GNUC__ ) /*------------------ GNU Compiler ---------------------*/

/* GNU gcc specific functions *//** \brief Enable IRQ InterruptsThis function enables IRQ interrupts by clearing the I-bit in the CPSR.Can only be executed in Privileged modes.*/

__attribute__( ( always_inline ) ) __STATIC_INLINE void __enable_irq(void)

{__ASM volatile ("cpsie i" : : : "memory");

}/** \brief Disable IRQ InterruptsThis function disables IRQ interrupts by setting the I-bit in the CPSR.Can only be executed in Privileged modes.*/

__attribute__( ( always_inline ) ) __STATIC_INLINE void __disable_irq(void)

{__ASM volatile ("cpsid i" : : : "memory");

}/** \brief Get Control RegisterThis function returns the content of the Control Register.\return Control Register value*/

__attribute__( ( always_inline ) ) __STATIC_INLINE uint32_t __get_CONTROL(void)

{uint32_t result;__ASM volatile ("MRS %0, control" : "=r" (result) );return(result);

}/** \brief Set Control RegisterThis function writes the given value to the Control Register.\param [in] control Control Register value to set*/

__attribute__( ( always_inline ) ) __STATIC_INLINE void __set_CONTROL(uint32_t control)

{__ASM volatile ("MSR control, %0" : : "r" (control) );

}/** \brief Get IPSR RegisterThis function returns the content of the IPSR Register.\return IPSR Register value*/

__attribute__( ( always_inline ) ) __STATIC_INLINE uint32_t __get_IPSR(void)

{uint32_t result;__ASM volatile ("MRS %0, ipsr" : "=r" (result) );return(result);

}/** \brief Get APSR RegisterThis function returns the content of the APSR Register.\return APSR Register value*/

__attribute__( ( always_inline ) ) __STATIC_INLINE uint32_t __get_APSR(void)

{uint32_t result;__ASM volatile ("MRS %0, apsr" : "=r" (result) );return(result);

}/** \brief Get xPSR RegisterThis function returns the content of the xPSR Register.\return xPSR Register value*/

__attribute__( ( always_inline ) ) __STATIC_INLINE uint32_t __get_xPSR(void)

{uint32_t result;__ASM volatile ("MRS %0, xpsr" : "=r" (result) );return(result);

}/** \brief Get Process Stack PointerThis function returns the current value of the Process Stack Pointer (PSP).\return PSP Register value*/

__attribute__( ( always_inline ) ) __STATIC_INLINE uint32_t __get_PSP(void)

{register uint32_t result;__ASM volatile ("MRS %0, psp\n" : "=r" (result) );return(result);

}/** \brief Set Process Stack PointerThis function assigns the given value to the Process Stack Pointer (PSP).\param [in] topOfProcStack Process Stack Pointer value to set*/

__attribute__( ( always_inline ) ) __STATIC_INLINE void __set_PSP(uint32_t topOfProcStack)

{__ASM volatile ("MSR psp, %0\n" : : "r" (topOfProcStack) );

}/** \brief Get Main Stack PointerThis function returns the current value of the Main Stack Pointer (MSP).\return MSP Register value*/

__attribute__( ( always_inline ) ) __STATIC_INLINE uint32_t __get_MSP(void)

{register uint32_t result;__ASM volatile ("MRS %0, msp\n" : "=r" (result) );return(result);

}/** \brief Set Main Stack PointerThis function assigns the given value to the Main Stack Pointer (MSP).\param [in] topOfMainStack Main Stack Pointer value to set*/

__attribute__( ( always_inline ) ) __STATIC_INLINE void __set_MSP(uint32_t topOfMainStack)

{__ASM volatile ("MSR msp, %0\n" : : "r" (topOfMainStack) );

}/** \brief Get Priority MaskThis function returns the current state of the priority mask bit from the Priority Mask Register.\return Priority Mask value*/

__attribute__( ( always_inline ) ) __STATIC_INLINE uint32_t __get_PRIMASK(void)

{uint32_t result;__ASM volatile ("MRS %0, primask" : "=r" (result) );return(result);

}/** \brief Set Priority MaskThis function assigns the given value to the Priority Mask Register.\param [in] priMask Priority Mask*/

__attribute__( ( always_inline ) ) __STATIC_INLINE void __set_PRIMASK(uint32_t priMask)

{__ASM volatile ("MSR primask, %0" : : "r" (priMask) );

}#if (__CORTEX_M >= 0x03)/** \brief Enable FIQThis function enables FIQ interrupts by clearing the F-bit in the CPSR.Can only be executed in Privileged modes.*/

__attribute__( ( always_inline ) ) __STATIC_INLINE void __enable_fault_irq(void)

{__ASM volatile ("cpsie f" : : : "memory");

}/** \brief Disable FIQThis function disables FIQ interrupts by setting the F-bit in the CPSR.Can only be executed in Privileged modes.*/

__attribute__( ( always_inline ) ) __STATIC_INLINE void __disable_fault_irq(void)

{__ASM volatile ("cpsid f" : : : "memory");

}/** \brief Get Base PriorityThis function returns the current value of the Base Priority register.\return Base Priority register value*/

__attribute__( ( always_inline ) ) __STATIC_INLINE uint32_t __get_BASEPRI(void)

{uint32_t result;__ASM volatile ("MRS %0, basepri_max" : "=r" (result) );return(result);

}/** \brief Set Base PriorityThis function assigns the given value to the Base Priority register.\param [in] basePri Base Priority value to set*/

__attribute__( ( always_inline ) ) __STATIC_INLINE void __set_BASEPRI(uint32_t value)

{__ASM volatile ("MSR basepri, %0" : : "r" (value) );

}/** \brief Get Fault MaskThis function returns the current value of the Fault Mask register.\return Fault Mask register value*/

__attribute__( ( always_inline ) ) __STATIC_INLINE uint32_t __get_FAULTMASK(void)

{uint32_t result;__ASM volatile ("MRS %0, faultmask" : "=r" (result) );return(result);

}/** \brief Set Fault MaskThis function assigns the given value to the Fault Mask register.\param [in] faultMask Fault Mask value to set*/

__attribute__( ( always_inline ) ) __STATIC_INLINE void __set_FAULTMASK(uint32_t faultMask)

{__ASM volatile ("MSR faultmask, %0" : : "r" (faultMask) );

}#endif /* (__CORTEX_M >= 0x03) */#if (__CORTEX_M == 0x04)/** \brief Get FPSCRThis function returns the current value of the Floating Point Status/Control register.\return Floating Point Status/Control register value*/

__attribute__( ( always_inline ) ) __STATIC_INLINE uint32_t __get_FPSCR(void)

{

#if (__FPU_PRESENT == 1) && (__FPU_USED == 1)uint32_t result;__ASM volatile ("VMRS %0, fpscr" : "=r" (result) );return(result);

#elsereturn(0);

#endif

}/** \brief Set FPSCRThis function assigns the given value to the Floating Point Status/Control register.\param [in] fpscr Floating Point Status/Control value to set*/

__attribute__( ( always_inline ) ) __STATIC_INLINE void __set_FPSCR(uint32_t fpscr)

{

#if (__FPU_PRESENT == 1) && (__FPU_USED == 1)__ASM volatile ("VMSR fpscr, %0" : : "r" (fpscr) );

#endif

}#endif /* (__CORTEX_M == 0x04) */#elif defined ( __TASKING__ ) /*------------------ TASKING Compiler --------------*/

/* TASKING carm specific functions *//** The CMSIS functions have been implemented as intrinsics in the compiler.* Please use "carm -?i" to get an up to date list of all instrinsics,* Including the CMSIS ones.*/#endif/*@} end of CMSIS_Core_RegAccFunctions */#endif /* __CORE_CMFUNC_H *//**************************************************************************//*** @file core_cmInstr.h* @brief CMSIS Cortex-M Core Instruction Access Header File* @version V3.02* @date 08. May 2012** @note* Copyright (C) 2009-2012 ARM Limited. All rights reserved.** @par* ARM Limited (ARM) is supplying this software for use with Cortex-M* processor based microcontrollers. This file can be freely distributed* within development tools that are supporting such ARM based processors.** @par* THIS SOFTWARE IS PROVIDED "AS IS". NO WARRANTIES, WHETHER EXPRESS, IMPLIED* OR STATUTORY, INCLUDING, BUT NOT LIMITED TO, IMPLIED WARRANTIES OF* MERCHANTABILITY AND FITNESS FOR A PARTICULAR PURPOSE APPLY TO THIS SOFTWARE.* ARM SHALL NOT, IN ANY CIRCUMSTANCES, BE LIABLE FOR SPECIAL, INCIDENTAL, OR* CONSEQUENTIAL DAMAGES, FOR ANY REASON WHATSOEVER.*******************************************************************************/#ifndef __CORE_CMINSTR_H

#define __CORE_CMINSTR_H/* ########################## Core Instruction Access ######################### */

/** \defgroup CMSIS_Core_InstructionInterface CMSIS Core Instruction InterfaceAccess to dedicated instructions@{

*/#if defined ( __CC_ARM ) /*------------------RealView Compiler -----------------*/

/* ARM armcc specific functions */#if (__ARMCC_VERSION < 400677)#error "Please use ARM Compiler Toolchain V4.0.677 or later!"

#endif/** \brief No OperationNo Operation does nothing. This instruction can be used for code alignment purposes.*/

#define __NOP __nop/** \brief Wait For InterruptWait For Interrupt is a hint instruction that suspends executionuntil one of a number of events occurs.*/

#define __WFI __wfi/** \brief Wait For EventWait For Event is a hint instruction that permits the processor to entera low-power state until one of a number of events occurs.*/

#define __WFE __wfe/** \brief Send EventSend Event is a hint instruction. It causes an event to be signaled to the CPU.*/

#define __SEV __sev/** \brief Instruction Synchronization BarrierInstruction Synchronization Barrier flushes the pipeline in the processor,so that all instructions following the ISB are fetched from cache ormemory, after the instruction has been completed.*/

#define __ISB() __isb(0xF)/** \brief Data Synchronization BarrierThis function acts as a special kind of Data Memory Barrier.It completes when all explicit memory accesses before this instruction complete.*/

#define __DSB() __dsb(0xF)/** \brief Data Memory BarrierThis function ensures the apparent order of the explicit memory operations beforeand after the instruction, without ensuring their completion.*/

#define __DMB() __dmb(0xF)/** \brief Reverse byte order (32 bit)This function reverses the byte order in integer value.\param [in] value Value to reverse\return Reversed value*/

#define __REV __rev/** \brief Reverse byte order (16 bit)This function reverses the byte order in two unsigned short values.\param [in] value Value to reverse\return Reversed value*/

#ifndef __NO_EMBEDDED_ASM

__attribute__((section(".rev16_text"))) __STATIC_INLINE __ASM uint32_t __REV16(uint32_t value)

{rev16 r0, r0bx lr

}

#endif/** \brief Reverse byte order in signed short valueThis function reverses the byte order in a signed short value with sign extension to integer.\param [in] value Value to reverse\return Reversed value*/

#ifndef __NO_EMBEDDED_ASM

__attribute__((section(".revsh_text"))) __STATIC_INLINE __ASM int32_t __REVSH(int32_t value)

{revsh r0, r0bx lr

}

#endif/** \brief Rotate Right in unsigned value (32 bit)This function Rotate Right (immediate) provides the value of the contents of a register rotated by a variable number of bits.\param [in] value Value to rotate\param [in] value Number of Bits to rotate\return Rotated value*/

#define __ROR __ror#if (__CORTEX_M >= 0x03)/** \brief Reverse bit order of valueThis function reverses the bit order of the given value.\param [in] value Value to reverse\return Reversed value*/

#define __RBIT __rbit/** \brief LDR Exclusive (8 bit)This function performs a exclusive LDR command for 8 bit value.\param [in] ptr Pointer to data\return value of type uint8_t at (*ptr)*/

#define __LDREXB(ptr) ((uint8_t ) __ldrex(ptr))/** \brief LDR Exclusive (16 bit)This function performs a exclusive LDR command for 16 bit values.\param [in] ptr Pointer to data\return value of type uint16_t at (*ptr)*/

#define __LDREXH(ptr) ((uint16_t) __ldrex(ptr))/** \brief LDR Exclusive (32 bit)This function performs a exclusive LDR command for 32 bit values.\param [in] ptr Pointer to data\return value of type uint32_t at (*ptr)*/

#define __LDREXW(ptr) ((uint32_t ) __ldrex(ptr))/** \brief STR Exclusive (8 bit)This function performs a exclusive STR command for 8 bit values.\param [in] value Value to store\param [in] ptr Pointer to location\return 0 Function succeeded\return 1 Function failed*/

#define __STREXB(value, ptr) __strex(value, ptr)/** \brief STR Exclusive (16 bit)This function performs a exclusive STR command for 16 bit values.\param [in] value Value to store\param [in] ptr Pointer to location\return 0 Function succeeded\return 1 Function failed*/

#define __STREXH(value, ptr) __strex(value, ptr)/** \brief STR Exclusive (32 bit)This function performs a exclusive STR command for 32 bit values.\param [in] value Value to store\param [in] ptr Pointer to location\return 0 Function succeeded\return 1 Function failed*/

#define __STREXW(value, ptr) __strex(value, ptr)/** \brief Remove the exclusive lockThis function removes the exclusive lock which is created by LDREX.*/

#define __CLREX __clrex/** \brief Signed SaturateThis function saturates a signed value.\param [in] value Value to be saturated\param [in] sat Bit position to saturate to (1..32)\return Saturated value*/

#define __SSAT __ssat/** \brief Unsigned SaturateThis function saturates an unsigned value.\param [in] value Value to be saturated\param [in] sat Bit position to saturate to (0..31)\return Saturated value*/

#define __USAT __usat/** \brief Count leading zerosThis function counts the number of leading zeros of a data value.\param [in] value Value to count the leading zeros\return number of leading zeros in value*/

#define __CLZ __clz#endif /* (__CORTEX_M >= 0x03) */#elif defined ( __ICCARM__ ) /*------------------ ICC Compiler -------------------*/

/* IAR iccarm specific functions */#include <cmsis_iar.h>#elif defined ( __TMS470__ ) /*---------------- TI CCS Compiler ------------------*/

/* TI CCS specific functions */#include <cmsis_ccs.h>#elif defined ( __GNUC__ ) /*------------------ GNU Compiler ---------------------*/

/* GNU gcc specific functions *//** \brief No OperationNo Operation does nothing. This instruction can be used for code alignment purposes.*/

__attribute__( ( always_inline ) ) __STATIC_INLINE void __NOP(void)

{__ASM volatile ("nop");

}/** \brief Wait For InterruptWait For Interrupt is a hint instruction that suspends executionuntil one of a number of events occurs.*/

__attribute__( ( always_inline ) ) __STATIC_INLINE void __WFI(void)

{__ASM volatile ("wfi");

}/** \brief Wait For EventWait For Event is a hint instruction that permits the processor to entera low-power state until one of a number of events occurs.*/

__attribute__( ( always_inline ) ) __STATIC_INLINE void __WFE(void)

{__ASM volatile ("wfe");

}/** \brief Send EventSend Event is a hint instruction. It causes an event to be signaled to the CPU.*/

__attribute__( ( always_inline ) ) __STATIC_INLINE void __SEV(void)

{__ASM volatile ("sev");

}/** \brief Instruction Synchronization BarrierInstruction Synchronization Barrier flushes the pipeline in the processor,so that all instructions following the ISB are fetched from cache ormemory, after the instruction has been completed.*/

__attribute__( ( always_inline ) ) __STATIC_INLINE void __ISB(void)

{__ASM volatile ("isb");

}/** \brief Data Synchronization BarrierThis function acts as a special kind of Data Memory Barrier.It completes when all explicit memory accesses before this instruction complete.*/

__attribute__( ( always_inline ) ) __STATIC_INLINE void __DSB(void)

{__ASM volatile ("dsb");

}/** \brief Data Memory BarrierThis function ensures the apparent order of the explicit memory operations beforeand after the instruction, without ensuring their completion.*/

__attribute__( ( always_inline ) ) __STATIC_INLINE void __DMB(void)

{__ASM volatile ("dmb");

}/** \brief Reverse byte order (32 bit)This function reverses the byte order in integer value.\param [in] value Value to reverse\return Reversed value*/

__attribute__( ( always_inline ) ) __STATIC_INLINE uint32_t __REV(uint32_t value)

{uint32_t result;__ASM volatile ("rev %0, %1" : "=r" (result) : "r" (value) );return(result);

}/** \brief Reverse byte order (16 bit)This function reverses the byte order in two unsigned short values.\param [in] value Value to reverse\return Reversed value*/

__attribute__( ( always_inline ) ) __STATIC_INLINE uint32_t __REV16(uint32_t value)

{uint32_t result;__ASM volatile ("rev16 %0, %1" : "=r" (result) : "r" (value) );return(result);

}/** \brief Reverse byte order in signed short valueThis function reverses the byte order in a signed short value with sign extension to integer.\param [in] value Value to reverse\return Reversed value*/

__attribute__( ( always_inline ) ) __STATIC_INLINE int32_t __REVSH(int32_t value)

{uint32_t result;__ASM volatile ("revsh %0, %1" : "=r" (result) : "r" (value) );return(result);

}/** \brief Rotate Right in unsigned value (32 bit)This function Rotate Right (immediate) provides the value of the contents of a register rotated by a variable number of bits.\param [in] value Value to rotate\param [in] value Number of Bits to rotate\return Rotated value*/

__attribute__( ( always_inline ) ) __STATIC_INLINE uint32_t __ROR(uint32_t op1, uint32_t op2)

{__ASM volatile ("ror %0, %0, %1" : "+r" (op1) : "r" (op2) );return(op1);

}#if (__CORTEX_M >= 0x03)/** \brief Reverse bit order of valueThis function reverses the bit order of the given value.\param [in] value Value to reverse\return Reversed value*/

__attribute__( ( always_inline ) ) __STATIC_INLINE uint32_t __RBIT(uint32_t value)

{uint32_t result;__ASM volatile ("rbit %0, %1" : "=r" (result) : "r" (value) );return(result);

}/** \brief LDR Exclusive (8 bit)This function performs a exclusive LDR command for 8 bit value.\param [in] ptr Pointer to data\return value of type uint8_t at (*ptr)*/

__attribute__( ( always_inline ) ) __STATIC_INLINE uint8_t __LDREXB(volatile uint8_t *addr)

{uint8_t result;__ASM volatile ("ldrexb %0, [%1]" : "=r" (result) : "r" (addr) );return(result);

}/** \brief LDR Exclusive (16 bit)This function performs a exclusive LDR command for 16 bit values.\param [in] ptr Pointer to data\return value of type uint16_t at (*ptr)*/

__attribute__( ( always_inline ) ) __STATIC_INLINE uint16_t __LDREXH(volatile uint16_t *addr)

{uint16_t result;__ASM volatile ("ldrexh %0, [%1]" : "=r" (result) : "r" (addr) );return(result);

}/** \brief LDR Exclusive (32 bit)This function performs a exclusive LDR command for 32 bit values.\param [in] ptr Pointer to data\return value of type uint32_t at (*ptr)*/

__attribute__( ( always_inline ) ) __STATIC_INLINE uint32_t __LDREXW(volatile uint32_t *addr)

{uint32_t result;__ASM volatile ("ldrex %0, [%1]" : "=r" (result) : "r" (addr) );return(result);

}/** \brief STR Exclusive (8 bit)This function performs a exclusive STR command for 8 bit values.\param [in] value Value to store\param [in] ptr Pointer to location\return 0 Function succeeded\return 1 Function failed*/

__attribute__( ( always_inline ) ) __STATIC_INLINE uint32_t __STREXB(uint8_t value, volatile uint8_t *addr)

{uint32_t result;__ASM volatile ("strexb %0, %2, [%1]" : "=&r" (result) : "r" (addr), "r" (value) );return(result);

}/** \brief STR Exclusive (16 bit)This function performs a exclusive STR command for 16 bit values.\param [in] value Value to store\param [in] ptr Pointer to location\return 0 Function succeeded\return 1 Function failed*/

__attribute__( ( always_inline ) ) __STATIC_INLINE uint32_t __STREXH(uint16_t value, volatile uint16_t *addr)

{uint32_t result;__ASM volatile ("strexh %0, %2, [%1]" : "=&r" (result) : "r" (addr), "r" (value) );return(result);

}/** \brief STR Exclusive (32 bit)This function performs a exclusive STR command for 32 bit values.\param [in] value Value to store\param [in] ptr Pointer to location\return 0 Function succeeded\return 1 Function failed*/

__attribute__( ( always_inline ) ) __STATIC_INLINE uint32_t __STREXW(uint32_t value, volatile uint32_t *addr)

{uint32_t result;__ASM volatile ("strex %0, %2, [%1]" : "=&r" (result) : "r" (addr), "r" (value) );return(result);

}/** \brief Remove the exclusive lockThis function removes the exclusive lock which is created by LDREX.*/

__attribute__( ( always_inline ) ) __STATIC_INLINE void __CLREX(void)

{__ASM volatile ("clrex");

}/** \brief Signed SaturateThis function saturates a signed value.\param [in] value Value to be saturated\param [in] sat Bit position to saturate to (1..32)\return Saturated value*/

#define __SSAT(ARG1,ARG2) \

({ \uint32_t __RES, __ARG1 = (ARG1); \__ASM ("ssat %0, %1, %2" : "=r" (__RES) : "I" (ARG2), "r" (__ARG1) ); \__RES; \})/** \brief Unsigned SaturateThis function saturates an unsigned value.\param [in] value Value to be saturated\param [in] sat Bit position to saturate to (0..31)\return Saturated value*/

#define __USAT(ARG1,ARG2) \

({ \uint32_t __RES, __ARG1 = (ARG1); \__ASM ("usat %0, %1, %2" : "=r" (__RES) : "I" (ARG2), "r" (__ARG1) ); \__RES; \})/** \brief Count leading zerosThis function counts the number of leading zeros of a data value.\param [in] value Value to count the leading zeros\return number of leading zeros in value*/

__attribute__( ( always_inline ) ) __STATIC_INLINE uint8_t __CLZ(uint32_t value)

{uint8_t result;__ASM volatile ("clz %0, %1" : "=r" (result) : "r" (value) );return(result);

}#endif /* (__CORTEX_M >= 0x03) */#elif defined ( __TASKING__ ) /*------------------ TASKING Compiler --------------*/

/* TASKING carm specific functions *//** The CMSIS functions have been implemented as intrinsics in the compiler.* Please use "carm -?i" to get an up to date list of all intrinsics,* Including the CMSIS ones.*/#endif/*@}*/ /* end of group CMSIS_Core_InstructionInterface */#endif /* __CORE_CMINSTR_H */

相关文章:

error: #5: cannot open source input file “core_cmInstr.h“

GD32F103VET6和STM32F103VET6引脚兼容。 GD32F103VET6工程模板需要包含头文件:core_cmInstr.h和core_cmFunc.h,这个和STM32F103还是有区别的,否则会报错,如下: error: #5: cannot open source input file "core…...

FastAPI 教程、结合vue实现前后端分离

英文版文档:https://fastapi.tiangolo.com/ 中文版文档:https://fastapi.tiangolo.com/zh/ 1、FastAPI 教程 简 介 FastAPI 和 Sanic 类似,都是 Python 中的异步 web 框架。相比 Sanic,FastAPI 更加的成熟、社区也更加的活跃。 …...

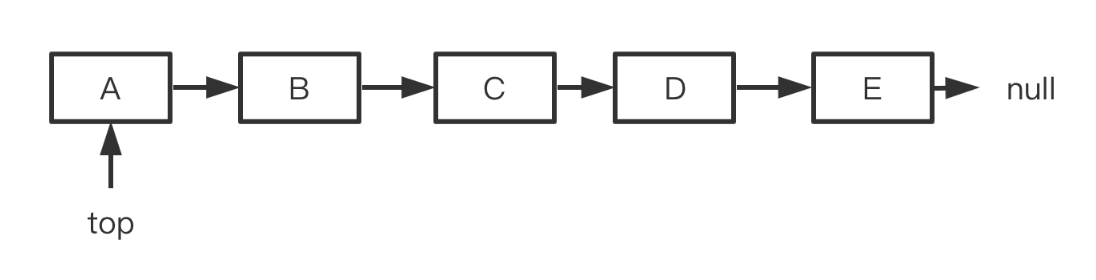

算法通关村第四关——如何基于数组(链表)实现栈

栈的基础知识 栈的特征 特征1 栈和队列是比较特殊的线性表,又被称为 访问受限的线性表。栈是很多表达式、符号等运算的基础,也是递归的底层实现(递归就是方法自己调用自己,在JVM的虚拟机栈中,一个线程中的栈帧就是…...

Postgresql警告日志的配置

文章目录 1.postgresql与日志有关的参数2.开启日志3.指定日志目录4.設置文件名format5.設置日志文件產出模式6.設置日志记录格式7.日誌輪換7.1非截斷式輪換7.2 截斷式輪換 8.日誌記錄內容8.1 log_statement8.2 log_min_duration_statement 9 輸出範本 1.postgresql与日志有关的…...

Java、JSAPI、 ssm架构 微信支付demo

1.前端 index.html <%page import"com.tenpay.configure.WxPayConfig"%> <% page language"java" contentType"text/html; charsetUTF-8" pageEncoding"UTF-8"%> <html><style>#fukuan{font-size: 50px;marg…...

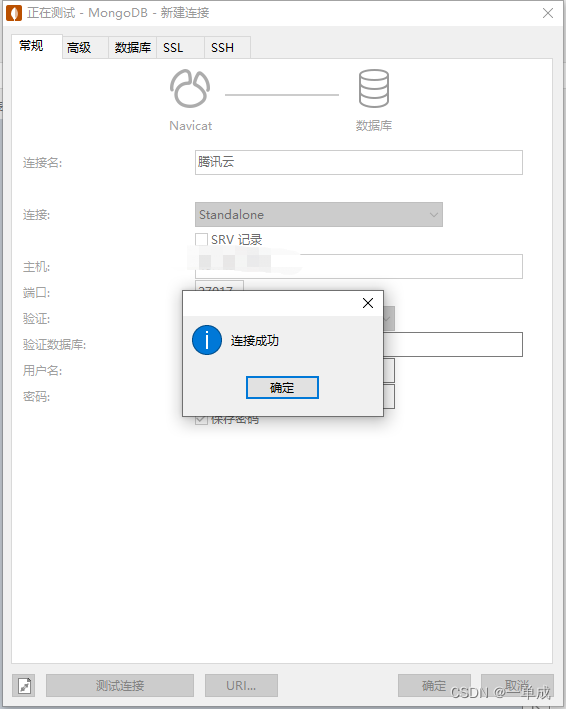

MongoDB文档--基本安装-linux安装(mongodb环境搭建)-docker安装(挂载数据卷)-以及详细版本对比

阿丹: 前面了解了mongodb的一些基本概念。本节文章对安装mongodb进行讲解以及汇总。 官网教程如下: 安装 MongoDB - MongoDB-CN-Manual 版本特性 下面是各个版本的选择请在安装以及选择版本的时候参考一下: MongoDB 2.x 版本:…...

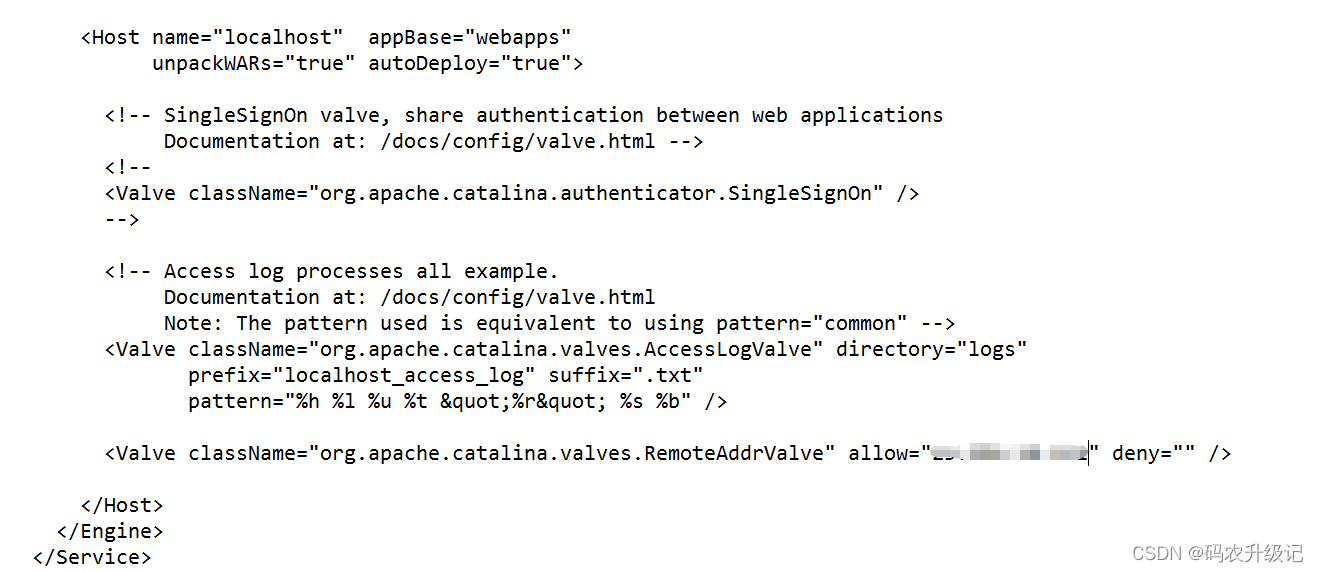

tomcat限制IP访问

tomcat可以通过增加配置,来对来源ip进行限制,即只允许某些ip访问或禁止某些来源ip访问。 配置路径:server.xml 文件下 标签下。与同级 <Valve className"org.apache.catalina.valves.RemoteAddrValve" allow"192.168.x.x&…...

互联网宠物医院系统开发:数字化时代下宠物医疗的革新之路

随着人们对宠物关爱意识的提高,宠物医疗服务的需求也日益增加。传统的宠物医院存在排队等待、预约难、信息不透明等问题,给宠物主人带来了诸多不便。而互联网宠物医院系统的开发,则可以带来许多便利和好处。下面将介绍互联网宠物医院系统开发…...

docker镜像批量导出导入

docker镜像批量导出导入 image_tar为存储镜像目录 删除所有容器 一、首先需要停止所有运行中的容器 docker stopdocker ps -a -q docker ps -a -q 意思是列出所有容器(包括未运行的),只显示容器编号,其中 -a : 显示所有的容器&…...

宇凡微2.4g遥控船开发方案,采用合封芯片

2.4GHz遥控船的开发方案是一个有趣且具有挑战性的项目。这样的遥控船可以通过无线2.4GHz频率进行远程控制,让用户在池塘或湖泊上畅游。以下是一个简要的2.4GHz遥控船开发方案: 基本构想如下 mcu驱动两个小电机,小电机上安装两个螺旋桨&#…...

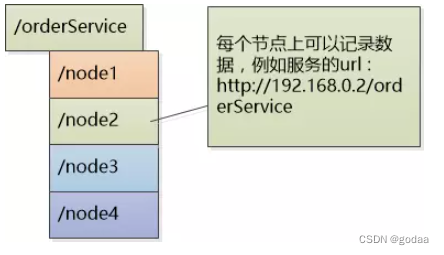

RPC框架引入zookeeper服务注册与服务发现

Zookeeper概念及其作用 ZooKeeper是一个分布式的,开放源码的分布式应用程序协调服务,是Google的Chubby一个开源的实现,是大数据生态中的重要组件。它是集群的管理者,监视着集群中各个节点的状态根据节点提交的反馈进行下一步合理…...

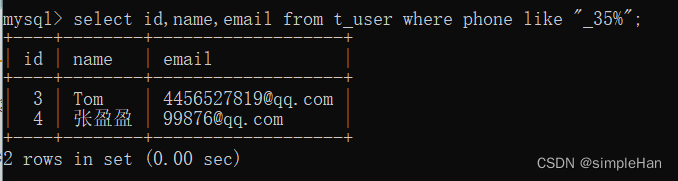

MySQL用通配符过滤数据

简单的不使用通配符过滤数据的方式使用的值都是已知的,但是当搜索产品名中包含ashui的所有产品时,用简单的比较操作符肯定不行,必须使用通配符。利用通配符可以创建比较特定数据的搜索模式。 通配符:用来匹配值的一部分的特殊字符…...

低通、高通、带通、阻通滤波器

目录 低通、高通、带通、阻通滤波器 低通、高通、带通、带阻滤波器的区别 通俗理解: 1、低通滤波器 2、高通滤波器 3、带通滤波器 4、带阻滤波器 5、全通滤波器 低通、高通、带通、阻通滤波器 低通、高通、带通、带阻滤波器的区别 低通滤波器:只…...

IDEA SpringBoot Maven profiles 配置

IDEA SpringBoot Maven profiles 配置 IDEA版本: IntelliJ IDEA 2022.2.3 注意:切换环境之后务必点击一下刷新,推荐点击耗时更短。 application.yaml spring:profiles:active: env多环境文件名: application-dev.yaml、 applicat…...

微信小程序 背景图片如何占满整个屏幕

1. 在页面的wxss文件中,设置背景图片的样式: page{background-image: url(图片路径);background-size: 100% 100%;background-repeat: no-repeat; } 2. 在页面的json文件中,设置背景图片的样式: {"backgroundTextStyle&qu…...

邪恶版ChatGPT来了!

「邪恶版」ChatGPT 出现:每月 60 欧元,毫无道德限制,专为“网络罪犯”而生。 WormGPT 并不是一个人工智能聊天机器人,它的开发目的不是为了有趣地提供无脊椎动物的人工智能帮助,就像专注于猫科动物的CatGPT一样。相反&…...

一、Postfix[安装与配置、smtp认证、Python发送邮件以及防垃圾邮件方法、使用腾讯云邮件服务]

Debian 11 一、安装 apt install postfix 二、配置 1.dns配置 解释:搭建真实的邮件服务器需要在DNS提供商那里配置下面的dns 配置A记录mail.www.com-1.x.x.x配置MX记录www.com-mail.www.com 解释:按照上面的配置通常邮件格式就是adminwww.com其通过…...

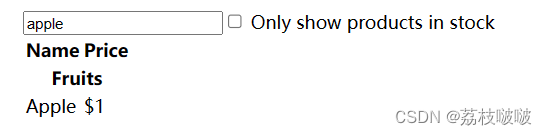

React哲学——官方示例

在本篇技术博客中,我们将介绍React官方示例:React哲学。我们将深入探讨这个示例中使用的组件化、状态管理和数据流等核心概念。让我们一起开始吧! 项目概览 React是一个流行的JavaScript库,用于构建用户界面。React的设计理念是…...

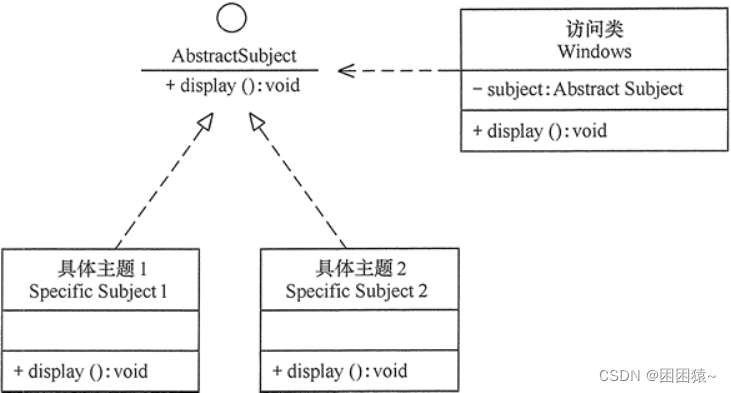

设计模式之开闭原则

什么是开闭原则? 开放封闭原则称为OCP原则(Open Closed Principle)是所有面向对象原则的核心。 “开闭原则”是面向对象编程中最基础和最重要的设计原则之一。 软件设计本身所追求的目标就是封装变化、降低耦合,而开放封闭原则正是对这一…...

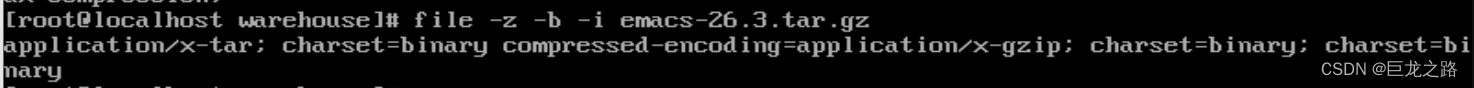

Linux中的file命令:查看文件类型

2023年8月1日,周二上午 目录 简要说明使用方法MIME类型举例说明 简要说明 在Linux中,file命令用于识别文件类型。 file命令可以识别各种类型的文件,包括普通文件、目录、符号链接、设备文件、压缩文件、二进制可执行文件等。 它是一个非常…...

SEO_ 揭秘影响搜索引擎排名的核心SEO因素

SEO的核心因素解析:提升搜索引擎排名的关键路径 在当今数字化时代,搜索引擎优化(SEO)已经成为每个网站和企业获取有效流量的重要途径。究竟有哪些核心因素影响搜索引擎的排名呢?本文将深入探讨这些核心SEO因素&#x…...

绝地求生游戏辅助工具:罗技鼠标宏自动化配置指南

绝地求生游戏辅助工具:罗技鼠标宏自动化配置指南 【免费下载链接】logitech-pubg PUBG no recoil script for Logitech gaming mouse / 绝地求生 罗技 鼠标宏 项目地址: https://gitcode.com/gh_mirrors/lo/logitech-pubg 在《绝地求生》这款高强度的战术竞技…...

避坑指南:在华为Atlas 200DK A2上部署YOLOv8-pose模型前,如何用ONNX Runtime在CPU/GPU上验证推理流程

边缘部署前的关键验证:YOLOv8-pose模型在CPU/GPU环境下的ONNX Runtime推理实战 在AI模型边缘部署的实践中,一个经常被忽视却至关重要的环节是本地验证。许多工程师在将模型部署到华为Atlas 200DK A2等边缘设备时,常常跳过这一步骤直接进入板端…...

)

自动驾驶开发必备:Vscode+Git双神器组合的隐藏技巧(含分支管理秘籍)

自动驾驶开发必备:VscodeGit双神器组合的隐藏技巧(含分支管理秘籍) 在自动驾驶开发领域,高效的代码管理和协作流程是项目成功的关键因素。随着代码库规模不断扩大,团队规模持续增长,传统的版本控制方式往往…...

SEO优化对网站收录有什么作用

SEO优化对网站收录有什么作用 在当今互联网信息爆炸的时代,网站的收录问题显得尤为重要。SEO优化对于网站的收录有着至关重要的作用,无论是对于新开的网站还是已经运营一段时间的网站,优化都能为其带来更多的流量和潜在客户。SEO优化对网站收…...

SEED数据集之外:脑电情感识别还有哪些开源数据集值得一试?

SEED数据集之外:脑电情感识别领域五大开源数据集深度评测 当我在实验室第一次尝试构建情感识别模型时,和大多数初学者一样,首先接触到的就是SEED数据集。但随着研究的深入,我逐渐发现这个领域远比想象中丰富——不同诱发范式、采集…...

TalkiePCM:嵌入式LPC语音合成库,纯C++轻量级PCM音频引擎

1. TalkiePCM:嵌入式平台上的轻量级LPC语音合成引擎TalkiePCM 是一个面向资源受限嵌入式系统的纯C语音合成库,其核心目标是在不依赖特定硬件外设(如PWM、DAC或I2S控制器)的前提下,以最小耦合方式生成标准PCM音频流。它…...

数字记忆自主化:GetQzonehistory技术架构与数据保护实践指南

数字记忆自主化:GetQzonehistory技术架构与数据保护实践指南 【免费下载链接】GetQzonehistory 获取QQ空间发布的历史说说 项目地址: https://gitcode.com/GitHub_Trending/ge/GetQzonehistory 一、技术演进视角下的数据脆弱性危机 数字存储技术的迭代速度与…...

深入Fly-By拓扑:为什么你的LPDDR4必须做Write Leveling?一次讲清时钟与数据对齐的核心原理

深入Fly-By拓扑:为什么你的LPDDR4必须做Write Leveling?一次讲清时钟与数据对齐的核心原理 在4266 Mbps的高速数据传输场景下,LPDDR4内存子系统如同一条需要精确调谐的八车道高速公路。当信号传输速率突破4GT/s时,皮秒级的时序偏差…...

Monaco-Editor插件使用小坑

无法通过鼠标进行选中文本<div id"monacoEditor" class"monacoEditor"></div>外层添加了splinter拖拽组件,导致mousemove事件被拦截,给monaco-editor添加css:pointer-events:auto.monacoEditor .…...