FPGA项目设计:数字时钟

项目要求:

设计一个数字时钟,数码管前两位显示小时,数码管中间两位显示分钟,数码管后面两位显示秒。

项目设计:

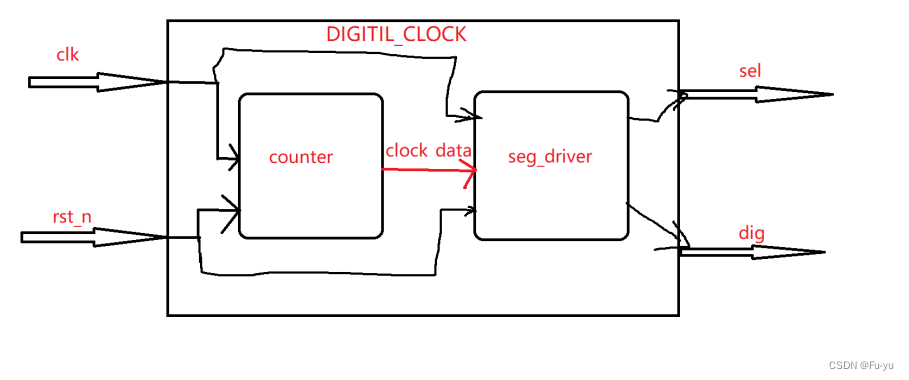

系统框架图:

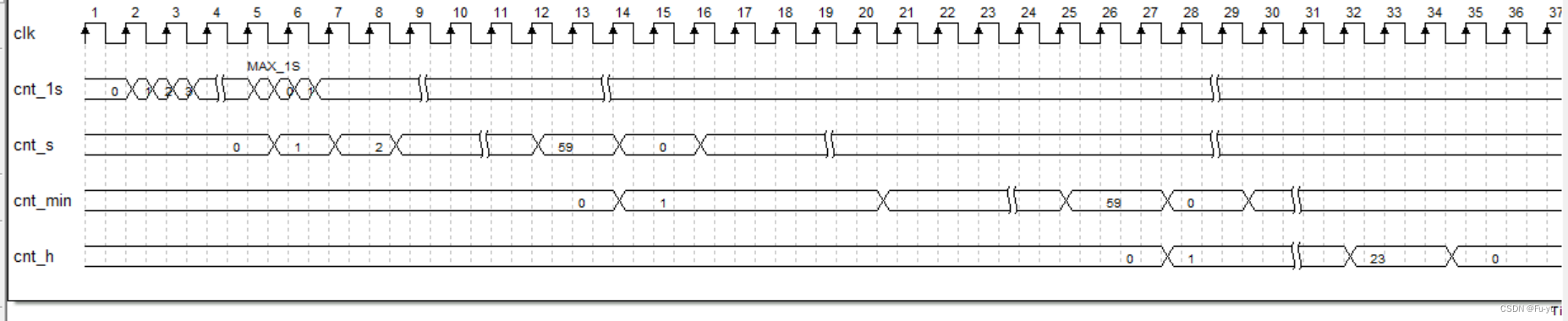

计数模块时序图:

代码实现:

计数模块:

/** @Description: 用于记数产生时钟* @Author: Fu Yu* @Date: 2023-08-02 11:16:46* @LastEditTime: 2023-08-02 15:23:14* @LastEditors: Fu Yu*/module counter (input wire clk ,input wire rst_n ,output wire [23:0] clock_data //输出时钟数值

);parameter MAX_1S = 26'd49_999_999;//1s

parameter MAX_S = 6'd59;//1S*60 = 1min

parameter MAX_MIN = 6'd59;//1min*60 = 1h

parameter MAX_H = 5'd23;//1h*24 = 1dlocalparam INIT_S = 40,//赋初值INIT_M = 58,INIT_H = 23;reg [25:0] cnt_1s;

reg [5:0] cnt_s;

reg [5:0] cnt_min;

reg [4:0] cnt_h;reg [3:0] time_s_low;

reg [3:0] time_s_high;

reg [3:0] time_min_low;

reg [3:0] time_min_high;

reg [3:0] time_h_low;

reg [3:0] time_h_high;wire add_cnt_1s;

wire end_cnt_1s;wire add_cnt_s;

wire end_cnt_s;wire add_cnt_min;

wire end_cnt_min;wire add_cnt_h;

wire end_cnt_h;//****************************************************************

//--1s计数器

//****************************************************************

always @(posedge clk or negedge rst_n) beginif(!rst_n) begincnt_1s <= 26'd0;endelse if(add_cnt_1s) beginif(end_cnt_1s) begincnt_1s <= 26'd0;endelse begincnt_1s <= cnt_1s + 1'd1;endendelse begincnt_1s <= cnt_1s;end

endassign add_cnt_1s = 1'b1;

assign end_cnt_1s = add_cnt_1s && cnt_1s == MAX_1S;//****************************************************************

//--秒计数器

//****************************************************************

always @(posedge clk or negedge rst_n) beginif(!rst_n) begincnt_s <= INIT_S;endelse if(add_cnt_s) beginif(end_cnt_s) begincnt_s <= 6'd0;endelse begincnt_s <= cnt_s + 1'd1;endendelse begincnt_s <= cnt_s;end

endassign add_cnt_s = end_cnt_1s;

assign end_cnt_s = add_cnt_s && cnt_s == MAX_S;//****************************************************************

//--分钟计数器

//****************************************************************

always @(posedge clk or negedge rst_n) beginif(!rst_n) begincnt_min <= INIT_M;endelse if(add_cnt_min) beginif(end_cnt_min) begincnt_min <= 6'd0;endelse begincnt_min <= cnt_min + 1'd1;endendelse begincnt_min <= cnt_min;end

endassign add_cnt_min = end_cnt_s;

assign end_cnt_min = add_cnt_min && cnt_min == MAX_MIN;//****************************************************************

//--小时计数器

//****************************************************************

always @(posedge clk or negedge rst_n) beginif(!rst_n) begincnt_h <= INIT_H;endelse if(add_cnt_h) beginif(end_cnt_h) begincnt_h <= 5'd0;endelse begincnt_h <= cnt_h + 1'd1;endendelse begincnt_h <= cnt_h;end

endassign add_cnt_h = end_cnt_min;

assign end_cnt_h = add_cnt_h && cnt_h == MAX_H;//****************************************************************

//--clock_data

//****************************************************************

always @(posedge clk or negedge rst_n) beginif(!rst_n) begintime_s_high <= 4'd0;time_s_low <= 4'd0;time_min_high <= 4'd0;time_min_low <= 4'b0;time_h_high <= 4'd0;time_h_low <= 4'd0;endelse begintime_h_high <= cnt_h/10;time_h_low <= cnt_h%10;time_min_high <= cnt_min/10;time_min_low <= cnt_min%10;time_s_high <= cnt_s/10;time_s_low <= cnt_s%10;end

endassign clock_data = {time_h_high,time_h_low,time_min_high,time_min_low,time_s_high,time_s_low};endmodule //counter

数码管显示模块:

/** @Description: 数码管显示模块,前两位显示时钟数据的小时,中间两位显示时间数据的分钟,最后两位显示时间数据的秒* @Author: Fu Yu* @Date: 2023-08-02 13:43:47* @LastEditTime: 2023-08-02 14:00:00* @LastEditors: Fu Yu*/module seg_driver (input wire clk ,input wire rst_n ,input wire [23:0] clock_data_in ,output wire [5:0] sel ,//位选信号output wire [7:0] dig //段选信号

);parameter MAX_1MS = 16'd49_999;//1msparameter ZERO = 7'b100_0000,ONE = 7'b111_1001,TWO = 7'b010_0100,THREE = 7'b011_0000,FOUR = 7'b001_1001,FIVE = 7'b001_0010,SIX = 7'b000_0010,SEVEN = 7'b111_1000,EIGHT = 7'b000_0000,NINE = 7'b001_0000;reg [5:0] sel_r;

reg [7:0] dig_r;

reg [5:0] point_n;//小数点

reg point_n_r;

reg [3:0] disp_data ;//每一位数码管显示的数值reg [15:0] cnt_1ms;

wire add_cnt_1ms;

wire end_cnt_1ms;//****************************************************************

//--1ms计数器

//****************************************************************

always @(posedge clk or negedge rst_n)begin if(!rst_n)begincnt_1ms <= 16'd0;end else if(add_cnt_1ms)begin if(end_cnt_1ms)begin cnt_1ms <= 16'd0;endelse begin cnt_1ms <= cnt_1ms + 1'b1;end end

end assign add_cnt_1ms = 1'b1;

assign end_cnt_1ms = add_cnt_1ms && cnt_1ms == MAX_1MS;//****************************************************************

//--point_n

//****************************************************************

always @(posedge clk or negedge rst_n) beginif(!rst_n) beginpoint_n <= 6'b111_111;endelse beginpoint_n <= 6'b110101;end

end//****************************************************************

//--sel

//****************************************************************

always @(posedge clk or negedge rst_n) beginif(!rst_n) beginsel_r <= 6'b111110;endelse if(end_cnt_1ms) beginsel_r <= {sel_r[4:0],sel_r[5]};endelse beginsel_r <= sel_r;end

endassign sel = sel_r;//****************************************************************

//-- disp_data

//****************************************************************

always @(posedge clk or negedge rst_n) beginif(!rst_n) begindisp_data <= 4'd0;point_n_r <= 1'b1;endelse begincase (sel_r)6'b111110 : begindisp_data <= clock_data_in[23:20];point_n_r <= point_n[0];end6'b111101 : begindisp_data <= clock_data_in[19:16];point_n_r <= point_n[1];end6'b111011 : begindisp_data <= clock_data_in[15:12];point_n_r <= point_n[2];end6'b110111 : begindisp_data <= clock_data_in[11:8];point_n_r <= point_n[3];end6'b101111 : begindisp_data <= clock_data_in[7:4];point_n_r <= point_n[4];end6'b011111 : begindisp_data <= clock_data_in[3:0];point_n_r <= point_n[5];endendcaseend

end//****************************************************************

//--dig

//****************************************************************

always @(*)begin case (disp_data)0 : dig_r <= {point_n_r,ZERO };1 : dig_r <= {point_n_r,ONE };2 : dig_r <= {point_n_r,TWO };3 : dig_r <= {point_n_r,THREE };4 : dig_r <= {point_n_r,FOUR };5 : dig_r <= {point_n_r,FIVE };6 : dig_r <= {point_n_r,SIX };7 : dig_r <= {point_n_r,SEVEN };8 : dig_r <= {point_n_r,EIGHT };9 : dig_r <= {point_n_r,NINE };default: dig_r <= 8'hff;endcaseendassign dig = dig_r;endmodule //seg_driver

顶层文件:

module top (input wire clk ,input wire rst_n ,output wire [5:0] sel ,output wire [7:0] dig

);wire [23:0] data;counter u_counter(. clk (clk) ,. rst_n (rst_n) ,. clock_data (data)

);seg_driver u_seg_driver (. clk (clk) ,. rst_n (rst_n) ,. clock_data_in (data),. sel (sel) ,. dig (dig)

);endmodule //top

相关文章:

FPGA项目设计:数字时钟

项目要求: 设计一个数字时钟,数码管前两位显示小时,数码管中间两位显示分钟,数码管后面两位显示秒。 项目设计: 系统框架图: 计数模块时序图: 代码实现: 计数模块: /…...

科技云报道:向量数据库:AI时代的下一个热点

科技云报道原创。 最近,又一个概念火了——向量数据库。 随着大模型带来的应用需求提升,4月以来多家海外知名向量数据库创业企业传出融资喜讯。 4月28日,向量数据库平台Pinecone宣布获得1亿美元(约7亿元)B轮融资&am…...

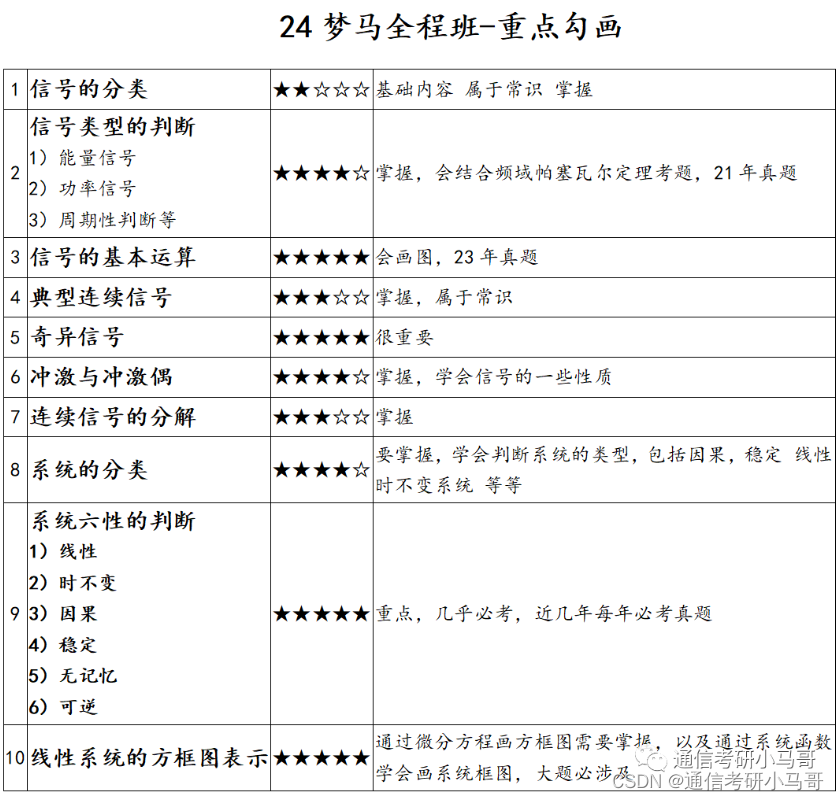

【更新】119所院校考研重点勾画更新预告!

截至目前,我已经发布了47篇不同院校的择校分析。发布了87套名校信号考研真题以及119所不同院校的考研知识点重点勾画。 另外为了更好服务已经报名的同学,24梦马全程班也到了收尾的阶段。即将封班!需要报名的同学抓紧啦! 去年开始…...

LRU算法(哈希链表法))

【Leetcode】(自食用)LRU算法(哈希链表法)

step by step. 题目: 请你设计并实现一个满足 LRU (最近最少使用) 缓存 约束的数据结构。 实现 LRUCache 类: LRUCache(int capacity) 以 正整数 作为容量 capacity 初始化 LRU 缓存int get(int key) 如果关键字 key 存在于缓存中,则返回关键…...

搜索引擎获取页面内容)

robots.txt 如何禁止蜘蛛(百度,360,搜狗,谷歌)搜索引擎获取页面内容

什么是蜘蛛抓取 搜索引擎使用spider程序自动访问互联网上的网页并获取网页信息。spider在访问一个网站时,会首先会检查该网站的根域下是否有一个叫做robots.txt的纯文本文件。您可以在您的网站中创建一个纯文本文件robots.txt,在文件中声明该网站中不想…...

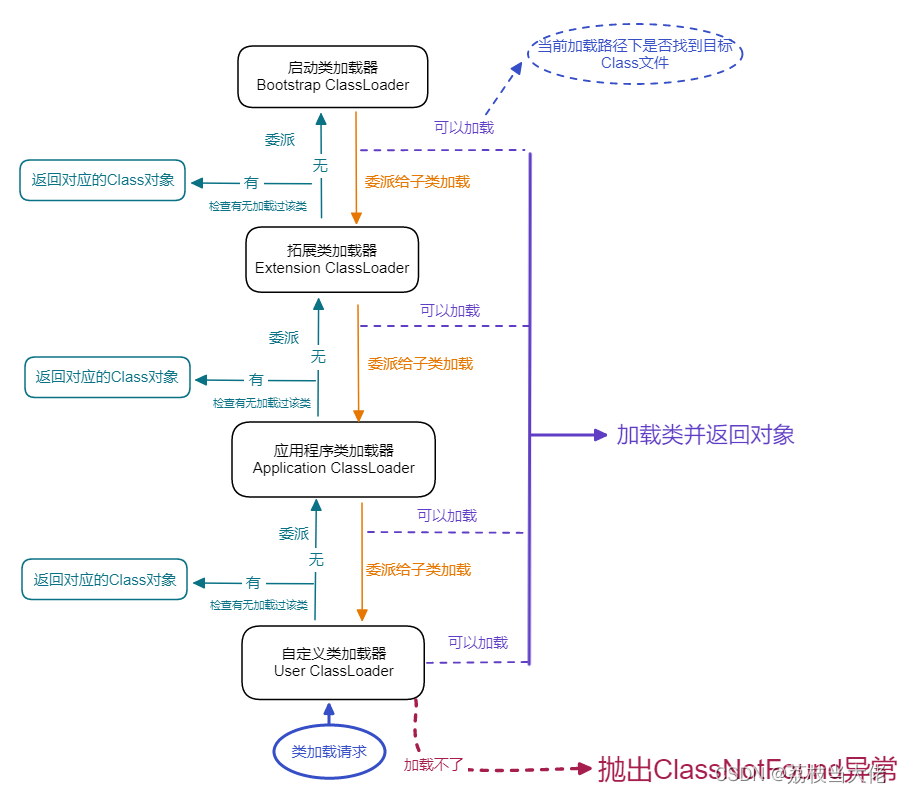

JVM 学习—— 类加载机制

前言 在上一篇文章中,荔枝梳理了有关Java中JVM体系架构的相关知识,其中涉及到的有关Java类加载机制的相关知识并没有过多描述。那么在这篇文章中,荔枝会详细梳理一下有关JVM的类加载机制和双亲委派模型的知识,希望能够帮助到有需要…...

C#实现int类型和字节流的相互在转化

通过TCP协议进行数据传输时,需要将所有传输的内容转为字节流,这里就用到了将int型的数据转为字节流的。代码如下: public static byte[] BytesConvertToInt(int vel) {byte[] hex new byte[4];hex[3] (byte)(vel >> 24) & 0xff)…...

Centos设置固定IP地址,外网访问

查看网络信息 一般会看到enp0s3的网络配置 ip address切换至网络配置路径 cd /etc/sysconfig/network-scripts/编辑配置 vi ifcfg-enp0s3 编辑配置 主要修改 静态ip:BOOTPROTOdhcp --> OOTPROTOstaticDNS(訪問外網):DNS1114.114.114.114本机ip: 192.168.70.121子网掩码…...

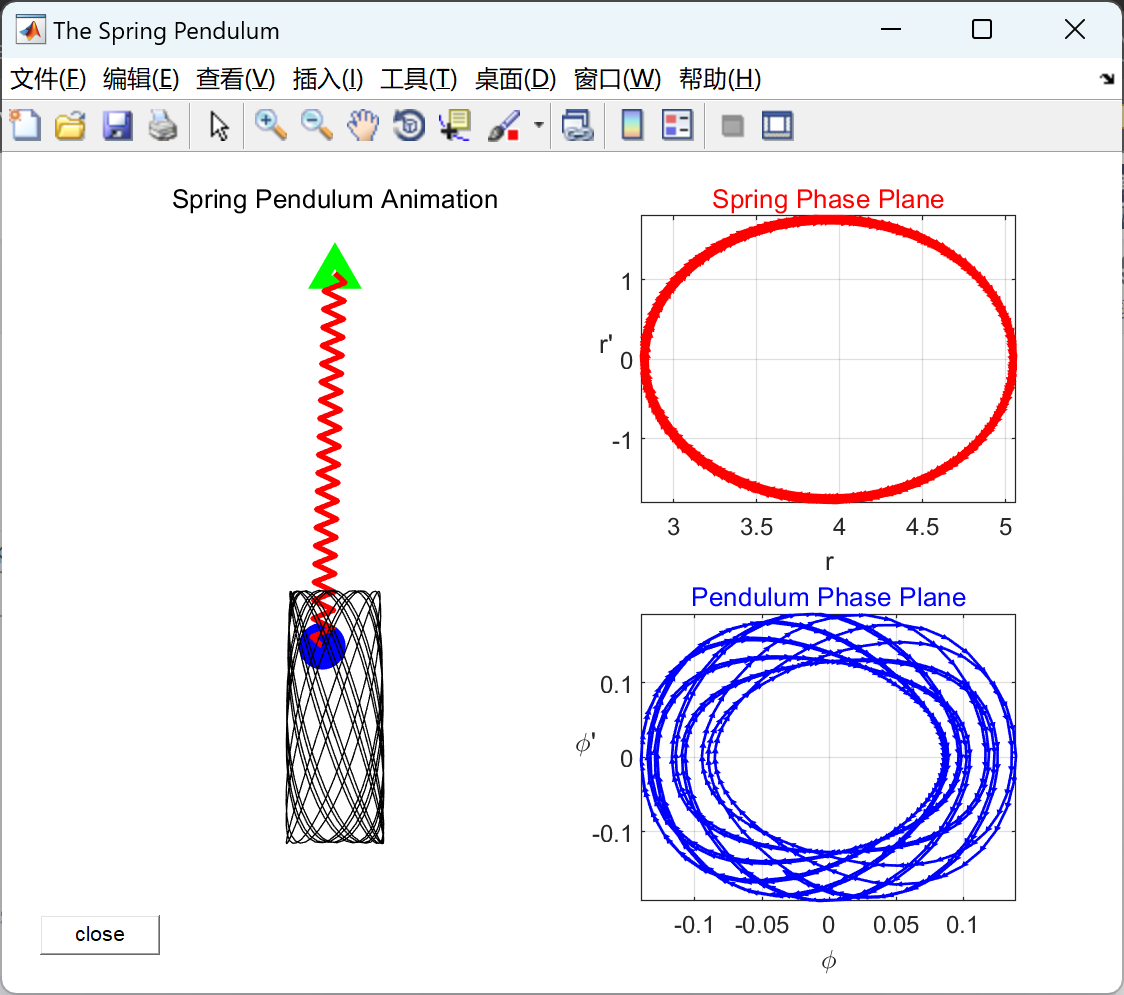

非线性弹簧摆的仿真(Matlab代码实现)

💥💥💞💞欢迎来到本博客❤️❤️💥💥 🏆博主优势:🌞🌞🌞博客内容尽量做到思维缜密,逻辑清晰,为了方便读者。 ⛳️座右铭&a…...

css实现文字颜色渐变+阴影

效果 代码 <div class"top"><div class"top-text" text"总经理驾驶舱">总经理驾驶舱</div> </div><style lang"scss" scoped>.top{width: 100%;text-align: center;height: 80px;line-height: 80px;fo…...

C++学习笔记总结练习:关联容器

关联容器 0 关联容器概述 关联容器与顺序容器的区别 关联容器和顺序容器有着根本不同。关联容器中的元素是按关键字来把偶才能和访问的。书序容器中的元素是按他们在容器中的位置来顺序保存和访问的。 两个基础类型 map:键值对key-value。关键字是索引,值表示与…...

)

TypeScript技能总结(二)

typescript是js的超集,目前很多前端框架都开始使用它来作为项目的维护管理的工具,还在不断地更新,添加新功能中,我们学习它,才能更好的在的项目中运用它,发挥它的最大功效 //readonly 只能修饰属性&#x…...

整理一些Postgresql工作中常用面试中会问的问题---Postgresql面试题001

1.什么是Postgresql TOAST? TOAST (The Oversized-Attribute Storage Technique,超大尺寸字段存储技术)主要用于存储大字段的值。 PostgreSQL 页面(page)大小是固定的(通常为8KB),且不允许tuples跨多个页面存储。因此不能存储非常大的字段值。为了克服这个限制,大字段…...

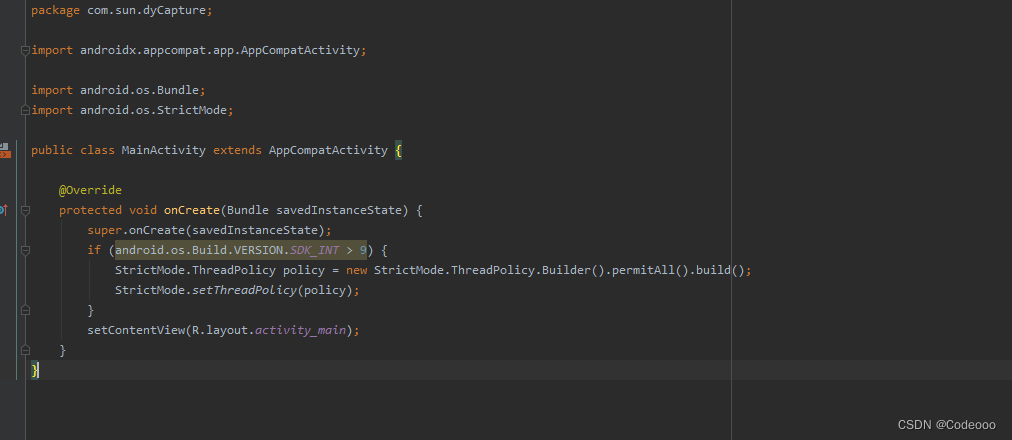

Xposed回发android.os.NetworkOnMainThreadException修复

最近用xposed进行hook回发的时候,又出现了新的问题; android.os.NetworkOnMainThreadException; 在Android4.0以后,写在主线程(就是Activity)中的HTTP请求,运行时都会报错,这是因为…...

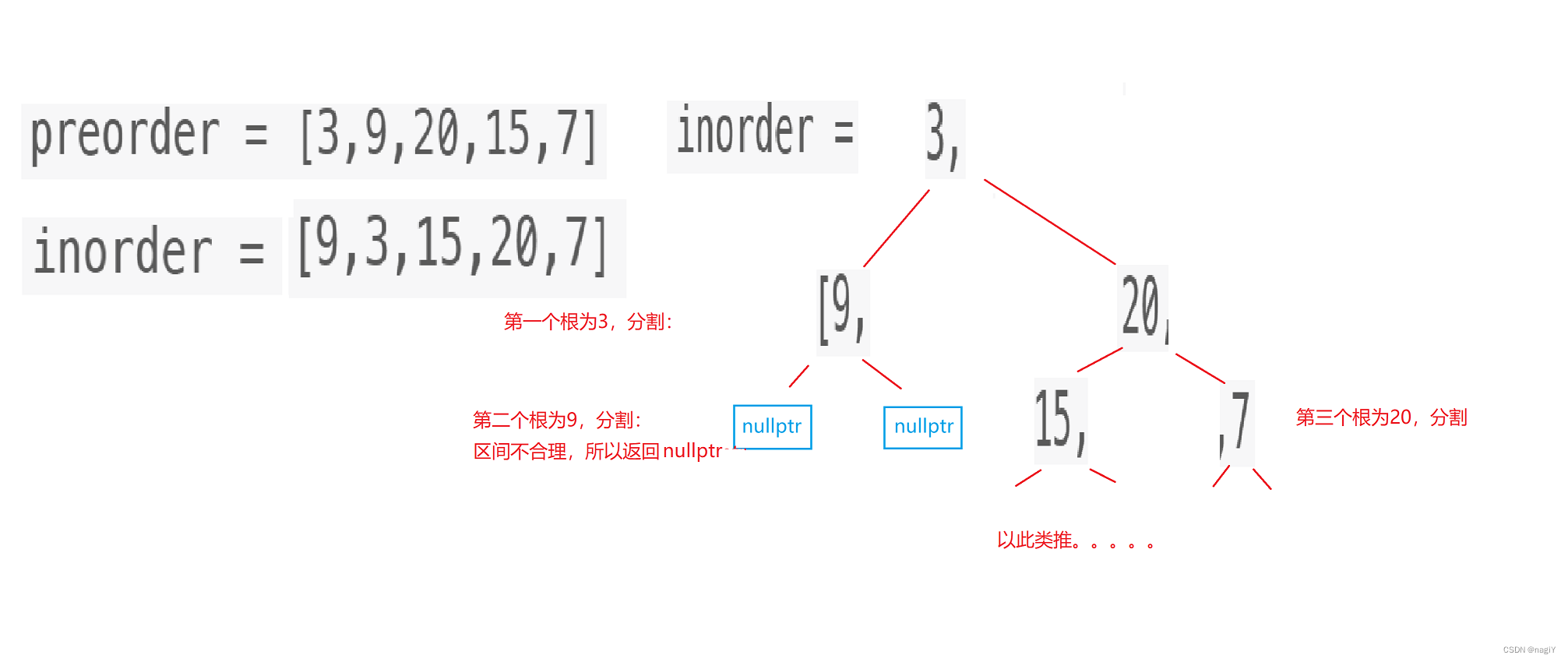

【Leetcode】二叉树的最近公共祖先,二叉搜索树转换成排好序的双向链表,前序遍历与中序遍历构造二叉树

一.二叉树的最近公共祖先 链接 二叉树的最近公共祖先 题目再现 『Ⅰ』思路一:转换成相交链表问题 观察上图,节点1和节点4的最近公共祖先是3,这是不是很像相交链表的问题,关于相交链表,曾经我在另一篇文章里写到过&a…...

途乐证券|互联金融概念爆发,安硕信息“20cm”涨停,高伟达等大涨

互联金融概念4日盘中强势拉升,截至发稿,安硕信息“20cm”涨停,高伟达、卓创资讯、慧博云通涨超12%,恒银科技、极点软件亦涨停,指南针涨超9%,金证股份涨逾7%。 高伟达昨日在投资者互动平台表明,公…...

计数排序算法

计数排序 计数排序说明: 计数排序(Counting Sort)是一种非比较性的排序算法,它通过统计元素出现的次数,然后根据元素出现的次数将元素排列在正确的位置上,从而实现排序。计数排序适用于非负整数或者具有确…...

企业高性能web服务器-nginx

1.nginx简介: nginx是企业高可用的web服务器,nginx也可用来做反向代理服务器器,具有高并发,占用资源少,功能丰富,也可以作为简单的负载均衡。 nginx在企业中的功能: web服务软件 反向代理服务器…...

GaussDB数据库的元数据及其管理简介

目录 一、前言 二、元数据简介 1、元数据定义 2、元数据分类 3、数据库元数据管理 三、GaussDB数据库的元数据管理 1、GaussDB数据库的元数据管理 2、通过“SQL 系统表/系统视图/系统函数”的方式管理(采集)元数据 1)获取表、视图及…...

合并两个有序链表 LeetCode热题100

题目 将两个升序链表合并为一个新的 升序 链表并返回。新链表是通过拼接给定的两个链表的所有节点组成的。 思路 遍历两个链表比较大小,按从小到大添加到链表即可。 代码 /*** Definition for singly-linked list.* struct ListNode {* int val;* List…...

职场高效神器:透明智能股票盯盘工具开发实战

1. 为什么职场人需要智能股票盯盘工具 早上9:30开盘时你正在开会,下午1:00休市前领导突然找你谈话——作为职场股民,这种时间冲突太常见了。传统炒股软件要么全屏遮挡工作内容,要么频繁切换窗口容易被发现。我去年就因为上班看盘被主管约谈&a…...

微信小程序实战:打造优雅的互动消息列表(评论 / 点赞 / 关注

在绿植类小程序开发中,互动消息模块(评论、点赞、关注)是提升用户粘性的核心场景。本文将基于实际开发场景,分享如何快速实现风格统一、交互友好的评论详情、点赞详情、关注详情列表页面,包含完整的代码实现和样式设计…...

Kali Linux下用stegpy解密XCTF MISC题:从安装到拿到flag的完整复盘

Kali Linux下用stegpy解密XCTF MISC题:从安装到拿到flag的完整复盘 在CTF竞赛中,MISC(杂项)类题目往往考验选手的综合能力,其中隐写术(Steganography)是常见考点。本文将详细复盘如何在Kali Lin…...

TCP八股

文章目录TCPTCP连接如何确保可靠性确认应答序号与确认序号超时重传连接管理三次握手(建立连接)四次挥手(断开连接)滑动窗口快速重传流量控制拥塞控制TCP和UDP的区别UDP怎么实现可靠传输TCP连接三次握手的过程, 为什么是三次, 可以是两次或者更多吗?TCP连接四次挥手的过程, 为什…...

)

考研复习Day 10 | 应用层(上)

一:应用层协议概述核心概念:应用层的协议多是基于客户-服务器方式。这里的客户和服务器都是应用进程。应用层协议规定了应用进程通信时遵循的规则。二:域名系统DNS2.1 DNS概述DNS(Domain Name System):互联…...

基于RISC-V指令集的五级流水线CPU设计、验证及上板实践:含详细说明、代码注释、Veril...

基于riscv指令集的五级流水线CPU设计及其验证 可以上板,且有详细说明和代码注释 基于vivado平台进行验证 包括verilog源代码、汇编验证代码、详细的说明文档(47页)以及PPT Modelsim quartus vivado都跑过,确认代码没有问题 已一、…...

安全智能:MongoDB EF Core 提供程序中的可查询加密和向量搜索牙

一、各自优势和对比 这是检索出来的数据,据说是根据第三方评测与企业数据,三款产品在代码生成质量上各有侧重: 产品 语言优势 场景亮点 核心差异 百度 Comate C核心代码质量第一;Python首生成率达92.3% SQL生成准确率提升35%&…...

【自动驾驶】从轨迹规划到安全评估:核心术语场景化解读

1. 自动驾驶技术链路全景解读 想象一下你坐在一辆自动驾驶汽车里,车辆正行驶在晚高峰的城市道路上。左侧突然有外卖电动车强行变道,右前方公交车正在靠站,而你的车需要在这复杂的场景中做出毫秒级的反应。这背后是一套完整的"感知-决策-…...

揭秘模型黑盒:如何用SALib快速完成全局敏感性分析?

揭秘模型黑盒:如何用SALib快速完成全局敏感性分析? 【免费下载链接】SALib Sensitivity Analysis Library in Python. Contains Sobol, Morris, FAST, and other methods. 项目地址: https://gitcode.com/gh_mirrors/sa/SALib 在复杂的系统建模和…...

Vue3+TypeScript+Cesium三维地图可视化项目:数字城市与数字孪生高效解决方案

Vue3TypeScriptCesium三维地图可视化项目:数字城市与数字孪生高效解决方案 【免费下载链接】vue3-ts-cesium-map-show 🔥前端 vue3.0 typescript 三维可视化 数字城市 数字孪生 选用 cesium开源GIS库 加入 主流地图 WebGL效果 完全开源 配合后台 实现可…...