基于FPGA的FIR低通滤波器实现(附工程源码),matlab+vivado19.2+simulation

基于FPGA的FIR低通滤波器实现(附工程源码)

文章目录

- 基于FPGA的FIR低通滤波器实现(附工程源码)

- 前言

- 一、matlab设计FIR滤波器,生成正弦波

- 1.设计FIR滤波器

- 1.生成正弦波.coe

- 二、vivado

- 1.fir滤波器IP核

- 2.正弦波生成IP核

- 3.时钟IP核设置

- 4.顶层文件/测试文件代码

- 三.simulation

- 四.源代码

前言

本文为FPGA实现FIR滤波器仿真过程,附源代码。

提示:以下是本篇文章正文内容,下面案例可供参考

一、matlab设计FIR滤波器,生成正弦波

1.设计FIR滤波器

打开MATLAB在命令行窗口输入:

fadtool

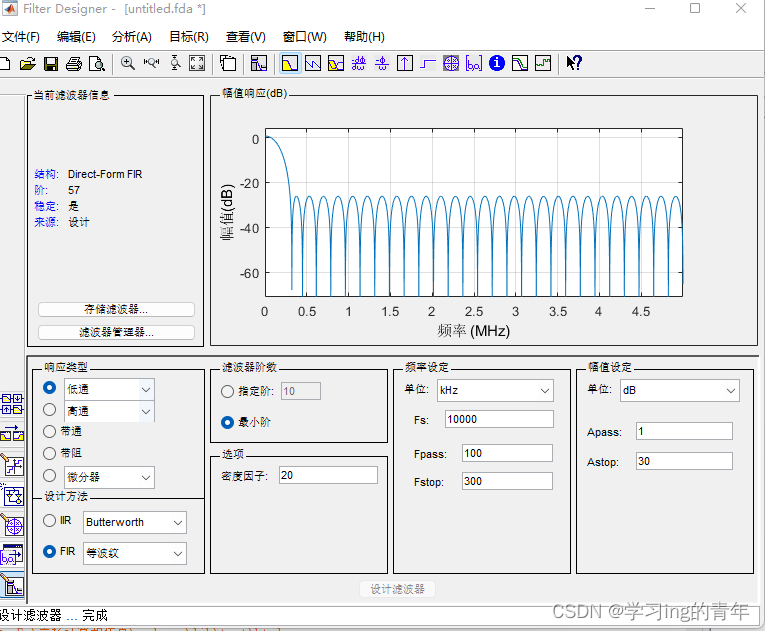

回车后在滤波器设计界面设置滤波器参数如下

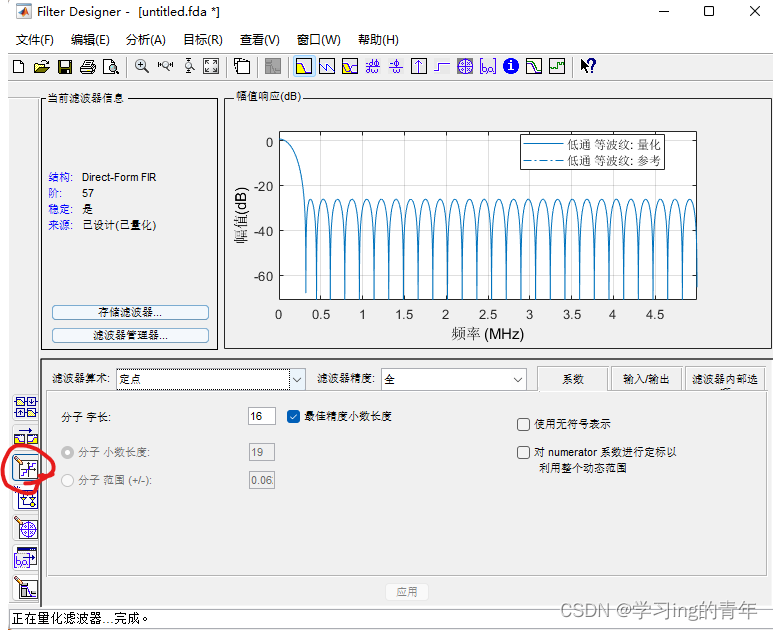

之后点击如图标志,设置定点,在菜单栏"目标(R)"出选择生成对应滤波器系数.COE文件

1.生成正弦波.coe

matlab代码如下

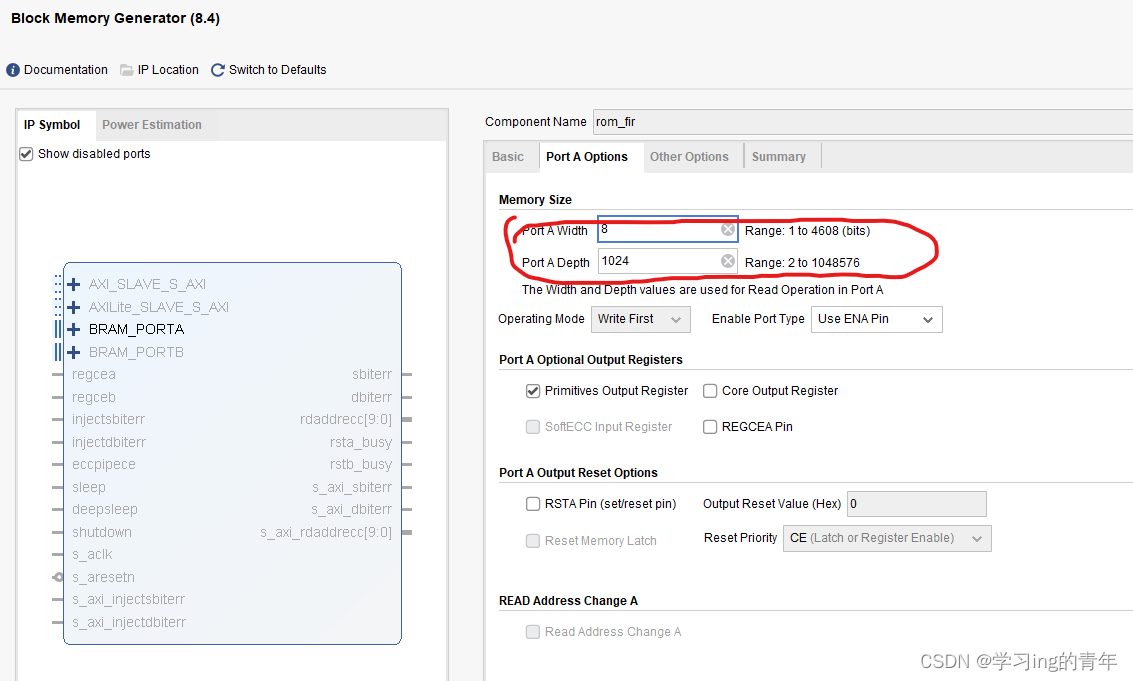

width=8; %rom的位宽

depth=1024; %rom的深度

x=linspace(0,2*pi,depth); %在一个周期内产生1024个采样点

y_sin=sin(x); %生成余弦数据

y_sin=round(y_sin*(2^(width-1)-1))+2^(width-1)-1; %将余弦数据全部转换为整数fid=fopen('C:\Users\lys\Desktop\fir\sin.coe','w'); %创建.coe文件

fprintf(fid,'%d,\n',y_sin); %向.coe文件中写入数据

fclose(fid); %关闭.coe文件

二、vivado

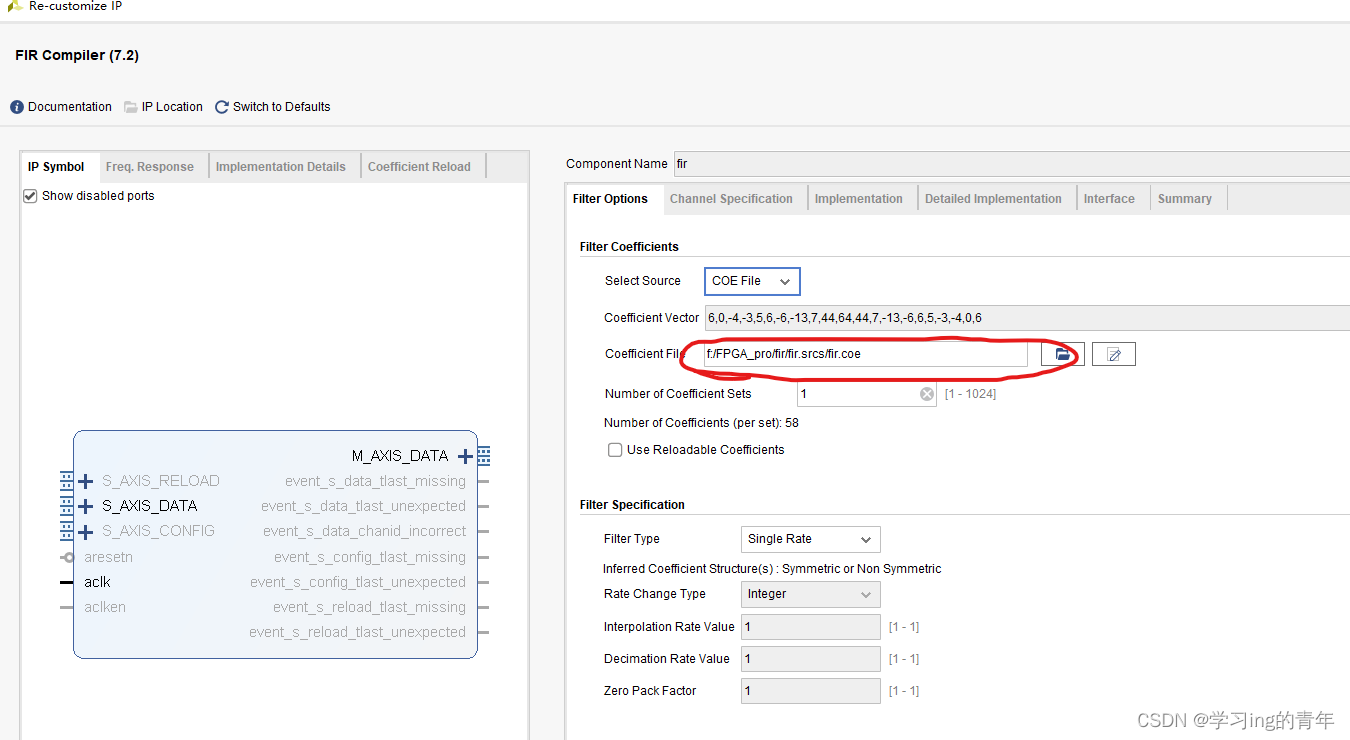

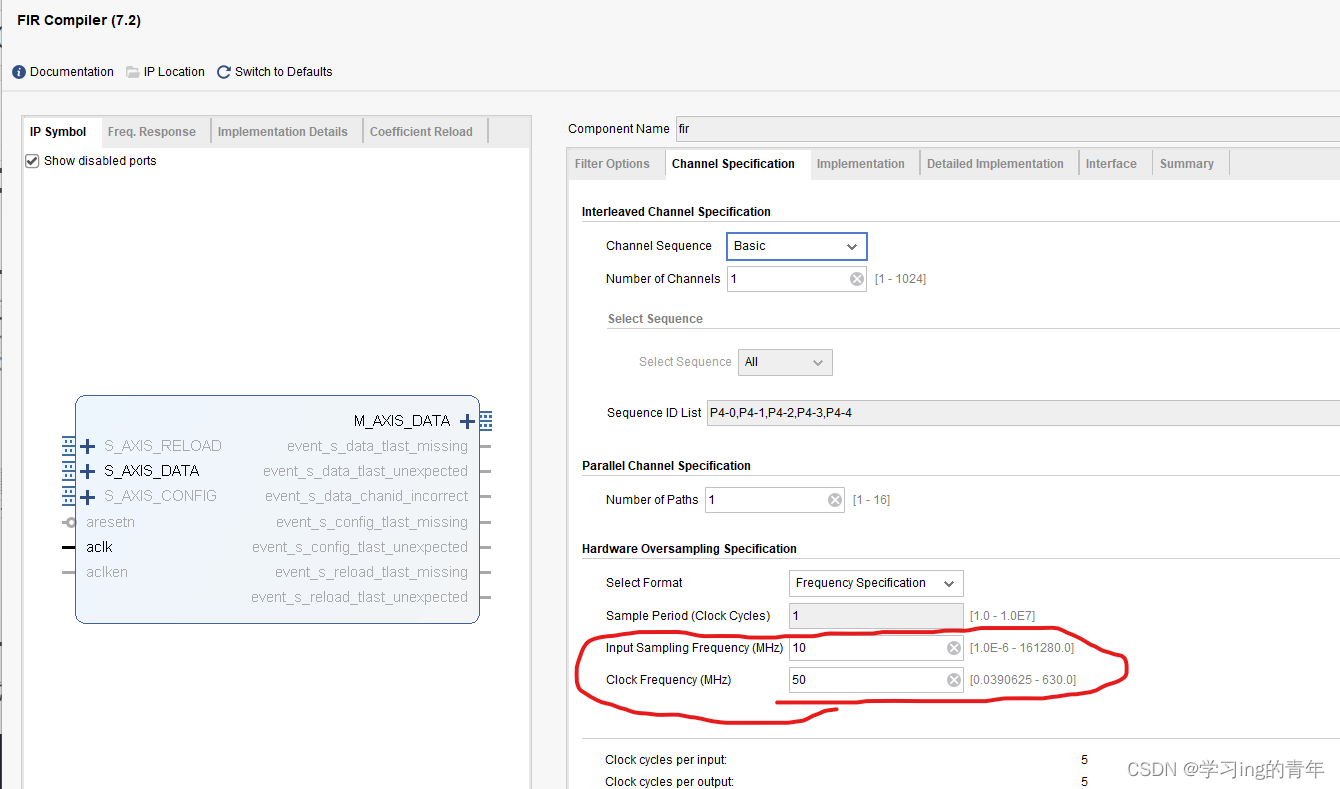

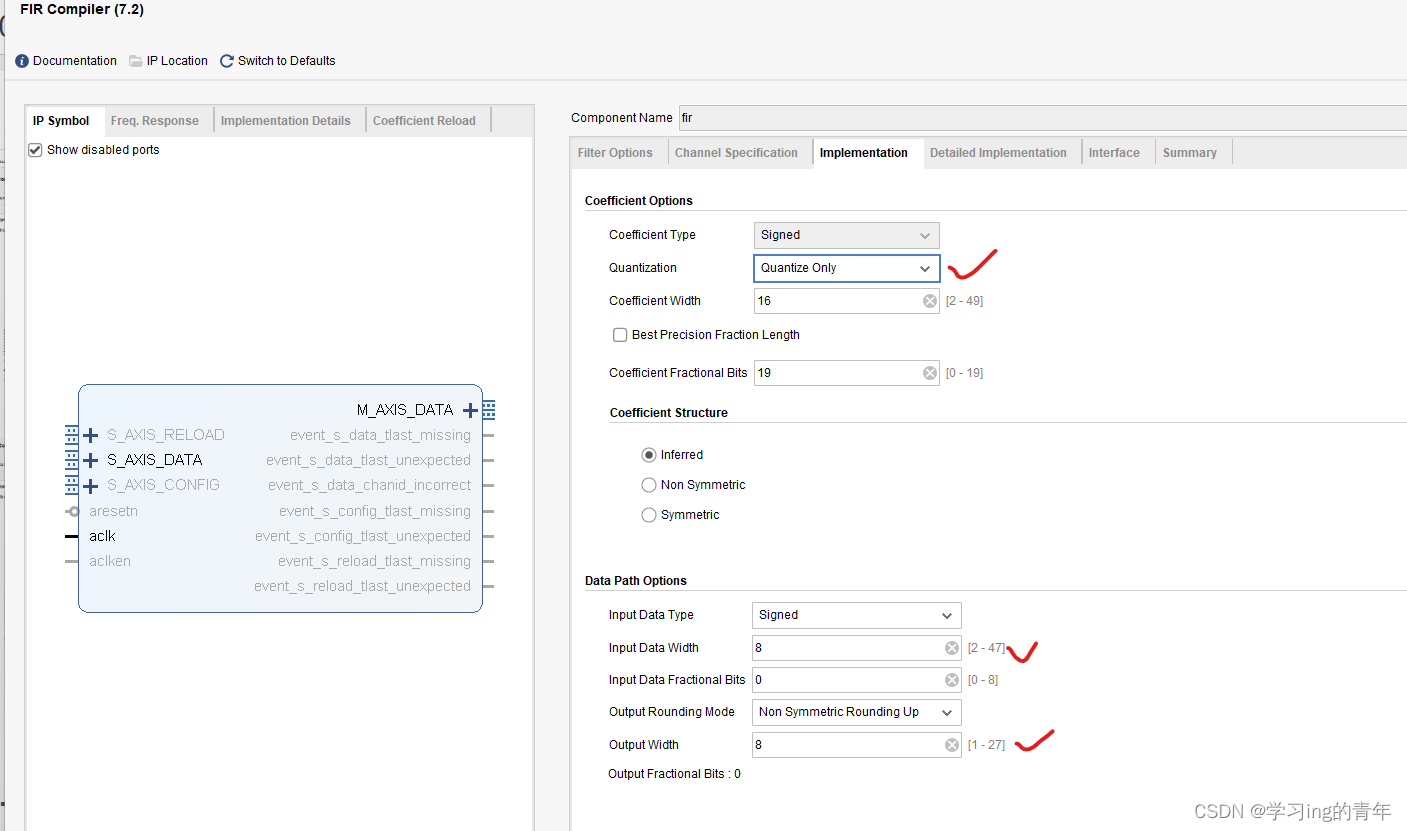

1.fir滤波器IP核

设置参数如下:

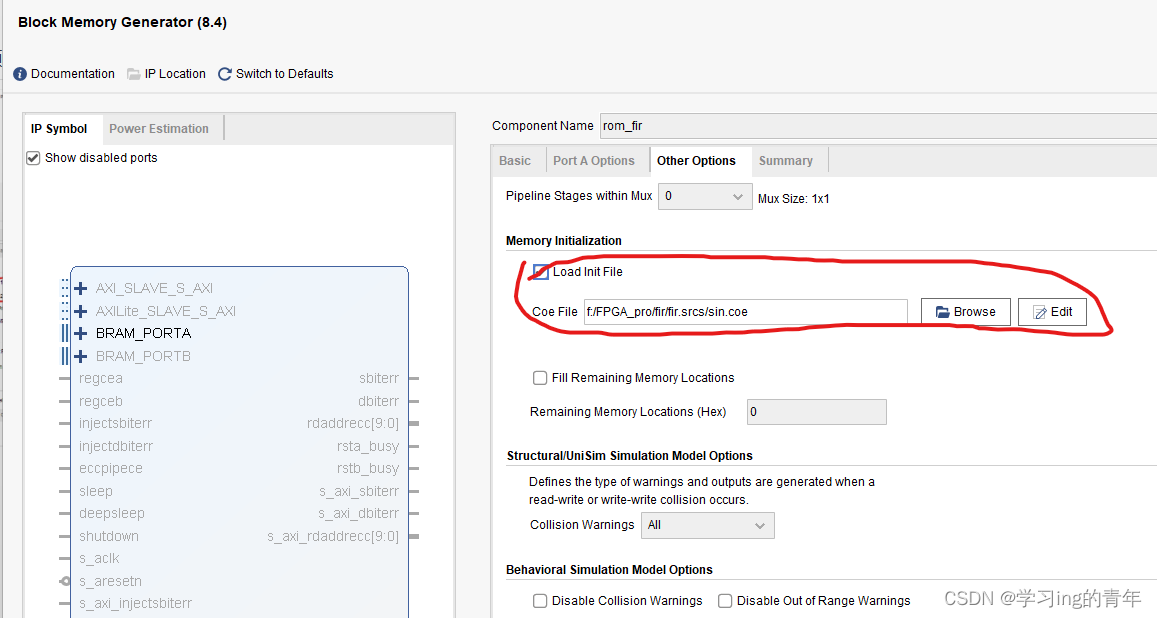

2.正弦波生成IP核

参数设置如下:

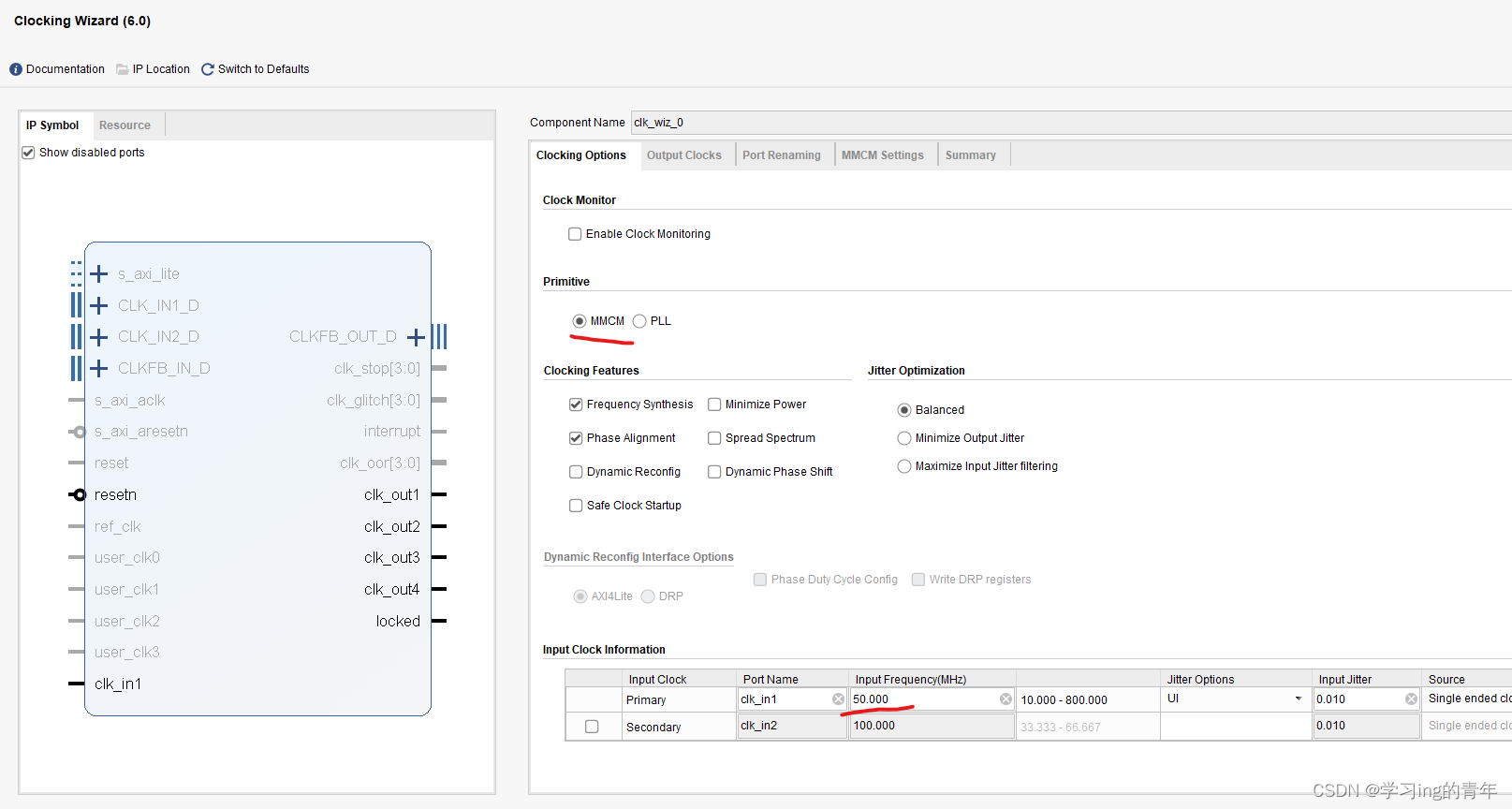

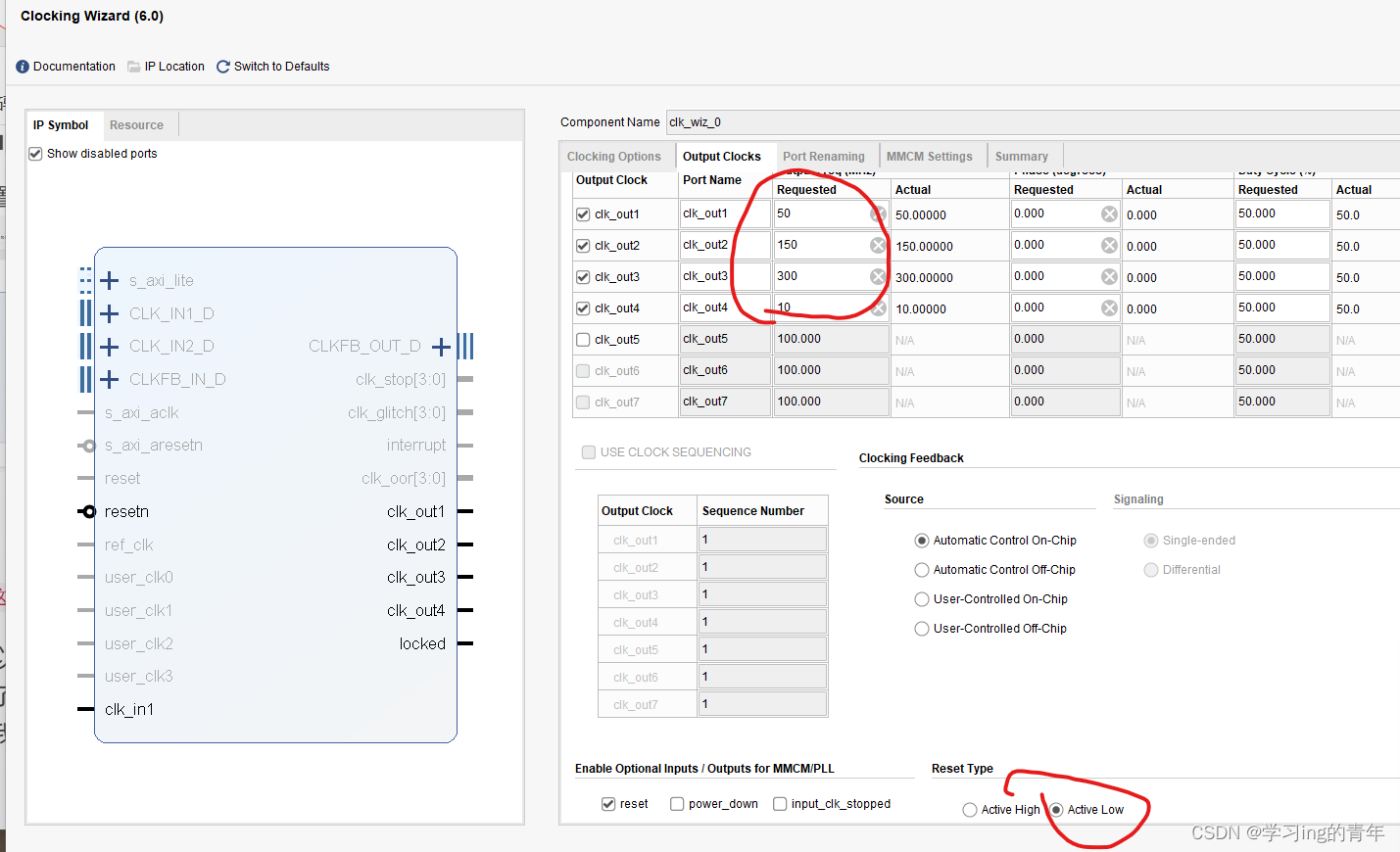

3.时钟IP核设置

参数设置如下:

4.顶层文件/测试文件代码

`timescale 1ns / 1psmodule fir_top(input clk,input rst_n,input [1:0]rom_sel,output [7:0]douta,output [7:0]fir_out_data);wire clk_10m;wire clk_1;wire clk_2;wire clk_3;// clk_wiz_0 instance_name(

// .clk_out1(clk_1), // output clk_out1

// .clk_out2(clk_2),

// .clk_out3(clk_3),

// .clk_out4(clk_10m),

// .reset(rst_n), // input resetn

// .locked(), // output locked

// .clk_in1(clk)

// ); // input clk_in1clk_wiz_0 instance_name(// Clock out ports.clk_out1(clk_1), // output clk_out1.clk_out2(clk_2), // output clk_out2.clk_out3(clk_3), // output clk_out3.clk_out4(clk_10m), // output clk_out4// Status and control signals.resetn(rst_n), // input reset.locked(), // output locked// Clock in ports.clk_in1(clk)); // input clk_in1wire clk_rom;assign clk_rom = (rom_sel == 0)?clk_1:((rom_sel == 1)?clk_2:clk_3);reg [9:0]addra;always@(posedge clk_rom or negedge rst_n)beginif(!rst_n)addra <= 'd0;elseaddra <= addra + 1'b1;endrom_fir rom_inst (.clka(clk_rom), // input wire clka.ena(1'b1), // input wire ena.addra(addra), // input wire [9 : 0] addra.douta(douta) // output wire [7 : 0] douta);wire [7:0]fir_in_data;assign fir_in_data = douta - 'd128;fir fir_inst (.aclk(clk), // input wire aclk.s_axis_data_tvalid(clk_10m), // input wire s_axis_data_tvalid.s_axis_data_tready(), // output wire s_axis_data_tready.s_axis_data_tdata(fir_in_data), // input wire [7 : 0] s_axis_data_tdata.m_axis_data_tvalid(), // output wire m_axis_data_tvalid.m_axis_data_tdata(fir_out_data) // output wire [7 : 0] m_axis_data_tdata);endmodule`timescale 1ns / 1psmodule fir_top_tb;reg clk;reg rst_n;reg [1:0]rom_sel;wire [7:0]douta;wire [7:0]fir_out_data;fir_top fir_top_inst(.clk (clk),.rst_n (rst_n),.rom_sel(rom_sel),.douta (douta),.fir_out_data(fir_out_data));initial clk = 0;always#10 clk = ~clk;initial beginrst_n = 0;rom_sel = 0;#200;rst_n = 1'b1;#200000;rom_sel = 1;#200000;rom_sel = 2;#200000;$stop;endendmodule三.simulation

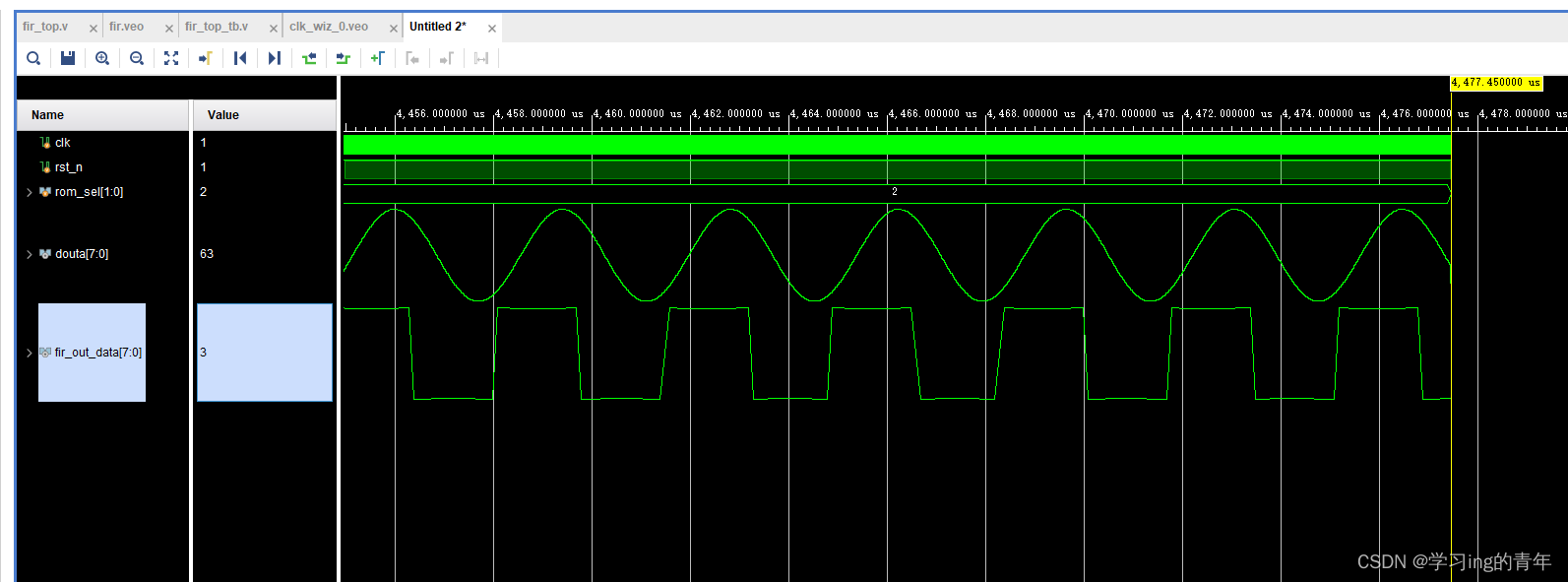

只为测试功能,未考虑滤波器性能,所以效果不佳,结果实现如下

四.源代码

https://download.csdn.net/download/qq_42761380/88243346

相关文章:

基于FPGA的FIR低通滤波器实现(附工程源码),matlab+vivado19.2+simulation

基于FPGA的FIR低通滤波器实现(附工程源码) 文章目录 基于FPGA的FIR低通滤波器实现(附工程源码)前言一、matlab设计FIR滤波器,生成正弦波1.设计FIR滤波器1.生成正弦波.coe 二、vivado1.fir滤波器IP核2.正弦波生成IP核3.时钟IP核设置4.顶层文件/测试文件代码 三.simul…...

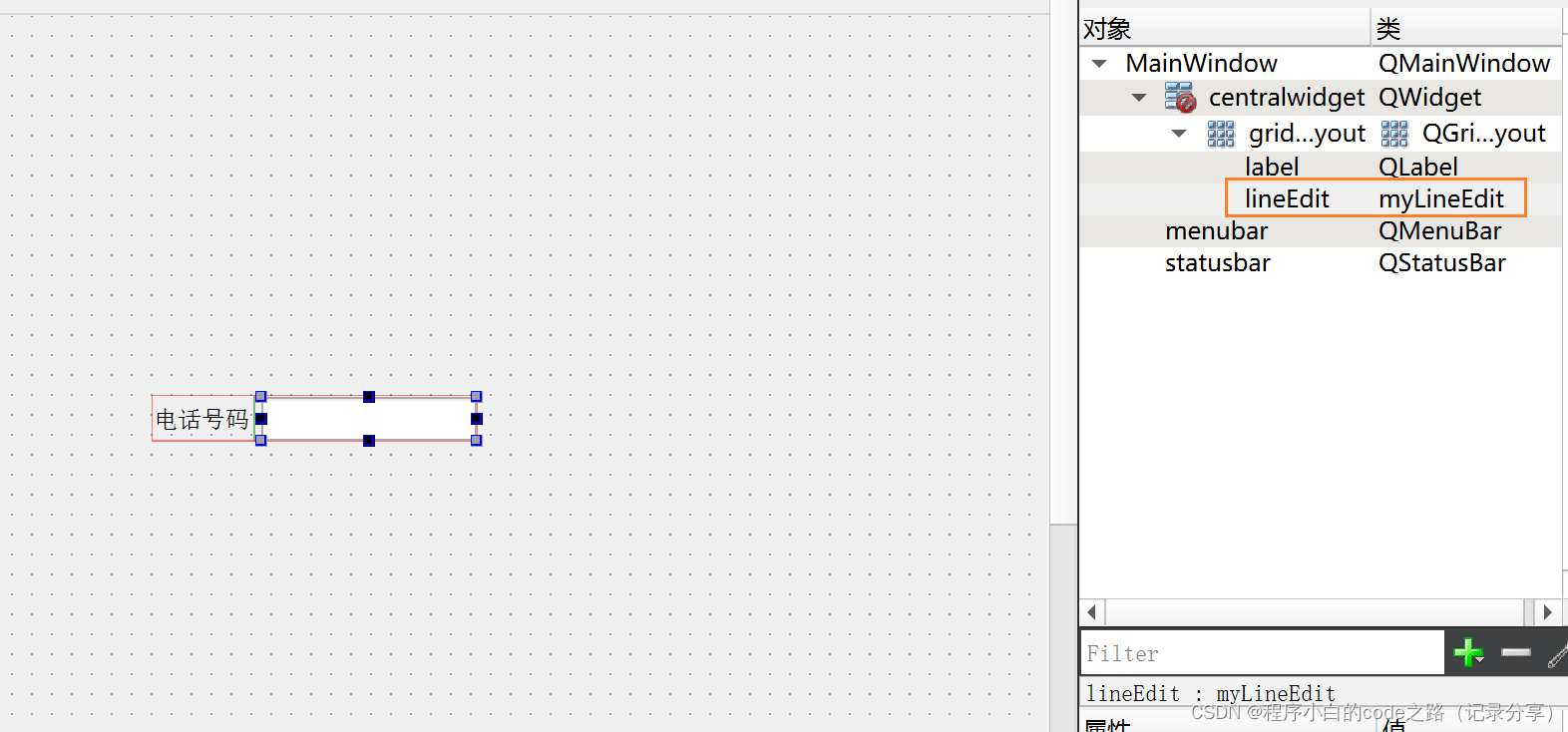

c++ qt--事件(第六部分)

c qt–事件(第六部分) 一.编辑伙伴,编辑顺序(按TAB进行切换) 1.编辑伙伴 此功能在设计界面如下的位置 1.设置伙伴关系 鼠标左键长按一个Label组件然后把鼠标移到另一个组件上 2.伙伴关系的作用 伙伴关系的作用就是…...

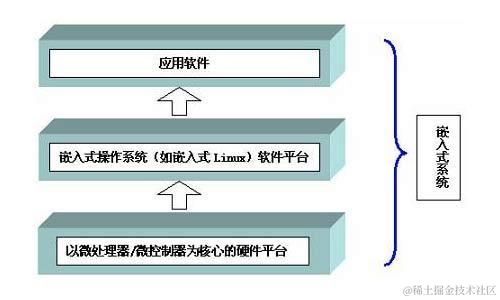

嵌入式系统入门实战:探索基本概念和应用领域

嵌入式系统是一种专用的计算机系统,它是为了满足特定任务而设计的。这些系统通常具有较低的硬件资源(如处理器速度、内存容量和存储容量),但具有较高的可靠性和实时性。嵌入式系统广泛应用于各种领域,如家用电器、汽车、工业控制、医疗设备等。 嵌入式系统的基本概念 微控…...

关于hive sql进行调优的理解

这是一个面试经常面的问题,很不幸,在没有准备的时候,我面到了这个题目,反思了下,将这部分的内容进行总结,给大家一点分享。 hive其实是基于hadoop的数据库管理工具,底层是基于MapReduce实现的&a…...

十大排序算法

一、冒泡排序 冒泡排序(Bubble Sort)是一种简单直观的排序算法。它重复地走访要排序的数列,一次比 较两个元素,如果他们的顺序错误就把他们交换过来。走访数列的工作是重复地进行直到没有再需要交换,也就是说该数列已经…...

PIP 常用操作汇总

1. 升级 python -m pip install --upgrade pip2. 列出所有安装包 pip list3. 查找特定包 pip list | findstr xxx4. 查看特定包 pip show xxx5. 安装软件包 pip install pyzmq24.0.16. 卸载软件包 pip uninstall -y pyzmq7. 查看配置 # 生效的配置(global -&…...

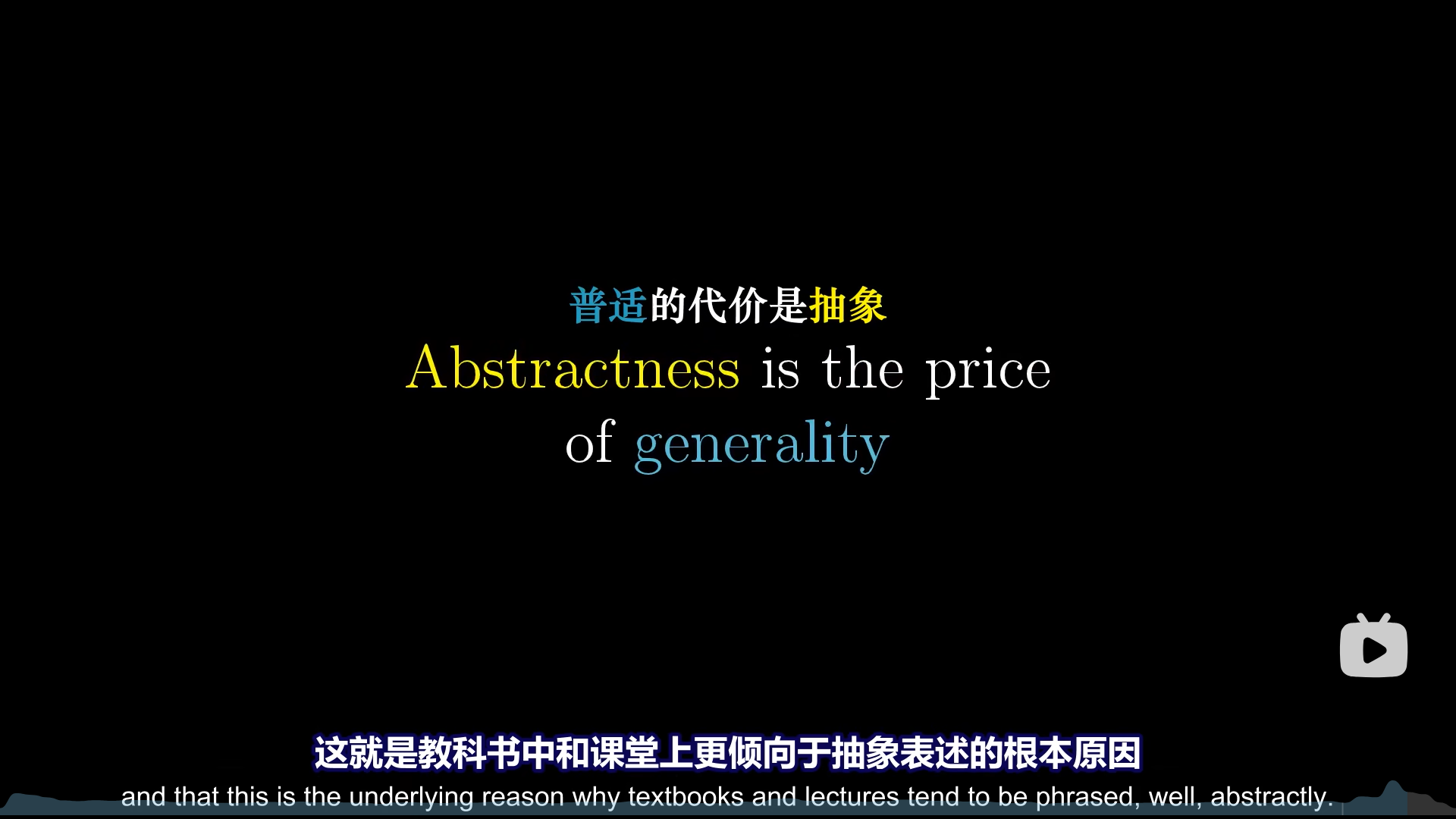

线性代数的本质笔记(3B1B课程)

文章目录 前言向量矩阵行列式线性方程非方阵点积叉积基变换特征向量与特征值抽象向量空间 前言 最近在复习线代,李永乐的基础课我刷了一下,感觉讲的不够透彻,和我当年学线代的感觉一样,就是不够形象。 比如,行列式为…...

快速掌握MQ消息中间件rabbitmq

快速掌握MQ消息中间件rabbitmq 目录概述需求: 设计思路实现思路分析1.video 参考资料和推荐阅读 Survive by day and develop by night. talk for import biz , show your perfect code,full busy,skip hardness,make a better result,wait for change,c…...

Git push拦截

遇到的问题 今天想提交代码到gitee,结果发现被拦截了,有段提示“forbidden by xxxx”… 我记得xxxx好像是公司的一个防泄密的东西… 这个东西是怎么实现的呢? 解决 原来git提供很多hook,push命令就有一个pre-push的hook&#x…...

拼多多anti-token分析

前言:拼多多charles抓包分析发现跟商品相关的请求头里都带了一个anti-token的字段且每次都不一样,那么下面的操作就从分析anti-token开始了 1.jadx反编译直接搜索 选中跟http相关的类对这个方法进行打印堆栈 结合堆栈方法调用的情况找到具体anti-token是由拦截器类f…...

基于微信小程序的中医体质辨识文体活动的设计与实现(Java+spring boot+MySQL)

获取源码或者论文请私信博主 演示视频: 基于微信小程序的中医体质辨识文体活动的设计与实现(Javaspring bootMySQL) 使用技术: 前端:html css javascript jQuery ajax thymeleaf 微信小程序 后端:Java s…...

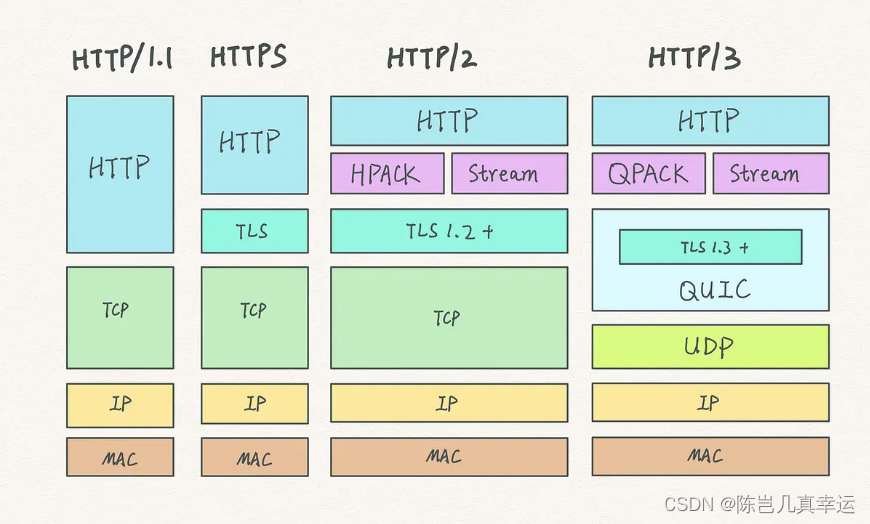

4.16 TCP 协议有什么缺陷?

目录 升级 TCP 的工作很困难 TCP 建立连接的延迟 TCP 存在队头阻塞问题 网络迁移需要重新建立 TCP 连接 升级 TCP 的工作很困难;TCP 建立连接的延迟;TCP 存在队头阻塞问题;网络迁移需要重新建立 TCP 连接; 升级 TCP 的工作很…...

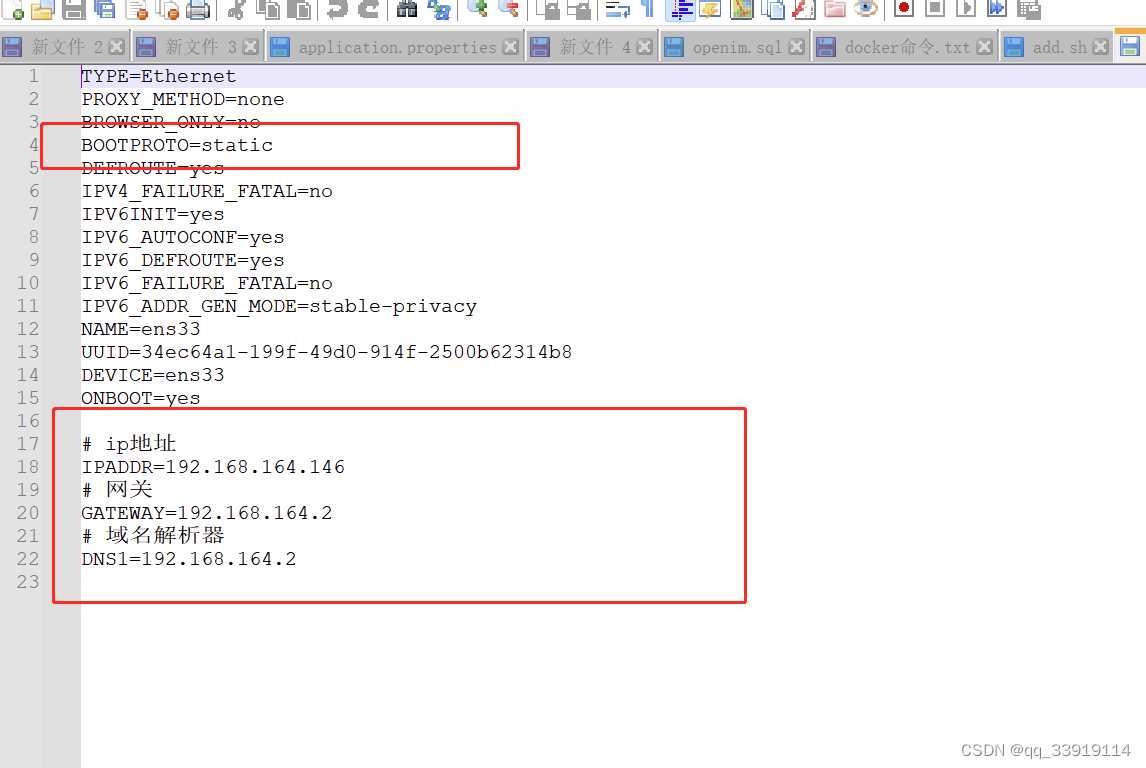

VMware 修改ip地址 虚拟机静态ip设置 centos动态ip修改为静态ip地址 centos静态ip地址 vmware修改ip地址

虚拟机的centos服务器经常变换ip,测试起来有些麻烦,故将动态ip修改为静态ip 1. 查看vmware 虚拟机网络配置: 点击编辑,打开虚拟网络配置 2. 选中nat模式,点击nat设置,最终获取网关ip: 192.168.164.2 3. 进…...

Deepin添加Ubuntu源

升级Deepin V23后,无法安装Zeal了,后面发现可以通过ubuntu源来安装。参考了以下两个文档。 添加Ubuntu源1 添加Ubuntu源2 1.添加ubuntu.list sudo vim /etc/apt/sources.list.d/ubuntu.list 2.添加中科大Ubuntu源 deb http://mirrors.ustc.edu.cn/…...

Mysql的多表查询和索引

MySQL 多表查询 当两个表查询时,从第一张表中取出一行和第二张表的每一行进行组合 返回结果含有两张表的所有列,一共返回的记录数第一张表行数*第二张表的行数(笛卡尔积) -- ?显示雇员名,雇员工资及所在部门的名字 【笛卡尔集…...

Java设计模式之建造者模式

建造者模式,又称生成器模式:将一个复杂的构建与其表示相分离,使得同样的构建过程可以创建不同的表示。 三个角色:建造者、具体的建造者、监工、使用者 建造者角色:定义生成实例所需要的所有方法; 具体的建…...

H5商城公众号商城系统源码 积分兑换商城系统独立后台

网购商城系统源码 积分兑换商城系统源码 独立后台附教程 测试环境:NginxPHP7.0MySQL5.6thinkphp伪静态...

华为OD机试 - 完全数计算(Java 2023 B卷 100分)

目录 专栏导读一、题目描述二、输入描述三、输出描述四、Java算法源码五、效果展示六、纵览全局 华为OD机试 2023B卷题库疯狂收录中,刷题点这里 专栏导读 本专栏收录于《华为OD机试(JAVA)真题(A卷B卷)》。 刷的越多&…...

每日一学——Vlan配置

VLAN(Virtual Local Area Network)是虚拟局域网的缩写,它是一种将多台主机和网络设备逻辑上划分成不同的局域网的技术。VLAN的实施可以基于端口、MAC地址、协议等多种方式进行。 VLAN的主要功能包括: 分割网络:VLAN可…...

Pimpl模式

写在前面 Pimpl(Pointer to implementation,又称作“编译防火墙”) 是一种减少代码依赖和编译时间的C编程技巧,其基本思想是将一个外部可见类(visible class)的实现细节(一般是所有私有的非虚成员)放在一个单独的实现类(implemen…...

App 测试用例覆盖率提升检查清单

App 测试用例覆盖率提升检查清单 核心用途:核对现有测试用例,快速找出「需求、功能、非功能、移动端特有场景」的覆盖遗漏点,适配 App UI 自动化手动测试,兼顾 PO 模型、数据驱动、各类用例设计方法(等价类/边界值等&a…...

Ostrakon-VL像素终端实战:为盲人顾客生成语音版货架导航

Ostrakon-VL像素终端实战:为盲人顾客生成语音版货架导航 1. 项目背景与价值 在零售场景中,视觉障碍顾客常常面临难以独立寻找商品的困境。传统解决方案依赖人工引导或专用盲道,成本高且灵活性不足。我们基于Ostrakon-VL-8B多模态大模型&…...

Path of Building PoE2:零基础掌握流放之路2角色规划工具实战指南

Path of Building PoE2:零基础掌握流放之路2角色规划工具实战指南 【免费下载链接】PathOfBuilding-PoE2 项目地址: https://gitcode.com/GitHub_Trending/pa/PathOfBuilding-PoE2 你是否曾遇到这样的困境:花费数小时规划的角色build,…...

如何极速获取金融市场数据:5分钟实战指南

如何极速获取金融市场数据:5分钟实战指南 【免费下载链接】qstock qstock由“Python金融量化”公众号开发,试图打造成个人量化投研分析包,目前包括数据获取(data)、可视化(plot)、选股(stock)和量化回测(策…...

如何通过自动化硬件适配技术突破Hackintosh配置瓶颈:OpCore Simplify技术深度解析

如何通过自动化硬件适配技术突破Hackintosh配置瓶颈:OpCore Simplify技术深度解析 【免费下载链接】OpCore-Simplify A tool designed to simplify the creation of OpenCore EFI 项目地址: https://gitcode.com/GitHub_Trending/op/OpCore-Simplify 在开源系…...

相场法模拟二元合金中考虑溶质偏析的comsol枝晶生长研究

comsol枝晶生长相场法模拟 二元合金 考虑溶质偏析枝晶生长这玩意儿在材料模拟里算是经典难题了。咱们用相场法搞COMSOL模拟的时候,最刺激的就是看那些枝晶分叉怎么从混乱中长出来。这次搞的是二元合金体系,重点得盯着溶质偏析这个捣蛋鬼——它能让晶体长…...

在树莓派4B上编译运行Speedtest-CLI:手把手解决curl和expat库的交叉编译难题

树莓派4B实战:从零构建Speedtest-CLI测速工具全流程指南 1. 环境准备与工具链配置 在树莓派4B上构建Speedtest-CLI测速工具,首先需要搭建完整的交叉编译环境。不同于x86平台的直接编译,ARM架构下的开发需要特别注意工具链的选择和配置。 必备…...

Kodi PVR IPTV Simple全方位应用指南:从入门到精通的多场景解决方案

Kodi PVR IPTV Simple全方位应用指南:从入门到精通的多场景解决方案 【免费下载链接】pvr.iptvsimple IPTV Simple client for Kodi PVR 项目地址: https://gitcode.com/gh_mirrors/pv/pvr.iptvsimple 一、场景痛点分析:当IPTV体验不如预期时&…...

PFC5.0代码:含三种矿物组成的岩石或类岩石材料GBM单轴压缩2d算例代码,仅供学习与提升

PFC5.0代码,含三种矿物组成的岩石或者类岩石材料,GBM,单轴压缩2d,算例代码仅供学习以及提升 打开PFC5.0的建模界面,突然想把花岗岩里的石英、长石、云母做成颗粒组合。先整点暴力的——直接拿球体颗粒拼成矿物晶粒&…...

炉石传说自动化脚本终极指南:从3小时到3分钟的游戏体验革命

炉石传说自动化脚本终极指南:从3小时到3分钟的游戏体验革命 【免费下载链接】Hearthstone-Script Hearthstone script(炉石传说脚本)(2024.01.25停更至国服回归) 项目地址: https://gitcode.com/gh_mirrors/he/Heart…...