串行FIR滤波器

串行 FIR 滤波器设计

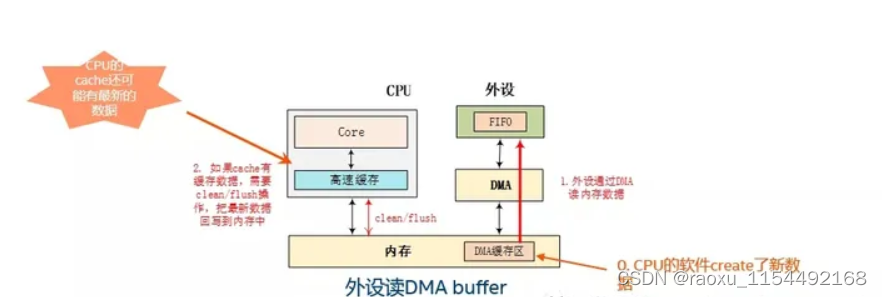

串行设计,就是在 16 个时钟周期内对 16 个延时数据分时依次进行乘法、加法运算,然后在时钟驱动下输出滤波值。考虑到 FIR 滤波器系数的对称性,计算一个滤波输出值的周期可以减少到 8 个。串行设计时每个周期只进行一次乘法运算,所以设计中只需一个乘法器即可。此时数据需要每 8 个时钟周期有效输入一次,但是为了保证输出信号频率的正确性,工作时钟需要为采样频率的 8 倍,即 400MHz。这种方法的优点是资源耗费少,但是工作频率要求高,数据不能持续输出。

串行设计

/**********************************************************

>> Description : fir study with serial tech

>> : Fs:50Mhz, fstop:1-6Mhz, order:16, sys clk:400MHz

***********************************************************/

`define SAFE_DESIGNmodule fir_serial(input rstn,input clk, // 系统工作时钟,400MHzinput en , // 输入数据有效信号input [11:0] xin, // 输入混合频率的信号数据output valid, // 输出数据有效信号output [28:0] yout // 输出数据);//delay of input data enablereg [11:0] en_r ;always @(posedge clk or negedge rstn) beginif (!rstn) beginen_r[11:0] <= 'b0 ;endelse beginen_r[11:0] <= {en_r[10:0], en} ;endend//fir coeficientwire [11:0] coe[7:0] ;assign coe[0] = 12'd11 ;assign coe[1] = 12'd31 ;assign coe[2] = 12'd63 ;assign coe[3] = 12'd104 ;assign coe[4] = 12'd152 ;assign coe[5] = 12'd198 ;assign coe[6] = 12'd235 ;assign coe[7] = 12'd255 ;//(1) 输入数据移位部分reg [2:0] cnt ;integer i, j ;always @(posedge clk or negedge rstn) beginif (!rstn) begincnt <= 3'b0 ;endelse if (en || cnt != 0) begincnt <= cnt + 1'b1 ; //8个周期计数endendreg [11:0] xin_reg[15:0];always @(posedge clk or negedge rstn) beginif (!rstn) beginfor (i=0; i<16; i=i+1) beginxin_reg[i] <= 12'b0;endendelse if (cnt == 3'd0 && en) begin //每8个周期读入一次有效数据xin_reg[0] <= xin ;for (j=0; j<15; j=j+1) beginxin_reg[j+1] <= xin_reg[j] ; // 数据移位endendend//(2) 系数对称,16个移位寄存器数据进行首位相加reg [11:0] add_a, add_b ;reg [11:0] coe_s ;wire [12:0] add_s ;wire [2:0] xin_index = cnt>=1 ? cnt-1 : 3'd7 ;always @(posedge clk or negedge rstn) beginif (!rstn) beginadd_a <= 13'b0 ;add_b <= 13'b0 ;coe_s <= 12'b0 ;endelse if (en_r[xin_index]) begin //from en_r[1]add_a <= xin_reg[xin_index] ;add_b <= xin_reg[15-xin_index] ;coe_s <= coe[xin_index] ;endendassign add_s = {add_a} + {add_b} ; //(3) 乘法运算,只用一个乘法wire [24:0] mout ;

`ifdef SAFE_DESIGNwire en_mult ;wire [3:0] index_mult = cnt>=2 ? cnt-1 : 4'd7 + cnt[0] ;mult_man #(13, 12) u_mult_single //例化自己设计的流水线乘法器(.clk (clk),.rstn (rstn),.data_rdy (en_r[index_mult]), //注意数据时序对应.mult1 (add_s),.mult2 (coe_s),.res_rdy (en_mult), .res (mout));`elsealways @(posedge clk or negedge rstn) beginif (!rstn) beginmout <= 25'b0 ;endelse if (|en_r[8:1]) beginmout <= coe_s * add_s ; //直接乘endendwire en_mult = en_r[2];

`endif//(4) 积分累加,8组25bit数据 -> 1组 29bit 数据reg [28:0] sum ;reg valid_r ;//mult output en counterreg [4:0] cnt_acc_r ;always @(posedge clk or negedge rstn) beginif (!rstn) begincnt_acc_r <= 'b0 ;endelse if (cnt_acc_r == 5'd7) begin //计时8个周期cnt_acc_r <= 'b0 ;endelse if (en_mult || cnt_acc_r != 0) begin //只要en有效,计时不停cnt_acc_r <= cnt_acc_r + 1'b1 ;endendalways @(posedge clk or negedge rstn) beginif (!rstn) beginsum <= 29'd0 ;valid_r <= 1'b0 ;endelse if (cnt_acc_r == 5'd7) begin //在第8个累加周期输出滤波值sum <= sum + mout;valid_r <= 1'b1 ;endelse if (en_mult && cnt_acc_r == 0) begin //初始化sum <= mout ;valid_r <= 1'b0 ;endelse if (cnt_acc_r != 0) begin //acculating between cyclessum <= sum + mout ;valid_r <= 1'b0 ;endend//时钟锁存有效的输出数据,为了让输出信号不是那么频繁的变化reg [28:0] yout_r ;always @(posedge clk or negedge rstn) beginif (!rstn) beginyout_r <= 'b0 ;endelse if (valid_r) beginyout_r <= sum ;endendassign yout = yout_r ;//(5) 输出数据有效延迟,即滤波数据丢掉前15个滤波值reg [4:0] cnt_valid ;always @(posedge clk or negedge rstn) beginif (!rstn) begincnt_valid <= 'b0 ;endelse if (valid_r && cnt_valid != 5'd16) begincnt_valid <= cnt_valid + 1'b1 ;endendassign valid = (cnt_valid == 5'd16) & valid_r ;endmodule

testbench

module test ;//inputreg clk ;reg rst_n ;reg en ;reg [11:0] xin ;//outputwire [28:0] yout ;wire valid ;parameter SIMU_CYCLE = 64'd1000 ;parameter SIN_DATA_NUM = 200 ;//=====================================

// 8*50MHz clk generatinglocalparam TCLK_HALF = (10_000 >>3);initial beginclk = 1'b0 ;forever begin# TCLK_HALF clk = ~clk ;endend//============================

// reset and finishinitial beginrst_n = 1'b0 ;# 30 rst_n = 1'b1 ;# (TCLK_HALF * 2 * 8 * SIMU_CYCLE) ;$finish ;end//=======================================

// read cos data into registerreg [11:0] stimulus [0: SIN_DATA_NUM-1] ;integer i ;initial begin$readmemh("E:/appdata/SimulationTools/modelsim/demo/filter/FIR_filter/tb/cosx0p25m7p5m12bit.txt", stimulus) ;en = 0 ;i = 0 ;xin = 0 ;# 200 ;forever beginrepeat(7) @(negedge clk) ; //空置7个周期,第8个周期给数据en = 1 ;xin = stimulus[i] ;@(negedge clk) ;en = 0 ; //输入数据有效信号只持续一个周期即可if (i == SIN_DATA_NUM-1) i = 0 ;else i = i + 1 ;endendfir_serial u_fir_serial (.clk (clk),.rstn (rst_n),.en (en),.xin (xin),.valid (valid),.yout (yout));endmodule

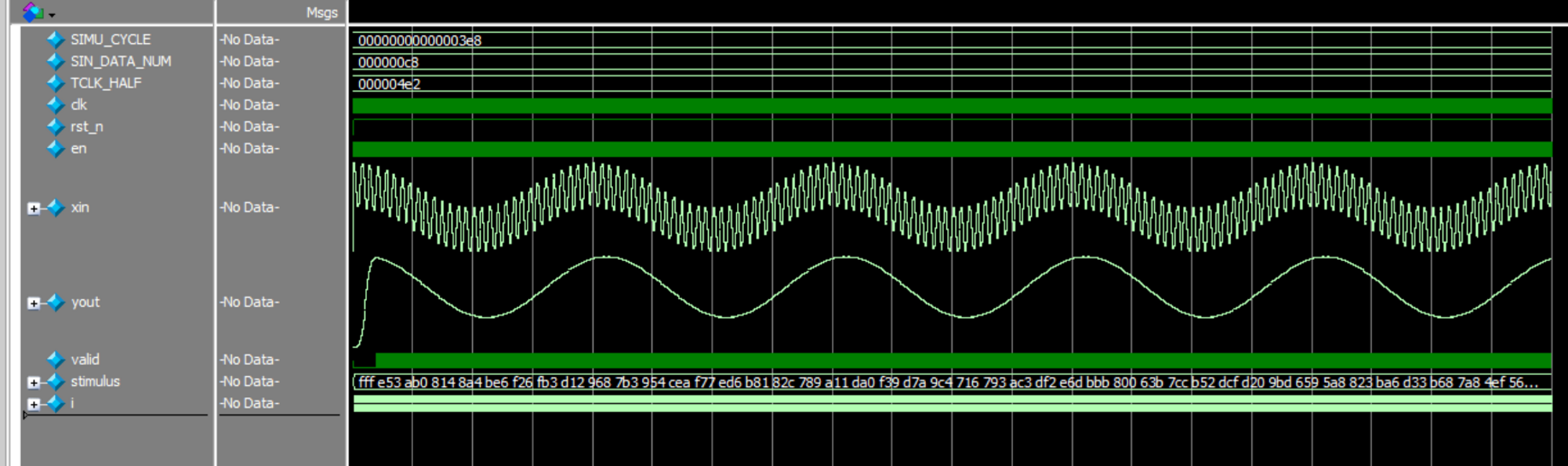

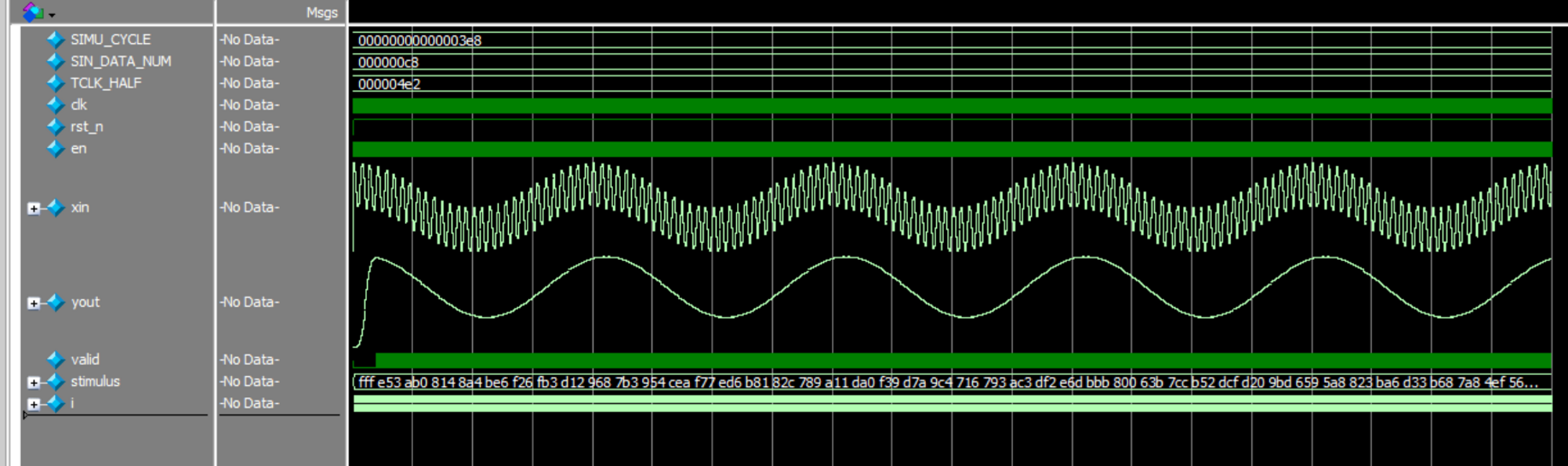

仿真结果

相关文章:

串行FIR滤波器

串行 FIR 滤波器设计 串行设计,就是在 16 个时钟周期内对 16 个延时数据分时依次进行乘法、加法运算,然后在时钟驱动下输出滤波值。考虑到 FIR 滤波器系数的对称性,计算一个滤波输出值的周期可以减少到 8 个。串行设计时每个周期只进行一次乘…...

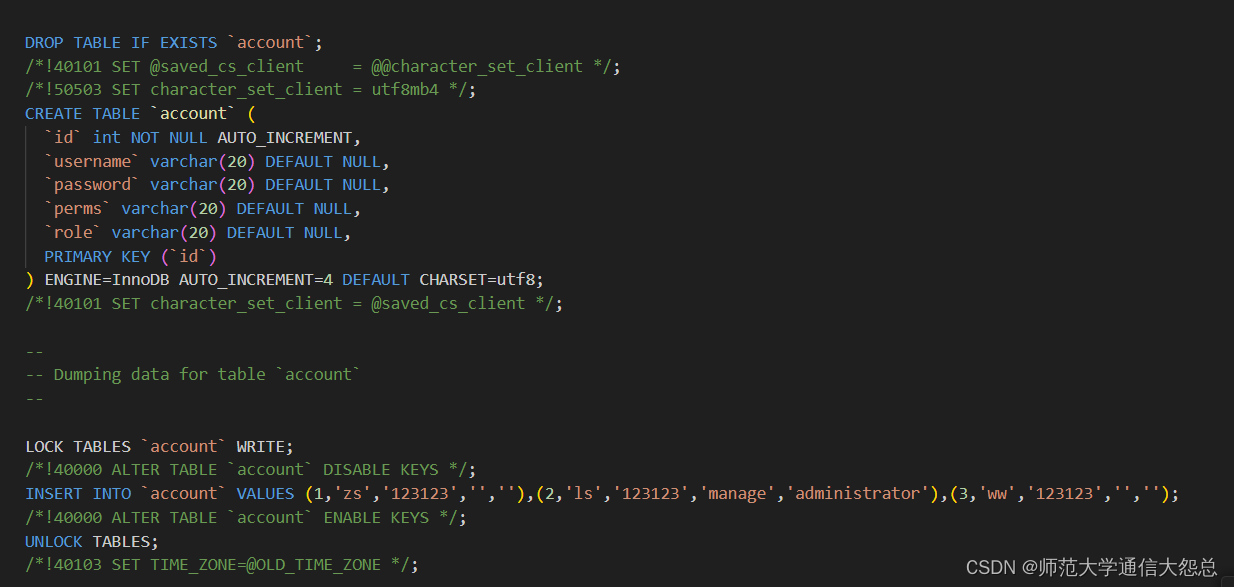

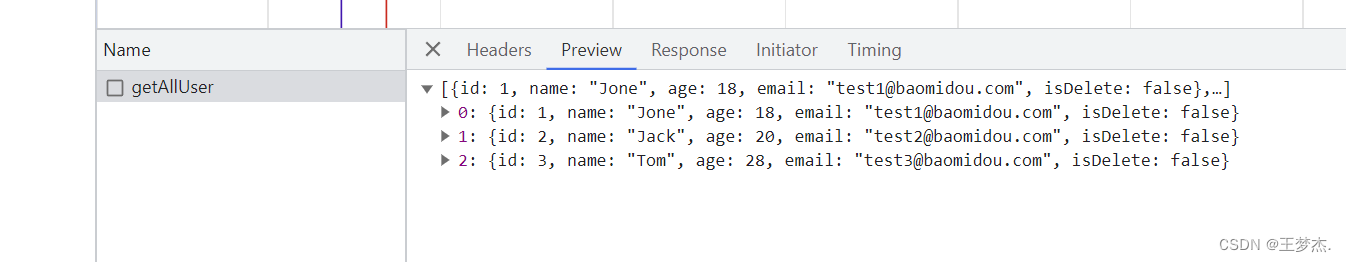

Spring Boot 整合 Shiro(后端)

1 Shiro 什么是 Shiro 官网: http://shiro.apache.org/ 是一款主流的 Java 安全框架,不依赖任何容器,可以运行在 Java SE 和 Java EE 项目中,它的主要作用是对访问系统的用户进行身份认证、 授权、会话管理、加密等操作。 …...

面试中的自我介绍:首印象决定一切

🌷🍁 博主猫头虎(🐅🐾)带您 Go to New World✨🍁 🦄 博客首页——🐅🐾猫头虎的博客🎐 🐳 《面试题大全专栏》 🦕 文章图文…...

深入理解联邦学习——联邦学习的价值

分类目录:《深入理解联邦学习》总目录 毫无疑问,如今我们正经历互联网第四次信息革命,坐拥海量的信息与数据。这些数据如果能够用AI的方式进行解读,将会为人类日常生活带来颠覆性变革。联邦学习作为未来AI发展的底层技术ÿ…...

linux 内存一致性

linux 出现内存一致性的场景 1、编译器优化 ,代码上下没有关联的时候,因为编译优化,会有执行执行顺序不一致的问题(多核单核都会出现) 2、多核cpu乱序执行,cpu的乱序执行导致内存不一致(多核出…...

Vue 如何监听 localstorage的变化

需求 分析 1. 初始想法 computed: {lonlat(){console.log(localStorage.getItem(lonlat))return localStorage.getItem(lonlat)}},watch: {lonlat(newVal,oldVal){console.log(1002,newVal,oldVal)}},我们想着用 计算属性 computed 和 watch 监听实现,但根本没有…...

ActiveMQ使用JDBC持久化消息

为了避免服务器宕机而导致消息丢失,ActiveMQ提供消息持久化机制。 ActiveMQ提供多种消息持久化的方式,如LevelDB Store、KahaDB 、AMQ、JDBC等,详情可以访问官网。 ActiveMQ默认是使用KahaDB持久化消息。在/conf/activemq.xml如下配置&…...

光环云出席Enjoy出海AIGC主题研讨会,助力企业迎接AI时代机遇与挑战

AIGC的崛起,为2023年的全球化突围之路拓展了想象空间。 从年初至今,OpenAI和ChatGPT高举高打,很大程度上起到了教育市场的作用;此外,Meta推出大模型,Snapchat、Soul、字节等大厂或上线或内测聊天机器人&…...

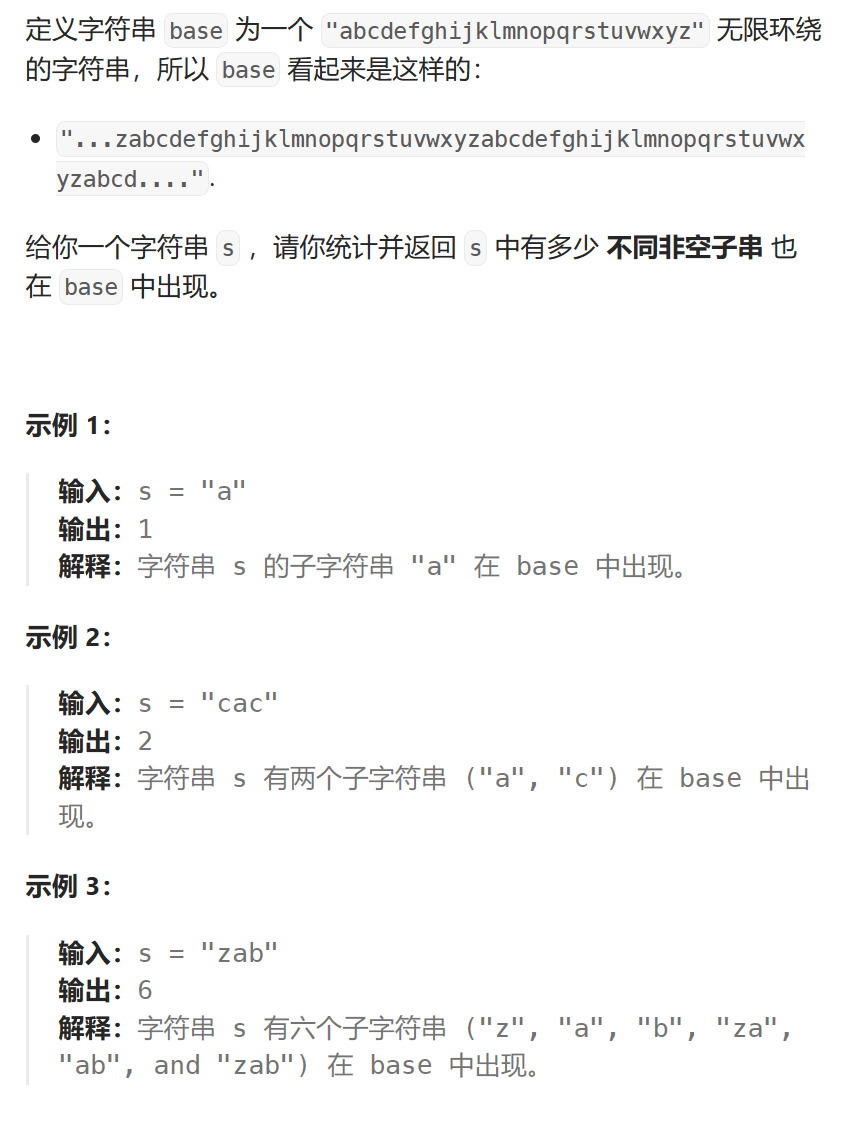

动态规划:路径和子数组问题(C++)

动态规划:路径和子数组问题 路径问题1.不同路径(中等)2.不同路径II(中等)3.下降路径最⼩和(中等)4.地下城游戏(困难) 子数组问题1.最大子数组和(中等…...

微服务-gateway跨域配置

文章目录 一、前言二、gateway跨域配置1、问题描述1.1、什么是跨域请求?1.1.1、同源策略1.1.2. 安全性考虑1.1.3. 跨域攻击 1.2、问题产生原因 2、解决方法2.1、修改配置文件2.2、配置类统一配置2.3、全局跨域拦截器 三、总结 一、前言 在SpringCloud项目中&#x…...

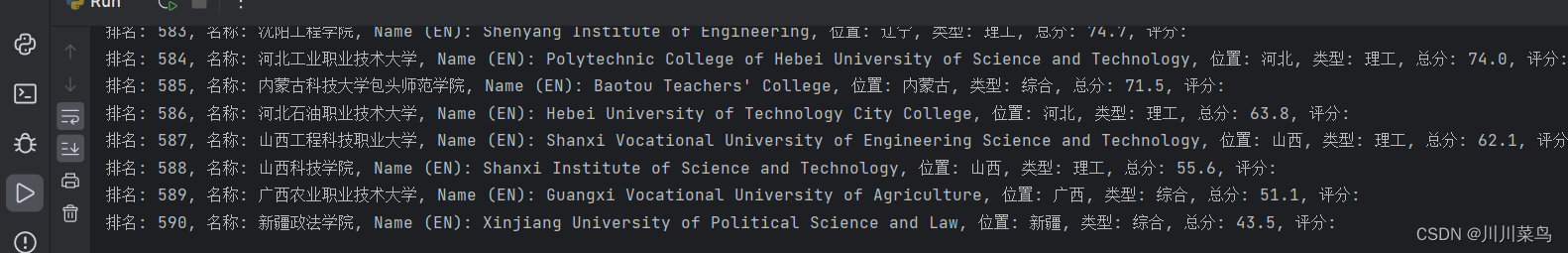

爬虫项目(二):中国大学排名

《Python网络爬虫入门到实战》京东购买地址,这里讲解了大量的基础知识和实战,由本人编著:https://item.jd.com/14049708.html配套代码仓库地址:https://github.com/sfvsfv/Crawer文章目录 分析第一步:获取源码分析第一…...

十二、MySQL(DQL)分组/排序/分页查询如何实现?

总括 select 字段列表 from 表名 [where 条件] (group by)/(order by)/(limit) 分组字段名 分组查询 1、分组查询 (1)基础语法: select 字段列表 from 表名 [where 条件] group by 分组字段名 [having 分组之后的过滤条件] (…...

设计模式概念学习

创建类型 单例模式 饿汉 构建时就创建 懒汉 单线程-访问到的时候才创建多线程-低效率 做法:加锁->若未创建则创建->获取资源->解锁 缺点:效率低,每次访问之前都要加锁,资源创建之后不能被同时被多个线程访问多线程-…...

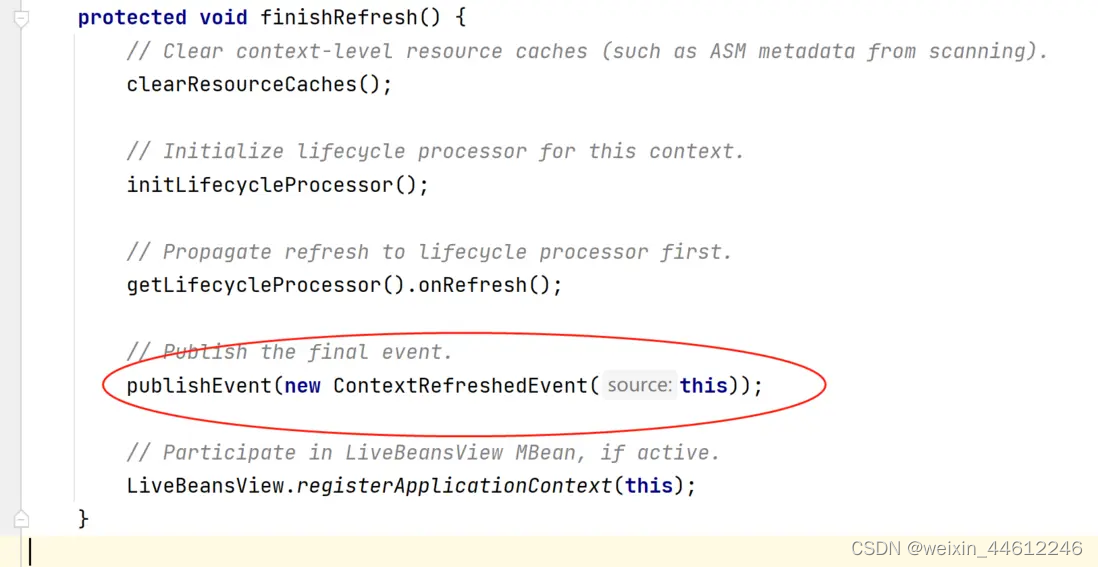

Spring MVC 五 - DispatcherServlet初始化过程(续)

今天的内容是SpringMVC的初始化过程,其实也就是DispatcherServilet的初始化过程。 Special Bean Types DispatcherServlet委托如下一些特殊的bean来处理请求、并渲染正确的返回。这些特殊的bean是Spring MVC框架管理的bean、按照Spring框架的约定处理相关请求&…...

day36:网编day3,TCP、UDP模型

下载: #include <myhead.h>#define ERR(s) do\ {\fprintf(stderr,"__%d__",__LINE__);\perror(s);\ }while(0) #define PORT 69 #define IP "192.168.115.184"int do_download(int cfd,struct sockaddr_in sin); //int do_upload(); int…...

MySQL——MySQL的基础操作部分

使用命令行登录 mysql -u root -p 直接敲击回车后输入密码即可: 当看到出现“mysql>“的符号之后,就表示已经进入到了MySQL系统中,就可以输入My…...

编译OpenWrt内核驱动

编译OpenWrt内核驱动可以参考OpenWrt内部其它驱动的编写例程,来修改成自己需要的驱动 一、OpenWrt源代码获取与编译 1.1、搭建环境 下载OpenWrt的官方源码: git clone https://github.com/openwrt/openwrt.git1.2、安装编译依赖项 sudo apt update -…...

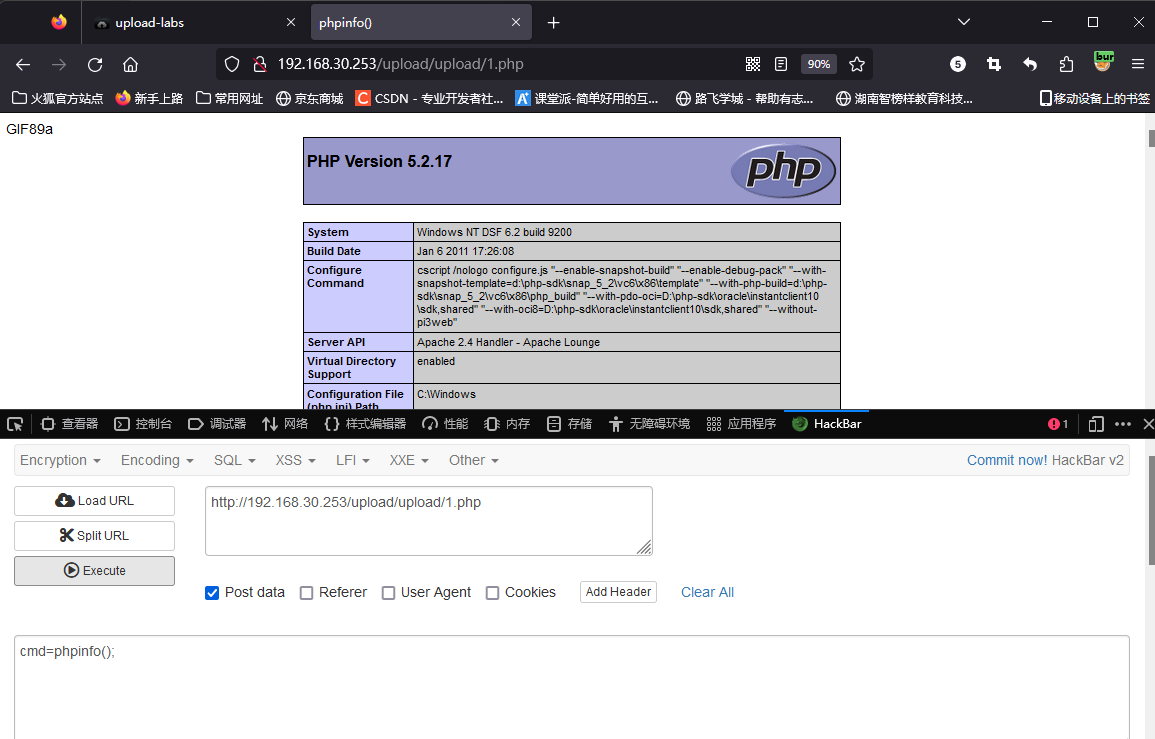

文件上传漏洞-upload靶场5-12关

文件上传漏洞-upload靶场5-12关通关笔记(windows环境漏洞) 简介 在前两篇文章中,已经说了分析上传漏的思路,在本篇文章中,将带领大家熟悉winodws系统存在的一些上传漏洞。 upload 第五关 (大小写绕过…...

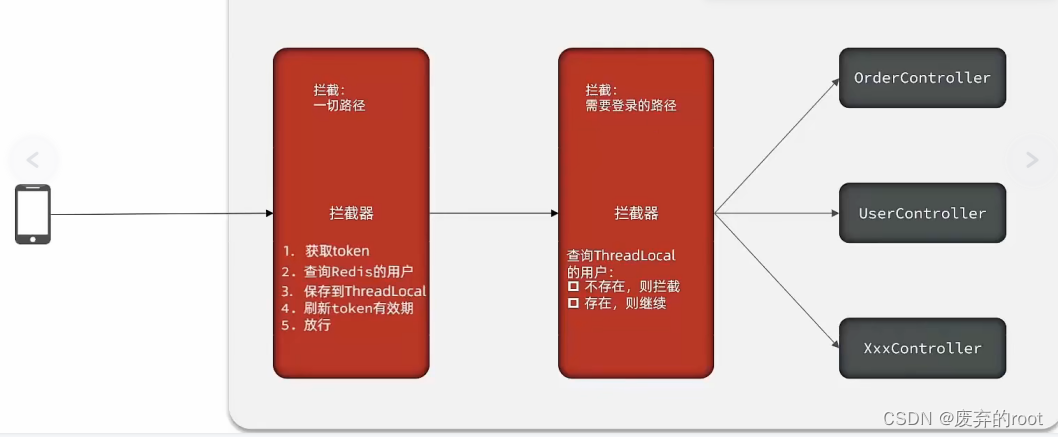

Redis功能实战篇之Session共享

1.使用redis共享session来实现用户登录以及token刷新 当用户请求我们的nginx服务器,nginx基于七层模型走的事HTTP协议,可以实现基于Lua直接绕开tomcat访问redis,也可以作为静态资源服务器,轻松扛下上万并发, 负载均衡…...

leetcode235. 二叉搜索树的最近公共祖先(java)

二叉搜索树的最近公共祖先 题目描述递归 剪枝代码演示: 上期经典 题目描述 难度 - 中等 LC235 二叉搜索树的最近公共祖先 给定一个二叉搜索树, 找到该树中两个指定节点的最近公共祖先。 百度百科中最近公共祖先的定义为:“对于有根树 T 的两个结点 p、q…...

超强干货整理!2026GEO排名查询监测系统排名,适配多场景企业需求

2026年,AI搜索主导信息分发逻辑,GEO(生成式引擎优化)成为企业品牌曝光、流量增长的核心抓手。对企业而言,GEO优化的关键不仅是“铺内容、做适配”,更在于“精准监测、科学优化”——唯有实时掌握AI搜索排名…...

)

Linux 软件包管理(含上机实例)

文章目录软件包管理一、知识要点1.rpm作用2.安装问题1:文件已被安装问题2:文件冲突问题3:未解决依赖关系3.卸载rpm包4.升级rpm包5.查询已安装的软件包的数据库6.验证软件包完整性二、YUM的使用yum简述yum命令集三、上机任务6 软件包管理 一、…...

UE5污水智慧数字化运维供应商

在环保行业不断发展的今天,污水运维的数字化转型成为了众多企业关注的焦点。UE5技术凭借其强大的功能,为污水智慧数字化运维带来了新的变革。在众多供应商中,江苏天清世恒环保节能集团有限公司(以下简称“天清世恒”)凭…...

PCB直流电阻精确估算:从基础公式到工程实践的全解析

1. 项目概述:为什么需要精确估算PCB直流电阻? 在硬件设计,尤其是电源完整性、信号完整性和热管理的世界里,PCB走线的直流电阻常常是一个被低估的关键参数。很多工程师在设计初期,注意力都集中在阻抗匹配、串扰和EMI上&…...

多版面文章活动公众号管理系统

文章营销活动系统概述基于微擎系统开发的在线交付文章营销推广类源码应用,支持多活动管理、多站点搭建及多版面切换。核心功能包括转发奖励积分或余额,适配文章推广、流量裂变及营销获客需求。核心功能多活动管理 后台可创建并管理多个营销活动ÿ…...

深圳 EMC 整改避坑指南:别让一次失败,毁掉整个产品周期

深圳,这座全球电子产业的心脏,每天都有上百款新产品从这里走向世界。但 2026 年 4 月 FCC 新规的落地,给无数深圳电子企业浇了一盆冷水:单次海外测试费暴涨至 6-10 万元,周期拉长到 6-12 周,一次整改失败&a…...

避开这些坑!新手用Python处理MODIS HDF数据时最常遇到的5个问题及解决方法

Python处理MODIS HDF数据的五大实战陷阱与解决方案 当你第一次用Python打开MODIS HDF文件时,那种期待感就像拆开一份科技礼物——直到GDAL抛出一连串晦涩的错误信息。作为遥感领域最常用的数据格式之一,MODIS HDF文件以其复杂的层级结构和特有的数据处理…...

APK Installer终极指南:在Windows上轻松安装Android应用的完整解决方案

APK Installer终极指南:在Windows上轻松安装Android应用的完整解决方案 【免费下载链接】APK-Installer An Android Application Installer for Windows 项目地址: https://gitcode.com/GitHub_Trending/ap/APK-Installer 你是否曾经想在Windows电脑上运行An…...

Ubuntu 22.04下编译安装Realtek RTL8852BE驱动,内核版本大于5.18和小于5.18的区别操作

Ubuntu 22.04下Realtek RTL8852BE驱动编译指南:内核版本差异全解析 当你兴奋地在新买的RedmiBook上安装Ubuntu 22.04,却发现WiFi图标神秘消失时,别慌——这很可能是因为Realtek RTL8852BE这块WiFi 6网卡在Linux下的驱动支持问题。作为一块性能…...

链路原型)

从通信系统设计视角:如何用Xilinx DDS Compiler v6.0高效搭建数字上变频(DUC)链路原型

基于Xilinx DDS Compiler v6.0的数字上变频链路设计与优化实战 在软件无线电(SDR)和雷达信号处理系统中,数字上变频(DUC)是实现基带信号到中频转换的核心环节。作为DUC链路中的本振信号发生器,Xilinx LogiC…...