Verilog 学习第五节(串口发送部分)

小梅哥串口部分学习part1

- 串口通信发送原理

- 串口通信发送的Verilog设计与调试

- 串口发送应用之发送数据

- 串口发送应用之采用状态机实现多字节数据发送

串口通信发送原理

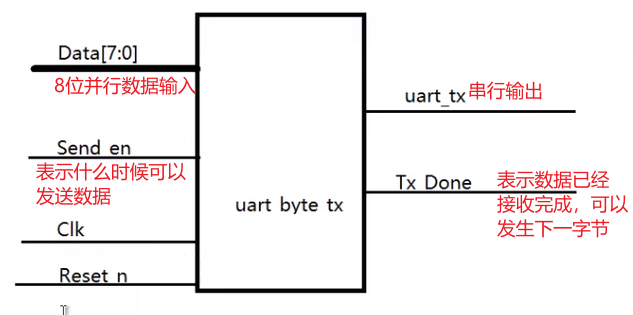

1:串口通信模块设计的目的是用来发送数据的,因此需要有一个数据输入端口

2:串口通信,支持不同的波特率,所以需要一个波特率设置端口

3:串口通信的本质就是将8位并行数据通过一根信号线,在不同的时刻传输并行数据的不同位,通过多个时刻,最终将8位并行数据全部传出

4:串口通信以1位的低电平标志串行传输的开始,待8位数据传输完成之后,在1位的高电平标志传输的结束

5:控制信号,控制并转串模块什么时候开始工作;什么时候一个数据发送完成?须有一个发送开始信号,以及一个发送完成信号

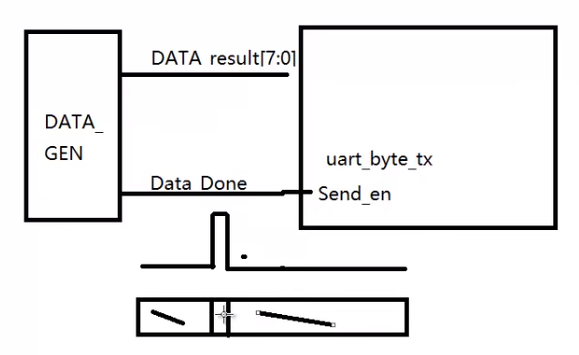

注:图中少了一个波特率设置端口

串口通信发送的Verilog设计与调试

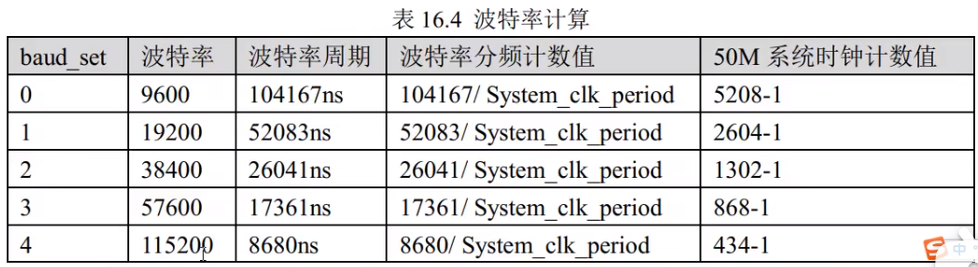

1:波特率为300起对应的计算公式为1000 000 000/300=3 333 333ns

3 333 333ns/20=166 666次 对应的是18位,所以一般有关波特率设置的端口设置的最大值为18位计数

源代码

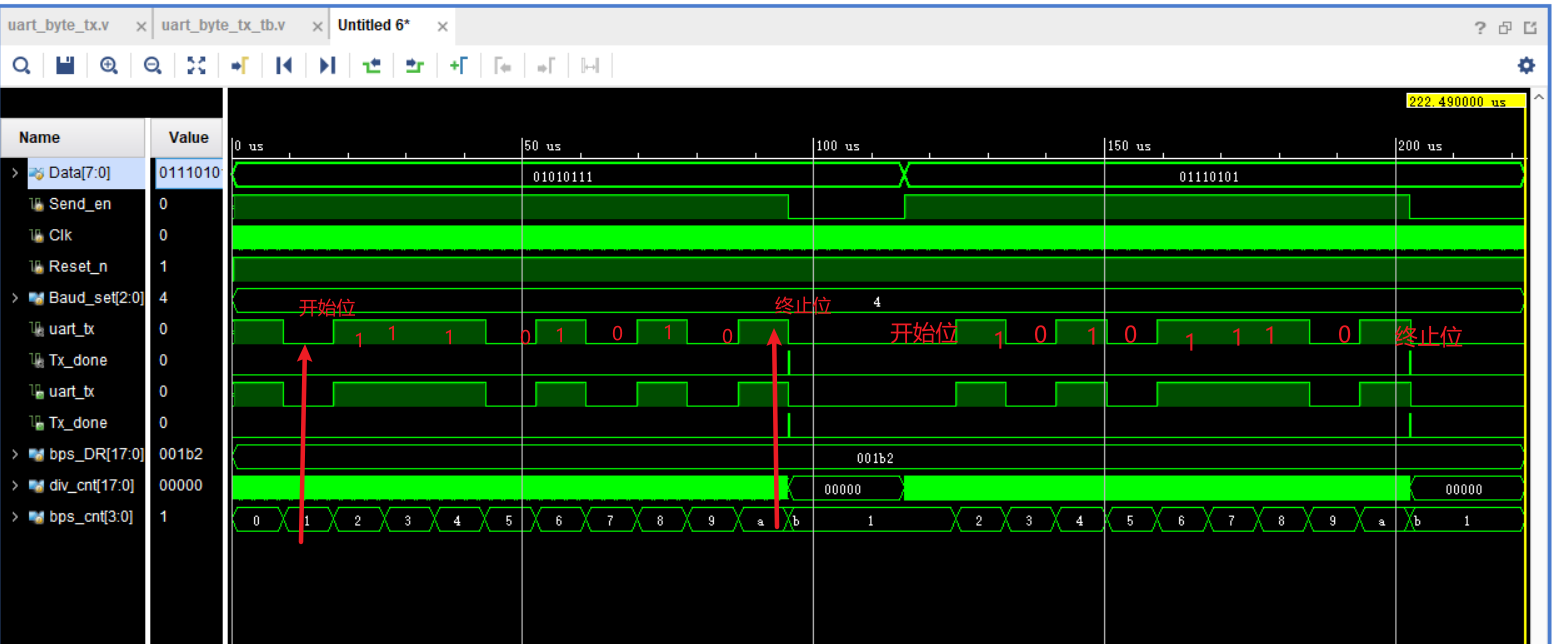

module uart_byte_tx(input [7:0]Data,input Send_en,input Clk,input Reset_n,input [2:0]Baud_set,output reg uart_tx,output reg Tx_done);//Baud_set=0 就让波特率=9600//Baud_set=1 就让波特率=19200//Baud_set=2 就让波特率=38400//Baud_set=3 就让波特率=57600//Baud_set=4 就让波特率=115200reg [17:0]bps_DR;always@(*)begincase(Baud_set)0:bps_DR=1000000000/9600/20;1:bps_DR=1000000000/19200/20;2:bps_DR=1000000000/38400/20;3:bps_DR=1000000000/57600/20;4:bps_DR=1000000000/115200/20;default:bps_DR=1000000000/9600/20;endcaseendwire bps_clk;assign bps_clk = (div_cnt == 1);reg [17:0]div_cnt;always@(posedge Clk or negedge Reset_n)beginif(!Reset_n)div_cnt<=0;else if(Send_en)beginif(div_cnt==bps_DR-1)div_cnt<=0;elsediv_cnt<=div_cnt+1'b1;endelsediv_cnt<=0;endreg [3:0]bps_cnt;always@(posedge Clk or negedge Reset_n)beginif(!Reset_n)bps_cnt<=0;else if(Send_en)beginif(bps_clk)beginif(bps_cnt==11)bps_cnt<=0;elsebps_cnt<=bps_cnt+1;endendelsebps_cnt<=1'b1;end//并串转换always@(posedge Clk or negedge Reset_n)beginif(!Reset_n)beginuart_tx<=1'b0;Tx_done<=1'b0;endelse begincase(bps_cnt)1:begin uart_tx<=1'b0;Tx_done=1'b0;end2:uart_tx<=Data[0];3:uart_tx<=Data[1];4:uart_tx<=Data[2];5:uart_tx<=Data[3];6:uart_tx<=Data[4];7:uart_tx<=Data[5];8:uart_tx<=Data[6];9:uart_tx<=Data[7];10:uart_tx<=1'b1;11:begin uart_tx<=1'b1;Tx_done=1'b1; end default: uart_tx<=1'b1;endcaseendendendmodule测试文件

`timescale 1ns / 1ns

module uart_byte_tx_tb();reg [7:0]Data;reg Send_en;reg Clk;reg Reset_n;reg [2:0]Baud_set;wire uart_tx;wire Tx_done;uart_byte_tx uart_byte_tx(.Data(Data),.Send_en(Send_en),.Clk(Clk),.Reset_n(Reset_n),.Baud_set(Baud_set),.uart_tx(uart_tx),.Tx_done(Tx_done));initial Clk=0;always#10 Clk=!Clk;initial beginReset_n=0;Send_en=0;Data=0;Baud_set=4;#201;Reset_n=1;Data=8'h57;Send_en=1;#20;//下面的意思是一直在等待Tx_done变量,没有等到的话就不往下进行@(posedge Tx_done);Send_en=0;#20000;Data=8'h75;Send_en=1;#20;@(posedge Tx_done);Send_en=0;#20000;$stop;endendmodule仿真截图

收获:

1:在有多级if else的时候要记得加上begin end 否则可能造成识别不出来,导致结果错误~

2:在主代码中为了模拟实际电路中的赋值情况,可以设置#10代表延时时间,上面记得加`timescale 1ns/1ns,因为在下载到电路板上以及vivado识别的时候会自动略去这里的延时,但是这么写对实际电路仿真的时候却又非常有用

串口发送应用之发送数据

题目:使用上面的串口发送模块,设计一个数据发送器,每10ms以115200的波特率发送一个数据,每次发送的数据比前一个数据大一(计数器)

uart_byte_tx代码

module uart_byte_tx(input [7:0]Data,input Send_Go,input Clk,input Reset_n,input [2:0]Baud_set,output reg uart_tx,output reg Tx_done);reg Send_en;always@(posedge Clk or negedge Reset_n)beginif(!Reset_n)Send_en<=0;else if(Send_Go)Send_en<=1;else if(Tx_done)Send_en <= 0;endreg [7:0]r_Data;always@(posedge Clk)beginif(Send_Go)r_Data<=Data;elser_Data<=r_Data;end//Baud_set=0 就让波特率=9600//Baud_set=1 就让波特率=19200//Baud_set=2 就让波特率=38400//Baud_set=3 就让波特率=57600//Baud_set=4 就让波特率=115200reg [17:0]bps_DR;always@(*)begincase(Baud_set)0:bps_DR=1000000000/9600/20;1:bps_DR=1000000000/19200/20;2:bps_DR=1000000000/38400/20;3:bps_DR=1000000000/57600/20;4:bps_DR=1000000000/115200/20;default:bps_DR=1000000000/9600/20;endcaseendwire bps_clk;assign bps_clk = (div_cnt == 1);reg [17:0]div_cnt;always@(posedge Clk or negedge Reset_n)beginif(!Reset_n)div_cnt<=0;else if(Send_en)beginif(div_cnt==bps_DR-1)div_cnt<=0;elsediv_cnt<=div_cnt+1'b1;endelsediv_cnt<=0;endreg [3:0]bps_cnt;always@(posedge Clk or negedge Reset_n)beginif(!Reset_n)bps_cnt<=0;else if(Send_en)beginif(bps_clk)beginif(bps_cnt==11)bps_cnt<=0;elsebps_cnt<=bps_cnt+1;endendelsebps_cnt<=1'b0;end//并串转换always@(posedge Clk or negedge Reset_n)beginif(!Reset_n)beginuart_tx<=1'b0;endelse begincase(bps_cnt)1:uart_tx<=1'b0;2:uart_tx<=r_Data[0];3:uart_tx<=r_Data[1];4:uart_tx<=r_Data[2];5:uart_tx<=r_Data[3];6:uart_tx<=r_Data[4];7:uart_tx<=r_Data[5];8:uart_tx<=r_Data[6];9:uart_tx<=r_Data[7];10:uart_tx<=1'b1;11: uart_tx<=1'b1;default: uart_tx<=1'b1;endcaseendendalways@(posedge Clk or negedge Reset_n)beginif(!Reset_n)Tx_done<=1'b0;else if((bps_cnt==10)&&(bps_clk==1))Tx_done<=1'b1;else Tx_done<=1'b0;end

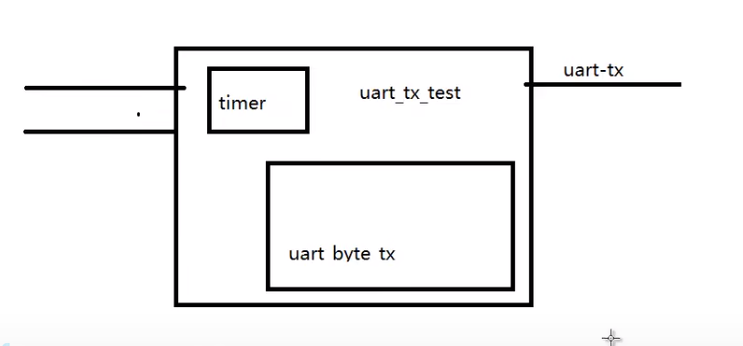

endmoduleuart_tx_test代码顶层模块

module uart_tx_test(input Clk,input Reset_n,output uart_tx);reg [7:0]Data;reg Send_Go;wire Tx_done;uart_byte_tx uart_byte_tx(.Data(Data),.Send_Go(Send_Go),.Clk(Clk),.Reset_n(Reset_n),.Baud_set(3'd4),.uart_tx(uart_tx),.Tx_done(Tx_done));//首先计时10msreg [18:0] cnt;always@(posedge Clk or negedge Reset_n)beginif(!Reset_n)cnt<=0;else if(cnt==499999)cnt<=0;elsecnt<=cnt+1'b1;end//接着设计何时Send_Go开始发送数据always@(posedge Clk or negedge Reset_n)beginif(!Reset_n)Send_Go<=0;else if(cnt==1)Send_Go<=1;//这里需要注意本来的Send_en是一段时间的信号,比较长,但是Send_Go属于脉冲信号就一下else Send_Go<=0;end//接着设计数据变化always@(posedge Clk or negedge Reset_n)beginif(!Reset_n)Data<=0;else if(Tx_done)Data<=Data+1;endendmoduleuart_tx_test_tb测试文件

`timescale 1ns / 1ns

module uart_tx_test_tb();reg Clk;reg Reset_n;wire uart_tx;

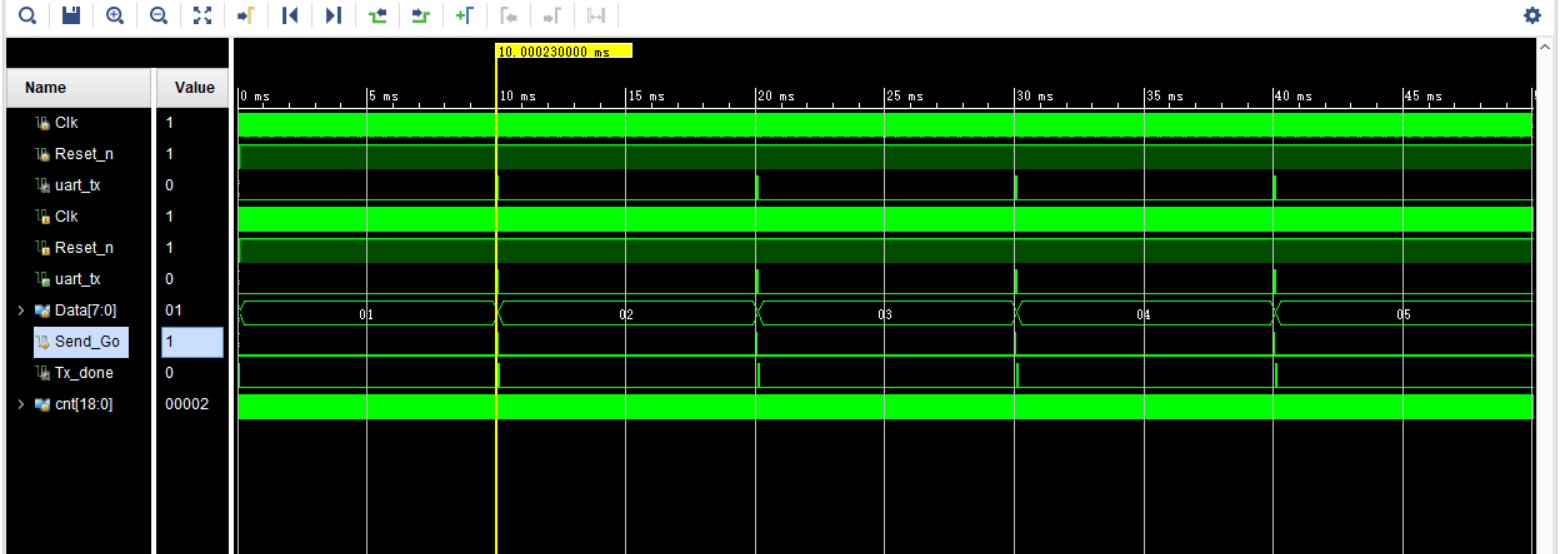

uart_tx_test uart_tx_test(.Clk(Clk),.Reset_n(Reset_n),.uart_tx(uart_tx));initial Clk=0;always #10 Clk=!Clk;initial begin Reset_n=0;#201;Reset_n=1;#50000000;$stop;endendmodule仿真截图

收获

1:对于一些很重要的控制信号最好单独拿出来写,参杂在一些其他功能中很可能会产生其他的影响,例如Tx_done

2:Go一般是单脉冲信号,en是电平信号

串口发送应用之采用状态机实现多字节数据发送

有些人会了8位的串口传送数据但是总会有一些问题例如,

1.ADC,采样的结果是12位的,怎么使用串口发送

2.16位的数据,怎样通过串口发送

3.有多个字节的数据通过串口发送

不能直接将8位改成12位、16位,因为UART规定了,发送的数据位只能有6、7、8位所以应该把大于8位的字节分成多个字节进行发送

三种情况:

1:没有开始发送(上一次的已经发送完成,新的40位数据的发送请求没有出现)

2:来了发送40位数据的请求信号

3:依次发送数据的状态

第一个状态:第一种情况的时候,咱干什么事情?等待传输请求(Trans_Go)的到来,Data40[7:0]给到uart_byte_tx的Data,并同时产生Send_Go信号,启动第一个字节的发送

接着应该等待,等待Tx_Done信号的到来

40位数据是否发完了?发完了,回到第一个状态继续等Trans_Go,没发完,启动下一个8位数据的发送

源代码:

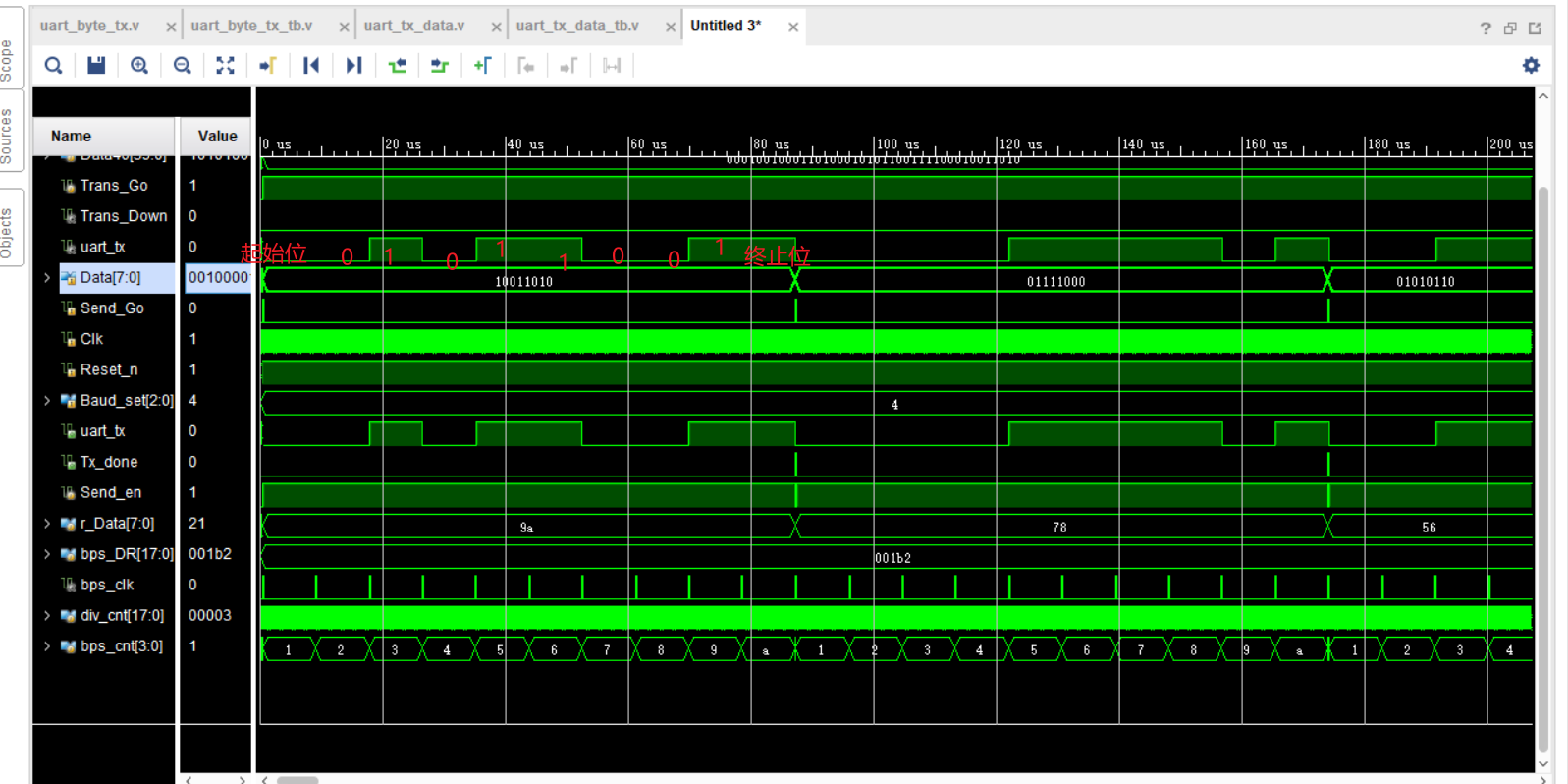

//该模块完成的功能是采用状态机实现多字节数据发送

module uart_tx_data(input Clk,input Reset_n,input [39:0]Data40,input Trans_Go,//表示合适开始发送数据,即传输请求output reg Trans_Down,//表示一次40位的数据传输完成output uart_tx);reg [7:0]Data;reg Send_Go;wire Tx_done;uart_byte_tx uart_byte_tx(.Data(Data),.Send_Go(Send_Go),.Clk(Clk),.Reset_n(Reset_n),.Baud_set(3'h4),.uart_tx(uart_tx),.Tx_done(Tx_done));reg [2:0]state;always@(posedge Clk or negedge Reset_n)beginif(!Reset_n)beginstate<=0;Data<=0;Send_Go<=0;Trans_Down<=0;end//下面部分也可以用case语句实现,记得加default~else if(state==0)beginTrans_Down<=0;if(Trans_Go)beginData<=Data40[7:0];state<=1;Send_Go<=1;endelse beginData<=Data;state<=0;Send_Go<=0;endendelse if(state==1)beginif(Tx_done)beginData<=Data40[15:8];state<=2;Send_Go<=1;endelse beginData<=Data;state<=1;Send_Go<=0;endendelse if(state==2)beginif(Tx_done)beginData<=Data40[23:16];state<=3;Send_Go<=1;endelse beginData<=Data;state<=2;Send_Go<=0;endendelse if(state==3)beginif(Tx_done)beginData<=Data40[31:24];state<=4;Send_Go<=1;endelse beginData<=Data;state<=3;Send_Go<=0;endendelse if(state==4)beginif(Tx_done)beginData<=Data40[39:32];state<=5;Send_Go<=1;endelse beginData<=Data;state<=4;Send_Go<=0;endend else if(state==5)beginif(Tx_done)beginstate<=0;Trans_Down<=1;Send_Go<=0;endelse beginData<=Data;state<=5;Send_Go<=0;endend endendmodule测试文件:

`timescale 1ns / 1nsmodule uart_tx_data_tb();reg Clk;reg Reset_n;reg [39:0]Data40;reg Trans_Go;wire Trans_Down;wire uart_tx;uart_tx_data uart_tx_data(Clk,Reset_n,Data40,Trans_Go,//表示合适开始发送数据,即传输请求Trans_Down,//表示一次40位的数据传输完成uart_tx);initial Clk=0;always #10 Clk=!Clk;initial beginReset_n=0;Data40=0;Trans_Go=0;#201Reset_n=1;#201Data40=40'h123456789a;Trans_Go=1;@(posedge Trans_Down);Trans_Go=0;#201Data40=40'ha987654321;Trans_Go=1;@(posedge Trans_Down);#200000$stop;end

endmodule仿真截图:

任务:

1:优化状态机,实现只要2个或3个状态实现发送的功能,并易于修改为发送任意个字节的数据(加个计数器进行二级验证~)

2:思考不使用状态机实现的方法

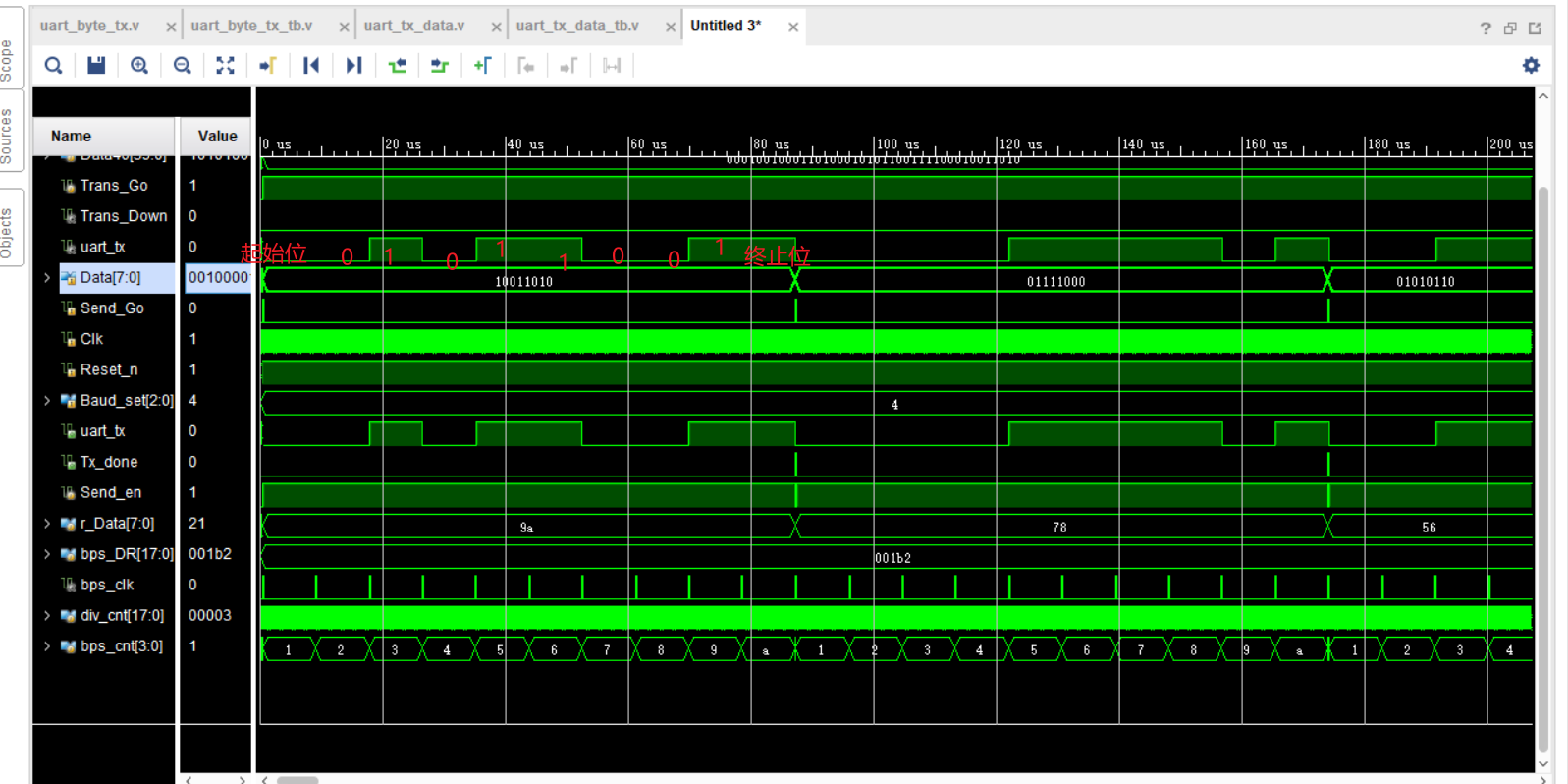

任务一代码(已进行仿真)

//该模块完成的功能是采用状态机实现多字节数据发送

module uart_tx_data2(input Clk,input Reset_n,input [39:0]Data40,input Trans_Go,//表示合适开始发送数据,即传输请求output reg Trans_Down,//表示一次40位的数据传输完成output uart_tx);reg [7:0]Data;reg Send_Go;wire Tx_done;uart_byte_tx uart_byte_tx(.Data(Data),.Send_Go(Send_Go),.Clk(Clk),.Reset_n(Reset_n),.Baud_set(3'h4),.uart_tx(uart_tx),.Tx_done(Tx_done));reg [2:0]state;//用来记录当前发送到第几个字节了reg [2:0]cnt;always@(posedge Clk or negedge Reset_n)beginif(!Reset_n)begincnt<=0;end else if(Tx_done) beginif(cnt==4)cnt<=0;elsecnt<=cnt+1;endendalways@(posedge Clk or negedge Reset_n)beginif(!Reset_n)beginstate<=0;Data<=0;Send_Go<=0;Trans_Down<=0;end//下面部分也可以用case语句实现,记得加default~else if(state==0)beginTrans_Down<=0;if(Trans_Go)beginTrans_Down<=0;if(Tx_done)begincase(cnt)0:begin Data<=Data40[7:0]; state<=0;end 1:begin Data<=Data40[15:8];state<=0;end2:begin Data<=Data40[23:16];state<=0;end3:begin Data<=Data40[31:24];state<=0;end4:begin Data<=Data40[39:32];state<=1;enddefault:Data<=Data;endcaseSend_Go<=1;endelse beginData<=Data;state<=0;Send_Go<=0;endendend else if(state==1)beginif(Tx_done)beginstate<=0;Trans_Down<=1;Send_Go<=0;endelse beginData<=Data;state<=1;Send_Go<=0;endend endendmodule相关文章:

Verilog 学习第五节(串口发送部分)

小梅哥串口部分学习part1 串口通信发送原理串口通信发送的Verilog设计与调试串口发送应用之发送数据串口发送应用之采用状态机实现多字节数据发送串口通信发送原理 1:串口通信模块设计的目的是用来发送数据的,因此需要有一个数据输入端口 2:…...

破解遗留系统快速重构的5步心法(附实例)

前两天和一个架构师朋友闲聊,说到了 「重构」 这个话题,他们公司早年间上线的项目系统,因一直没专人在演进过程中为代码质量负责,导致现在代码越来越混乱,逐渐堆积成“屎山”,目前的维护成本已远高于重新开…...

信号量(上)实验

实验1:解决订票终端的临界区管理 订票终端是解决冲突问题,所以信号量的值是1 #include <stdio.h> #include <pthread.h> #include <unistd.h> #include <semaphore.h> int ticketAmout 2; // 票的数量: 全局变量 sem_t mutex…...

阿里5年,一个女工对软件测试的理解

成为一个优秀的测试工程师需要具备哪些知识和经验? 针对这个问题,可以直接拆分以下三个小问题来详细说明: 1、优秀软件测试工程师的标准是什么? 2、一个合格的测试工程师需要具备哪些专业知识? 3、一个合格的测试工程…...

前端练习项目

30 Web Projects 30 多个带有 HTML、CSS 和 JavaScript 的 Web 项目,由 Packt Publishing 提供 https://github.com/PacktPublishing/30-Web-Projects-with-HTML-CSS-and-JavaScript Small projects https://github.com/WebDevVikramChoudhary/small_projects_for_…...

sql复习(set运算符、高级子查询)

一、set运算符 union:得到两个查询结果的并集,并且⾃动去掉重复⾏。不会排序 union all:得到两个查询结果的并集,不会去掉重复⾏。也不会排序 intersect:得到两个查询结果的交集,并且按照结果集的第⼀个列进…...

整车电源的几种模式:OFF/ACC/RUN/CRANK

本文框架1.前言2. 四种电源模式2.1 OFF模式2.2 ACC模式2.3 ON模式2.4 CRANK模式3. KL15/KL301.前言 在诊断或者网络管理相关模块开发对客户的需求进行梳理时,经常会看到客户对不同车辆模式下处理策略的需求,如果前期没接触过这几种模式,可能…...

踩了大坑:wordpress后台 无法将上传的文件移动至wp-content

一、问题描述 今天迁移了wordpress站点至新服务器,结果上传图片出现“无法将上传的文件移动至wp-content/uploads”的提示,这是怎么回事,为什么会这样。 报错如下: 2023/02/20 08:57:48 [error] 9861#9861: *79624 FastCGI sen…...

page cache设计及实现

你好,我是安然无虞。 page cache的设计及实现 page cache 本质上也是一个哈希桶, 它是按照页的数量进行映射的. 当 central cache 向 page cache 申请内存时, page cache 先检查对应位置是否有span, 如果没有则向更大页去寻找一个span, 如果找到则分裂成两个. 比如…...

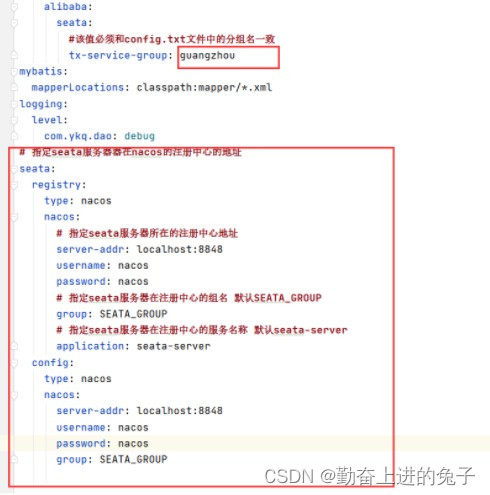

使用seata来解决分布式事务

文章目录 目录 文章目录 前言 一、Seata的执行流程如下 二、使用步骤 三、配置微服务客户端 总结 前言 Seata部署指南 Seata 是一款开源的分布式事务解决方案,致力于提供高性能和简单易用的分布式事务服务。Seata 将为用户提供了 AT、TCC、SAGA 和 XA 事务模…...

推荐一款新的自动化测试框架:DrissionPage

今天给大家推荐一款基于Python的网页自动化工具:DrissionPage。这款工具既能控制浏览器,也能收发数据包,甚至能把两者合而为一,简单来说:集合了WEB浏览器自动化的便利性和 requests 的高效率。 一、DrissionPage产生背…...

MQ系列面试

先来说说什么是MQ,MQ与多线程之间的区别MQ是消息中间件 可以实现异步 多线程也可以实现异步使用传统http协议方式调用接口存在的缺点如果服务器端没有及时的响应给客户端的时候,容易造成客户端阻塞等待。服务器响应超时 客户端发送重试机制 需要考虑避免…...

一句话设计模式2:原型模式

原型模式:每次得到一个新对象。 文章目录 原型模式:每次得到一个新对象。前言一、原型模式和new的区别二、如何实现原型模式1. 什么clone接口2. 开始使用,并验证浅clone效果3. 深度clone(也就是address也要复制一份)总结前言 原型模式可以说是目前接触的设计模式中,比较无用的…...

c++11特性与c++17特性

1、自动类型推导auto // C11 auto func1() -> int // 需要指定返回值类型 {return 10; }auto func2() -> std::function<void()> {auto lambda []() { };return lambda; }// c17 // 之后无需指定返回值类型 auto func1() {return 10; }auto func2() {auto lambda…...

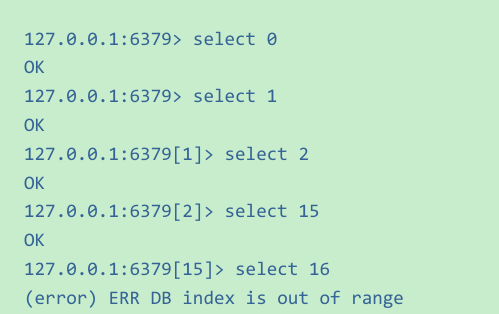

Redis02: Redis基础命令

一、基础命令 先启动redis服务,使用redis-cli客户端连到redis数据库里面 1. 获取符合规则的键: keys 要点: (1)keys 后面可以指定正则表达式 (2)在生产环境下建议禁用keys命令,因为这个命令会查…...

MDK的HardFault硬件异常和NMI异常原因总结

发出来,出现问题自行比对,现在一些代码,也会对这个进行分析。硬件异常原因: Unaligned load or store Load 或者 store 指令访问未对齐地址 Undefined Instruction 执行 ARM 未定义的指令 EPSR Fault 当前程序没有在 Thumb 状态下…...

视频图像质量诊断

视频图像质量诊断有哪些原理,视频图像质量诊断有哪些算法? 视频图像质量诊断技术支持对视频黑屏、视频干扰、视频卡顿、视频遮挡、亮度异常、图像偏色、视频模糊、视频冻结、视频抖动、场景变更、无字符叠加等20种视频图像质量异常进行诊断,…...

make、Makefile项目自动化构建工具

环境:centos7.6,腾讯云服务器Linux文章都放在了专栏:【Linux】欢迎支持订阅🌹前言自动化构建工具是干什么的呢?主要是为了让我们对指令进行一些设置,就比如说,假如一个项目里有很多个源文件&…...

Linux系统之Uboot、Kernel、Busybox思考之一

目录 一 基础环境 1 硬件基础环境 2 软件基础环境 2.1 Uboot 2.2 内核 2.3 文件系统 二 启动过程 1 2 3 4 5 6 7 一 基础环境 1 硬件基础环境 CPU、内存和FLASH为基础环境,有了这三样,程序就可以跑起来。在此基础上补充各种外设ÿ…...

CCNP350-401学习笔记(401-450题)

401、What is the function of vBond in a Cisco SDWAN deployment? A. initiating connections with SD-WAN routers automatically B. pushing of configuration toward SD-WAN routersC. onboarding of SDWAN routers into the SD-WAN overlay D. gathering telemetry dat…...

Gemma-3-12B-IT WebUI保姆级教程:多模型切换与Gemma-3-27B对比体验

Gemma-3-12B-IT WebUI保姆级教程:多模型切换与Gemma-3-27B对比体验 1. 开篇:为什么你需要一个更聪明的AI助手? 想象一下,你手头有一个能写代码、能解答技术难题、还能陪你聊天的AI助手。它运行在你自己的服务器上,数…...

springboot+vue基于web的社区养老服务系统的设计系统

目录同行可拿货,招校园代理 ,本人源头供货商系统功能模块分析服务预约模块社区互动模块后台管理模块技术实现要点项目技术支持源码获取详细视频演示 :文章底部获取博主联系方式!同行可合作同行可拿货,招校园代理 ,本人源头供货商 系统功能模块分析 用户…...

Phi-4-mini-reasoning惊艳效果:自动识别题目所属数学分支并推荐解法策略

Phi-4-mini-reasoning惊艳效果:自动识别题目所属数学分支并推荐解法策略 1. 模型介绍 Phi-4-mini-reasoning是微软推出的3.8B参数轻量级开源模型,专为数学推理、逻辑推导和多步解题等强逻辑任务设计。这个模型主打"小参数、强推理、长上下文、低延…...

射频工程师必备:如何用ADS仿真优化PA和LNA的噪声系数?

射频工程师必备:ADS仿真优化PA与LNA噪声系数的实战手册 在5G和物联网设备爆发式增长的今天,射频前端模块的性能直接决定了通信质量的上限。作为射频电路设计的核心环节,功率放大器(PA)和低噪声放大器(LNA)的噪声系数优化,往往是决…...

避开Verilog数据转换的坑:ASCII码转16进制时,大小写处理你真的做对了吗?

Verilog字符转换实战:如何正确处理ASCII与十六进制的大小写问题 在数字系统设计中,数据格式转换是最基础却又最容易出错的环节之一。最近在review团队一位新成员的UART通信模块代码时,发现一个典型的"大小写陷阱"——当十六进制数据…...

零基础玩转像素心智:手把手教你用情绪解码器分析用户评论

零基础玩转像素心智:手把手教你用情绪解码器分析用户评论 1. 认识像素心智情绪解码器 1.1 什么是情绪解码器 像素心智情绪解码器(Pixel Mind Decoder)是一款基于M2LOrder核心引擎构建的AI情绪识别工具。它将复杂的自然语言处理技术封装在一个充满复古游戏风格的1…...

如何快速实现Tale博客系统国际化:多语言博客搭建完整指南

如何快速实现Tale博客系统国际化:多语言博客搭建完整指南 【免费下载链接】tale 🦄 Best beautiful java blog, worth a try 项目地址: https://gitcode.com/gh_mirrors/ta/tale Tale博客系统是一款优雅的Java博客程序,提供了强大的内…...

Phi-3-mini-4k-instruct-gguf多场景落地:客服话术优化、会议纪要提炼、周报生成实战

Phi-3-mini-4k-instruct-gguf多场景落地:客服话术优化、会议纪要提炼、周报生成实战 1. 轻量级文本生成利器介绍 Phi-3-mini-4k-instruct-gguf是微软推出的轻量级文本生成模型,特别适合处理日常办公场景中的文本任务。这个模型体积小巧但能力出众&…...

三三复制商业模式系统介绍

三三复制商业模式系统介绍:裂变逻辑与合规落地全解析在数字经济时代,社交电商与分销模式的创新成为企业突破增长瓶颈的关键。三三复制模式以其几何级数的裂变效率、清晰的层级收益结构和低门槛参与机制,在电商、直销等领域展现出强大的生命力…...

华为交换机MAC地址漂移检测与风暴抑制联动配置指南

1. 华为交换机MAC地址漂移检测原理与实战 刚接触网络运维时,第一次遇到MAC地址漂移报警简直一头雾水。后来才发现,这其实是交换机在提醒我们:"兄弟,你的网络里可能有环路!" MAC地址漂移的本质是同一个MAC地址…...