FIR滤波器简述及FPGA仿真验证

数字滤波器的设计,本项目做的数字滤波器准确来说是FIR滤波器。

FIR滤波器(有限冲激响应滤波器),与另一种基本类型的数字滤波器——IIR滤波器(无限冲击响应滤波器)相对应,其实就是将所输入的信号都看成是离散的,用离散的冲击信号代替实际的信号。对于FIR滤波器而言,就是将有限个最近输入的冲击信号进行加权平均运算得到新的输出信号,用以滤除其他不需要的信号。而IIR滤波器不仅需要对输入信号进行加权平均,对输出信号也要进行加权平均,从而得到新的输出信号,滤除其他不需要的信号。

FIR滤波器的算法就是类似卷积的算法。核心其实就是加权平均,即:

Y(n)=h(0)*x(n)+h(1)*x(n-1)+h(2)*x(n-2)+h(3)*x(n-3)+……+ h(N-1)*x(n-N+1)

X(n)是我们待滤波的信号,h(n)是滤波器系数。

在用Verilog编程之前用MATLAB计算出h(k)(k=0~N-1)权重。

对于FPGA而言,有两种方法可以实现FIR滤波器的设计,一种是通过Verilog语言编写,另一种是通过IP核实现。

用Verilog语言编写需要通过Matlab的工具箱生成h(k)(k=0~N-1)权重。而用IP核的话直接在软件里生成就行,本文是以Quartus软件为例。

本文刚开始还不想用IP核来生成的,并介绍了使用Matlab中FDATOOL工具箱的方法,然后后面改用了IP核的方式来完成FIR滤波器的设计与仿真。

Fdatool生成FIR相关的系数

打开matlab的fdatool工具箱。

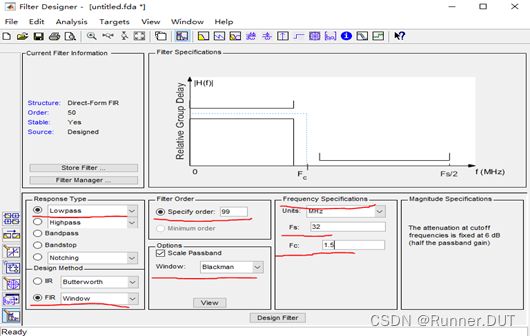

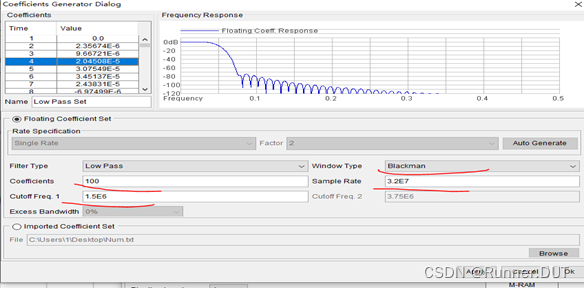

然后选择设计需要的滤波器,低通,FIR滤波器,窗函数设计(Window),采用布莱克曼窗(Blackman),99阶(这样有100个系数),采样频率50MHz,通带频率1.5MHz。

按照上图设定参数后,在上图中Specify order是阶数,Fc是截止频率,Fs是序列的采样频率。点击Design Filter。

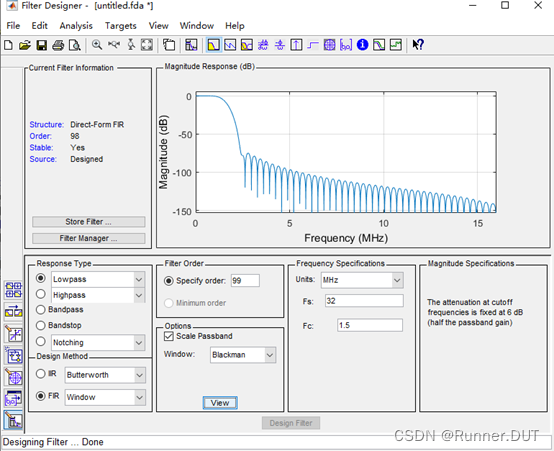

设计完成了,可以看到显示的频率为0~Fs/2的幅频响应,大概在2MHz左右幅度下降为原来的-60dB以下,也就是正常幅度的千分之一。

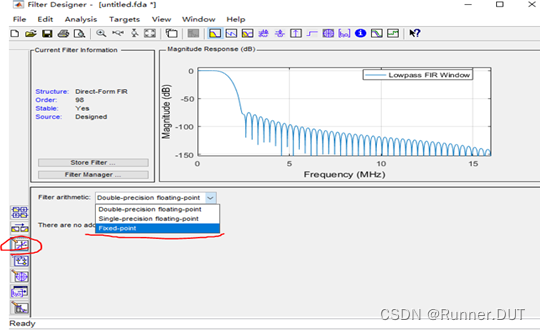

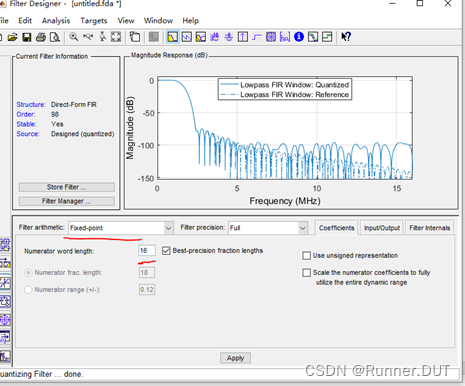

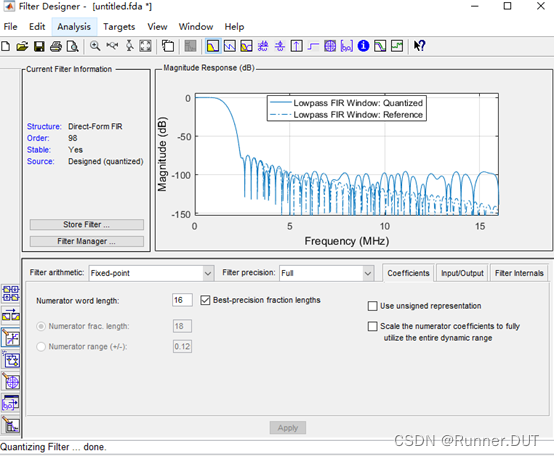

由于在FPGA中计算浮点数是一件很麻烦的事情,此处就设置成定点数,且位数越高越精确,这里设置的是16位定点数来量化。

然后点击Apply。下方图片中实线是量化后的,虚线是未量化过的精准的。可以看到虽然5MHz之后的阻带衰减不如原来,但也可以衰减到-100dB,也就是原来的1/100000。这个衰减程度已经足够了。

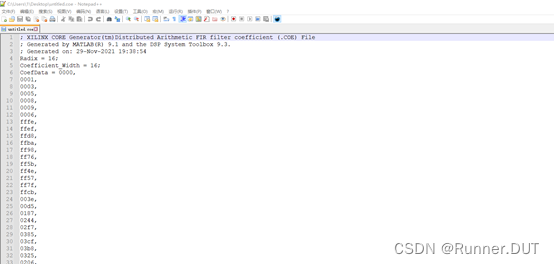

最后是导出系数。直接通过file——export导出的是没有经过量化的系数,通过量化的系数要经过Targets———XILINX Coefficient file导出.coe文件就可以查看量化后的数了。

新建Quartus工程设计FIR滤波器

首先创建好工程,这里不再赘述。

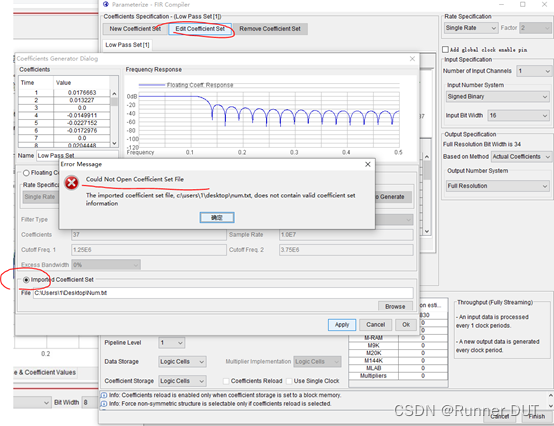

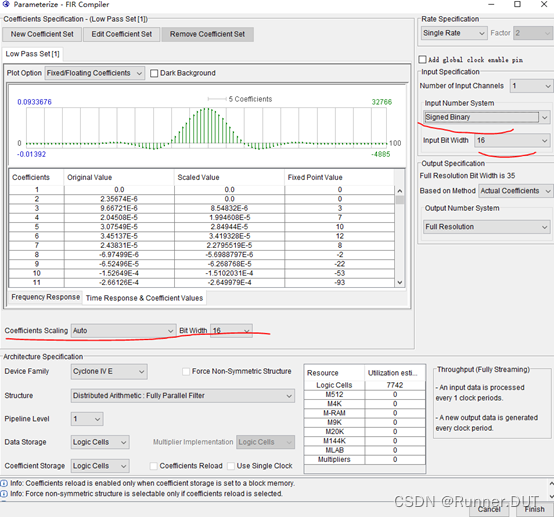

然后,生成FIR Compiler II 的IP核,随意先生成了一个,但是好像还不太对。后来才知道,应该选用FIR Complier v13.1的FIR IP核。首先进入step1,最开始要设置好滤波器系数,但是不知道为什么就是导不进去。如果可以导进去的话那么matlab中的fdatool工具箱我们就是用到了,但是问题就是导不进去。不过好在点击上面那个floating Coefficient Set可以自动生成浮点数的滤波器系数。

于是我们简单设置以下,让IP核自动生成相应的系数。

然后设置一下数据位宽

Step2的内容就全部勾选即可,然后进入step3自动生成IP核。

仿真

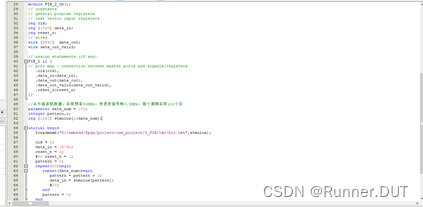

采用IP核的方式产生的FIR滤波器仿真的话直接通过编辑textbench仿真文件的方式仿真;采用Verilog语言编写方式产生的FIR滤波器在编辑textbench仿真文件之前还需对顶层.v文件进行编辑。

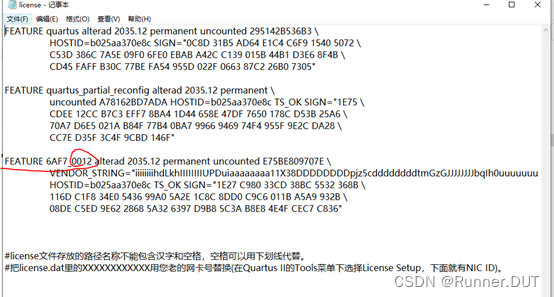

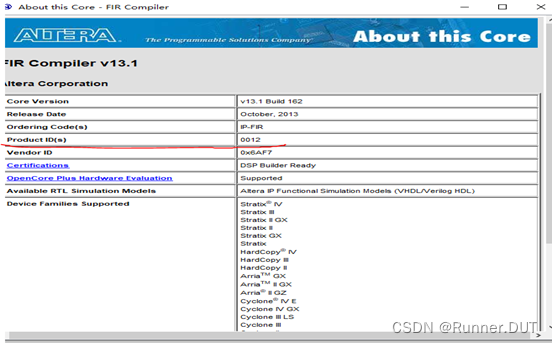

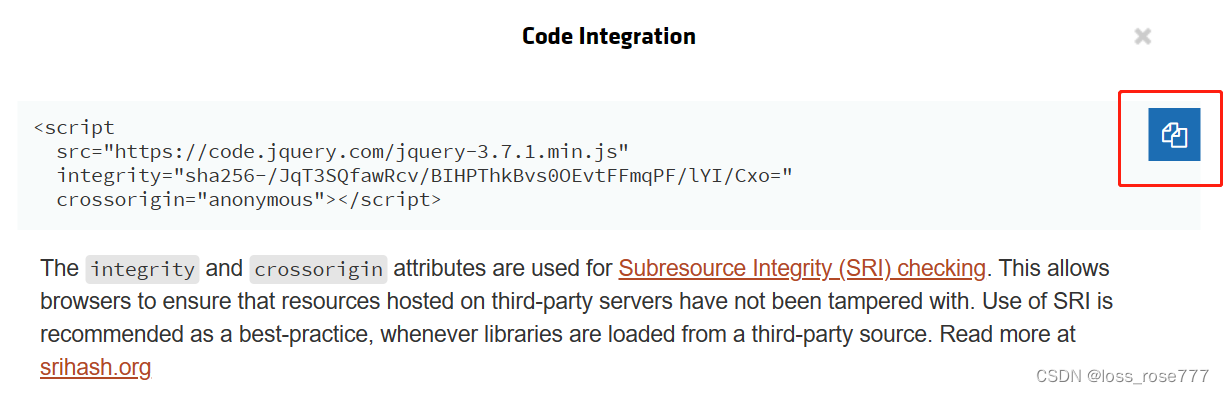

首先介绍采用IP核的方式仿真,一开始遇到的问题是关于FIR Compliter的IP核没有破解,后来需要改一下Licence文件才能使用。如下图所示,原来红框中是00A2,后来改成FIR Compliter的IP核的ID号,然后重启就能正常编译使用了。

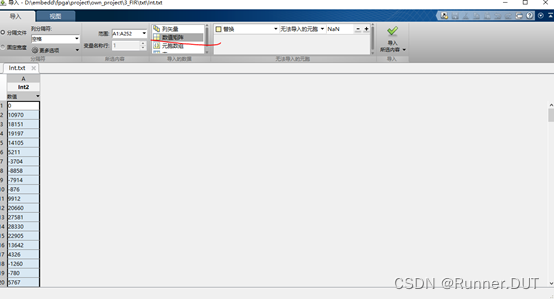

然后遇到的问题是待滤波的数据和滤波后的数据分别是怎样输入进去以及怎样输出保存起来的。先做一种尝试,待滤波的数据通过Matlab生成并存放在.txt文档中,然后在仿真文件里调用该文档的数据,不过要注意采样周期和采样数据点的问题,也就是时序的问题。输出的数据的话先不用管,直接通过仿真看滤波后输出数据的变化即可。

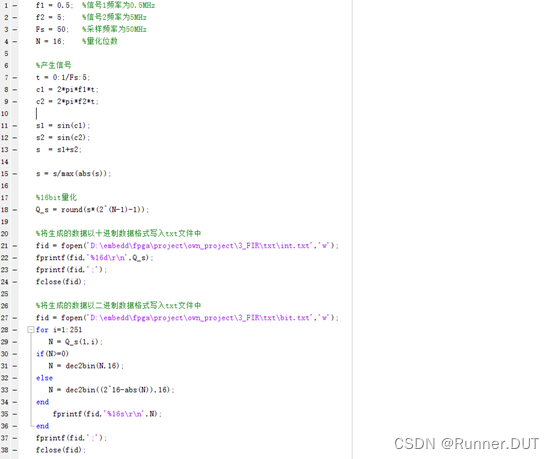

编写Matlab程序产生待滤波信号,产生两个信号0.5MHz和5MHz,采样频率50MHz,采样5个周期,进行16-bit量化,并把量化后的数据写到.txt文件中。目前的问题在于怎么转换成16位二进制数。最后还是选择一种比较好的方法。首先判断读取的一个数是否大于零,如果大于零,直接采用dec2bin函数转换成16位的二进制数;如果小于零,则用216 减去该数的绝对值,再用dec2bin函数将其转换成16位的二进制数。主要卡在如何分别读取每一个数上面,还是对matlab的操作不太熟悉。不过好在最后还是弄出来了。Matlab相关程序如下图所示。

减去该数的绝对值,再用dec2bin函数将其转换成16位的二进制数。主要卡在如何分别读取每一个数上面,还是对matlab的操作不太熟悉。不过好在最后还是弄出来了。Matlab相关程序如下图所示。

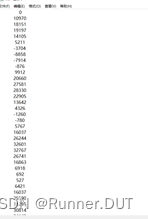

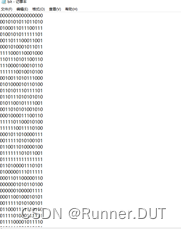

最终生成的十进制数和二进制数的txt文件内容如下图所示。

然后再学习一下FFT算法,利用matlab先对输入的数据进行频谱分析。有两种方法,一种是编写程序的方法,在MATLAB中,FFT的调用函数主要有两个,即:Y=FFT(X)和Y=FFT(X,N)。网上的例子:

clf;

fs=100;N=128; %采样频率和数据点数

n=0:N-1;t=n/fs; %时间序列

x=0.5*sin(2*pi*15*t)+2*sin(2*pi*40*t); %信号

y=fft(x,N); %对信号进行快速Fourier变换

mag=abs(y); %求得Fourier变换后的振幅

f=n*fs/N; %频率序列

subplot(2,2,1),plot(f,mag); %绘出随频率变化的振幅

xlabel('频率/Hz');

ylabel('振幅');title('N=128');grid on;

一种是利用Simulink仿真模型的方法。首先导入数据,然后进入Simulink。利用Powergui模块进行FFT分析,加上一个Form warkspace和一个示波器就可以了,具体就不介绍。

我们只需要知道FFT输入的是按时间来划分的采样点数据,经过FFT运算之后得出的是按频率来划分的同样数据长度的数据。

之后我们进入最关键的阶段,即仿真阶段。我们只需要导入Matlab生成的待滤波信号,然后在仿真软件中观察滤波后的信号即可。

我们先编写好仿真文件。

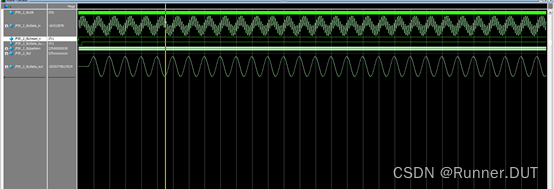

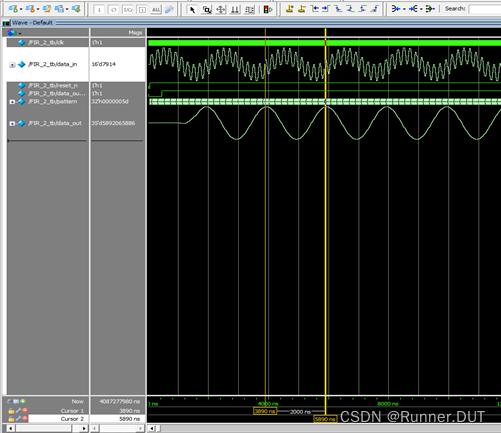

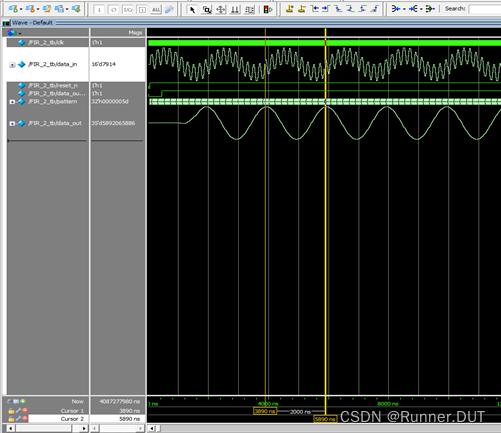

然后联合Modelsim仿真。右键data_in和data_out设置radix为decimal十进制,format为analog。

得到仿真结果,可以看到其周期为2000ns,即0.5MHz,表示5MHz干扰滤除干净了。

本文大部分内容都属于原创,如需转载,请附上本文网站,

如果需要相关的仿真图、程序代码等资料可以直接私信我,我会及时回复。

相关文章:

FIR滤波器简述及FPGA仿真验证

数字滤波器的设计,本项目做的数字滤波器准确来说是FIR滤波器。 FIR滤波器(有限冲激响应滤波器),与另一种基本类型的数字滤波器——IIR滤波器(无限冲击响应滤波器)相对应,其实就是将所输入的信号…...

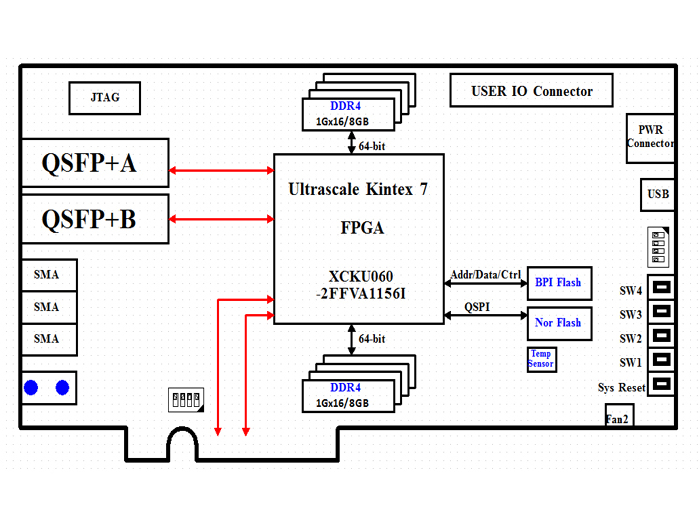

高速信号处理板资料保存:383-基于kintex UltraScale XCKU060的双路QSFP+光纤PCIe 卡设计原理图

基于kintex UltraScale XCKU060的双路QSFP光纤PCIe 卡 一、板卡概述 本板卡系我司自主研发,基于Xilinx UltraScale Kintex系列FPGA XCKU060-FFVA1156-2-I架构,支持PCIE Gen3 x8模式的高速信号处理板卡,搭配两路40G QSFP接口…...

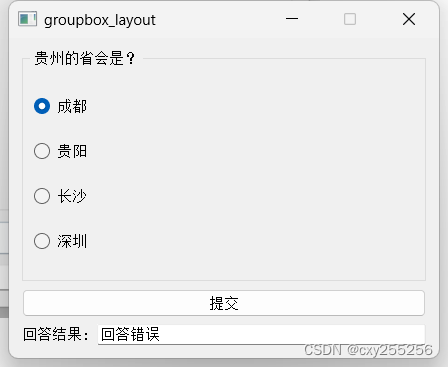

QT:使用分组框、单选按钮、普通按钮、标签、行编辑器、垂直分布、水平分布做一个小项目

widget.h #ifndef WIDGET_H #define WIDGET_H#include <QWidget> #include <QRadioButton> //单选按钮 #include <QGroupBox> //分组框 #include <QHBoxLayout> //水平布局 #include <QVBoxLayout> //垂直布局 #include <QPushButton>…...

封装微信小程序隐私信息授权

隐私 代码 html (modal 组件再后面封装有提供) <modal isShow"{{show}}"><view class"privacy-auth-dialog"><view class"title">温馨提示</view><view class"content"><vi…...

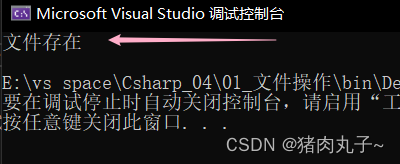

【C#】FileInfo类 对文件进行操作

提示:使用FileInfo类时,要引用System.IO命名空间。 using System.IO; FileInfo类 生成文件删除文件移动文件复制文件获取文件名判断文件是否存在属性列表其它常用方法 生成文件 Create():在指定路径上创建文件。 FileInfo myFile new FileIn…...

python中的字符串也是可迭代对象吗?

python中的字符串也是可迭代对象吗? ━━━━━━━━━━━━━━━━━━━━━━ 是的,Python中的字符串是可迭代对象。这意味着你可以像处理列表或元组那样处理字符串。例如,你可以使用for循环遍历字符串中的每个字符,或…...

C++ 图像线特征提取【HoughLinesP算法】

目录 一、函数介绍二、实现步骤三、代码示例一、函数介绍 HoughLinesP:是一种基于Hough变换的直线检测算法。它可以识别图像中的直线,并返回它们的端点坐标。其函数接口如下: cv::HoughLinesP( InputArray src, // 输入图像,必须 8-bit 的灰度图像 OutputArray…...

Stable Diffusion WebUI内存不够爆CUDA Out of memory怎么办?

在我们运行SD的时候,我们经常会爆CUDA Out of memory。 我们应该怎么办呢? 这是因为我们的显存或者内存不够了。 如果你是用cpu来跑图的则表示内存不够,这个时候就需要换个大点的内存了。 如果你是用gpu来跑图的就说明你显存不够用咯,这时候咋办呢? 下面我将一一述说…...

模板学堂|数据可视化仪表板大屏设计流程梳理

DataEase开源数据可视化分析平台于2022年6月正式发布模板市场(https://dataease.io/templates/)。模板市场旨在为DataEase用户提供专业、美观、拿来即用的仪表板模板,方便用户根据自身的业务需求和使用场景选择对应的仪表板模板&a…...

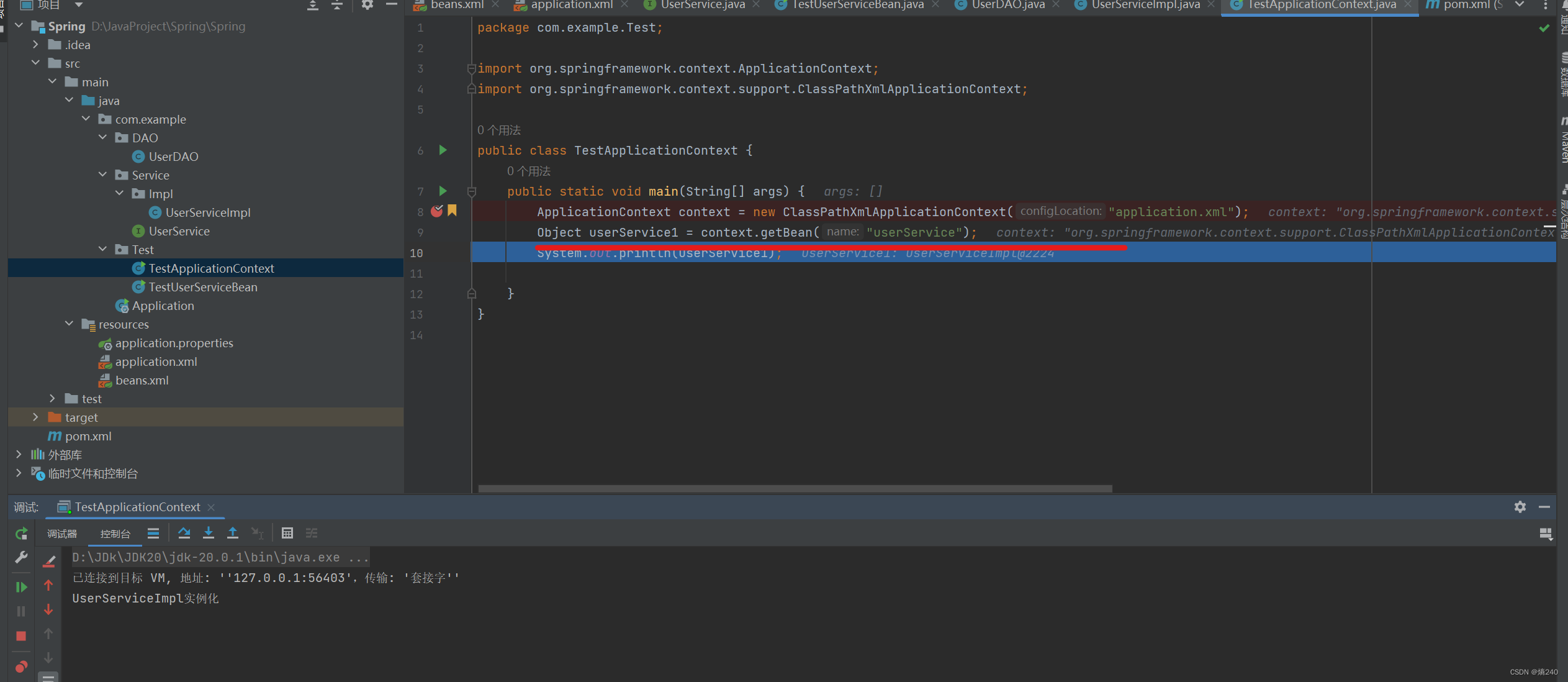

基于Xml方式Bean的配置-Bean的延时加载

SpringBean的配置详解 Bean的延时加载 当lazy-init设置为true时为延时加载,也就是当Spring容器创建的时候,不会立即创建Bean实例,等待用到时再创建Bean实例并储存到单例池中,后续使用该Bean时直接从单例池中获取即可,…...

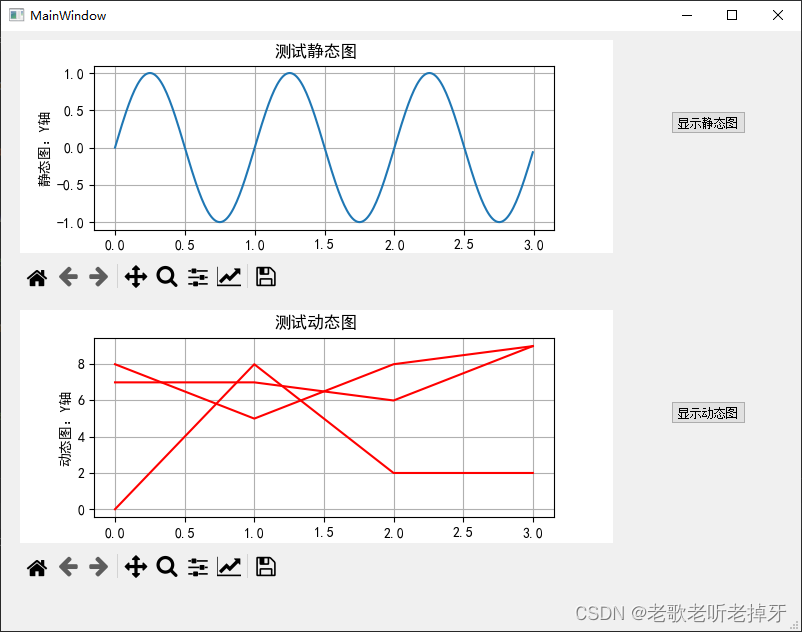

python之pyQt5实例:Matplotlib的应用

1、显示逻辑 1.1MatplotlibWidget.py import sys import random import matplotlibmatplotlib.use("Qt5Agg") from PyQt5 import QtCore from PyQt5.QtWidgets import QApplication, QMainWindow, QVBoxLayout, QSizePolicy, QWidget from numpy import arange, si…...

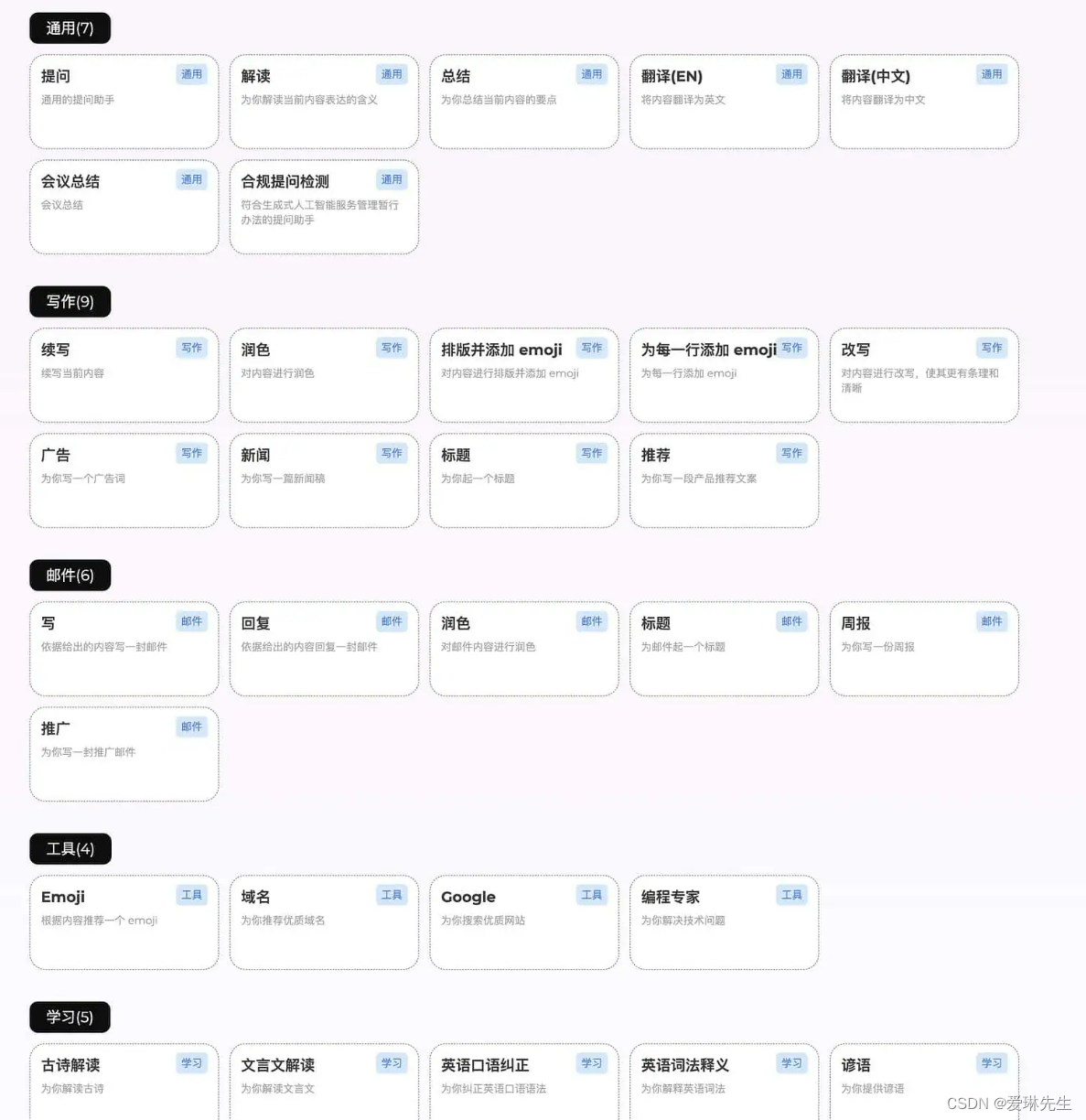

智囊AI-基于 ChatGPT 的 AI 工具产品 你的私人AI助手

智囊AI是一款基于 ChatGPT 的 AI 工具产品,主打免费、智能、方便,可以在此雇佣各种各样的免费智囊进行对话、自己创造和分享智囊、共享有趣有用的对话等。不过使用需要注册登录,可以使用自己的openai key或者使用网站提供的api key࿰…...

nginx配置vue前端代理

背景:做一个前后端分离的项目,我这里是vue3 view ts创建的前端项目,在前端配置跨域请求。 一、开发阶段 在vue.config.js中配置devserver的proxy进行代理请求配置,然后将所有请求改为/api开头的即可。但是这样配置只在开发阶段…...

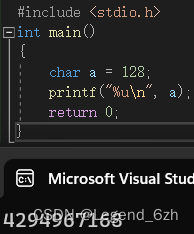

【C语言】【数据存储】用%u打印char类型?用char存128?

1.题目一: #include <stdio.h> int main() {char a -128;printf("%u\n",a);return 0; }%u 是打印无符号整型 解题逻辑: 1. 原反补互换,截断 -128 原码:10000000…10000000 补码:11111111…10000000…...

git-git命令汇总

1.git 存储永久凭据 git config --global credential.helper store 2.git 查询分支或标签的引用 git show-ref 【标签名|分支名】 3.git 搜索关键分支和tag git tag -l *branch* --sortcommitterdate 4.git 删除标签 git tag -d v1.32 删除标签v1.32,参数d…...

自定义实现简易版ArrayList

文章目录 1.了解什么是顺序表2.实现哪些功能3.初始化ArrayList4.实现功能接口遍历顺序表判断顺序表是否已满添加元素指定下标添加元素自定义下标不合法异常判断顺序表是否为空查找指定元素是否存在查找指定元素返回下标获取指定下标的元素顺序表为空异常修改指定下标元素的值删…...

)

React中的Hooks--useReducer()

首先,useReducer是React提供的一个钩子函数,用于管理组件内部的状态。它可以接收一个reducer函数和初始状态,并返回一个包含状态和更新状态的函数的数组。 与之相反,Redux是一个独立的状态管理库,它可以在整个应用程序…...

DM@数理逻辑@命题公式及其赋值@真值表@公式分类

文章目录 abstract命题公式及其赋值命题常项命题变项 命题公式合式公式(命题公式)限定基本联结词的合适公式的定义合式公式中的0和1子公式 **公式的层次定义**分层加括号 命题公式的赋值和解释成真赋值成假赋值公式的书写规范括号的省略 真值表赋值方法数量构造真值表 公式分类…...

HTTP协议(超级详细)

HTTP协议介绍 基本介绍: HTTP:超文本传输协议,是从万维网服务器传输超文本到本地浏览器的传送协议HTTP是一种应用层协议,是基于TCP/IP通信协议来传送数据的,其中 HTTP1.0、HTTP1.1、HTTP2.0 均为 TCP 实现࿰…...

leetcode做题笔记135. 分发糖果

n 个孩子站成一排。给你一个整数数组 ratings 表示每个孩子的评分。 你需要按照以下要求,给这些孩子分发糖果: 每个孩子至少分配到 1 个糖果。相邻两个孩子评分更高的孩子会获得更多的糖果。 请你给每个孩子分发糖果,计算并返回需要准备的…...

)

STM32CubeMX配置I2C驱动ADS1115,从零开始实现高精度电压采集(附完整工程源码)

STM32CubeMX配置I2C驱动ADS1115:从零实现工业级电压采集系统 在嵌入式开发中,高精度模拟信号采集一直是工程师面临的挑战。当我们需要测量微弱电压信号或实现多通道同步采集时,STM32内置ADC往往难以满足精度要求。本文将手把手教你使用STM32C…...

OpenMC多群截面计算深度解析:传输修正合并的3种解决方案与性能优化实战

OpenMC多群截面计算深度解析:传输修正合并的3种解决方案与性能优化实战 【免费下载链接】openmc OpenMC Monte Carlo Code 项目地址: https://gitcode.com/gh_mirrors/op/openmc 你是否在使用OpenMC进行多群蒙特卡洛计算时,遇到模拟结果与参考值偏…...

NoSleep:告别Windows意外休眠的终极解决方案,让你的电脑始终保持清醒状态

NoSleep:告别Windows意外休眠的终极解决方案,让你的电脑始终保持清醒状态 【免费下载链接】NoSleep Lightweight Windows utility to prevent screen locking 项目地址: https://gitcode.com/gh_mirrors/nos/NoSleep 你是否经历过视频会议演示到一…...

普冉PY32F0系列开发:如何用VSCode+Cortex-Debug插件实现媲美Keil的图形化调试体验?

普冉PY32F0开发实战:VSCodeCortex-Debug打造专业级嵌入式调试环境 在嵌入式开发领域,高效的调试工具往往能决定项目的成败。对于使用普冉PY32F0系列Cortex-M0 MCU的开发者而言,传统商业IDE虽然功能完善,但存在许可成本高、跨平台支…...

Marko恢复机制:hydration过程中的状态恢复终极指南

Marko恢复机制:hydration过程中的状态恢复终极指南 【免费下载链接】marko A declarative, HTML-based language that makes building web apps fun 项目地址: https://gitcode.com/gh_mirrors/ma/marko Marko是一个基于HTML的声明式语言,专注于构…...

避坑指南:香橙派串口开发中orangepiEnv.txt与armbianEnv.txt的配置差异详解

香橙派串口开发实战:系统配置差异与深度调试指南 当你在深夜调试香橙派串口时,突然发现修改的配置文件毫无反应——这种经历相信不少开发者都遇到过。问题的根源往往不在于代码本身,而是隐藏在系统环境中的配置差异。本文将带你深入剖析香橙派…...

开发者的文件对比神器:Beyond Compare 4在Linux下从安装、汉化到‘延长试用’的完整指南

Beyond Compare 4在Linux环境下的高效应用指南 对于开发者而言,文件与目录的高效对比是不可或缺的日常工作。无论是代码版本管理、配置文件同步还是数据校验,一个强大的对比工具都能显著提升工作效率。Beyond Compare作为业界公认的专业对比工具…...

LangGraph实战:从链式到图式AI工作流开发指南

1. 项目概述:为什么我们需要一个“Awesome-LangGraph”?如果你最近在折腾AI应用开发,尤其是那些需要让多个AI智能体协同工作、或者构建复杂业务流程的应用,那你大概率已经听过或者用过LangChain。LangChain确实是个好框架…...

自建Vaultwarden密码服务器:Docker部署与安全实践指南

1. 项目概述:自建密码管理服务器的核心价值在数字化生活成为常态的今天,我们每个人都被数十甚至上百个账号密码所包围。从工作邮箱到社交媒体,从银行账户到流媒体订阅,管理这些凭证早已超出了人脑的记忆极限。于是,密码…...

-加工生产的影响)

12钛丝驱动技术(NiTiDrivetech)-加工生产的影响

钛丝驱动技术(NiTiDrivetech)的可靠性设计【前言】形状记忆合金(Shape memory alloy, SMA),也叫形态记忆合金、肌肉丝、镍钛记忆合金,它是由Ni(镍)- Ti(钛)材…...