FPGA时序分析与约束(9)——主时钟约束

一、时序约束

时序引擎能够正确分析4种时序路径的前提是,用户已经进行了正确的时序约束。时序约束本质上就是告知时序引擎一些进行时序分析所必要的信息,这些信息只能由用户主动告知,时序引擎对有些信息可以自动推断,但是推断得到的信息不一定正确。关于时序路径的详细内容,请阅读:

FPGA时序分析与约束(5)——时序路径![]() https://blog.csdn.net/apple_53311083/article/details/132641522

https://blog.csdn.net/apple_53311083/article/details/132641522

- 第一种路径需要约束Input_delay;

- 第二种路径需要约束时钟;

- 第三种路径需要约束output_delay;

- 第四种路径需要约束Max_delay/Min_delay;

二、时钟约束

首先用户必须要正确的约束时钟,时序引擎才能根据时钟信息进行各种时序检查。用户约束时钟时,一般有两种类型的时钟需要约束。

2.1 主时钟(Primary Clock)

主时钟(Primary Clock)有两种类型:第一种是从FPGA的全局时钟输入引脚输入的时钟;第二种是从高速收发器输出给用户的恢复时钟。

2.2 生成时钟(Generated Clock)

生成时钟(Generated Clock)有两种类型:第一种是由FPGA的专用时钟管理模块(PLL/MMCM)产生的时钟(这种时钟可以由时序引擎自动推断出来);第二种是由用户通过LUT或寄存器产生的时钟(这种时钟必须由用户手动约束)。

三、主时钟约束

3.1 create_clock

在设计中,我们用来说明主时钟的SDC指令是 create_clock 。该指令的BNF(Backus-Naur Form,巴斯科范式)为:

create_clock -period period_value[source_objects][-name clock_name][-waveform edge_list][-add][-comment comment_string]3.1.1 定义时钟周期

-period 选项用于定义时钟周期。 时钟周期的单位由库时间单位推到得出,一般采用ns,时钟周期的值必须大于0。

设计者也可以使用 set_units 命令自行设定单位。

3.1.2 标识时钟源

create_clock 通常在时钟源的设计对象中进行声明。这些对象可以是端口、引脚或网络。如果在网络中定义时钟,则要确保网络中由驱动信号(引脚或者端口),否则时钟信号将没有信号源。一个时钟信号可能有多个时钟源。这种情况通常用在设计必须支持时钟切换冗余或者不同操作模式中。时钟切换通常的特点是锁相环可用,在主时钟停止运行时,可以打开冗余时钟。

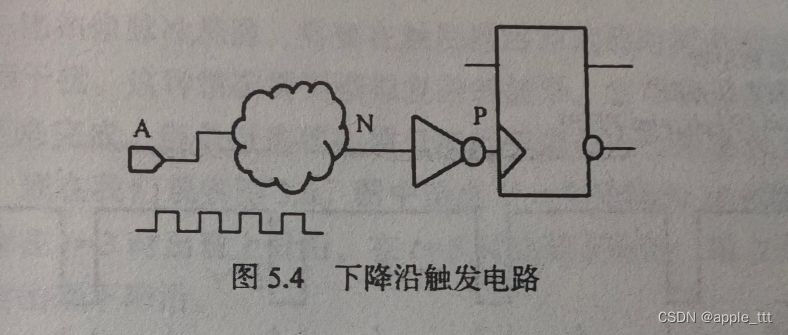

以下图为例:

#代表作为时钟源的端口

create_clock -period 10 [get_ports A]ORcreate_clock -period 10 [get_nets N]OR#代表作为时钟源的引脚

#假设触发器实例名称FF

create_clock -period 10 [get_pins FF/P] 3.1.3 命名时钟

每个时钟定义都会给出时钟信号命名。用 -name 选项可以指定一个字符串作为时钟名称。当 -name 选项没有明确指定字符串并且时钟已经被声明,工具将指定自己的名字给时钟信号命名。对于前边给出的第一个例子,时钟信号的名称设定为A。在SDC中,时钟信号的名称是至关重要的。时钟信号一旦被定义并且命名,所有其他依赖于此时钟的SDC指令只需要提到时钟信号的名称,而不需要提供其他任何特征。当提到时钟信号名字的时候,时钟信号的所有特征就都知道了。时钟名称提供了更加简单的方法来统称时钟信号的所有特征。

3.1.4 指定占空比

时钟信号的占空比用 -waveform 选项来指定。

-waveform {<rise_time><fall_time>}<rise_time>表示上升沿时刻,默认值为0;<fall_time>表示下降沿时刻,默认值是时钟周期的一半。单位也是ns。举个简单的例子:

create_clock -period 10 -name CLK -waveform{5 10} [get_ports A]表示的就是在t = 5时刻出现上升沿,在t = 10时刻出现下降沿。如下图所示:

接下来我们考虑下面的这种情况:在一个时钟周期内,时钟沿在 t = 4时下降,接着在t = 5时上升。由于该-waveform 选项只能按照先上升沿再下降沿的顺序来表示,并且数值都是单调递增的,因此我们必须考虑两个时钟周期内时钟信号的变化。在两个时钟周期内,该时钟信号在 t = 5时出现第一个上升沿,接着在 t = 14时出现一个下降沿。因此该时钟信号表示为:

create_clock -period 10 -name CLK -waveform {5 14} [get_ports C2] 3.1.5 同源多时钟

许多设计需要在时钟源指定多个时钟,从而满足多I/O速度协议的需求。可以采用-add的方式实现,这里暂时不做展开。

3.1.6 注释时钟

可以采用-comment的方式实现对于时钟的注释。增加SDC的可读性和可以移植性。

3.2 主时钟约束

主时钟约束时,准确地指定时钟源的物理节点至关重要。下面通过几个简单的例子看下如何使用create_clock进行主时钟约束。

3.2.1 引脚输入的主时钟约束

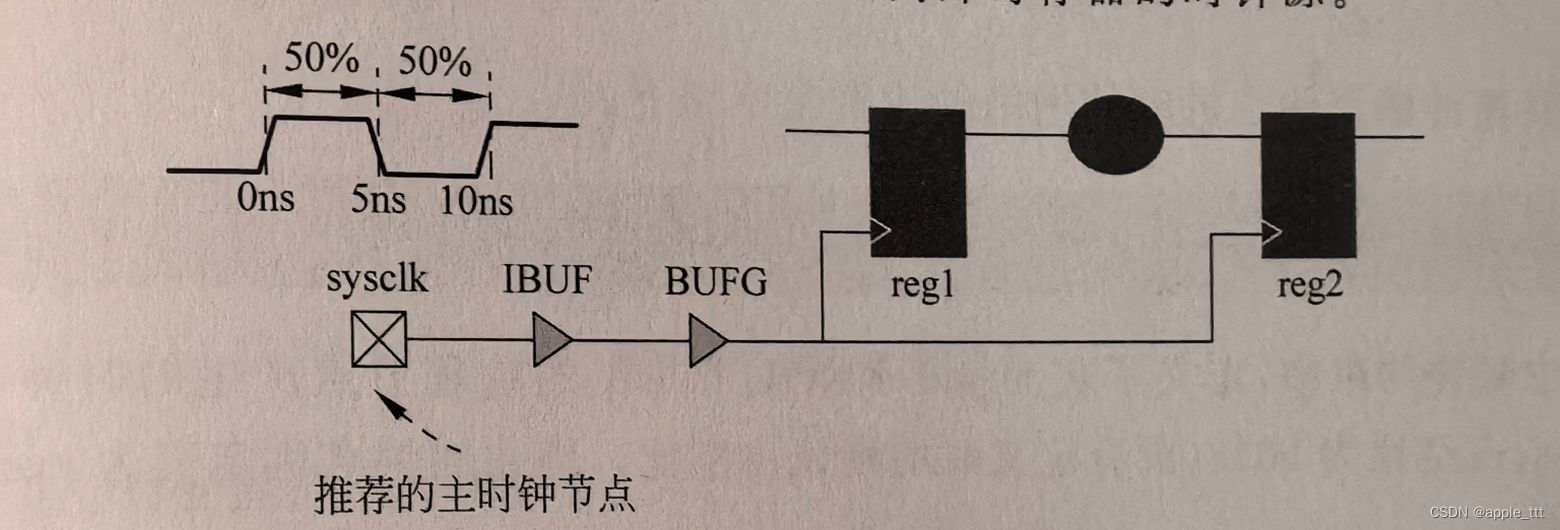

如下图所示,名为sysclk的引脚是FPGA内部寄存器的时钟源。

对于该输入时钟的约束如下:

create_clock -name SysClk -period 10 -waveform {0 5} {get_ports sysclk}在这个主时钟约束中,定义了名为sysclk的物理节点产生的时钟,它的周期是10ns,占空比为50%,命名为SysClk。

3.2.2 高速传输器输出的主时钟约束

高速传输器的输出时钟网络,经过时钟管理单元(CMT)之后,产生多个不同的生成时钟。在这种应用中,通常需要将高速传输器的输出时钟网络作为主时钟约束。

对该高速传输器输出的时钟网络的约束如下:

create_clock -name rxclk -period 6.667 [get_nets gt0/RXOUTCLK]这个主时钟约束中,定义了名为 gt0/RXOUTCLK 的物理节点产生的时钟,它的周期为6.667ns,占空比为50%(没有定义时的默认占空比),该主时钟名称定义为rxclk。

3.3.3 硬件原语输出的主时钟约束

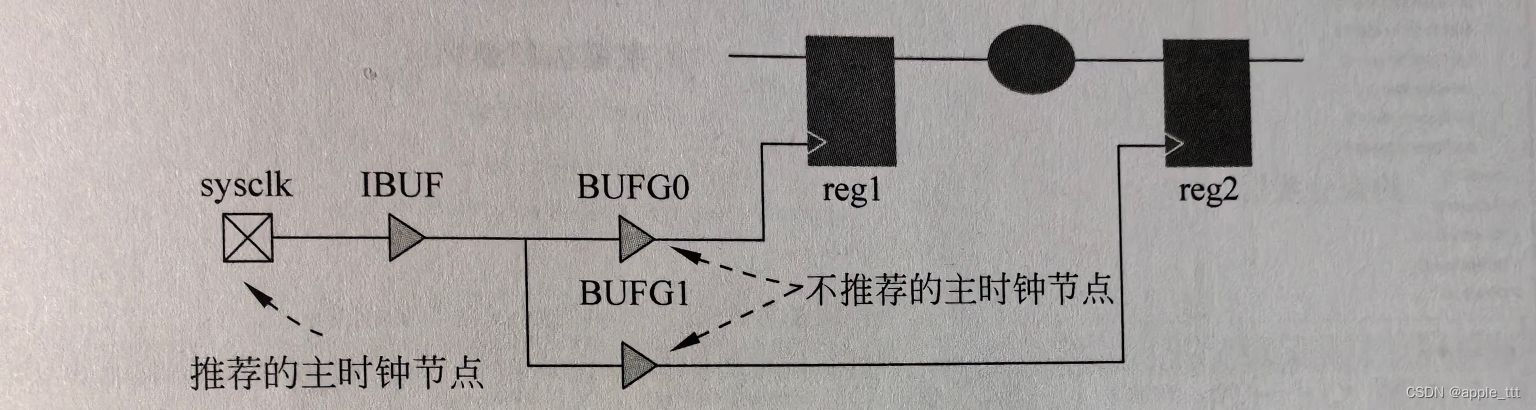

对于一些硬件原语的输出时钟引脚,若与其输入时钟之间没有很强的因果相关性,也可以将这个硬件原语的输出引脚作为时钟源进行主时钟约束,如下图所示,推荐使用instA/OUT作为主时钟节点。

而下图中的另一个例子,从输入引脚 sysclk 经过不同的 BUFG 所产生的时钟clk0(BFUG0)和clk1(BUFG1)分别作为时序路径中的一对源寄存器(reg1)和目的寄存器(reg2)的输入时钟。若此时还是指定BUFG原语的输出端作为主时钟约束的根节点,就可能由于clk0和clk1之间时钟偏斜差异而导致时序分析结果的误差。在这种情况下,clk0、clk1和输入时钟 sysclk 存在很强的因果相关性,只需要直接对源时钟 sysclk 进行主时钟约束,就能覆盖时钟 clk0 和 clk1 所驱动的所有时序路径。

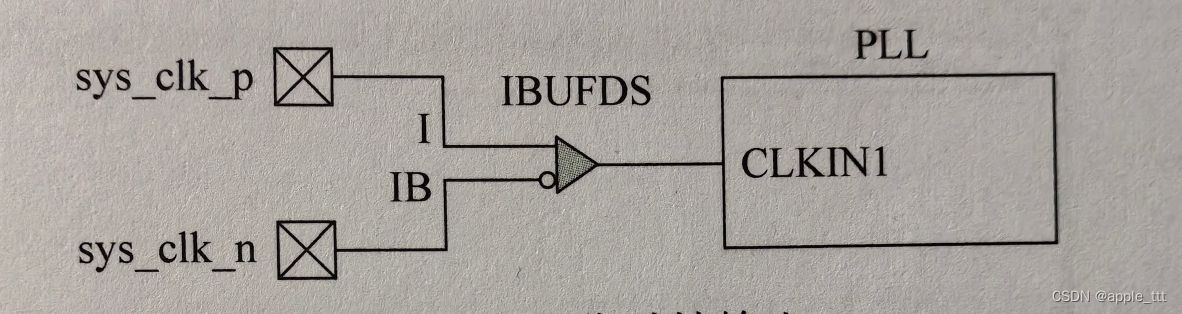

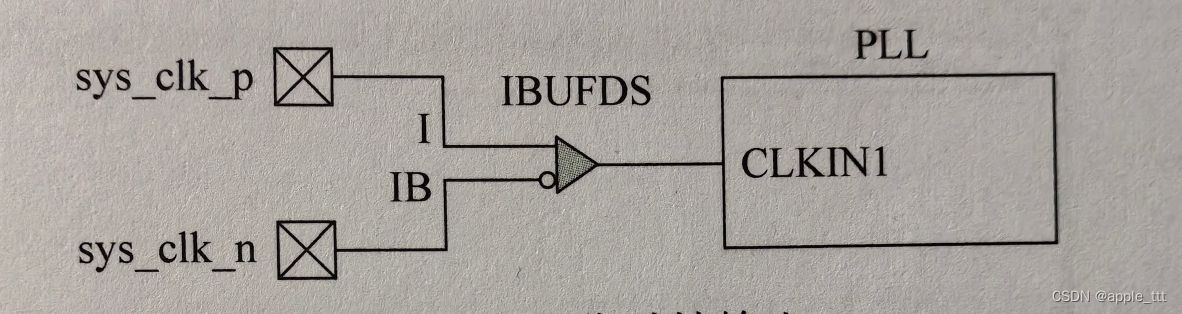

3.3.4 差分信号的主时钟约束

一个差分缓冲器(IBUFDS)产生的单端时钟信号作为 PLL 的输入时钟。在这种情况下,只需要对差分缓冲器的输入正端(sys_clk,p)进行主时钟约束即可。因为在指定了差分时钟的正端引脚之后,其负端引脚就是固定的,时序分析工具能够自动识别。若同时对差分缓冲器的输入正端和负端进行主时钟约束,反而会导致产生不真实的 CDC(Clock Domin Crossing)路径。

这个差分时钟的约束脚本如下:

create_clock -name sysclk -period 3.33 [get_ports sys_clk_p]相关文章:

FPGA时序分析与约束(9)——主时钟约束

一、时序约束 时序引擎能够正确分析4种时序路径的前提是,用户已经进行了正确的时序约束。时序约束本质上就是告知时序引擎一些进行时序分析所必要的信息,这些信息只能由用户主动告知,时序引擎对有些信息可以自动推断,但是推断得到…...

sqlite3 关系型数据库语言 SQL 语言

SQL(Structured Query Language)语言是一种结构化查询语言,是一个通用的,功能强大的关系型数据库操作语言. 包含 6 个部分: 1.数据查询语言(DQL:Data Query Language) 从数据库的二维表格中查询数据,保留字 SELECT 是 DQL 中用的最多的语句 2.数据操作语言(DML) 最主要的关…...

spring boot中的多环境配置

1.切换环境 spring:profiles:include: devactive: dev的作用是为了启动某个环境,两个作用基本一致, 环境定义如下: spring:profiles: dev或者是查找application-dev.yml这个文件的所有配置 2.加载文件 spring:config:import:- optional:f…...

python3 阿里云api进行巡检发送邮件

python3 脚本爬取阿里云进行巡检 不确定pip能不能安装上,使用时候可以百度一下,脚本是可以使用的,没有问题的 太长时间了,pip安装依赖忘记那些了,使用科大星火询问了下,给了下面的,看看能不能使…...

【Linux】安装使用Nginx负载均衡,并且部署前端项目

目录 一、Nginx概述 1. 什么 2. 背景 3. 作用 二、Nginx负载均衡 1. 讲述 2. 使用 1. 下载 2. 安装 3. 负载均衡 三、前端部署 1. 准备 2. 部署 一、Nginx概述 1. 什么 Nginx是一个高性能的开源Web服务器和反向代理服务器。它具有轻量级、高并发、低内存消耗的…...

k8s中 pod 或节点的资源利用率监控

pod 或节点的资源利用率监控 1 简介2 Kubectl Top介绍3 生效kubectl top命令3.1 下载配置components.yaml3.2 修改配置components.yaml参数3 kubectl top 应用3.1 查看node节点的资源占⽤率3.2 查看pod的资源占⽤率1 简介 通过Kubectl Top命令,可以查看你k8snode节点或者pod的…...

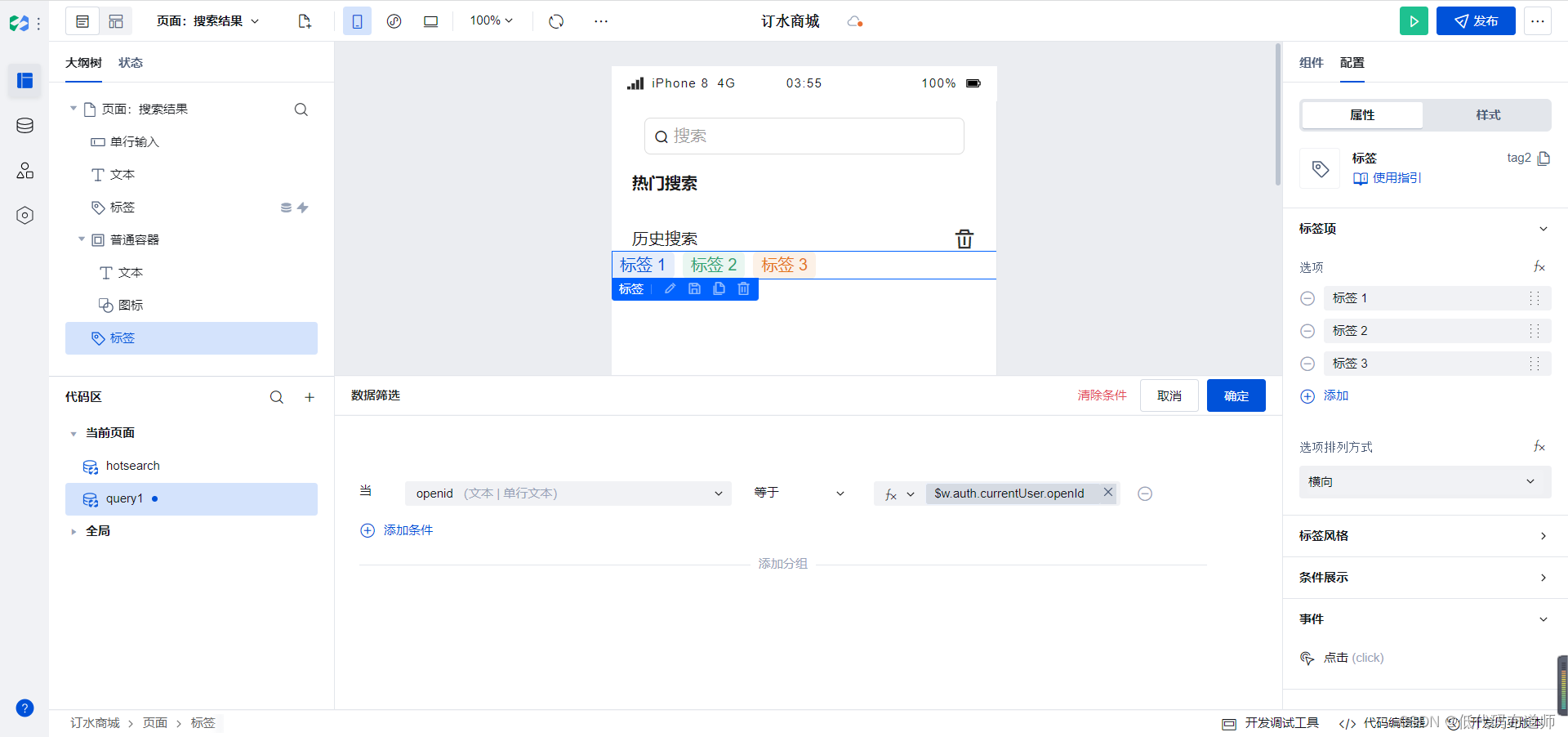

订水商城实战教程07-搜索

目录 1 创建数据源2 首页搜索功能3 创建搜索页面4 搭建搜索结果页面总结 上一篇我们讲解了店铺信息的展示功能,本篇讲解一下搜索功能。通常小程序在首页都配置了搜索的功能,输入关键词进行检索,可以在结果页上进行选购。同时还记录了用户的搜…...

stm32内 misc stm32f10x_hd stm32f10x_it stm32f10x_conf关系

STM32启动流程 初始位置 startup_stm32f10x_hd.s 查看源码 ;******************** (C) COPYRIGHT 2010 STMicroelectronics ******************** ;* File Name : startup_stm32f10x_hd.s ;* Author : MCD Application Team ;* Version :…...

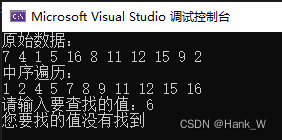

树结构及其算法-二叉查找树

目录 树结构及其算法-二叉查找树 C代码 树结构及其算法-二叉查找树 二叉树在建立的过程中是根据“左子树 < 树根 < 右子树”的原则建立的,因此只需从树根出发比较键值即可,如果比树根大就往右,否则往左而下,直到相等就找…...

PHP自定义文件缓存实现

文件缓存:可以将PHP脚本的执行结果缓存到文件中。当一个PHP脚本被请求时,先查看是否存在缓存文件,如果存在且未过期,则直接读取缓存文件内容返回给客户端,而无需执行脚本 1、文件缓存写法一,每个文件缓存一…...

猫耳 Android 播放框架开发实践

概述 猫耳FM是中国最大的 95 后声音内容分享平台,是B站重要平台之一,深度合作国内顶级声优工作室,打造了数百部精品广播剧,全站播放总量超过百亿次。 MEPlayer 是猫耳 Android 技术团队研发的一款适用于音视频、直播、特效播放等…...

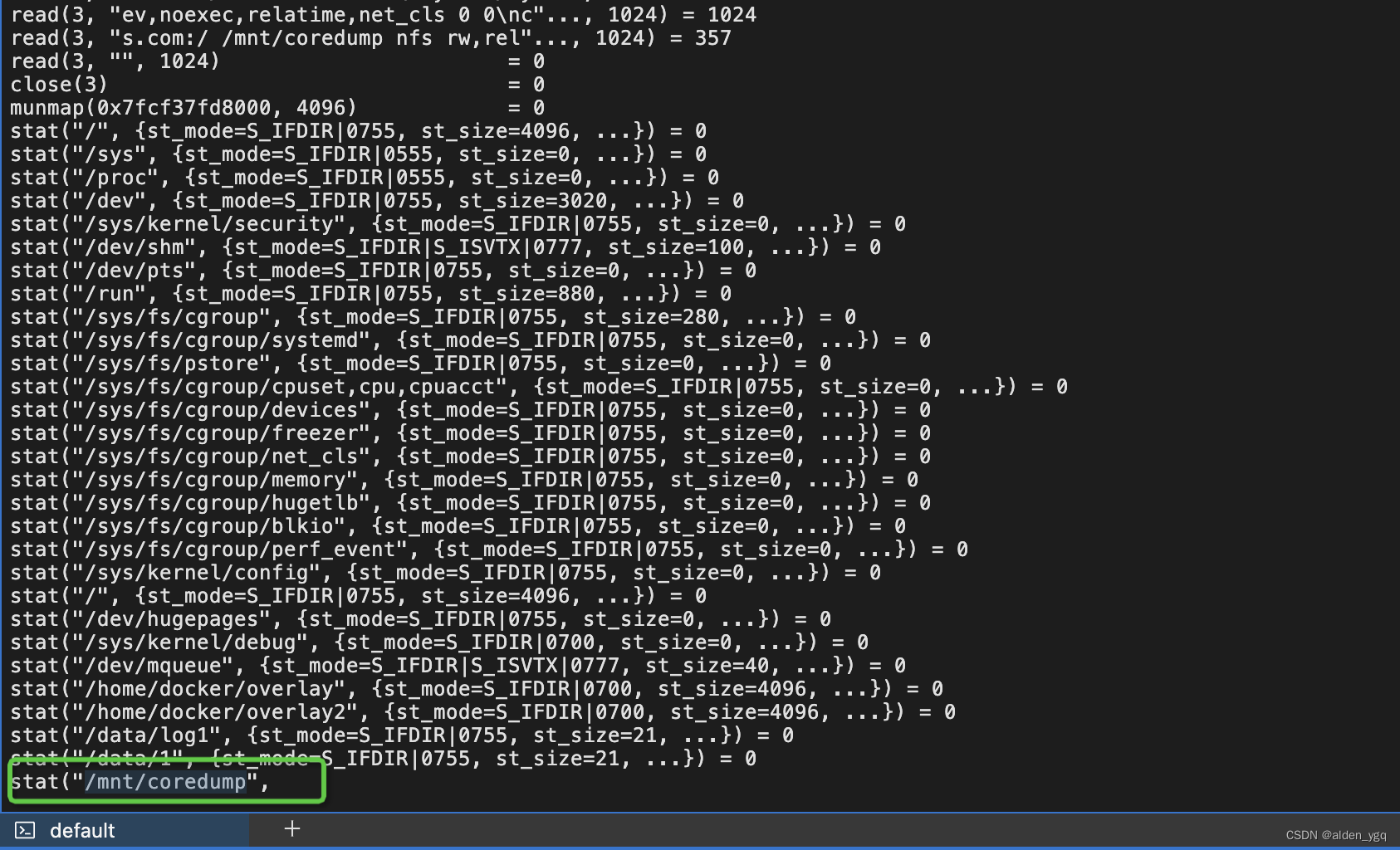

linux下df -h 命令一直卡住的解决方法

在Linux中,偶尔遇到用 df -h 查看磁盘情况时,一直卡住无法显示结果。 解决方法: 1、首先使用strace追踪到底执行到哪里卡住 $ strace df -h 2、如果没有strace命令则进行安装 $ yum install strace -y 3、显示出卡住的地方,如…...

系统架构设计热点知识

系统架构设计师考点包括以下内容: 1. 系统设计和架构思想. 了解系统设计和架构的基本概念和思想,特别是面向服务架构(SOA)、微服务架构、云架构、事件驱动架构、响应式架构等。 系统设计是指在软件项目中,确定系统结…...

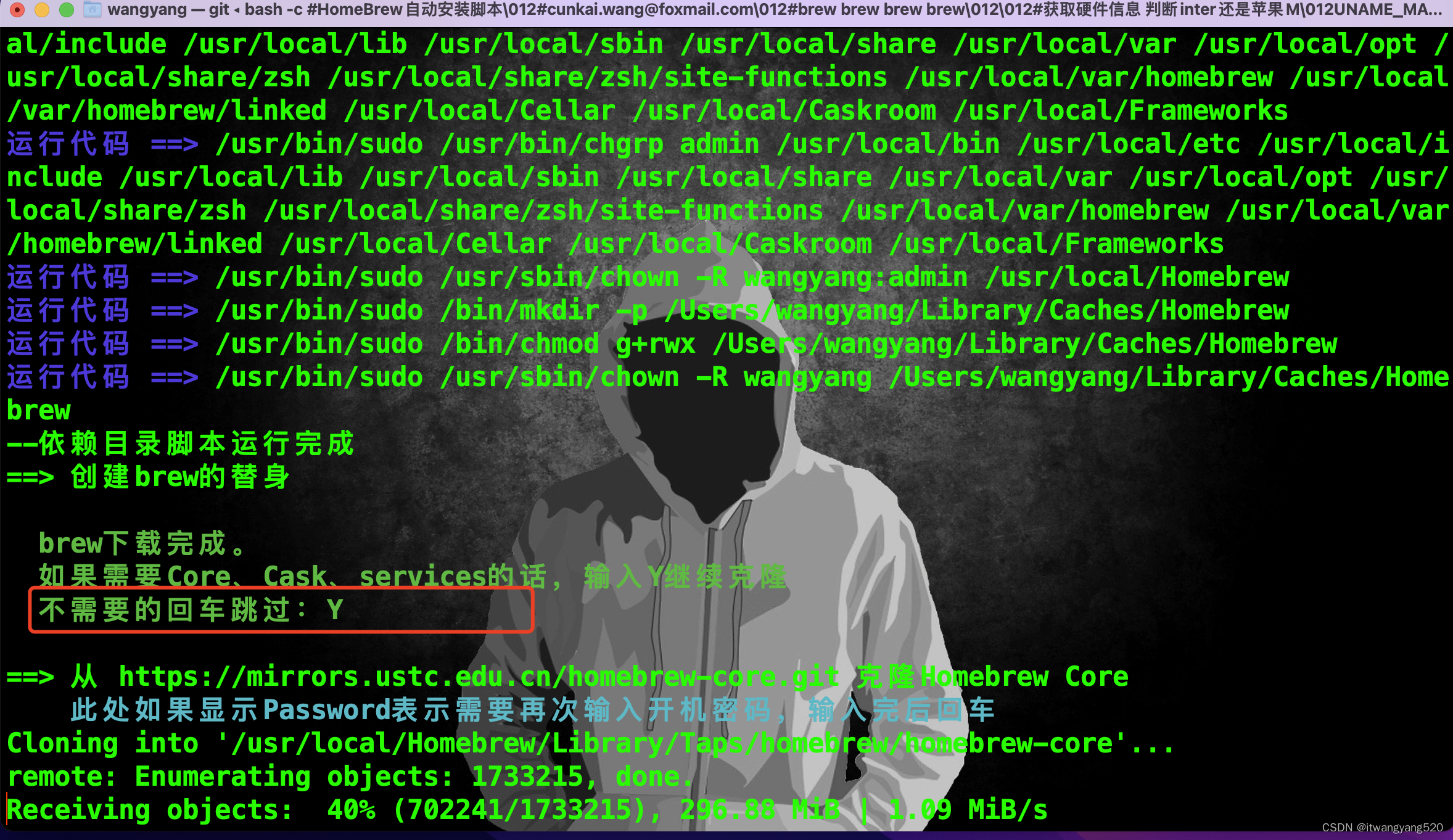

2023-在mac下安装Homebrew的国内镜像

mac安装Homebrew的国内镜像 尝试使用其他下载源:GitHub 可能会受到访问限制,尝试使用其他镜像或下载源。您可以使用清华大学、中科大或阿里云的 Homebrew 镜像,以提高下载速度和可靠性。例如,可以使用阿里云的镜像来安装 Homebre…...

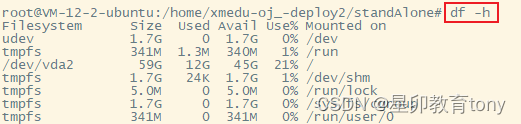

Ubuntu 20.04设置虚拟内存 (交换内存swap)解决内存不足

数据库服务器程序在运行起来之后,系统内存不足。 在系统监控中发现,当数据库服务程序启动后,占用了大量内存空间,导致系统的剩余的内存往往只有几十MB。 在ubuntu系统中,swap空间就是虚拟内存,所以考虑在磁…...

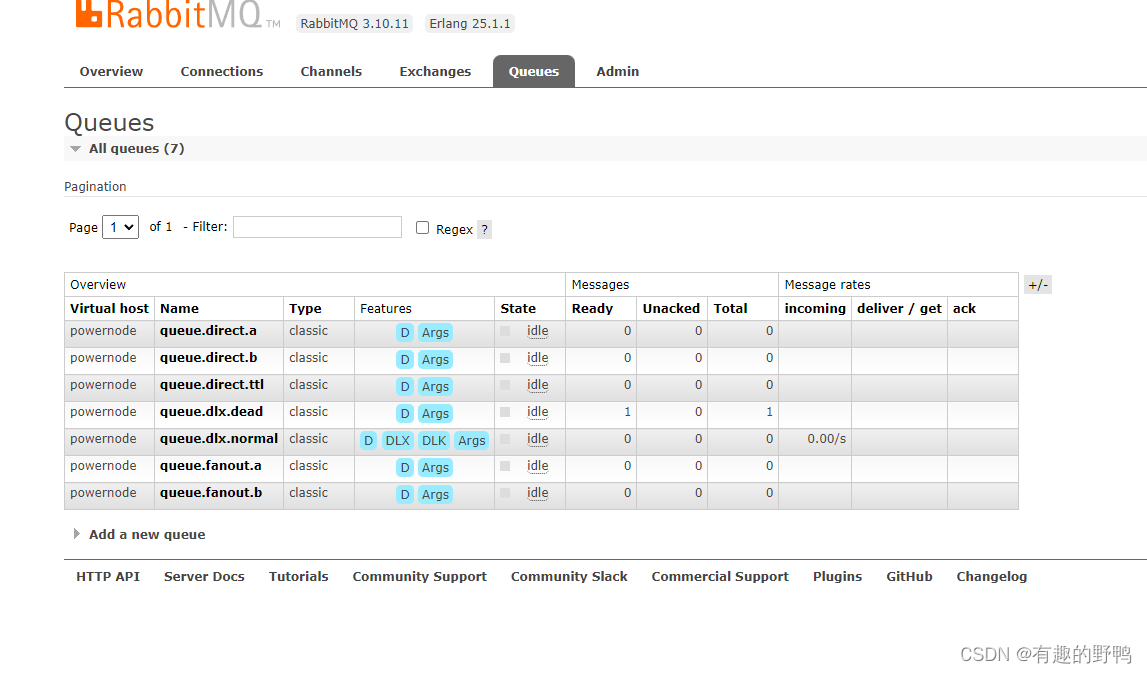

RabbitMQ-死信交换机和死信队列

1. 简介 1.1 DLX简介 DLX: Dead-Letter-Exchange 死信交换器,死信邮箱 当消息成为Dead message后,可以被重新发送到另一个交换机,这个交换机就是DLX。 如下图所示: 其实死信队列就是一个普通的交换机,有些队列的消息…...

[HNCTF 2022 WEEK2]easy_include 文件包含遇上nginx

这道纯粹记录 完全没想到 <?php //WEB手要懂得搜索if(isset($_GET[file])){$file $_GET[file];if(preg_match("/php|flag|data|\~|\!|\|\#|\\$|\%|\^|\&|\*|\(|\)|\-|\_|\|\/i", $file)){die("error");}include($file); }else{highlight_file(__…...

python中transform和apply的区别是什么

文章目录 1. 介绍transform:apply: 2. 应用示例示例数据使用transform进行向量化操作使用apply进行更复杂的操作性能比较 3. 示例输出使用 transform 进行向量化操作使用 apply 进行更复杂的操作 4. transform再举例示例数据使用transform计算平均销售额…...

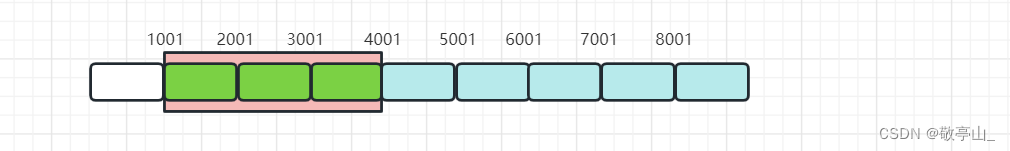

TCP 协议

文章目录 协议格式1面向连接:1.1三次握手(建立连接)1.2包序管理1.2四次挥手(断开连接) 2可靠传输:一。保证数据可靠有序的到达对端:确认应答机制超时重传机制 二。提高传输效率:1.提升自身发送数据量滑动窗口机制 rwnd滑动窗口丢包…...

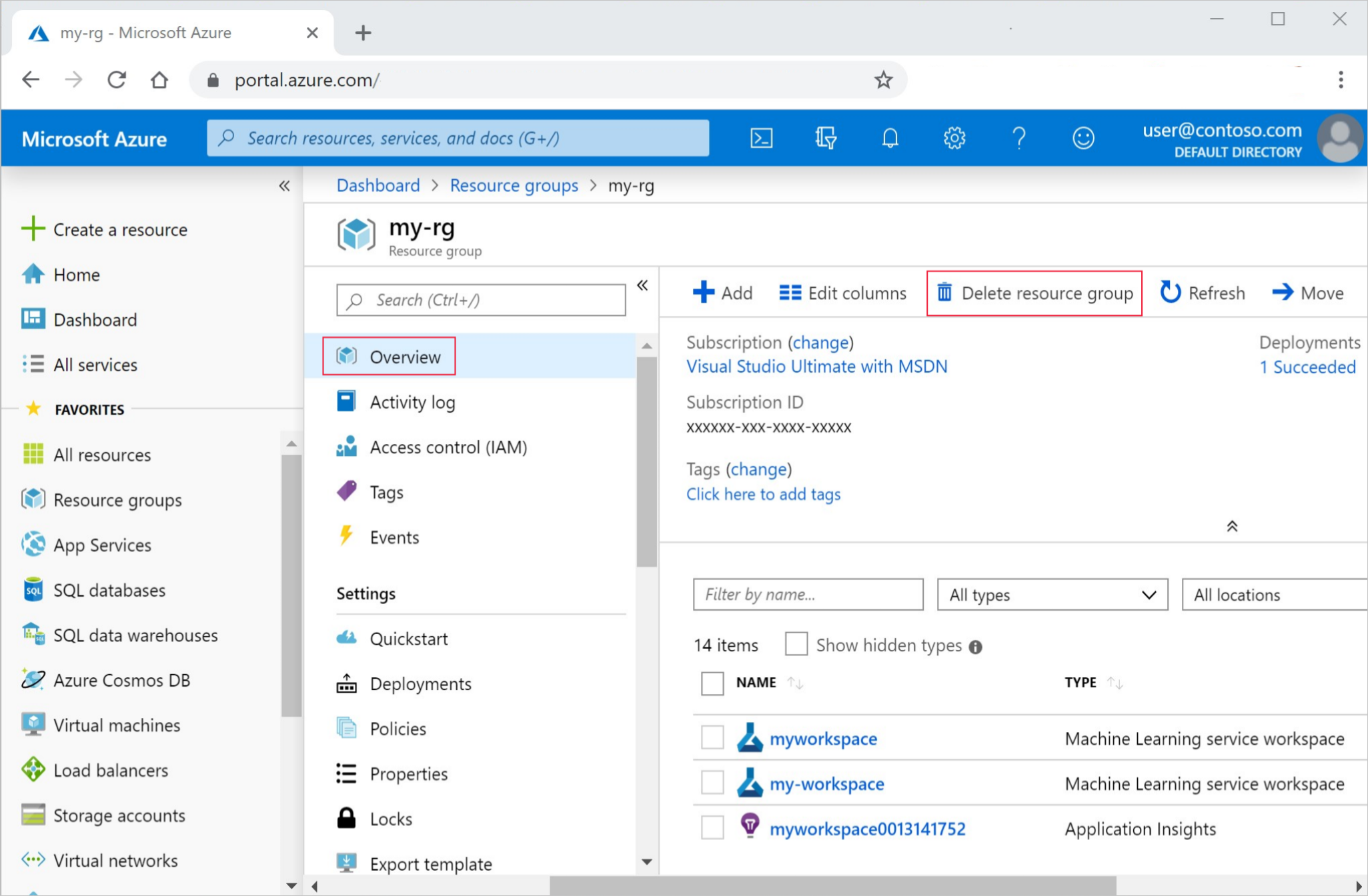

Azure机器学习 - 在 Azure 机器学习中上传、访问和浏览数据

目录 一、环境准备二、设置内核三、下载使用的数据四、创建工作区的句柄五、将数据上传到云存储空间六、访问笔记本中的数据七、创建新版本的数据资产八、清理资源 机器学习项目的开始阶段通常涉及到探索性数据分析 (EDA)、数据预处理(清理、特征工程)以…...

)

C# 13不安全代码审计清单:7项Roslyn Analyzer新规+4类CI/CD拦截阈值配置(附GHA自动化检测脚本)

第一章:C# 13不安全代码管控配置概览C# 13延续了对内存安全的高度重视,在默认启用/unsafe-(即禁用不安全上下文)的前提下,将不安全代码的启用明确纳入项目级显式管控范畴。开发者必须主动声明许可,并通过多…...

应对极端姿态与表情:cv_resnet101_face-detection_cvpr22papermogface 鲁棒性极限测试

应对极端姿态与表情:cv_resnet101_face-detection_cvpr22papermogface 鲁棒性极限测试 今天咱们不聊常规操作,来点刺激的。人脸检测模型平时表现都挺好,证件照、生活照基本不在话下。但真到了“实战”环境,情况就复杂多了&#x…...

墨语灵犀赋能在线教育:AI助教自动批改编程作业实践

墨语灵犀赋能在线教育:AI助教自动批改编程作业实践 每次上完《Python入门》课,看着邮箱里堆积如山的作业压缩包,你是不是也感到一阵头疼?打开一份作业,从代码缩进看到变量命名,再从逻辑结构分析到运行结果…...

Qwen3-Reranker-0.6B效果展示:中英文跨语言语义重排惊艳案例集

Qwen3-Reranker-0.6B效果展示:中英文跨语言语义重排惊艳案例集 1. 模型能力概览 Qwen3-Reranker-0.6B 是阿里云通义千问团队推出的新一代文本重排序模型,专门为文本检索和排序任务设计。这个模型虽然只有0.6B参数,但在语义相关性判断方面表…...

5分钟部署MinerU 2.5-1.2B:PDF转Markdown零门槛入门教程

5分钟部署MinerU 2.5-1.2B:PDF转Markdown零门槛入门教程 1. 为什么选择MinerU处理PDF文档 在日常工作和学习中,我们经常需要处理PDF文档。无论是技术文档、学术论文还是商业报告,PDF格式因其良好的跨平台兼容性而广受欢迎。然而,…...

氧化镓高体积热容的特性,集成高介电常数界面的结侧冷却架构

速览:技术背景与挑战背景: 虽然宽禁带(WBG)半导体(如SiC、GaN)已取得进展,但超宽禁带(UWBG)材料如氧化镓(Ga₂O₃)具有更高的理论极限。痛点&…...

OpenClaw跨平台配置指南:千问3.5-35B-A3B-FP8在mac与Win下的对接

OpenClaw跨平台配置指南:千问3.5-35B-A3B-FP8在mac与Win下的对接 1. 为什么需要跨平台配置指南 上周我在团队内部推广OpenClaw时遇到一个典型问题:同事A用macOS,同事B用Windows,两人都需要对接同一个千问3.5-35B-A3B-FP8模型。本…...

)

HTC Vive定位器固件更新后红灯闪烁?5步急救指南(附LED检测技巧)

HTC Vive定位器固件更新红灯急救手册:从诊断到修复的全流程实战 刚完成HTC Vive定位器的固件更新,却发现设备亮起刺眼的红灯——这种场景足以让任何VR玩家心跳加速。作为一套精密的空间定位系统,Vive定位器(基站)的异常…...

嵌入式轻量级时间解耦引擎:逻辑Tick与物理循环分离

1. 项目概述bluemicro_engine是一个面向嵌入式实时系统的轻量级时间解耦引擎,其核心设计目标是在硬件资源受限的微控制器(如 Cortex-M0/M3/M4)上,构建一个与用户输入响应、CPU主频波动及外设时序无关的确定性执行循环。它并非通用…...

Altium Designer原理图高效绘制:如何利用模板和快捷键提升3倍工作效率

Altium Designer原理图高效绘制:如何利用模板和快捷键提升3倍工作效率 在电子设计领域,效率往往决定着项目成败。当面对复杂电路设计时,熟练的设计师与新手之间的差距不仅体现在设计质量上,更体现在完成速度上。我曾参与过一个工业…...