FPGA时序分析与约束(10)——生成时钟

一、概述

最复杂的设计往往需要多个时钟来完成相应的功能。当设计中存在多个时钟的时候,它们需要相互协作或各司其职。异步时钟是不能共享确定相位关系的时钟信号,当多个时钟域交互时,设计中只有异步时钟很难满足建立和保持要求。我们将在后面的内容中介绍这部分问题,同步时钟则会共享固定相位关系。往往同步时钟产生自同一个时钟源。

如今的Soc在同一个芯片内包含多种异构设备。同一个芯片内可能包含高速的处理器和低速的存储器。这些工作在不同频率下的器件通常由不同的时钟触发。每个部分的运行是基于各自时钟的,这些会带来异步性的设计问题。这可能导致几个时钟都源于同一个主时钟,这些时钟称为生成时钟(衍生时钟、派生时钟)。

在FPGA设计中,生成时钟(Generated Clock)有两种类型:第一种是由FPGA的专用时钟管理模块(PLL/MMCM)产生的时钟(这种时钟可以由时序引擎自动推断出来);第二种是由用户通过LUT或寄存器产生的时钟(这种时钟必须由用户手动约束)。

二、如何进行生成时钟约束

2.1 约束方式

生成时钟的定义取决于主时钟的特性,生成时钟约束必须指定时钟源,这个时钟源可以是一个已经约束好的主时钟或者另一个生成时钟。生成时钟并不直接定义频率、占空比等参数,而是定义与其时钟源的相对关系,如分配系数、倍频系数、相移差值、占空比差值等。

生成时钟的约束定义能够帮助时序工具进行准确的时序分析。生成时钟约束时必须指定某个源时钟或某个已知的时钟传输扇出节点,由此时序工具才能准确地计算生成时钟相对于源时钟的插入时延。

2.2 生成时钟约束语法create_generated_clock

SDC中约束生成时钟create_generated_clock。该指令的BNF是:

create_generated_clock [source_objects]-source clock_source_pin[-master_clock master_clock_name][-name generated_clock_name][-edges edge_list][-divide_by factor][-multiply_by factor][-invert][-edge_shift shift_list][-duty_cycle percent][-combinational][-add][-comment comment_string]2.2.1 定义生成时钟的源

设定生成时钟的源引脚可利用-source选项,这个选项可以指明生成时钟是由哪个主时钟的源引脚派生的。

这里我们理解一下源对象和生成时钟源之间的区别,源对象指的是生成时钟(或者时钟)设定在哪个位置,而生成时钟源指的是具体是哪个获得生成时钟的参考信号。

一个源对象可以具有多个时钟。如果主时钟源引脚有多个时钟扇出,则生成时钟必须表明是由哪个主时钟派生来的。其功能可以通过-master_clock实现,这个选项采用了SDC时钟名称,该时钟已经被定义为驱动主时钟源引脚。只要定义了生成时钟,则开发工具将基于源的波形特性派生时钟特性。(如波形、周期等)

对于通过特定源生成的时钟,重要的一点是源必须能够通过某种方式保持与生成时钟的相关性。一种常见的错误是将生成时钟指定于一个并未扇出生成时钟的特定源。实际上这意味生成时钟的波形被设定在一个源引脚处的波形函数上,它与生成时钟无关。开发工具不能捕获这种情况,从而导致在静态时序分析期间将错误的时钟波形用于生成时钟。

2.2.2 时钟命名

像主时钟一样,生成时钟也需要通过名称来标识。可通过-name选项设定一个名称。若没有定义-name时,开发工具会自动指派一个名称。于生成时钟建立依赖关系后,任何SDC指令都将引用该名称。

2.2.3 设定生成时钟的特性

设定生成时钟的特性可以利用以下3个选项中的1个:

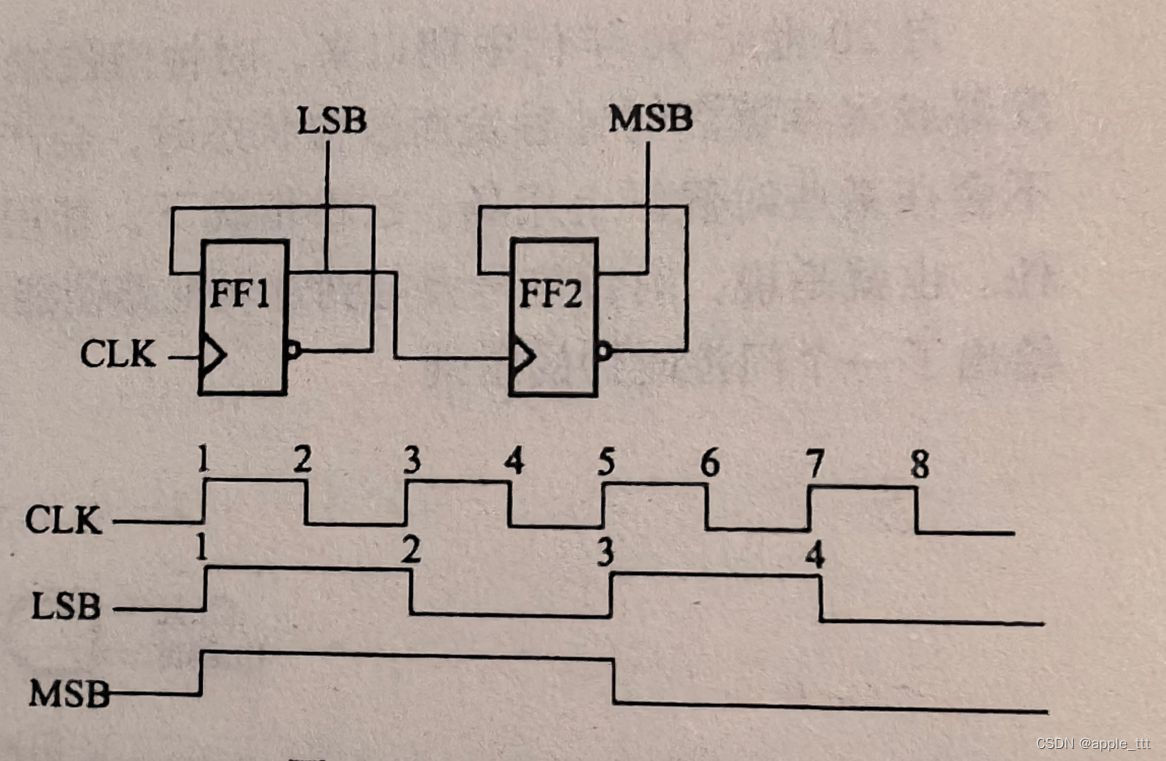

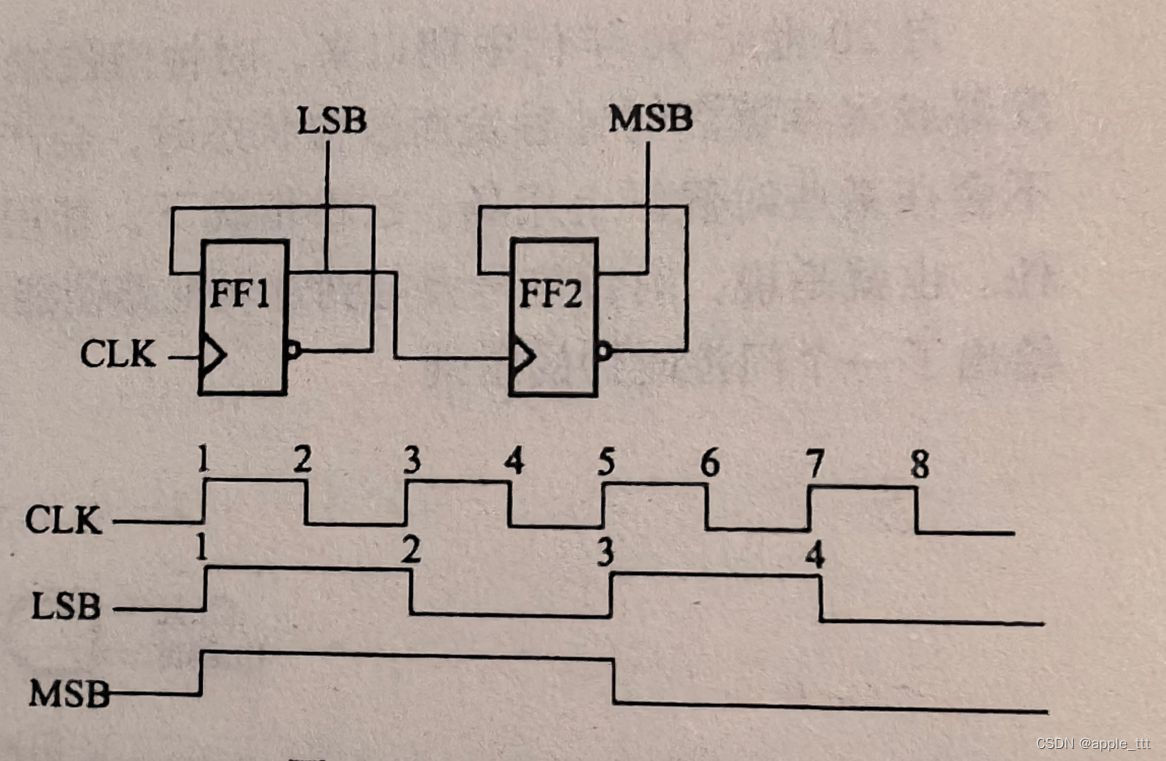

1、-edges ——作为一个对应源时钟边沿的整数数列,它表明了是从哪个生成时钟而产生的时钟边沿。时钟沿是指生成时钟交替的上升沿和下降沿。时钟沿的个数必须为奇数个整数,并且应当至少由3个整数表示一个完整生成时钟的周期。时钟沿计数由“1”开始,这个“1”表示源时钟的第一个上升沿。我们以下图为例:

create_clock -period 10 -name CLK [get_ports CLK]create_generated_clock -name LSB -source [get_ports CLK]

-edges {1 3 5}{get_pins FF1/Q}//用FF1/Q约束FF2/Q

create_generated_clock -name MSB -source [get_ports FF1/Q]

-edges {1 3 5}{get_pins FF2/Q}//用CLK约束FF2/Q

create_generated_clock -name MSB -source [get_ports CLK]

-edges {1 5 9}{get_pins FF2/Q}

2、-divide_by——这表示生成时钟通过某个因子而分频,周期则通过这个因子而加倍。

3、-multiply_by——这表示产生时钟通过某个因子而倍频,周期则要除以这个因子。应当注意的是,尽管时钟通过周期特性来定义,但要记住multiply_by和divide_by则是通过频率特性来设定的(即周期的倒数)。

总的来说,任何使用 -divide_by 或 -multiply_by 来表示的生成时钟也可以使用-edges来表示。反之则未必正确。

使用 -divide_by 或 -multiply_by 生成时钟有时需要进行取反,可以使用-invert选项来设定这个功能。

当定义的时钟需要倍频的时候占空比可以用-duty_cycle来设定,该选项指可以配合 -multiply_by来使用,并以表示倍频时钟为1时脉冲宽度的百分比。

2.2.4 时钟沿位移

生成时钟的时钟沿可能受到时间的影响而发生位移。-edge_shift 选项选取一组浮点数来表示在时间单元内每一个时钟沿的位移。该选项必须具有与时钟沿数量相同的参数来表示每个生成时钟沿的位移。我们举个例子进行说明:

create_generated_clock -name PLUSE -source [get_ports clk]

-edges {1 1 3} -edge_shift{0 2 0}{get_pins AN1/Z}

这段指令表示,在生成时钟上:

- 在第一个源时钟沿产生上升沿

- 在第一个源时钟沿达到后2ns后产生下降沿

- 在第三个源时钟沿产生下一个上升沿

三、总结

与主时钟相同,对生成时钟正确建模也很重要。否则可能导致时序收敛的迭代增加。由SDC约束定义的生成时钟,若其特性电路与实际功能不匹配,这很难通过调试发现。许多情况下,设计虽然与时序相符,但硬件却呈现出完全不一致的状态。

当定义生成时钟时,时钟的特性基于源时钟的特性而构成。通常可以直接通过create_clock在对象上定义相同的特性,而不利用生成时钟。从时序分析的角度来看,只要特性一致,时钟由create_generated_clock还是由create_clock设定并不重要。然而,若时钟是另一个时钟派生的,则无论何时都建议使用create_generated_clock,而非create_clock。这样做更易于维护和改进,因为修改源时钟的特性将直接影响生成时钟的特性。

同样,利用正确的约束可更好地模拟设计意图,当修改或改进约束时会减少产生错误的概率——包括移植技术和设计。

此外,当设计中多个时钟交互工作时,仅正确地定义时钟并不能满足要求,同样需要准确地定义各个时钟之间的关系。

相关文章:

FPGA时序分析与约束(10)——生成时钟

一、概述 最复杂的设计往往需要多个时钟来完成相应的功能。当设计中存在多个时钟的时候,它们需要相互协作或各司其职。异步时钟是不能共享确定相位关系的时钟信号,当多个时钟域交互时,设计中只有异步时钟很难满足建立和保持要求。我们将在后面…...

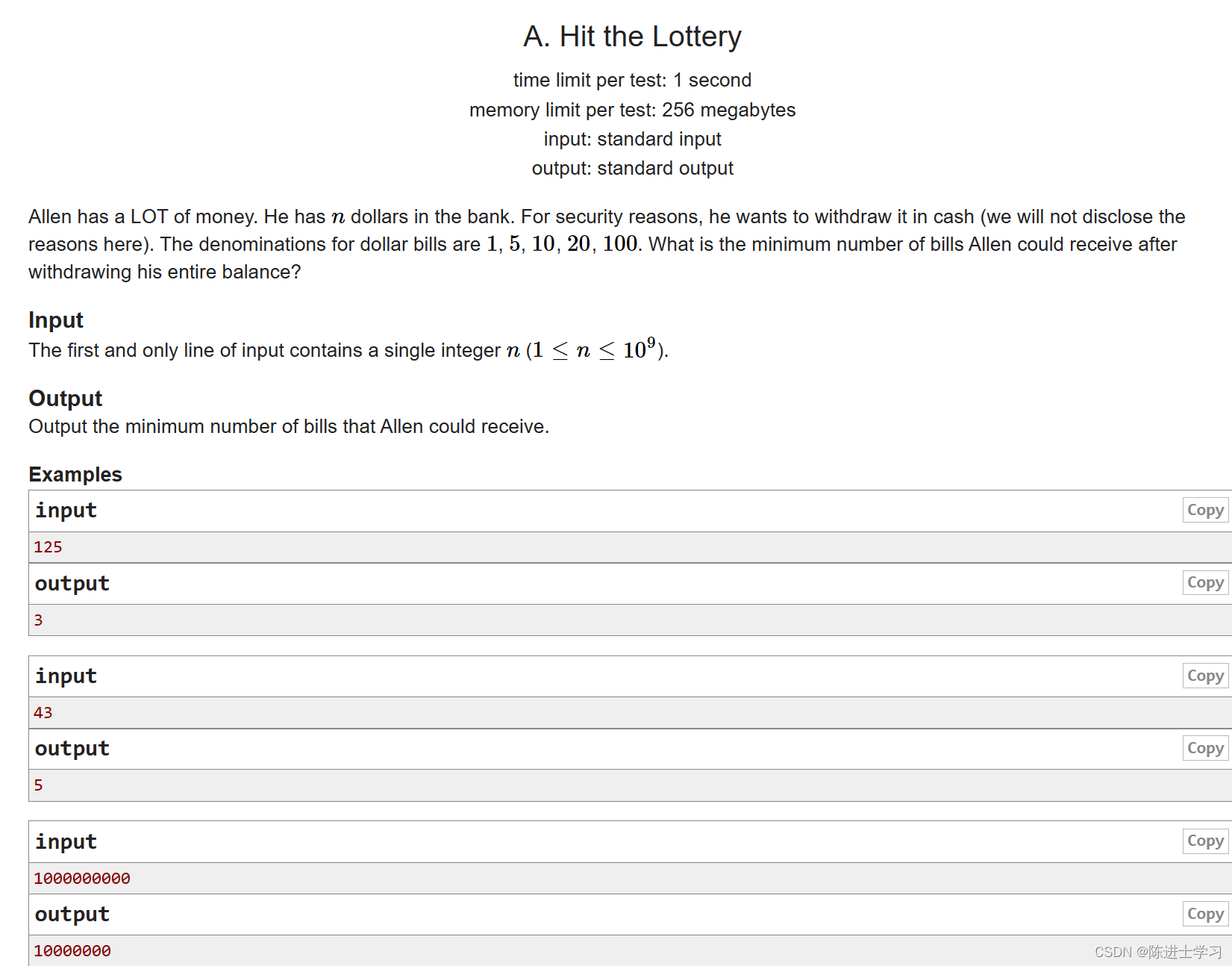

A. Hit the Lottery

#include<bits/stdc.h> using namespace std; const int N1e55; int n,a[N],res; int main(){scanf("%d",&n);int an/100;n%100;int bn/20;n%20;int cn/10;n%10;int dn/5;n%5;int en;cout<<abcde;return 0; }...

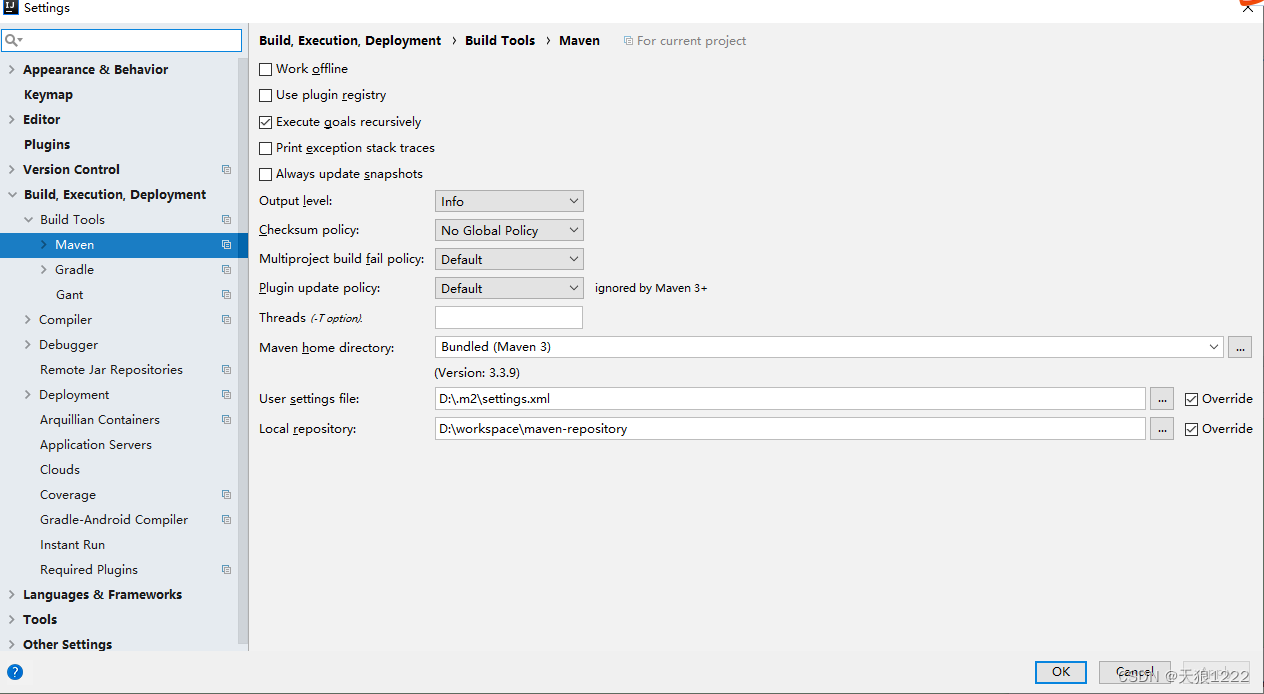

mvn: Downloading from pluginRepository

场景 maven 项目打包 mvn package 报git地址错误(有换新的git地址) 检查了下 settting.xml的配置没问题。是新的git地址。 处理: 用命令: mvn -X [DEBUG] Message styles: debug info warning error success failure stron…...

docker相关知识

docker-compose https://www.runoob.com/docker/docker-compose.html Compose 使用的三个步骤: 使用 Dockerfile 定义应用程序的环境。 使用 docker-compose.yml 定义构成应用程序的服务,这样它们可以在隔离环境中一起运行。 最后,执行 …...

)

Springboot 集成 RocketMQ(进阶-消息)

0. 入门篇 Springboot 集成 RocketMq(入门)-CSDN博客 1. 异步消息 1.1 生产者 GetMapping("/send/async/{messageBody}")public String sendAsyncMsg(PathVariable("messageBody") String messageBody) {// 构建消息对象Message m…...

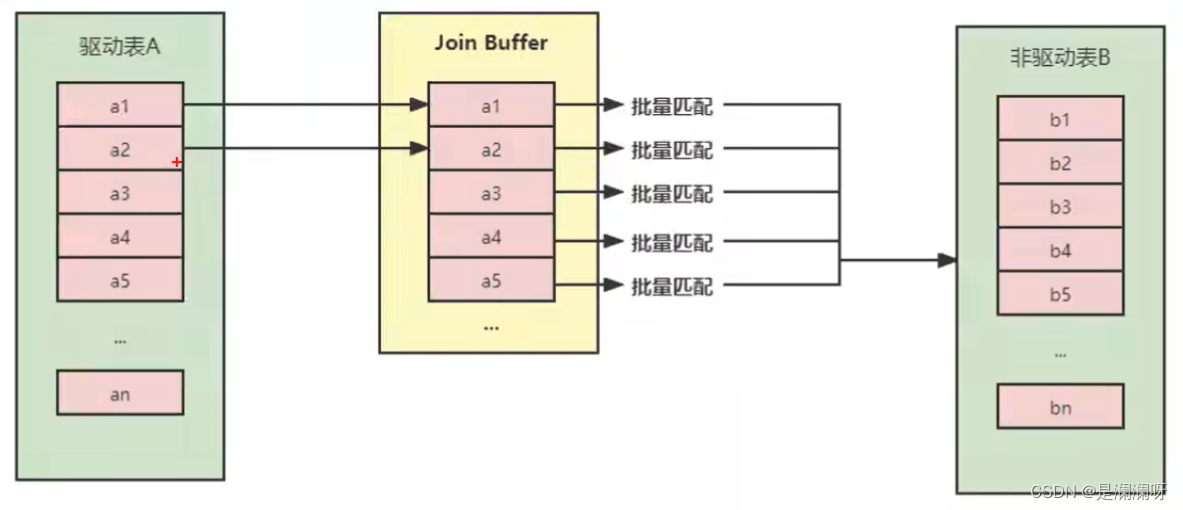

10 索引优化与查询优化

文章目录 索引失效案例关联查询优化对于左外连接对于内连接JOIN语句原理简单嵌套循环连接SNLJ索引嵌套循环连接INLJ块嵌套循环连接BNLJHash Join 子查询优化排序优化filesort算法:双路排序和单路排序 分组优化分页优化优先考虑覆盖索引索引下推ICP使用条件 其他查询…...

linux PVE安装

先下载安装包: ISO - Proxmox Virtual Environment 普通电脑主机的话,做个U盘启动盘,进行刷机即可。 如果还没制作U盘启动盘,建议用这个,方便多个镜像切换 Download . Ventoy 按照刷机提示页面一步步配置即可&#…...

ZZ038 物联网应用与服务赛题第J套

2023年全国职业院校技能大赛 中职组 物联网应用与服务 任 务 书 (J卷) 赛位号:______________ 竞赛须知 一、注意事项 1.检查硬件设备、电脑设备是否正常。检查竞赛所需的各项设备、软件和竞赛材料等; 2.竞赛任务中所使用…...

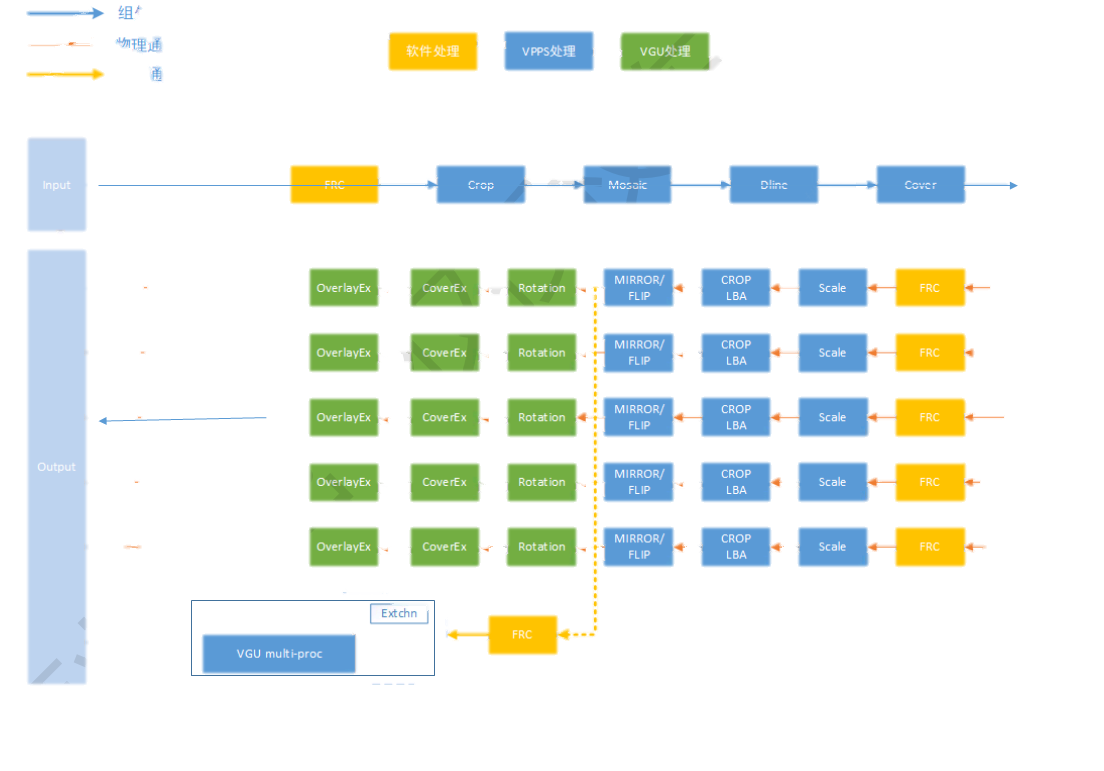

【寒武纪(3)】媒体处理系统的系统控制、视频输入和后处理子系统

系统控制 文章目录 系统控制1、配置视频缓存池Video Pool2、配置硬件IP为在线工作(不通过DDR数据交互)/ 离线工作(写入DDR)模式3、硬IP可以使用 非Video Block (VB)内存4、配置是否启动内存传递的压缩 视频…...

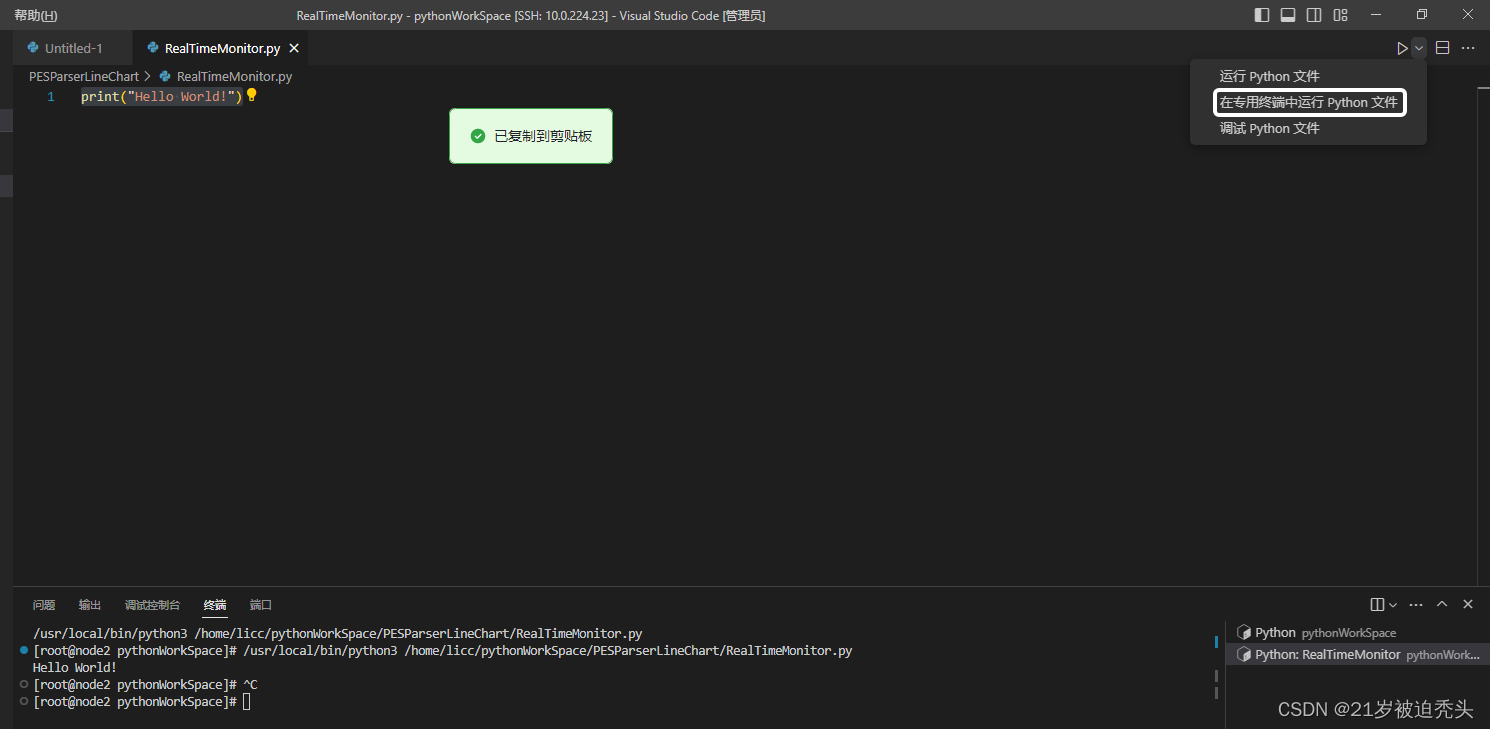

Linux下使用vscode编写Python项目

我此处是使用VScode远程连接的服务器,具体方法可看如下: 1、vscode中安装Python插件 按上面步骤安装好Python插件后,重启vscode; 2、选择Python解释器 创建Python项目结构: 按下F1,打开vscode命令栏&am…...

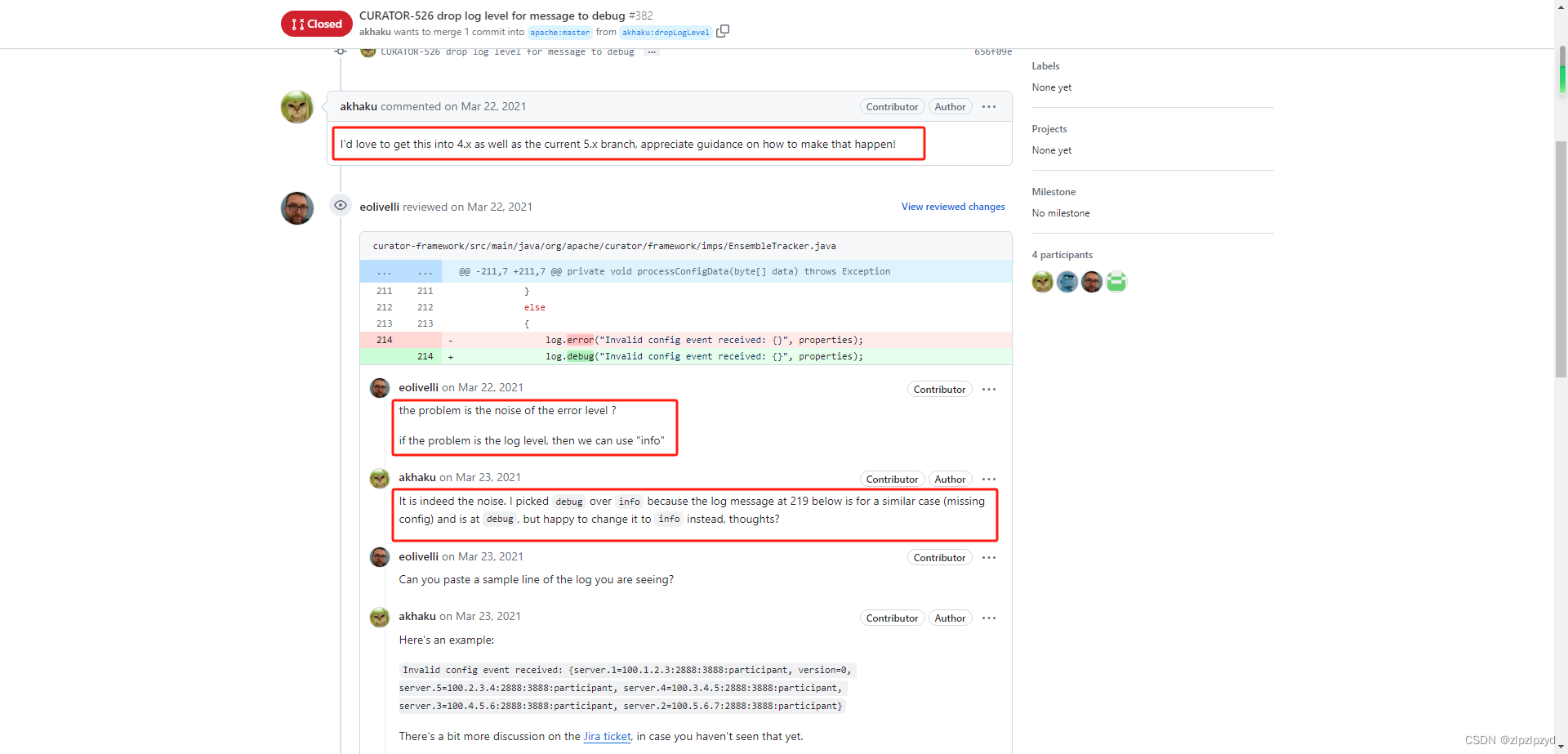

使用 curator 连接 zookeeper 集群 Invalid config event received

dubbo整合zookeeper 如图,错误日志 2023-11-04 21:16:18.699 ERROR 7459 [main-EventThread] org.apache.curator.framework.imps.EnsembleTracker Caller0 at org.apache.curator.framework.imps.EnsembleTracker.processConfigData(EnsembleTracker.java…...

大促期间也要做好低价治理

低价链接无处不在,对于品牌来说,日常治理低价是常规操作,那面对价格变化更快、促销信息更丰富的大促,对低价的治理要求会更高。否则容易被未授权在大促双十一、六一八期间分食流量。 力维网络有专业的团队为品牌提供低价治理服务&…...

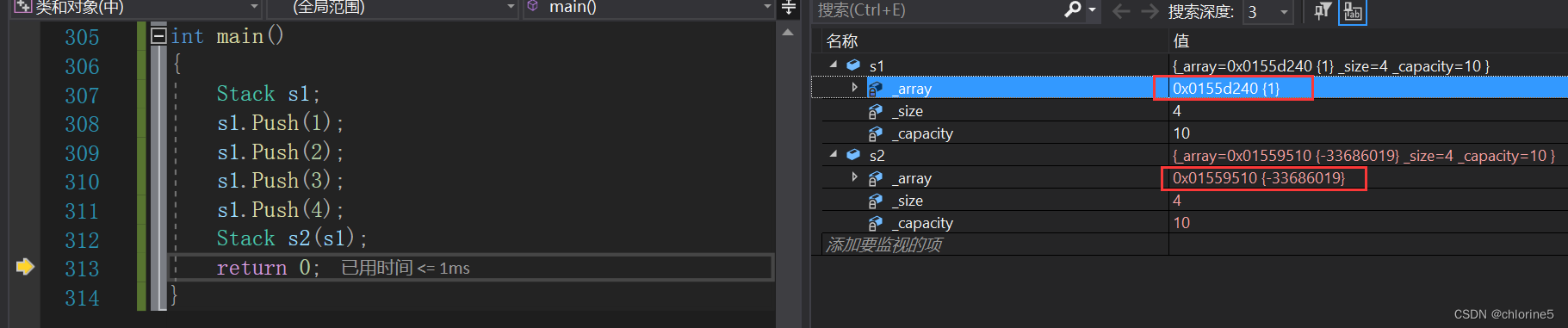

【c++】——类和对象(中)——默认成员函数(上)

【学习目标】 1. 类的6个默认成员函数 2. 构造函数 3. 析构函数 4. 拷贝构造函数 目录 一.类的6个默认成员函数 二. 构造函数 2.1 概念 2.2.特性 三.析构函数 3.1.概念 3.2 特性 四.拷贝构造函数 4.1.概念 4.2.特性 一.类的6个默认成员函数 如果一个类中什么成员…...

钉钉企业微应用开发C#-HTTP回调接口

官方的STREAM回调推送的方式,试了几次都认证不过,就放弃了还是用HTTP的模式吧。 /// <summary>/// 应用回调/// </summary>/// <param name"model"></param>/// <returns></returns>public static Dictio…...

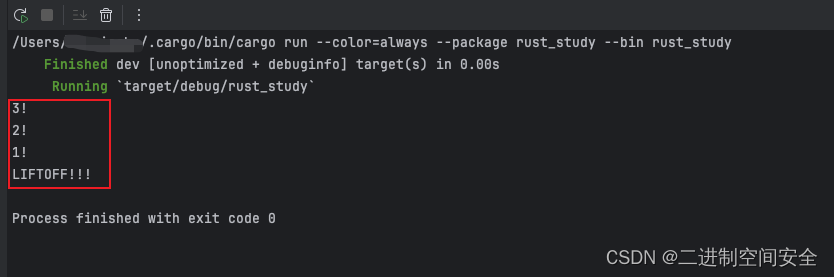

Rust编程基础之条件表达式和循环

1.if表达式 if 表达式允许根据条件执行不同的代码分支, 以下代码是一个典型的使用if表达式的例子: fn main() {let number 3; if number < 5 {println!("condition was true");} else {println!("condition was false");} } 所有的 if 表达式都以…...

)

MATLAB算法实战应用案例精讲-【人工智能】ROS机器人(补充篇)

目录 前言 ROS 机器人导航调参 1 速度和加速度 2 全局路径规划 3 局部路径规划...

基于8086汽车智能小车控制系统

**单片机设计介绍,基于8086汽车智能小车控制系统 文章目录 一 概要二、功能设计设计思路 三、 软件设计原理图 五、 程序六、 文章目录 一 概要 基于 8086 的汽车智能小车控制系统是一种将微处理器技术应用于汽车控制的系统。下面是其主要的设计介绍: 硬…...

全光谱大面积氙光灯太阳光模拟器老化测试

氙灯光源太阳光模拟器广泛应用于光解水产氢、光化学催化、二氧化碳制甲醇、光化学合成、光降解污染物、 水污染处理、生物光照,光学检测、太阳能电池研究、荧光材料测试(透射、反射、吸收) 太阳能电池特性测试,光热转化,光电材料特性测试,生物…...

linux添加一条到中间路由器的路由

有时候需要配置一些明细路由,不能直接通过网关进行路由转发 配置示例 ip route add 10.0.12.0/24 via 10.0.41.1 dev bond0 这个命令是用于在Linux操作系统上配置IP路由的命令。具体来说,这个命令的含义是: ip route add: 这部分表示要添加…...

)

不同MySQL服务的表以及库的数据迁移(/备份)

目标: 将本地主机上usernameroot,passwordroot,port3307的MySQL服务中migration_one数据库的table_11数据表导出到本地的D:\start_java\XinQiUtilsOrDemo\testMigrationMySQL\table_11.bak注意:目前D:\start_java\XinQiUtilsOrDemo\testMigrationMySQL该…...

终极LoRaWAN服务器搭建指南:如何快速构建你的私有物联网网络

终极LoRaWAN服务器搭建指南:如何快速构建你的私有物联网网络 【免费下载链接】lorawan-server Compact server for private LoRaWAN networks 项目地址: https://gitcode.com/gh_mirrors/lo/lorawan-server 你是否想拥有一个完全可控的LoRaWAN物联网平台&…...

)

Python农业物联网开发正在淘汰Django!FastAPI+Redis Stream+TimescaleDB构建毫秒级响应灌溉调度中枢(压测QPS达42,800)

第一章:Python农业物联网开发Python凭借其简洁语法、丰富生态和强大的硬件交互能力,已成为农业物联网(Agri-IoT)系统开发的主流语言。从土壤温湿度传感器数据采集到云端可视化决策支持,Python贯穿设备端、网关层与应用…...

)

Win11下用VMware16安装UOS服务器版全流程(附镜像+序列号)

Win11环境下VMware 16安装UOS服务器版实战指南 在数字化转型浪潮中,国产操作系统正逐步成为企业IT基础设施的新选择。统信UOS作为国内领先的服务器操作系统,凭借其稳定性与安全性,正在金融、政务等领域获得广泛应用。本文将手把手指导Windows…...

10个libxev实战技巧:从定时器到TCP服务器的完整实现

10个libxev实战技巧:从定时器到TCP服务器的完整实现 【免费下载链接】libxev libxev is a cross-platform, high-performance event loop that provides abstractions for non-blocking IO, timers, events, and more and works on Linux (io_uring or epoll), macO…...

前端埋点数据爆炸?WebTracing缓存策略与采样率配置避坑指南

前端埋点数据治理实战:WebTracing缓存策略与采样率配置深度解析 当你的应用日活突破百万量级时,埋点数据会像雪崩一样涌向服务器。某电商平台曾因未合理配置前端监控,导致单日产生2.3TB冗余埋点数据,不仅每年浪费数百万云存储成本…...

RPCS3完全攻略:从零开始打造你的PC端PS3游戏中心

RPCS3完全攻略:从零开始打造你的PC端PS3游戏中心 【免费下载链接】rpcs3 PS3 emulator/debugger 项目地址: https://gitcode.com/GitHub_Trending/rp/rpcs3 还在为无法重温经典PS3游戏而烦恼吗?想要在电脑上体验《最后生还者》、《神秘海域》等索…...

N_m3u8DL-RE流媒体下载器:多协议解析技术突破与下载效率提升

N_m3u8DL-RE流媒体下载器:多协议解析技术突破与下载效率提升 【免费下载链接】N_m3u8DL-RE 跨平台、现代且功能强大的流媒体下载器,支持MPD/M3U8/ISM格式。支持英语、简体中文和繁体中文。 项目地址: https://gitcode.com/GitHub_Trending/nm3/N_m3u8D…...

逆向视角看iOS加固:从机器码到伪代码,手把手教你分析加固效果与潜在风险

逆向视角看iOS加固:从机器码到伪代码的深度解析 当你在App Store下载一个应用时,可能不会想到这个看似简单的IPA文件背后隐藏着怎样的技术博弈。作为iOS开发者或安全研究员,我们常常需要从另一个角度思考——不是如何保护自己的应用…...

H3C F1070防火墙console密码恢复实战指南

1. 当console密码成为拦路虎时 刚接手公司网络设备那会儿,我就被H3C F1070防火墙来了个下马威。那天机房搬迁后需要调试设备,结果发现前任管理员留下的console密码早已失效。这种场景就像你拿着钥匙回老家,却发现锁芯被换了一样尴尬。作为网络…...

5分钟轻松掌握:Magisk让Android手机获得超能力的终极指南

5分钟轻松掌握:Magisk让Android手机获得超能力的终极指南 【免费下载链接】Magisk The Magic Mask for Android 项目地址: https://gitcode.com/GitHub_Trending/ma/Magisk 如果你想让自己的Android手机变得更强大、更自由,Magisk绝对是你不可错过…...