Verilog基础:三段式状态机与输出寄存

相关阅读

Verilog基础![]() https://blog.csdn.net/weixin_45791458/category_12263729.html

https://blog.csdn.net/weixin_45791458/category_12263729.html

对于Verilog HDL而言,有限状态机(FSM)是一种重要而强大的模块,常见的有限状态机书写方式可以分为一段式,二段式和三段式,笔者强烈建议使用三段式因为这样能使状态机逻辑清晰且易于维护。

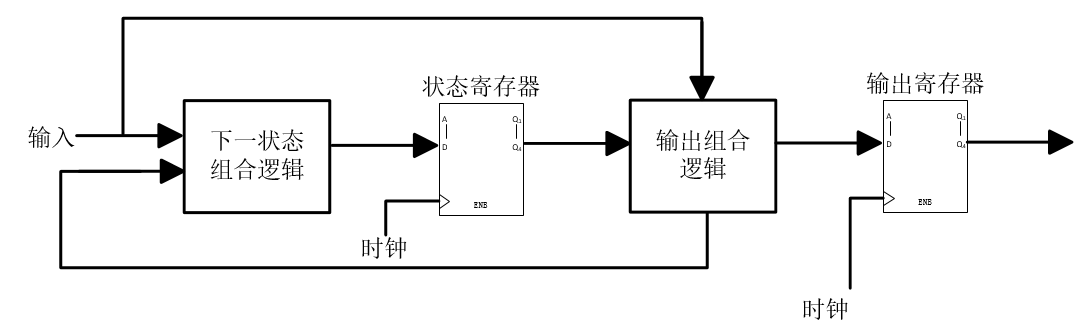

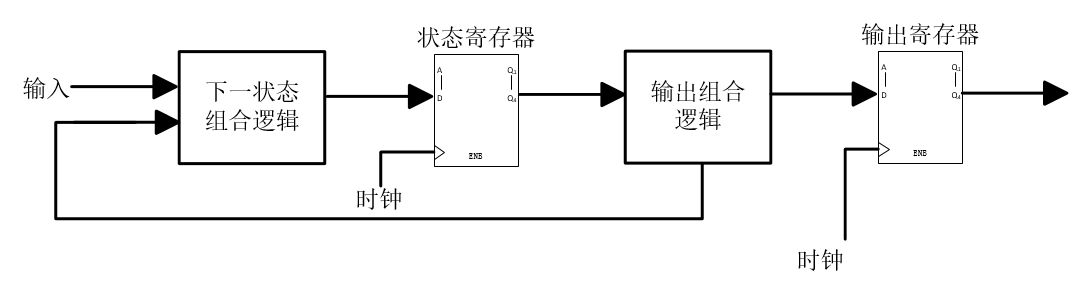

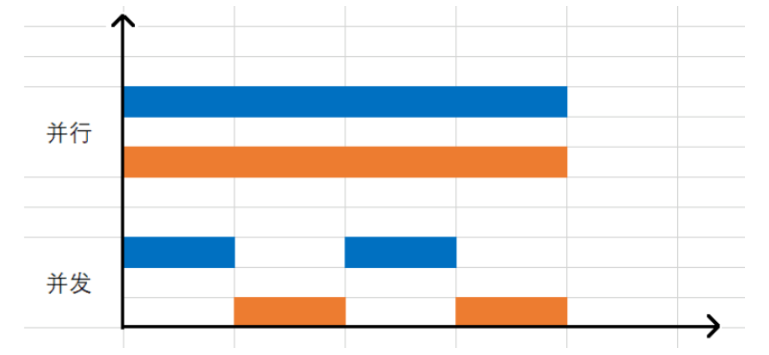

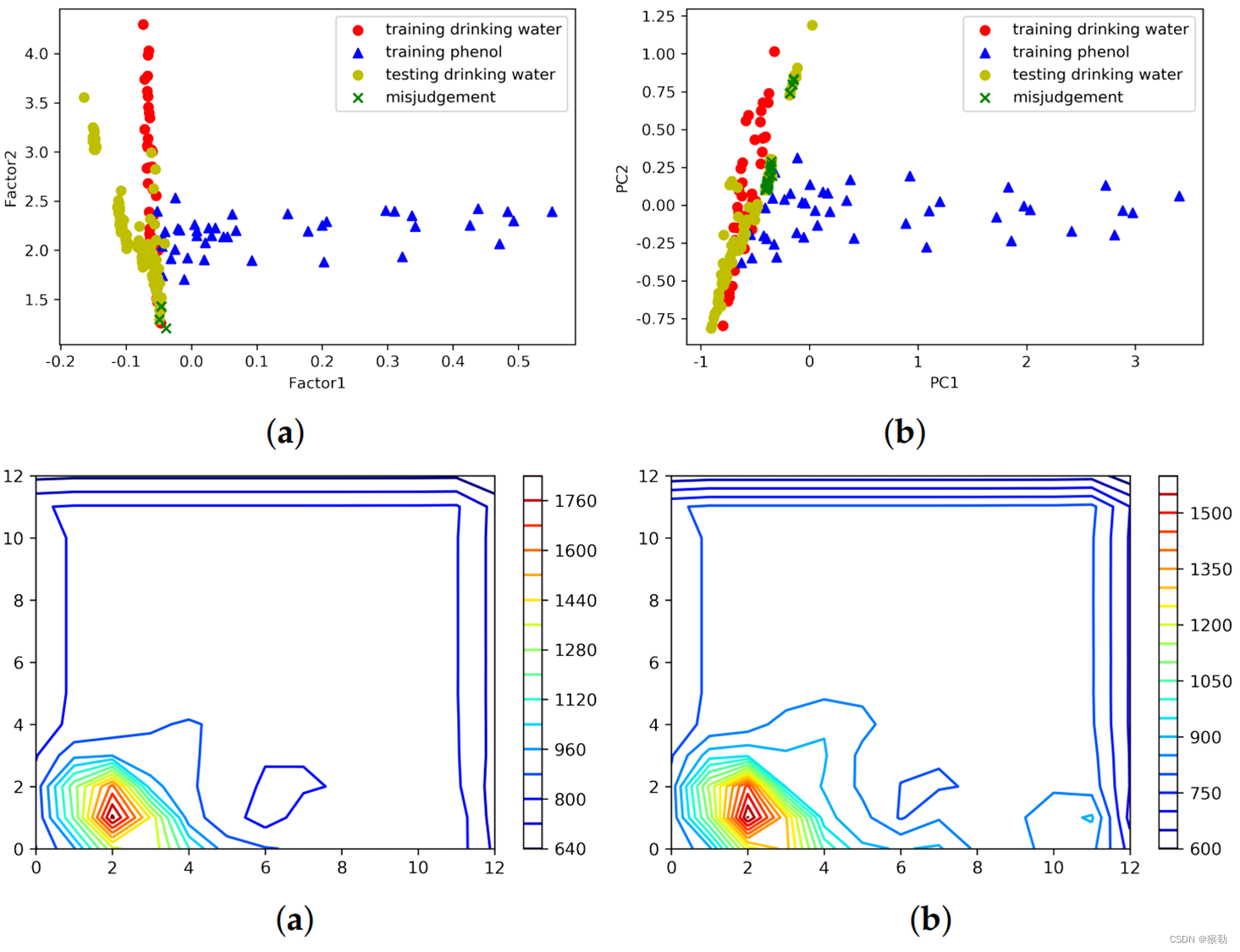

有限状态机有两种基本类型:Mealy机和Moore机。两者的区别在于:Mealy机的下一状态和输出都取决于当前状态和当前输入,而Moore机的下一状态取决于当前状态和当前输入,输出只取决于当前状态。这两类有限状态机的下一状态和输出都是组合逻辑的形式的(指输出不直接来自寄存器的输出),两类状态机的结构如图1、图2所示。

图1 Mealy型状态机

图1 Mealy型状态机

图2 Moore型状态机

图2 Moore型状态机

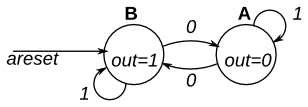

下面以一个简单的例子说明三段式Moore型状态机的书写方式。图3是一个有两个状态的异步复位的Moore机。

图3 一个简单的Moore机

module top_module (input clk,input in,input rst_n,output reg out

);

parameter A = 0;

parameter B = 1;

reg state, next_state; //定义寄存器变量保存状态信息//第一段,下一状态组合逻辑

always@(*) begincase (state) //根据不同的状态和输入,决定下一时钟周期的状态A: next_state = in ? A : B;B: next_state = in ? B : A;endcase

end//第二段,状态转移时序逻辑

always @(posedge clk, negedge rst_n) beginif (!rst_n) state <= B; //异步复位到状态Belse state <= next_state; end//第三段,输出组合逻辑

always@(*) beginif(state == B)out = 1;elseout = 0;

end//因为输出比较简单,这里的第三段的输出组合逻辑也可以用assign连续赋值

//但out此时不能定义为reg

//assign out = (state == B);endmodule对于Mealy型状态机,因为输出直接受输出影响,可能在某些情况下会出现毛刺(即不在时钟边沿的输出变化),所以可以使用寄存器采集输出。对于Moore型状态机,虽然没有输出毛刺的问题,但也可以使用寄存器采集输出以避免大段组合逻辑输出。图4和图5分别给出了寄存输出的Mealy型状态机和Moore型状态机的结构。

图4 寄存输出的Mealy型状态机

图4 寄存输出的Mealy型状态机

图5 寄存输出的Moore型状态机

图5 寄存输出的Moore型状态机

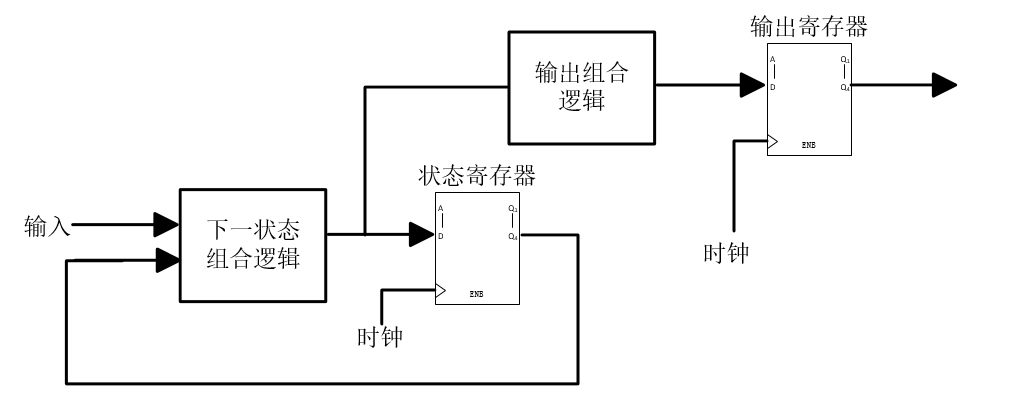

上面两图不难理解,但是一个新的问题出现了,即输出会延后一个周期得到,如果既需要当前周期给出输出,又需要对输出寄存,就不能使用当前状态和输入确定输出,而是应该使用下一状态组合逻辑和输入确定输出。图6和图7给出了这种情况下的Mealy型状态机和Moore型状态机。

图6 寄存输出的Mealy型状态机(下一状态)

图6 寄存输出的Mealy型状态机(下一状态)

图7 寄存输出的Moore型状态机(下一状态)

图7 寄存输出的Moore型状态机(下一状态)

对于Mealy状态机,因为需要状态转移和相应状态的输出同时出现,输出寄存器需要保存由下一状态组合逻辑和的输入推导的输出。对于Moore状态机,输出寄存器需要保存由下一状态组合逻辑推导的输出。

下面用一个更加复杂的有限状态机为例,说明寄存输出的具体写法。这是一个序列检测器,用于检测输入序列中三个连续的1信号,首先给出Moore型序列检测器的Verilog描述。

module Seq_Rec_Moore(output reg D_out, D_out_r1, D_out_r2, input D_in, En, clk, rst_n);parameter S_idle = 3'd0;parameter S_0 = 3'd1;parameter S_1 = 3'd2;parameter S_2 = 3'd3;parameter S_3 = 3'd4;reg [2:0] state, next_state;//下一状态组合逻辑always@(*)begincase(state)S_idle: if((En == 1)&&(D_in == 1))next_state = S_1;else if((En == 1)&&(D_in == 0))next_state = S_0;else next_state = S_idle;S_0: if(D_in == 0)next_state = S_0;else if(D_in == 1)next_state = S_1;elsenext_state = S_idle;S_1: if(D_in == 0)next_state = S_0;else if(D_in == 1)next_state = S_2;else next_state = S_idle;S_2: if(D_in == 0)next_state = S_0;else if(D_in == 1)next_state = S_3;else next_state = S_idle;S_3: if(D_in == 0)next_state = S_0;else if(D_in == 1)next_state = S_3;else next_state = S_idle;default: next_state = S_idle; endcaseend//状态转移时序逻辑always@(posedge clk, negedge rst_n)beginif(!rst_n)state <= S_idle;elsestate <= next_state;end//输出组合逻辑always@(*) beginD_out = (state == S_3);end//寄存输出always @(posedge clk, negedge rst_n) beginif(!rst_n)D_out_r1 <= 0;elseD_out_r1 <= D_out;end//寄存输出(下一状态)always@(posedge clk, negedge rst_n)beginif(!rst_n)D_out_r2 <= 0;elseD_out_r2 <= (next_state == S_3);end

endmodule一个简单的testbench如下所示,图8所示的仿真截图显示了三种不同形式的输出。

`timescale 1ns / 1ns

module t_Seq();reg D_in, clk, rst_n,En;wire D_out, D_out_r1, D_out_r2;Seq_Rec_Moore Seq_Rec_Moore_1 (.D_in(D_in), .clk(clk), .rst_n(rst_n), .D_out(D_out), .En(En), .D_out_r1(D_out_r1), .D_out_r2(D_out_r2));initial beginD_in = 0;clk = 0;rst_n = 1;En = 0;endinitial begin#5 rst_n = 0;#4 rst_n = 1;endalways begin#5 clk = 0;#5 clk = 1;endinitial begin#5 En =1;endinitial begin#5 D_in = 1;end

endmodule 图8 Moore状态机仿真截图

图8 Moore状态机仿真截图

下面是Mealy型序列检测器的Verilog描述。

module Seq_Rec_Mealy(output reg D_out, D_out_r1, D_out_r2, input D_in, En, clk, rst_n);parameter S_idle = 3'd0;parameter S_0 = 3'd1;parameter S_1 = 3'd2;parameter S_2 = 3'd3;parameter S_3 = 3'd4;reg [2:0] state, next_state;//下一状态组合逻辑always@(*)begincase(state)S_idle: if((En == 1)&&(D_in == 1))next_state = S_1;else if((En == 1)&&(D_in == 0))next_state = S_0;else next_state = S_idle;S_0: if(D_in == 0)next_state = S_0;else if(D_in == 1)next_state = S_1;elsenext_state = S_idle;S_1: if(D_in == 0)next_state = S_0;else if(D_in == 1)next_state = S_2;else next_state = S_idle;S_2: if(D_in == 0)next_state = S_0;else if(D_in == 1)next_state = S_3;else next_state = S_idle;S_3: if(D_in == 0)next_state = S_0;else if(D_in == 1)next_state = S_3;else next_state = S_idle;default: next_state = S_idle; endcaseend//状态转移时序逻辑always@(posedge clk, negedge rst_n)beginif(!rst_n)state <= S_idle;elsestate <= next_state;end//输出组合逻辑always@(*) beginD_out = (state == S_3)&(D_in == 1);end//寄存输出always @(posedge clk, negedge rst_n) beginif(!rst_n)D_out_r1 <= 0;elseD_out_r1 <= D_out;end//寄存输出(下一状态)always@(posedge clk, negedge rst_n)beginif(!rst_n)D_out_r2 <= 0;elseD_out_r2 <= (next_state == S_3)&(D_in == 1);end

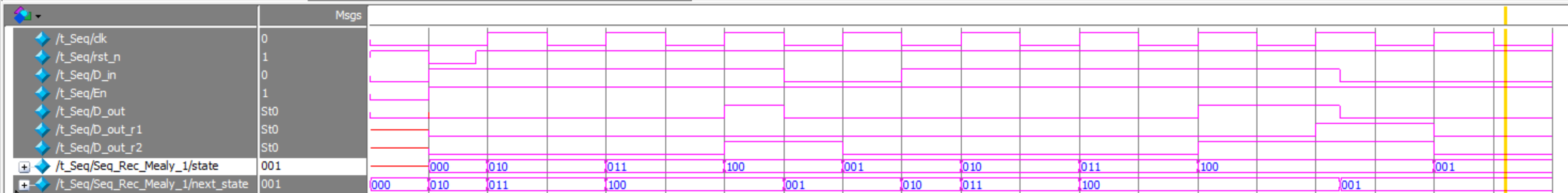

endmodule 图9 Mealy状态机仿真截图

图9 Mealy状态机仿真截图

一个简单的testbench如下所示,图9的仿真截图显示了如果使用寄存输出,而输入无法维持到下个时钟沿,则会丢失寄存输出信号。

`timescale 1ns / 1ns

module t_Seq();reg D_in, clk, rst_n,En;wire D_out, D_out_r1, D_out_r2;Seq_Rec_Mealy Seq_Rec_Mealy_1 (.D_in(D_in), .clk(clk), .rst_n(rst_n), .D_out(D_out), .En(En), .D_out_r1(D_out_r1), .D_out_r2(D_out_r2));initial beginD_in = 0;clk = 0;rst_n = 1;En = 0;endinitial begin#5 rst_n = 0;#4 rst_n = 1;endalways begin#5 clk = 0;#5 clk = 1;endinitial begin#5 En =1;endinitial begin#5 D_in = 1;#30 D_in = 0;#10 D_in = 1;#37 D_in = 0;end

endmodule相关文章:

Verilog基础:三段式状态机与输出寄存

相关阅读 Verilog基础https://blog.csdn.net/weixin_45791458/category_12263729.html 对于Verilog HDL而言,有限状态机(FSM)是一种重要而强大的模块,常见的有限状态机书写方式可以分为一段式,二段式和三段式,笔者强烈建议使用三…...

抖音商城双11好物节,从供需两侧重新定义“好货”

【潮汐商业评论/原创】 你用的第一款护肤品是什么? 大部分人回忆起童年的时候,想起来的都是那款有着牛奶香味的、塑料包装的小袋白色乳霜——郁美净儿童霜。 但是不知何时,它逐渐淡出了很多人、特别是年轻人的视野,直到今年在互…...

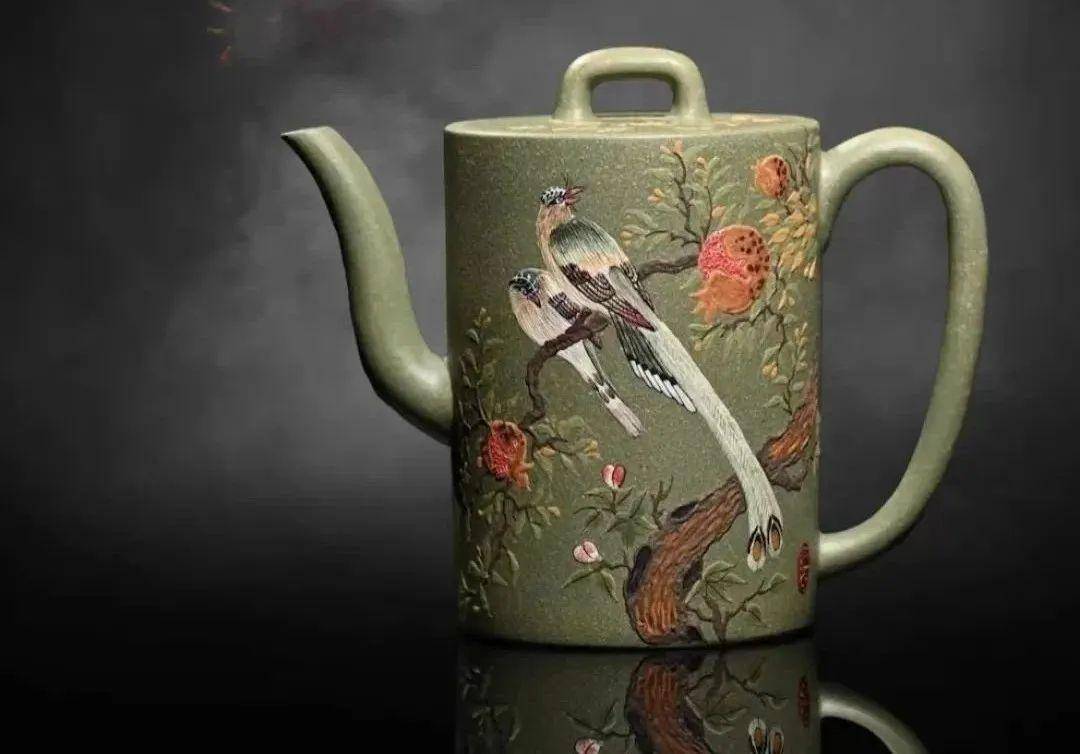

Mysql Explain工具介绍

使用EXPLAIN关键字可以模拟优化器执行SQL语句,分析查询语句或是结构的性能瓶颈。 准备表 -- 课程表 CREATE TABLE class (id int(11) NOT NULL,name varchar(45) DEFAULT NULL,update_time datetime DEFAULT NULL,PRIMARY KEY (id)) ENGINEInnoDB DEFAULT CHARSET…...

Linux系统中的静态库和共享库,以及一些计算机的基础知识

目录 1.库文件 2.静态库 3.共享库 4.静态库与共享库的区别 5.计算机基础知识 6.进程的基础知识 7.主函数的三个参数 1.库文件 1).库文件库是一组预先编译好的方法的集合;Linux系统存储库的位置一般在/lib 和 /usr/lib (64位系统/usr/lib64)库的头文件放在/usr/include 2…...

商品管理图片更换实现

<?xml version="1.0" encoding="UTF-8" ?> <!DOCTYPE mapperPUBLIC "-//mybatis.org//DTD Mapper 3.0//EN""http://mybatis.org/dtd/mybatis-3-mapper.dtd"> <mapper namespace="com.java1234.mapper.ProductMa…...

SDL2 加载图片

1.简介 在SDL中,本身只支持加载BMP格式的图片SDL_LoadBMP,如果想要加载别的格式图片,需要编译SDL_image库。 SDL_image库中IMG_Load和都是IMG_LoadTexture用于加载图片的函数,但是它们的使用方式和返回值有所不同。 IMG_Load和…...

监控和数据采集软件架构和详细设计

介绍 监控和数据采集软件通过提供实时监控、数据收集和分析功能,在各个行业中发挥着至关重要的作用。这些软件应用程序可帮助企业收集有价值的见解、优化流程并做出明智的决策。在本文中,我们将探讨监测和数据采集软件的软件架构、编程技术和详细设计规范…...

链动2+1模式系统开发之区域代理深度解析

区域代理的保护机制:在链动商城系统里设定的代理有唯一性,每个省只有一个省代,每个市只有一个市代,每个区县只有一个区县代。这样也是保护每个代理的收益权益。 区域代理包含的权益类别:购物奖励折扣;区域实…...

Amazon Bedrock | 大语言模型CLAUDE 2体验

这场生成式AI与大语言模型的饥饿游戏,亚马逊云科技也参与了进来。2023年,亚马逊云科技正式发布了 Amazon Bedrock,是客户使用基础模型构建和扩展生成式AI应用程序的最简单方法,为所有开发者降低使用门槛。在 Bedrock 上࿰…...

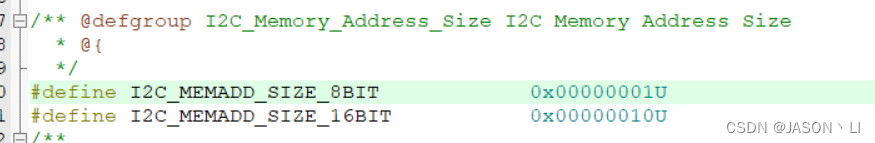

通讯协议学习之路(实践部分):IIC开发实践

通讯协议之路主要分为两部分,第一部分从理论上面讲解各类协议的通讯原理以及通讯格式,第二部分从具体运用上讲解各类通讯协议的具体应用方法。 后续文章会同时发表在个人博客(jason1016.club)、CSDN;视频会发布在bilibili(UID:399951374) 本文…...

『亚马逊云科技产品测评』活动征文|搭建带有“弱”图像处理功能的流媒体服务器

授权声明:本篇文章授权活动官方亚马逊云科技文章转发、改写权,包括不限于在 Developer Centre, 知乎,自媒体平台,第三方开发者媒体等亚马逊云科技官方渠道。 本文基于以下软硬件工具: aws ec2 frp-0.52.3 mediamtx-1.3…...

正交矩阵的定义

对于n阶矩阵A,如果,其中为单位矩阵,为A的转置矩阵,那么就称A为正交矩阵。 对于正交矩阵, 对于正交矩阵,其列向量都是单位向量,行向量都是单位向量...

K8S集群etcd 某个节点数据不一致如何修复 —— 筑梦之路

背景说明 二进制方式安装的k8s集群,etcd集群有3个节点,某天有一台机器hang住了,无法远程ssh登陆,于是被管理员直接重启了,重启后发现k8s集群删除一个deployment应用,多次刷新一会有,一会没有&am…...

selenium/webdriver运行原理与机制

最近在看一些底层的东西。driver翻译过来是驱动,司机的意思。如果将webdriver比做成司机,竟然非常恰当。 我们可以把WebDriver驱动浏览器类比成出租车司机开出租车。在开出租车时有三个角色: 乘客:他/她告诉出租车司机去哪里&a…...

论文阅读[121]使用CAE+XGBoost从荧光光谱中检测和识别饮用水中的有机污染物

【论文基本信息】 标题:Detection and Identification of Organic Pollutants in Drinking Water from Fluorescence Spectra Based on Deep Learning Using Convolutional Autoencoder 标题译名:基于使用卷积自动编码器的深度学习,从荧光光谱…...

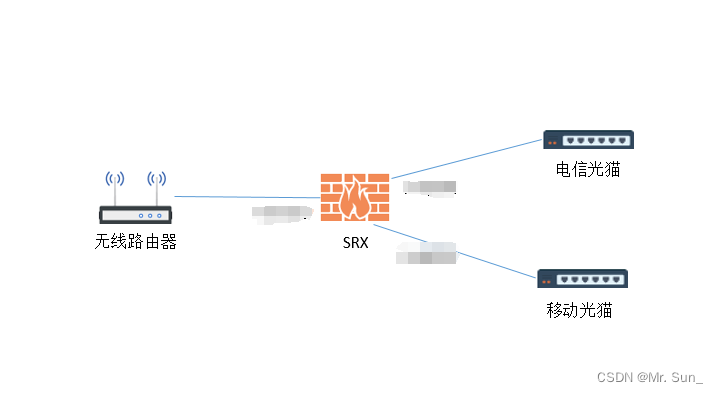

Juniper SRX PPPoE配置

直接上配置脚本 6号口接运营商进行拨号 ---------- set interfaces ge-0/0/6 unit 0 encapsulation ppp-over-ether set interfaces ge-0/0/6 description "Connect_to_Modem" set interfaces pp0 unit 0 pppoe-options underlying-interface ge-0/0/6.0 set inte…...

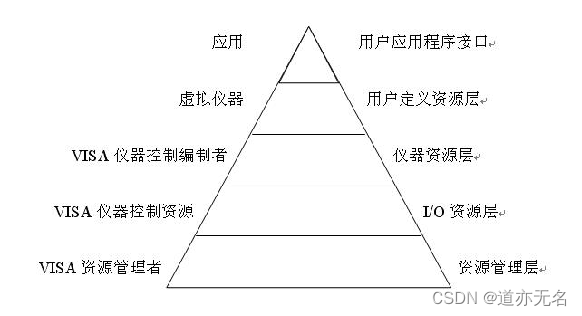

虚拟仪器软件结构VISA

1、什么是VISA VISA是虚拟仪器软件结构(Virtual Instrument Software Architectuere)的简称,是由VXI plug & play系统联盟所统一制定的I/O接口软件标准及其相关规范的总称。一般称这个I/O函数库为VISA库(用于仪器编程的标准I/O函数库)。…...

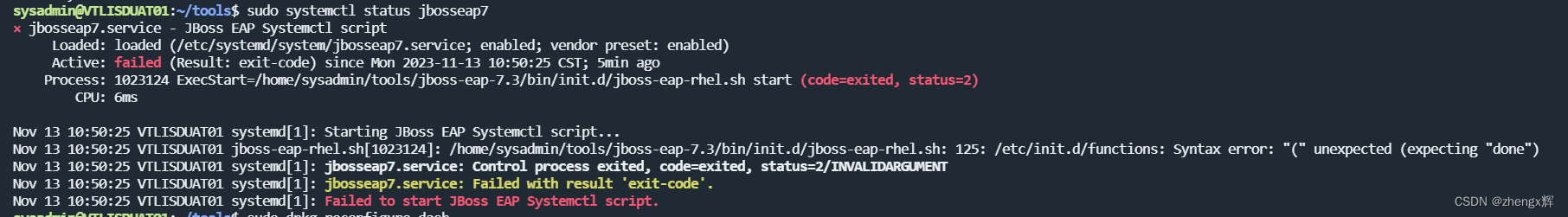

/etc/init.d/functions: Syntax error: “(“ unexpected (expecting “done“)

一.问题描述: ubuntu系统安装服务时报错: 二.问题解析: Ubuntu安装时默认使用dash,shell脚本命令失败,需要安装bash来运行,长期解决该问题就是重新配置dash 三:问题解决: sudo dpkg-reconfi…...

Google/微端/Amazon/IBM四个厂家在分布式里面提供的服务总结

1.背景 最近在复习分布式的课程,发现总有四家公司——Google/微端/Amazon/IBM绕不过去,而他们又开发了许许多多的服务和架构,需要去记忆,于是乎就整理了一下他们提供的服务 2.Google提供的服务 (1)GFS(Go…...

计网:第一章 概述

目录 1.1计算机网络在信息时代作用 1.2因特网概述 1.3三种交换方式 1.4计算机网络的定义和分类 1.5计算机网络的性能指标 1.6计算机网络的体系结构 基于湖科大教书匠b站计算机网络教学视频以及本校课程老师ppt 整合出的计算机网络学习笔记 根据文章目录,具体内…...

清北博雅考研|个性化备考服务指南,适配多元考生上岸需求

作为深耕考研辅导领域的老牌机构,清北博雅考研始终以“学员需求为核心”,打破传统辅导模式的局限,立足不同考生的备考痛点,打造“个性化定制实战化提分全维度保障”的专属服务,不搞同质化套路,不做虚假承诺…...

共享单车智能通信系统架构与技术解析

1. 共享单车通信系统架构解析共享单车的智能通信系统主要由四大核心模块构成:智能车锁、供电系统、通信模块和云端平台。这套系统设计最精妙之处在于,它完美结合了移动通信技术、蓝牙短距传输和GPS定位技术,构建了一个稳定可靠的物联网应用场…...

别再为ESP8266-01S配网发愁了!用STM32F103精英版+机智云,一个按键搞定AirLink

用STM32F103ESP8266-01S实现一键配网的终极方案 每次调试ESP8266-01S的Wi-Fi连接都像在玩俄罗斯轮盘赌?SmartConfig时灵时不灵,AT指令配置又太繁琐?今天我要分享一个让配网变得像按开关一样简单的方案——基于STM32F103和机智云平台的AirLink…...

小程序开发首选免费源码网:全开源生态下的创新加速器

一、全开源免费源码:破解开发难题的“钥匙”1. 降低技术门槛,加速产品落地对于初创团队或个人开发者而言,全开源免费源码的价值在于其“开箱即用”的特性。以GitHub和码云(Gitee)为例,这两个全球最大的开源…...

视觉化看板工具怎么选?9 款创意团队项目协作平台优势分析

本文将深入对比 9 款支持视觉化看板的项目协作工具:Worktile、Trello、Asana、monday.com、ClickUp、Wrike、Notion、Jira、Teambition,重点分析它们在创意团队中的项目管理能力、适用场景、部署方式、协作效率与安全合规差异,帮助企业选型者…...

深度解析WaveTools:鸣潮游戏性能优化与数据分析的专业工具

深度解析WaveTools:鸣潮游戏性能优化与数据分析的专业工具 【免费下载链接】WaveTools 🧰鸣潮工具箱 项目地址: https://gitcode.com/gh_mirrors/wa/WaveTools WaveTools作为一款专为《鸣潮》游戏设计的开源工具箱,通过帧率解锁、画质…...

Win11Debloat:三分钟搞定Windows 11系统瘦身与隐私保护

Win11Debloat:三分钟搞定Windows 11系统瘦身与隐私保护 【免费下载链接】Win11Debloat A simple, lightweight PowerShell script that allows you to remove pre-installed apps, disable telemetry, as well as perform various other changes to declutter and c…...

Unity UXML和USS实战:像搭积木一样设计你的第一个编辑器窗口

Unity UXML与USS模块化开发指南:构建可维护的编辑器界面 在Unity编辑器扩展开发中,界面设计往往成为制约开发效率的瓶颈。传统IMGUI虽然灵活,但维护成本随界面复杂度呈指数级增长。UI Toolkit带来的UXML/USS工作流,正在重塑Unity工…...

transformer 优化笔记 持续更新

目录 方案2:安装 xformers(推荐) 🚀 核心作用:更高效地计算注意力 xfusers 💡 为什么需要 xfusers? 方案2:安装 xformers(推荐) pip install xformers 然…...

终极RVM Gemset完全指南:如何优雅隔离Ruby项目依赖

终极RVM Gemset完全指南:如何优雅隔离Ruby项目依赖 【免费下载链接】rvm Ruby enVironment Manager (RVM) 项目地址: https://gitcode.com/gh_mirrors/rv/rvm Ruby开发中,项目依赖冲突是开发者最头疼的问题之一。Ruby enVironment Manager (RVM) …...