Verilog视频信号图形显示 FPGA(iCE40)

您需要一块带视频输出的 FPGA 板。 我们将在 640x480 下工作,几乎任何视频输出都可以在此像素工作。 它有助于轻松地对 FPGA 板进行编程并相当熟悉 Verilog。 如果您没有开发板,请不要担心,您可以使用 Verilator 模拟器。

材料

- Lattice iCE40

- 即用型开发平台(Xilinx Artix-7)

- 视频板(Xilinx Artix-7)

- 使用 SDL(简单直接媒体层) 进行 Verilator 模拟

屏幕是一个微型宇宙,有自己的空间和时间。从远处看,屏幕显示出平滑的二维图像。 近距离观察,它会分解成许多单独的色块:红色、绿色和蓝色。 我们将这种复杂性隐藏在像素的抽象概念后面:我们可以控制的屏幕的最小部分。 典型的高清屏幕为 1920 x 1080:总共 200 万像素。 即使 640x480 的显示屏也有超过 300,000 个像素。屏幕每秒刷新多次,从而产生运动的错觉。 在 60 Hz 频率下,1920x1080 屏幕每秒绘制 1.24 亿像素! 快速处理大量数据的需求是在硬件级别处理图形的一大挑战。

显示连接器和布线各不相同,但 VGA、HDMI 和 DisplayPort 具有相似的数据设计。 颜色有三个通道,通常是红色、绿色和蓝色,以及水平和垂直同步信号。 可能还有音频和配置数据,但现在这并不重要。红、绿、蓝通道依次承载每个像素的颜色。当屏幕接收到水平同步和垂直同步上的新帧时,屏幕开始新的一行。同步信号是消隐间隔的一部分。

消隐间隔允许阴极射线管 (CRT) 中的电子枪移动到下一行(水平回扫)或屏幕顶部(垂直回扫)。 现代数字显示器保留了消隐间隔,并将其重新用于传输音频和其他数据。

驱动显示器

选择显示时序后,我们就可以创建视频信号了。有四个阶段:

- 像素时钟

- 显示信号

- 绘制图形

- 视频输出(VGA、HDMI、DisplayPort)

像素时钟

我们知道我们需要 25.2 MHz 的频率,但是如何实现它呢?

FPGA 包括锁相环 (PLL),用于生成自定义时钟频率。遗憾的是,并没有配置 PLL 的标准方法。我们需要特定于供应商的设计。

我已经为我们的板子提供了实施方案:

iCE40板子:

module clock_480p (input wire logic clk_12m, // input clock (12 MHz)input wire logic rst, // resetoutput logic clk_pix, // pixel clockoutput logic clk_pix_locked // pixel clock locked?);localparam FEEDBACK_PATH="SIMPLE";localparam DIVR=4'b0000;localparam DIVF=7'b1000010;localparam DIVQ=3'b101;localparam FILTER_RANGE=3'b001;logic locked;SB_PLL40_PAD #(.FEEDBACK_PATH(FEEDBACK_PATH),.DIVR(DIVR),.DIVF(DIVF),.DIVQ(DIVQ),.FILTER_RANGE(FILTER_RANGE)) SB_PLL40_PAD_inst (.PACKAGEPIN(clk_12m),.PLLOUTGLOBAL(clk_pix), // use global clock network.RESETB(rst),.BYPASS(1'b0),.LOCK(locked));endmodule

开发平台:

module clock_480p (input wire logic clk_12m, // input clock (12 MHz)input wire logic rst, // resetoutput logic clk_pix, // pixel clockoutput logic clk_pix_locked // pixel clock locked?);localparam FEEDBACK_PATH="SIMPLE";localparam DIVR=4'b0000;localparam DIVF=7'b1000010;localparam DIVQ=3'b101;localparam FILTER_RANGE=3'b001;logic locked;SB_PLL40_PAD #(.FEEDBACK_PATH(FEEDBACK_PATH),.DIVR(DIVR),.DIVF(DIVF),.DIVQ(DIVQ),.FILTER_RANGE(FILTER_RANGE)) SB_PLL40_PAD_inst (.PACKAGEPIN(clk_12m),.PLLOUTGLOBAL(clk_pix), // use global clock network.RESETB(rst),.BYPASS(1'b0),.LOCK(locked));endmodule

显示信号

我们可以从像素时钟和显示时序生成同步信号。我们还想报告当前的屏幕位置以了解何时绘制内容。

我们用一个简单的显示模块来完成这两件事:

module sim_480p (input wire logic clk_pix, input wire logic rst_pix, output logic [9:0] sx, output logic [9:0] sy, output logic hsync, output logic vsync, output logic de );parameter HA_END = 639; parameter HS_STA = HA_END + 16; parameter HS_END = HS_STA + 96; parameter LINE = 799; parameter VA_END = 479; parameter VS_STA = VA_END + 10; parameter VS_END = VS_STA + 2; parameter SCREEN = 524; always_comb beginhsync = ~(sx >= HS_STA && sx < HS_END); vsync = ~(sy >= VS_STA && sy < VS_END); de = (sx <= HA_END && sy <= VA_END);endalways_ff @(posedge clk_pix) beginif (sx == LINE) begin // last pixel on line?sx <= 0;sy <= (sy == SCREEN) ? 0 : sy + 1; // last line on screen?end else beginsx <= sx + 1;endif (rst_pix) beginsx <= 0;sy <= 0;endend

endmodule

测试台

绘制图形

视频输出

Verilator仿真

关联项目

- 驱动 32×32 RGB LED 矩阵

- FPGA游戏台

- VGA时钟

- 光束射线追踪器赛车

- FPGA 媒体播放器

参阅一:亚图跨际

参阅二:亚图跨际

相关文章:

)

Verilog视频信号图形显示 FPGA(iCE40)

您需要一块带视频输出的 FPGA 板。 我们将在 640x480 下工作,几乎任何视频输出都可以在此像素工作。 它有助于轻松地对 FPGA 板进行编程并相当熟悉 Verilog。 如果您没有开发板,请不要担心,您可以使用 Verilator 模拟器。 材料 Lattice iCE…...

【LeetCode 面试经典150题】26. Remove Duplicates from Sorted Array 在有序数组中移除重复元素

26. Remove Duplicates from Sorted Array 题目大意 Given an integer array nums sorted in non-decreasing order, remove the duplicates in-place such that each unique element appears only once. The relative order of the elements should be kept the same. Then …...

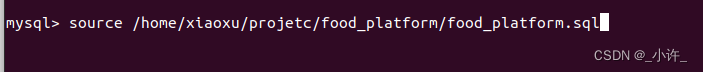

linux系统下sql脚本的执行与导出

terminal中执行 执行 mysql -u [username] -p -D [databasename] < [XXX.sql] 导出 mysql -u [username] -p [datbasename] > [XXX.sql] 导出的数据库名自定义。 mysql -u [username] -p [databasename] [tablename] > [xxx.sql] 导出表名自定义 mysql shell 执行 …...

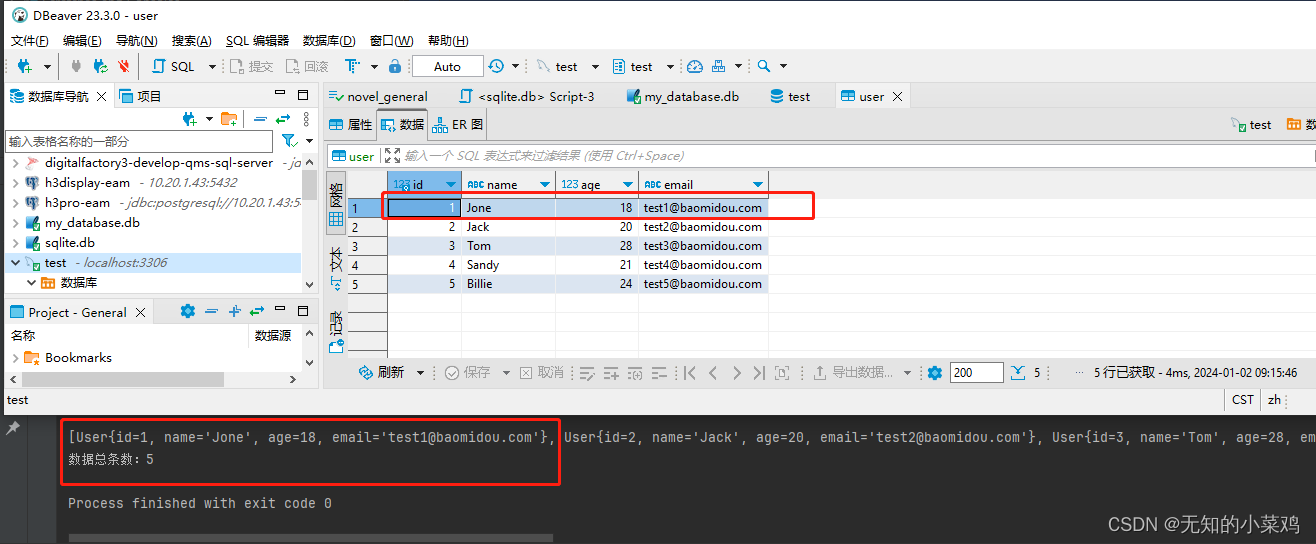

MyBatis学习一:快速入门

前言 公司要求没办法,前端也要了解一下后端知识,这里记录一下自己的学习 学习教程:黑马mybatis教程全套视频教程,2天Mybatis框架从入门到精通 文档: https://mybatis.net.cn/index.html MyBatis 快速入门…...

零售业物流这个防漏水技术,居然没有翻车!

随着科技的不断发展,水浸监控系统在各个领域得到了广泛应用。水浸监控不仅仅是为了保护建筑结构和设备,更是为了防范因水灾引起的生命安全和财产损失。 因此,为了有效预防和应对水浸事件,水浸监控系统应运而生,成为各行…...

主浏览器优化之路1——你现在在用的是什么浏览器?Edge?谷歌?火狐?360!?

上一世,我的浏览器之路 引言为什么要用两个浏览器为什么一定要放弃火狐结尾给大家一个猜数字小游戏(测运气) 引言 小时候,我一开始上网的浏览器是2345王牌浏览器吧, 因为上面集成了很多网站,我记得上面有7…...

gitlab请求合并分支

直接去看原文: 原文链接:Gitlab合并请求相关流程_source branch target branch-CSDN博客 --------------------------------------------------------------------------------------------------------------------------------- 入口: 仓库控制台的这两个地方都…...

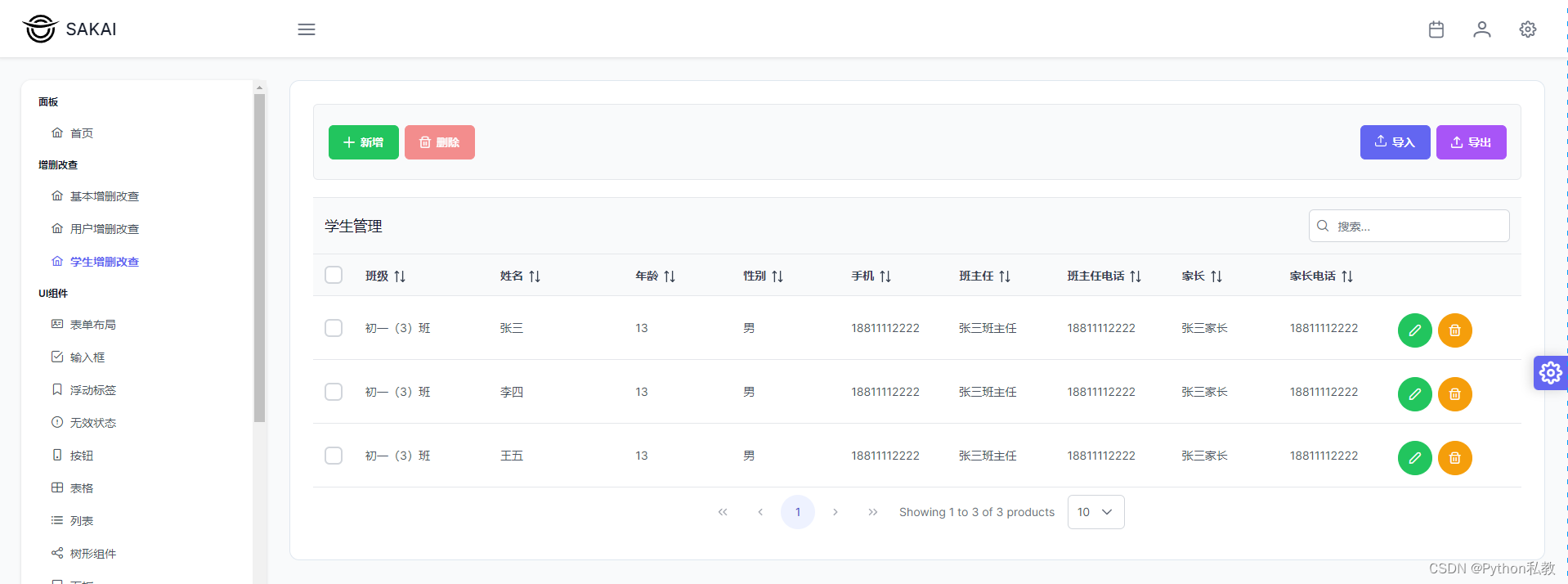

使用Vue3开发学生管理系统模板1

环境搭建 通过解压之前《Vue3开发后台管理系统模板》的代码,我们能够得到用户增删改查的页面,我们基于用户增删改查的页面做进一步的优化。 创建学生增删改查页面 第一步:复制用户增删改查页面,重命名为StudentCRUD.vue <…...

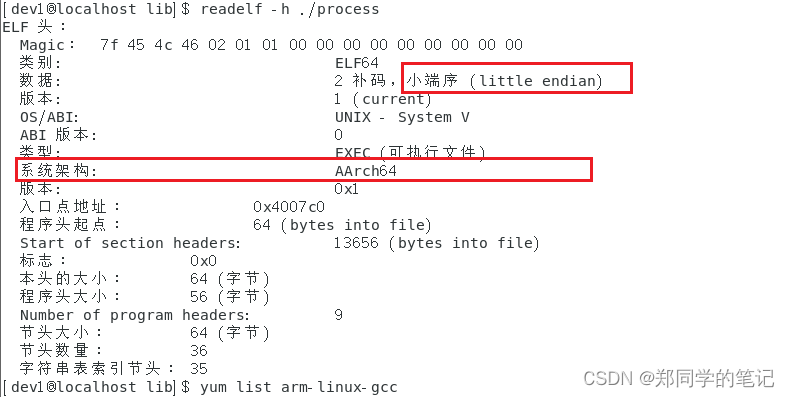

【cmake实战:番外】交叉编译——Linaro

【cmake实战:番外】交叉编译——Linaro 一、交叉编译1、交叉编译简介2、为什么会有交叉编译 二、交叉编译链1、什么是交叉编译链2、交叉编译工具 三、Linaro1、下载2、解压3、demo3.1、toolchain_aarch64.cmake3.2、CMakeLists.txt3.3、main.cpp 4、执行编译5、查看…...

)

2024年年初Java5年实战面试题(北京)

高阶篇: 一、在面对千万条并发请求的情况下,如果数据库频繁查询导致崩溃,可以采取以下措施来解决问题: 1.缓存数据:可以使用缓存技术来减少对数据库的查询次数。将经常查询的数据存储在缓存中,例如使用Redis等内存数据库ÿ…...

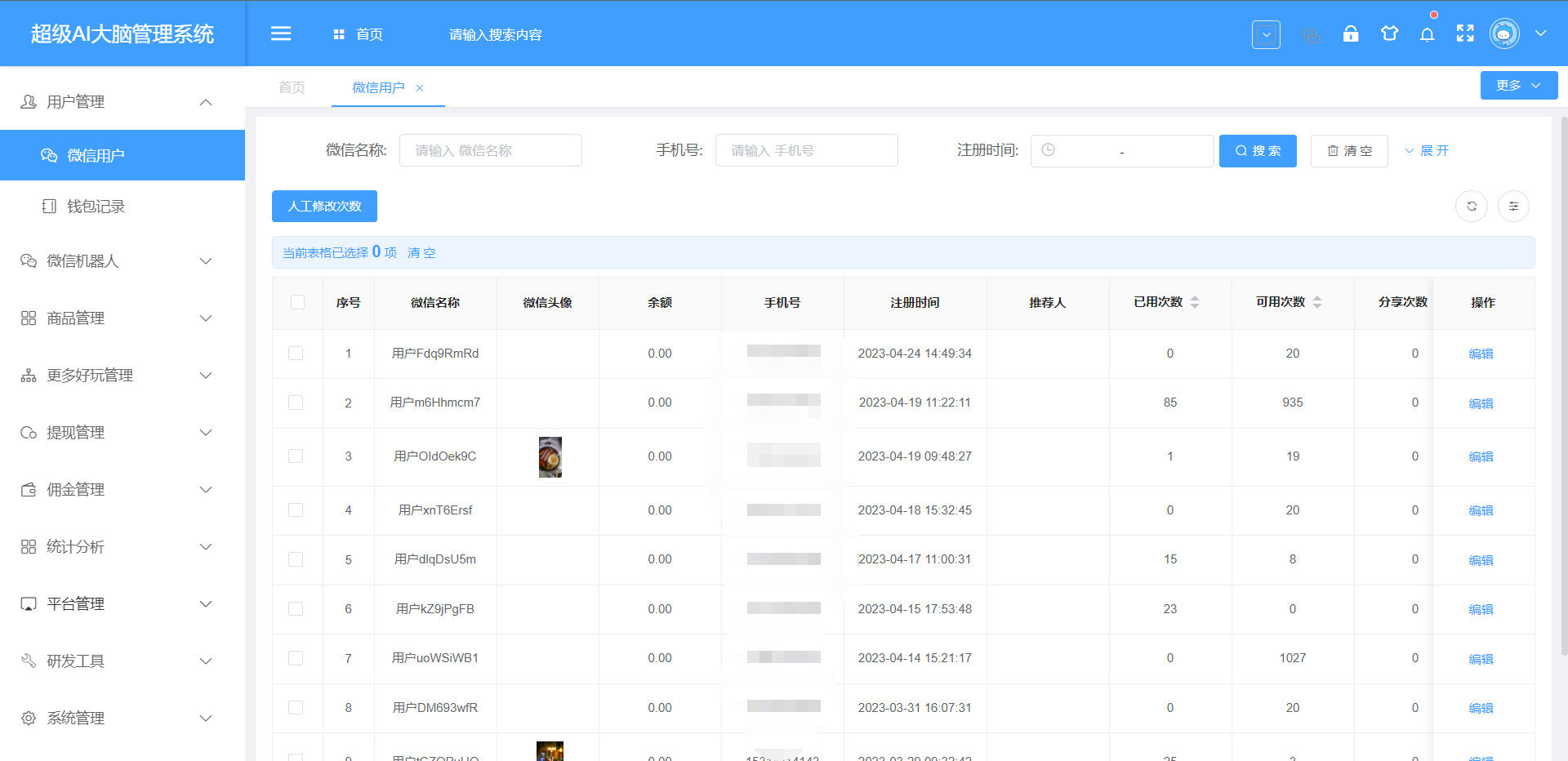

【Apache-2.0】springboot-openai-chatgpt超级AI大脑产品架构图

springboot-openai-chatgpt: 一个基于SpringCloud的Chatgpt机器人,已对接GPT-3.5、GPT-4.0、百度文心一言、stable diffusion AI绘图、Midjourney绘图。用户可以在界面上与聊天机器人进行对话,聊天机器人会根据用户的输入自动生成回复。同时也支持画图&a…...

如何在iPhone设备中查看崩溃日志

目录 如何在iPhone设备中查看崩溃日志 摘要 引言 导致iPhone设备崩溃的主要原因是什么? 使用克魔助手查看iPhone设备中的崩溃日志 奔溃日志分析 总结 摘要 本文介绍了如何在iPhone设备中查看崩溃日志,以便调查崩溃的原因。我们将展示三种不同的…...

对接第三方接口鉴权(Spring Boot+Aop+注解实现Api接口签名验证)

前言 一个web系统,从接口的使用范围也可以分为对内和对外两种,对内的接口主要限于一些我们内部系统的调用,多是通过内网进行调用,往往不用考虑太复杂的鉴权操作。但是,对于对外的接口,我们就不得不重视这个…...

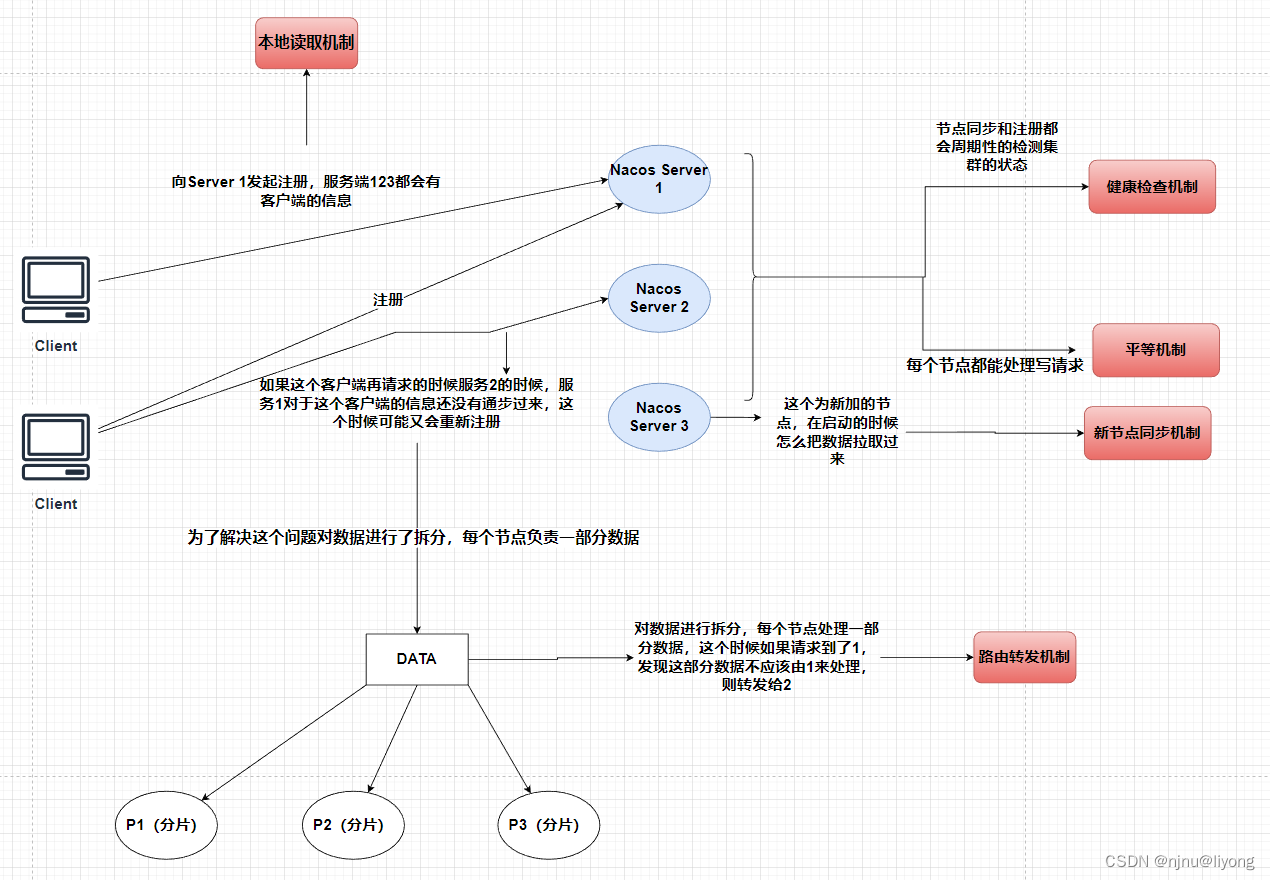

微服务-理论(CAP,一致性协议)

CAP理论 关于CAP理论的介绍可以直接看这篇文章 CAP分别是什么? 一致性(Consistency 一致性包括强一致性,弱一致性,最终一致性。 一致性其实是指数据的一致性,为什么数据会不一致呢? 如上面这张图&…...

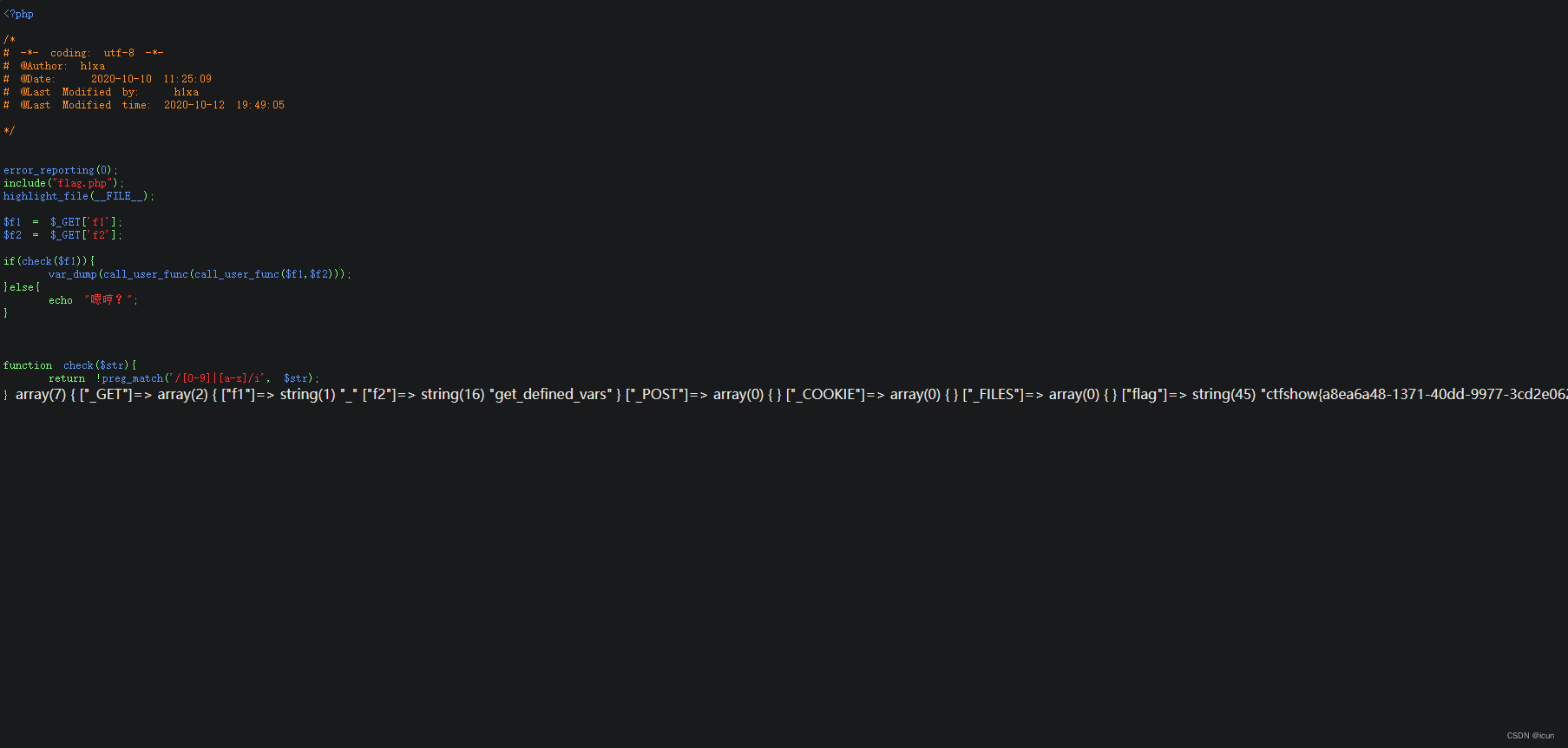

CTFshow web入门web128-php特性31

开启环境: 一个新的姿势,当php扩展目录下有php_gettext.dll时: _()是一个函数。 _()gettext() 是gettext()的拓展函数,开启text扩展get_defined_vars — 返回由所有已定义变量所组成的数组。 call_user_func — 把第一个参数作为回调函数调…...

再见2023,你好2024(附新年烟花python实现)

亲爱的朋友们: 写点什么呢,我已经停更两个月了。2023年快结束了,时间真的过得好快,总要写点什么留下纪念吧。这一年伴随着许多挑战和机会,给了我无数的成长和体验。坦白说,有时候我觉得自己好像是在时间的…...

Redis 的常用命令

一、Redis 通用命令 TYPE key:返回 key 所储存的值的类型。 OBJECT ENCODING key:返回key所储存的值的底层编码方式。 DEL key:该命令用于在 key 存在时删除 key。 EXPIRE key seconds:设置指定key的过期时间。 RENAME key newke…...

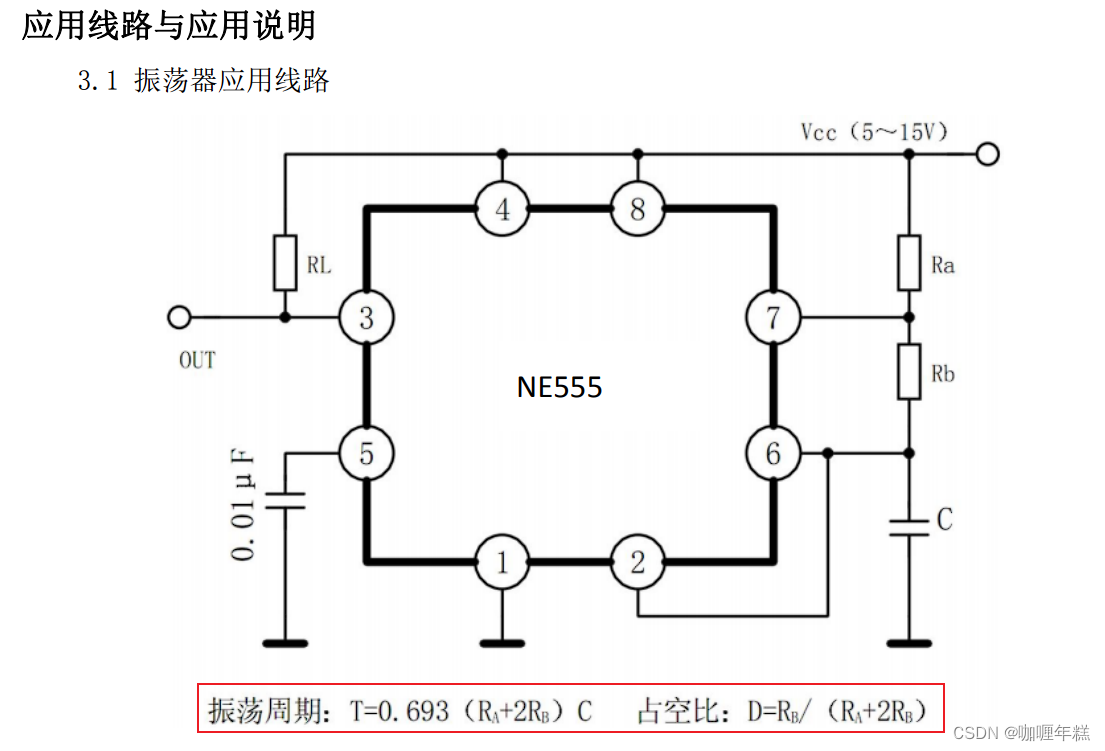

【模拟电路】模拟集成电路之神-NE555

一、集成电路NE555简介 二、功能框图与引脚说明 三、比较器(运放) 四、反相门(非门) 五、或非门 六、双稳态触发器 七、NE555的工作原理 集成电路NE555的芯片手册 C5157696 一、集成电路NE555简介 NE555起源于上个世纪70年代&a…...

)

收集最新的 Sci-Hub 网址(本文章持续更新2024)

自用收集最新的 Sci-Hub 网址 本文章持续更新收集 Sci-Hub 的可用网址链接仅供交流学习使用,如对您有所帮助,请收藏并推荐给需要的朋友,由于网站限制,不一定所有网址都能在您所在的位置访问,通常情况下,一…...

)

针对NPC客户端的升级(脚本执行)

上一次我们使用NPS自动注册的方式,在被控端上实现了自动创建NPC客户端链接。 Linux主机自动注册NPS客户端(脚本化) 但是在使用过程中我发现存在很多的问题,如果被控端重启客户端或者出现了多个NPS时会造成冲突,所以考虑…...

深度解析:如何高效实现Android应用级定位模拟的完整方案

深度解析:如何高效实现Android应用级定位模拟的完整方案 【免费下载链接】FakeLocation Xposed module to mock locations per app. 项目地址: https://gitcode.com/gh_mirrors/fak/FakeLocation 在移动应用开发和测试领域,精准控制定位信息是确保…...

四川全行业 APP 开发服务商参考

随着四川各行业数字化进程加快,APP 开发覆盖政务、电商、教育、生活服务、企业管理等多元场景,市场服务商在行业适配、技术能力、服务保障上各有侧重。本文结合多行业落地案例、技术全面性、交付稳定性、运维支持能力,整理全行业适配的 APP 开…...

OctoSuite代码审查:深入理解GitHub数据模型设计的5个关键要点

OctoSuite代码审查:深入理解GitHub数据模型设计的5个关键要点 【免费下载链接】octosuite Terminal-based toolkit for GitHub data analysis. 项目地址: https://gitcode.com/gh_mirrors/oc/octosuite OctoSuite是一个强大的终端GitHub数据分析工具包&#…...

从Xilinx 7系列FPGA看架构演进与工程选型实战

1. 项目概述:从一则旧闻看FPGA的演进与选型看到这个标题,很多朋友可能会觉得这是一则十多年前的“旧闻”了。确实,2011年Xilinx宣布其28nm 7系列FPGA在六个月内获得超过200个设计订单,这在当时是半导体行业的一个里程碑。但今天回…...

Deep Multiview Clustering by Contrasting Cluster Assignments

通过对比不同的聚类分配实现深度多视图聚类摘要深度学习在大规模多视图聚类上表现好,但是该领域如何学习不同视图的潜在表示仍是一个问题。作者认为不同视图之间应该对齐的不是中间层特征,而是最后的聚类分配结果。因此提出 CVCL,通过对比不同…...

基于LLM的风格化内容生成:从提示工程到系统化实践

1. 项目概述:一个基于AI的创意内容生成工具最近在折腾AI应用开发,发现了一个挺有意思的项目,叫“jasonkneen/vibeclaw”。乍一看这个名字,可能会有点摸不着头脑,但简单来说,它是一个利用大型语言模型&#…...

5分钟搞定VRoid Studio中文界面:汉化插件完全使用指南

5分钟搞定VRoid Studio中文界面:汉化插件完全使用指南 【免费下载链接】VRoidChinese VRoidStudio汉化插件 项目地址: https://gitcode.com/gh_mirrors/vr/VRoidChinese 你是否因为VRoid Studio的全英文界面而感到困扰?作为一款功能强大的3D角色设…...

温室大棚结构设计与选型指南:从荷载计算到智能控制系统

摘要 温室大棚作为现代农业的核心基础设施,其结构设计、材料选型及环境调控系统的合理性直接影响作物产量与运营成本。本文从工程技术角度出发,系统介绍日光温室、智能连栋温室、菌菇专用大棚等常见类型的技术特点、结构参数、荷载计算要点及智能控制系统…...

航空航天装备制造行业「气动外形工程师→型号总师、技术副总、CTO」完整晋升路径

适配主机厂、飞行器研究所、航空航天整机 / 无人机 / 导弹装备制造企业,纯技术线 技术管理线双轨晋级,从气动外形基层岗一路到集团 / 公司 CTO,岗位阶梯清晰无断层。一、基层技术阶段(入门→骨干,纯气动专业ÿ…...

客户总问案件进度?知识产权自助查询系统让咨询量直降 80%

做知产代理的伙伴一定深有体会:客服每天大半时间都在回复 **“案件到哪一步了?”“历史文件发我一下”“去年委托的案子状态是什么”**;找历史文档要翻遍聊天记录、文件夹,耗时又尴尬;高频次沟通占用大量人力ÿ…...