【FPGA】Verilog:时序电路应用 | 序列发生器 | 序列检测器

前言:本章内容主要是演示Vivado下利用Verilog语言进行电路设计、仿真、综合和下载

示例:序列发生器与序列检测器

- 功能特性: 采用 Xilinx Artix-7 XC7A35T芯片

- 配置方式:USB-JTAG/SPI Flash

- 高达100MHz 的内部时钟速度

- 存储器:2Mbit SRAM N25Q064A SPI Flash(样图旧款为N25Q032A)

- 通用IO:Switch :x8LED:x16Button:x5DIP:x8 通用扩展IO:32pin

- 音视频/显示: 7段数码管:x8 VGA视频输出接口 Audio音频接口

- 通信接口:UART:USB转UART Bluetooth:蓝牙模块

- 模拟接口: DAC:8-bit分辨率 XADC:2路12bit 1Msps ADC

目录

Ⅰ. 前置知识

0x00 序列检测器

0x01 序列发生器

Ⅱ. 示例讲解

0x00 序列发生器

0x01 序列检测器

Ⅲ. Verilog实现

0x00 序列检测器

0x01 序列发生器

Ⅰ. 前置知识

0x00 序列检测器

序列检测器在数据通讯,雷达和遥测等领域中用于检测同步识别标志。

它是一种用来检测一组或多组序列信号的电路。例如检测器收到一组指定的串行码后,输出标志1,否则,输出0。检测器每收到一个符合要求的串行码就需要用一个状态进行记忆。

若要检测的串行码长度为N位,则需要N个状态;另外,还需要增加一个“未收到一个有效位”的初始状态,共N+1个状态;

0x01 序列发生器

序列发生器用于产生一个指定序列串,与序列检测器类似,每产生一个符合要求的串行码就需要用一个状态进行记忆。

若要产生的串行码长度为N位,则需要N个状态;另外,还需要增加一个“未产生一个有效位”的初始状态,共N+1个状态

❗注:

进行序列发生器或者序列检测器的设计,首先按要求画出状态转换图(表),然后按照实现方案采用经典设计方法或者Verilog语言完成设计。

Ⅱ. 示例讲解

0x00 序列发生器

设计一个序列发生器,输出序列为110100

a、设计实现方法;

b、基于Verilog语言完成设计;

c、利用VIVADO验证并给出testbench结果(波形图)。

参考方法一:计数器加组合输出网络类型

计数型序列信号发生器的结构框图如图示:

它由计数器和组合输出网络两部分组成,序列信号从组合输出网络输出。

这种类型的序列信号发生器一般分两步来设计,首先根据序列的长度M设计模M计数器,计数器的状态可以自定;然后按计数器的状态转移关系和序列码的要求设计组合输出网络。

由于计数器的状态设置和输出网络没有直接的关系,因此这种结构对于输出序列的更改比较方便,而且还能同时产生多组序列码。

下面描述的为计数器加组合输出网络构成的序列信号发生器,产生001011序列信号,通过内部的3位计数器进行计数,由计数状态和输出序列的对应关系,得到其输出组合逻辑真值表,从表中可以看到,Q2Q1Q0从000开始计数并不断加1,每个状态对应一个输出Z。通过真值表可以得到卡诺图,

化简后可以得到输出逻辑函数为:![]()

| Q2 | Q1 | Q0 | Z |

| 0 | 0 | 0 | 0 |

| 0 | 0 | 1 | 0 |

| 0 | 1 | 0 | 1 |

| 0 | 1 | 1 | 0 |

| 1 | 0 | 0 | 1 |

| 1 | 0 | 1 | 1 |

参考代码如下:

module sequence_signal_counter(input clk, input rst_n, output outD);

//实现001011序列信号产生reg [2:0] counter;always @(posedge clk) beginif(rst_n == 1'b0) counter <= 3'b000;else if(counter == 3'b101) counter <= 3'b000;else counter <= counter + 1'b1;endassign outD = ((~counter[0]) & counter[1]) | counter[2];

endmodule参考方法二:寄存器方式实现的序列信号产生器。

利用6位移位寄存器方式实现序列信号产生器,在输入端din输入任意序列,通过移位寄存器,使得输入信号的最高位移入最低位,其他各位依次向左移一位,在每个时钟上升沿到来时,将输入信号的最高位通过dout输出,从而循环产生序列信号。

module sequence_signal_shifter(input clk, input rst, input [5:0] din, output outD); reg dout;reg [5:0] temp;assign outD=dout;always@(posedge clk)beginif(rst == 1'b0)temp <= din;elsebegindout <= temp[5];temp <= {temp[4:0], temp[5]};endend

endmodule参考方法三:利用有限状态机构造序列信号产生器。关于状态图和状态机的构造可以参考下面序列检测器的内容。

module sequence_signal_FSM(input clk, input rst_n, output outD);//有限状态机方式实现010011序列信号产生器reg dout; reg [2:0] pre_state, next_state; parameter s0 = 3'b000, s1 = 3'b001, s2 = 3'b010, s3 = 3'b011, s4 = 3'b100, s5 = 3'b101; assign outD=dout;always @(posedge clk or negedge rst_n) begin if(rst_n == 0) pre_state <= s0; //让初始为输出0的状态,观察与设为s5的区别else pre_state <= next_state; end always @(pre_state) begin case(pre_state) s0: begin dout = 1'b0; next_state <= s1; end s1: begin dout = 1'b1; next_state = s2; end s2: begin dout = 1'b0; next_state = s3; end s3: begin dout = 1'b0;next_state = s4; end s4: begin dout = 1'b1;next_state = s5; end s5: begin dout = 1'b1;next_state = s0; end default: next_state = s0; endcase end

endmodule0x01 序列检测器

设计一个序列检测器,检测序列为11010

a、画出状态转换图;

b、基于Verilog语言完成设计,结合序列发生器,编写顶层文件,在vivado中验证并给出整体test bench结果(波形图)

下面讨论状态机的设计方法:

在“11010”序列检测器中,有6个状态,如果加上一个Idle状态,共7个状态,最初的状态分析如下表:

| input NS/out PS | 0 | 1 |

| IDLE | 0/0 | 1/0 |

| 0 | 0/0 | 1/0 |

| 1 | 0/0 | 11/0 |

| 11 | 110/0 | 11/0 |

| 110 | 0/0 | 1101/0 |

| 1101 | 11010/1 | 11/0 |

| 11010 | 0/0 | 1/0 |

| Present State | Next State/Output | |

对应状态图如图:

首先考虑是否可以通过状态化简,简化电路结构,减少Verilog代码量。

可以看到状态“Idle”、状态“0”和“11010”在相同的输入下,它们的次态、输出都完全相同,故此三个状态可以化简为一个状态。化简结果如下表和下图。

| input NS/out PS | 0 | 1 |

| 0 | 0/0 | 1/0 |

| 1 | 0/0 | 11/0 |

| 11 | 110/0 | 11/0 |

| 110 | 0/0 | 1101/0 |

| 1101 | 0/1 | 11/0 |

| Present State | Next State/Output | |

接下来对化简后的状态进行命名、编码。本例将“0”,“1”,“11”,“110”,“1101”状态分别命名为“S0”,“S1”,“S11”,“S110”,“S1101”。

Verilog参考程序如下:

module sequence_detector(input seq, input clk, input rst,output Z); // detector "11010"

reg b;

reg [4:0]state;

assign Z=b;

parameter S0 = 5'b1_0000,S1 = 5'b0_1000,S11 = 5'b0_0100,S110 = 5'b0_0010,S1101 = 5'b0_0001;

//状态的记录利用one-hot编码

always @(posedge clk or negedge rst) //low activeif (!rst) beginstate <= S0;b <= 0;endelse case(state)S0: if( seq == 0)beginstate <= S0;b <= 0;endelsebeginstate <= S1;b <= 0;endS1: if( seq == 0)beginstate <= S0;b <= 0;endelsebeginstate <= S11;b <= 0;endS11: if( seq == 0)beginstate <= S110;b <= 0;endelsebeginstate <= S11;b <= 0;endS110: if( seq == 0)beginstate <= S0;b <= 0;endelsebeginstate <= S1101;b <= 0;endS1101: if( seq == 0)beginstate <= S0;b <= 1;endelsebeginstate <= S11;b <= 0;enddefault state <= 5'bx;endcase

endmoduleⅢ. Verilog实现

0x00 序列检测器

设计代码:

module t_11010(reset,clk,x,z);

input reset,clk,x;

output z;

parameter y0=3'b000,y1=3'b001,y2=3'b010,y3=3'b011,y4=3'b100,y5=3'b101;

reg z;

reg [3:1] now,next;

always@(posedge clk)

if(!reset)now<=y0;

else now<=next;always@(x or now)

case(now)

y0:if(x) next=y1;

else next=y0;

y1:if(x) next=y2;

else next=y0;

y2:if(!x)next=y3;

else next=y2;

y3:if(x) next=y4;

else next=y0;

y4:if(!x) next=y0;

else next=y2;

default:next=y0;

endcasealways @(posedge clk)

if(!reset)z<=0;

else if((now==y0)&&(x==0))z<=1;

else z<=0;

endmodule

仿真代码:

module sim_pj1();

reg reset,clk,x;

wire z;

reg[10:0]test;

t_11010 uu1(reset,clk,x,z);

initial begin

clk=0;

reset=0;

test=11'd0;

#100 reset=1;

test=11'b0001_1010_000;

end

always #20 clk=~clk;

always #40

begin

x=test[10];

test={test[9:0],test[10]};

endendmodule

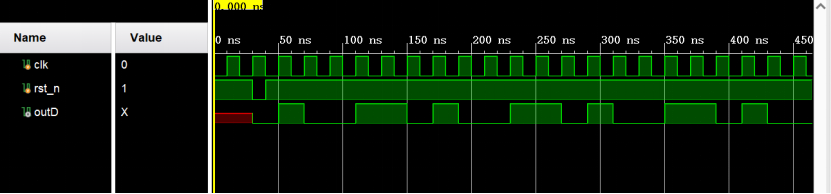

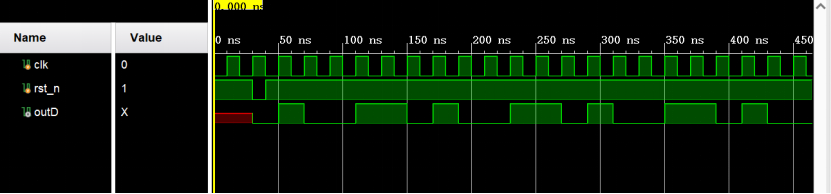

仿真波形:

0x01 序列发生器

设计代码:

module sequence_signal_FSM(input clk, input rst_n, output outD);//有限状态机方式实现010011序列信号产生器reg dout; reg [2:0] pre_state, next_state; parameter s0 = 3'b000, s1 = 3'b001, s2 = 3'b010, s3 = 3'b011, s4 = 3'b100, s5 = 3'b101; assign outD=dout;always @(posedge clk or negedge rst_n) begin if(rst_n == 0) pre_state <= s0; //让初始为输出0的状态,观察与设为s5的区别else pre_state <= next_state; end always @(pre_state) begin case(pre_state) s0: begin dout = 1'b0; next_state <= s1; end s1: begin dout = 1'b1; next_state = s2; end s2: begin dout = 1'b0; next_state = s3; end s3: begin dout = 1'b0;next_state = s4; end s4: begin dout = 1'b1;next_state = s5; end s5: begin dout = 1'b1;next_state = s0; end default: next_state = s0; endcase end

endmodule仿真代码:

module sim_sequence_signal_FSM();reg clk;reg rst_n;wire outD;sequence_signal_FSM uu1(clk,rst_n,outD);initial beginclk=0;rst_n=1;#30;rst_n=0;#10;rst_n=1;endalways #10 clk=~clk;

endmodule

仿真波形图:

相关文章:

【FPGA】Verilog:时序电路应用 | 序列发生器 | 序列检测器

前言:本章内容主要是演示Vivado下利用Verilog语言进行电路设计、仿真、综合和下载 示例:序列发生器与序列检测器 功能特性: 采用 Xilinx Artix-7 XC7A35T芯片 配置方式:USB-JTAG/SPI Flash 高达100MHz 的内部时钟速度 存储器…...

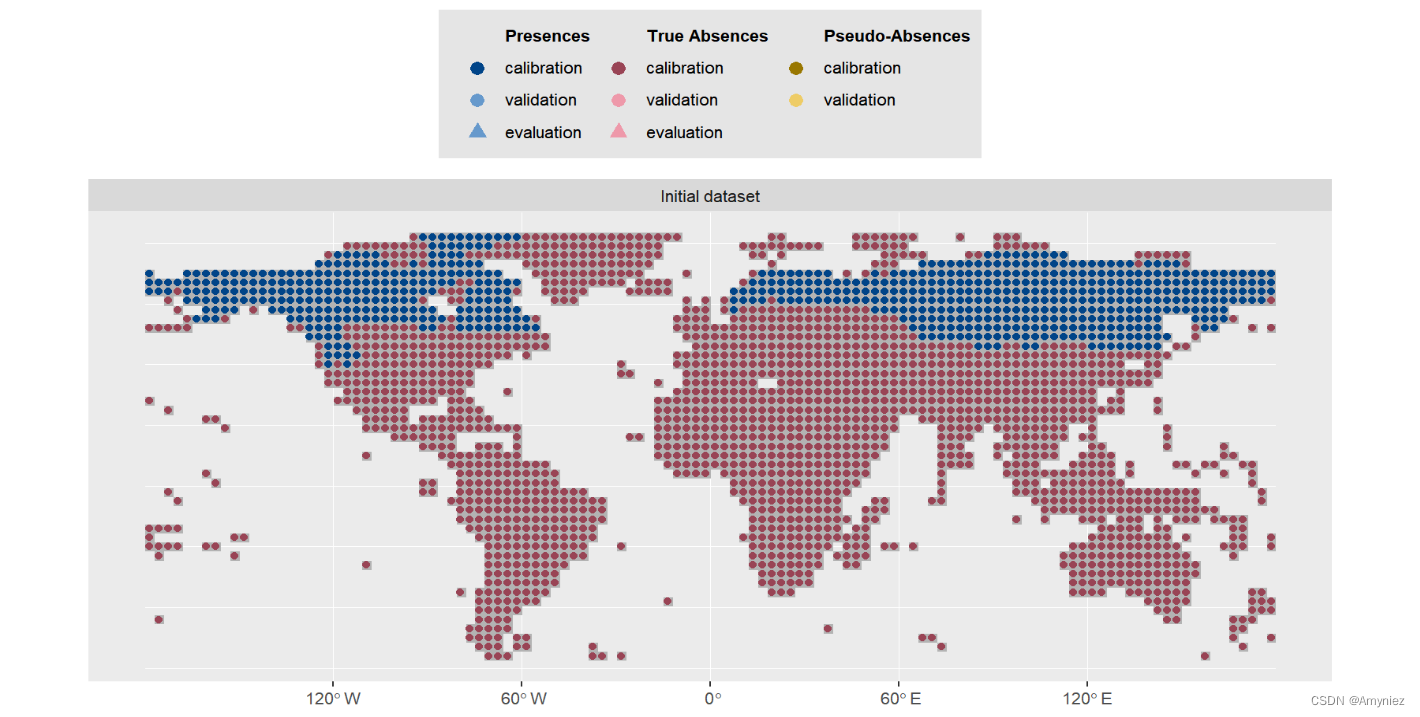

Biomod2 (下):物种分布模型建模

这里写目录标题1.给出一个线性回归模型并求出因子贡献度2.biomod22.1 pseudo-absences:伪不存在点(PA)2.1.1 random2.2.2 disk2.2.3 user.defined method3.使用网格划分区域3.1 计算质心4. 完整案例1.给出一个线性回归模型并求出因子贡献度 ##---------…...

Linux性能学习(2.2):内存_进程线程内存分配机制探究

文章目录1 进程内存分配探究1.1 代码1.2 试验过程2 线程内存分配探究2.1 代码2.2 试验过程3 总结参考资料:1. 嵌入式软件开发杂谈(3):Linux下内存与虚拟内存2. 嵌入式软件开发杂谈(1):Linux下最…...

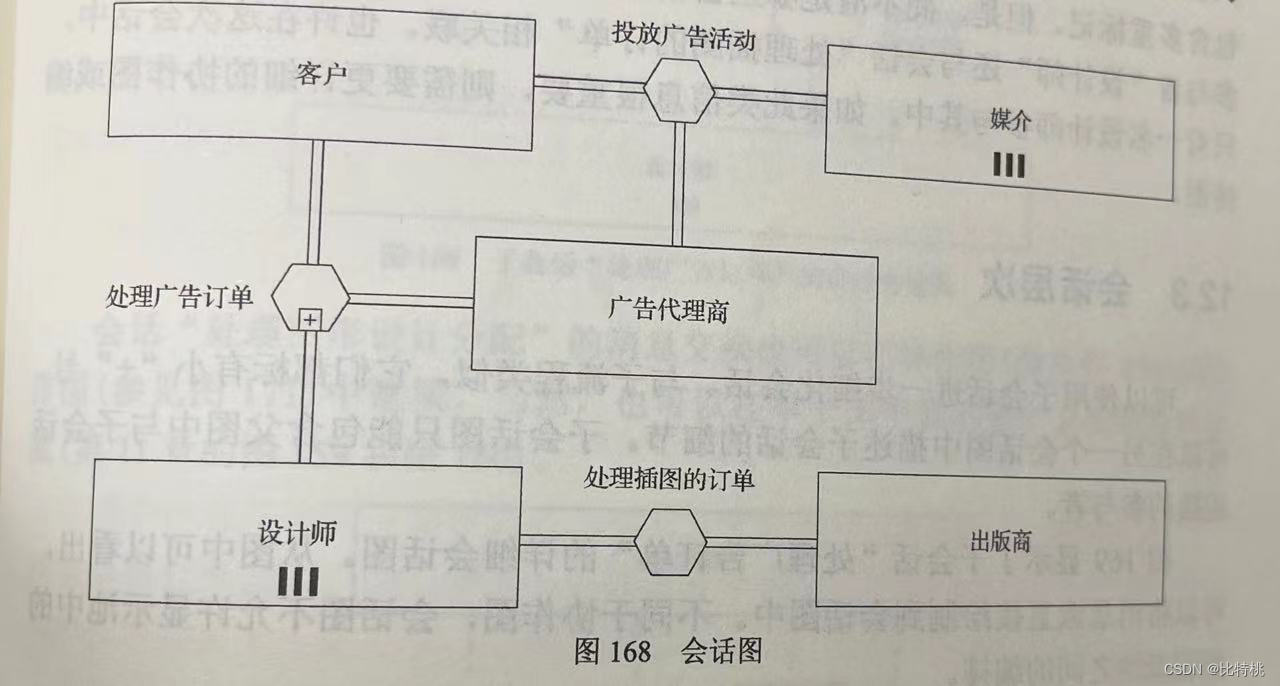

BPMN2.0规范及流程引擎选型方案

BPMN2.0规范及流程引擎选型方案一、基本概念二、BPMN意义三、主要元素3.1 活动任务子流程调用活动事件子流程事务3.2 网关排他网关包容网关并行网关事件网关3.3 事件开始事件结束事件中间事件3.4 辅助泳道图注释与组数据存储四、图类型4.1 编排图4.2 会话图五、技术选型5.1 前端…...

VMware虚拟机安装Linux教程

前言 本文小新为大家带来 VMware虚拟机安装Linux教程 ,后边将为大家分享Linux系统的相关知识与操作,在此之前的第一步我们需要在我们的电脑上搭建好一个Linux系统的环境,本文的具体内容包括VMware虚拟机软件安装与Linux系统安装~ 不积跬步&a…...

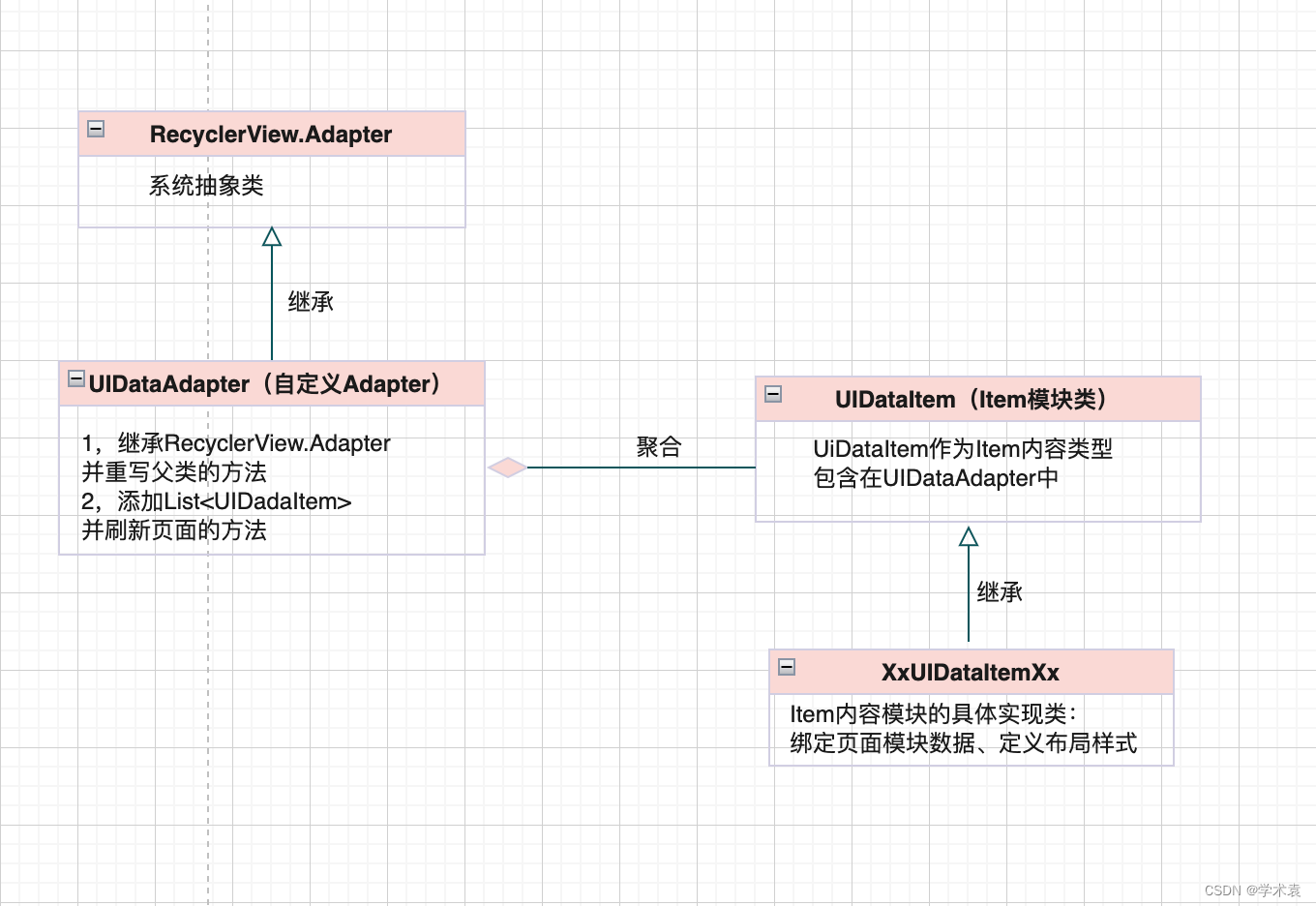

多人协作|RecyclerView列表模块新架构设计

多人协作|RecyclerView列表模块新架构设计多人协作设计图新架构设计与实现设计背景与新需求新架构设计多人协作设计图 根据产品设计,将首页列表即将展示内容区域,以模块划分成多个。令团队开发成员分别承接不同模块进行开发,且互不影响任务开…...

整合配置文件 @Value、ConfigurationProperties)

SpringBoot (六) 整合配置文件 @Value、ConfigurationProperties

哈喽,大家好,我是有勇气的牛排(全网同名)🐮🐮🐮 有问题的小伙伴欢迎在文末评论,点赞、收藏是对我最大的支持!!!。 1 使用 Value 注解 /** Auth…...

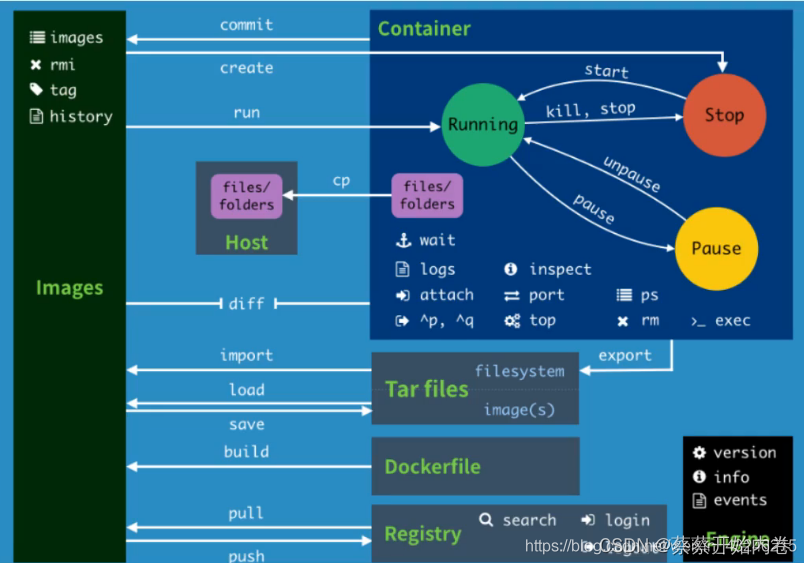

docker 入门篇

docker为什么会出现? 一款产品:开发---->运维,两套环境!应用环境,应用配置! 常见问题:我的电脑可以运行,版本更新,导致服务不可用。 环境配置十分的麻烦,…...

MapReduce的shuffle过程详解

shuffle流程概括 因为频繁的磁盘I/O操作会严重的降低效率,因此“中间结果”不会立马写入磁盘,而是优先存储到Map节点的“环形内存缓冲区”,在写入的过程中进行分区(partition),也就是对于每个键值对来说&a…...

【软件使用】MarkText下载安装与汉化设置 (markdown快捷键收藏)

一、安装与汉化 对版本没要求的可以直接选择 3、免安装的汉化包 1、下载安装MarkText MaxText win64 https://github.com/marktext/marktext/releases/download/v0.17.1/marktext-setup.exe 使用迅雷可以快速下载 2. 配置中文语言包 中文包下载地址:GitHub - chi…...

LeetCode笔记:Biweekly Contest 99

LeetCode笔记:Biweekly Contest 99 1. 题目一 1. 解题思路2. 代码实现 2. 题目二 1. 解题思路2. 代码实现 3. 题目三 1. 解题思路2. 代码实现 4. 题目四 1. 解题思路2. 代码实现 比赛链接:https://leetcode.com/contest/biweekly-contest-99 1. 题目一…...

初探富文本之CRDT协同实例

初探富文本之CRDT协同实例 在前边初探富文本之CRDT协同算法一文中我们探讨了为什么需要协同、分布式的最终一致性理论、偏序集与半格的概念、为什么需要有偏序关系、如何通过数据结构避免冲突、分布式系统如何进行同步调度等等,这些属于完成协同所需要了解的基础知…...

团队死气沉沉?10种玩法激活你的项目团队拥有超强凝聚力

作为项目经理和PMO,以及管理者最头疼的是团队的氛围和凝聚力,经常会发现团队死气沉沉,默不作声,你想尽办法也不能激活团队,也很难凝聚团队。这样的项目团队你很难带领大家去打胜仗,攻克堡垒。但是如何才能避…...

Spring三级缓存核心思想

spring在启动时候,会创建bean,并给bean填充属性,这事会使用到三级缓存 private final Map<String, Object> singletonObjects new ConcurrentHashMap<>(256); //一级缓存private final Map<String, Object> earlySingleto…...

深度学习算法训练和部署流程介绍--让初学者一篇文章彻底理解算法训练和部署流程

目录 1 什么是深度学习算法 2 算法训练 2.1 训练的原理 2.2 名词解释 3 算法C部署 3.1 嵌入式终端板子部署 3.3.1 tpu npu推理 3.3.2 cpu推理 3.2 服务器部署 3.2.1 智能推理 3.2.2 CPU推理 1 什么是深度学习算法 这里不去写复杂的概念,就用通俗的话说…...

计算机网络整理

TCP与UDP 介绍 HTTP:(HyperText Transport Protocol)是超文本传输协议的缩写,它用于传送WWW方式的数据,关于HTTP协议的详细内容请参考RFC2616。HTTP协议采用了请求/响应模型。 TCP:(Transmission Contro…...

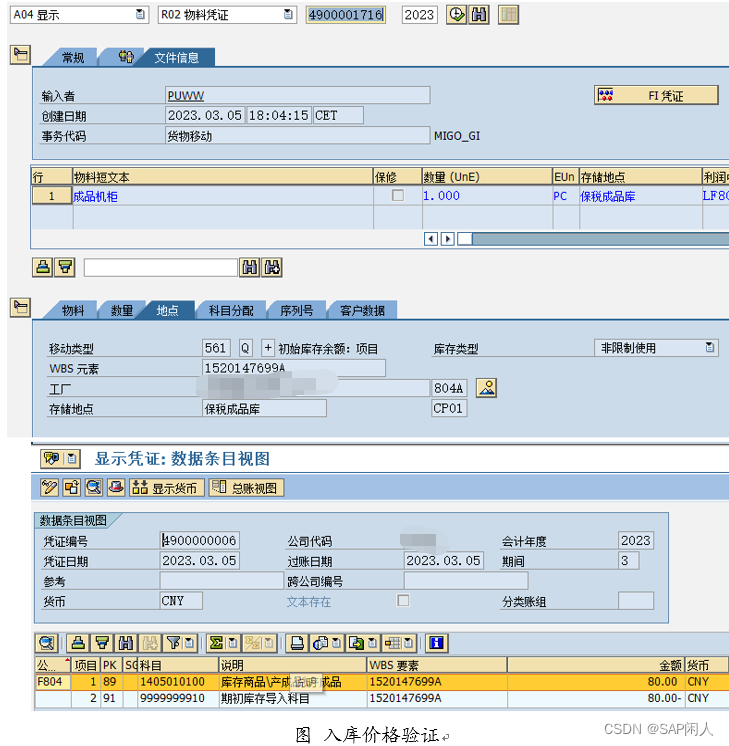

闲人闲谈PS之三十八——混合制生产下WBS-BOM价格发布增强

惯例闲话:最近中《三体》的毒很深,可能是电视剧版确实给闲人这种原著粉带来太多的感动,又一次引发了怀旧的热潮,《我的三体-罗辑传》是每天睡前必刷的视频,结尾BGM太燃了。闲人对其中一句台词感触很深——人类不感谢罗…...

Java 根类 Object

java.lang.Object 是 Java 类层次结构中的根类,所有类都直接或间接实现了此类的方法。 Object API 源码 package java.lang;public class Object {private static native void registerNatives();static {registerNatives();}public final native Class<?>…...

04_Apache Pulsar的可视化监控管理、Apache Pulsar的可视化监控部署

1.4.Apache Pulsar的可视化监控管理 1.4.1.Apache Pulsar的可视化监控部署 1.4.Apache Pulsar的可视化监控管理 1.4.1.Apache Pulsar的可视化监控部署 第一步:下载Pulsar-Manager https://archive.apache.org/dist/pulsar/pulsar-manager/pulsar-manager-0.2.0/…...

【算法】期末复盘,酒店住宿问题——勿向思想僵化前进

文章目录前言题目描述卡在哪里代码(C)前言 省流:一个人也可以住双人间,如果便宜的话。 害!尚正值青春年华,黄金岁月,小脑瓜子就已经不灵光咯。好在我在考试的最后一分钟还是成功通过了这题&am…...

段落自己改 vs 全文工具降:论文AI率哪种降得更彻底

段落自己改 vs 全文工具降:论文AI率哪种降得更彻底 降AI率的时候,很多人的直觉是"哪段被标红就改哪段"——这个思路乍一看很合理,精准处理、不动其他内容。 但实际操作下来,分段改写往往结果很差。 来说说为什么&…...

为什么99%的视频系统都是假的?——没有空间数据的视频,只是一个会动的PPT

一、开头:你看到的“监控”,其实什么都没看见你有没有这种感觉:城市里到处都是摄像头 监控系统越来越多 画面越来越清晰(甚至4K、8K)但一旦真的发生事情:👉 找不到人 👉 跟不上路径 …...

HeyGem数字人视频生成系统批量版:快速部署与使用,新手入门全攻略

HeyGem数字人视频生成系统批量版:快速部署与使用,新手入门全攻略 1. 系统概述与核心价值 HeyGem数字人视频生成系统批量版是一款基于AI技术的智能视频合成工具,能够将音频与视频素材智能结合,生成口型同步的数字人视频。科哥的二…...

MAVROS无人机Offboard模式实战:从代码解析到自主飞行

1. 从零理解MAVROS与Offboard模式 第一次接触无人机编程时,我被各种专业术语搞得晕头转向。直到亲手用MAVROS控制无人机完成第一个Offboard飞行,才真正理解这套系统的精妙之处。简单来说,MAVROS就像无人机世界的"翻译官"——它把RO…...

)

Spring AI聊天记录丢了怎么办?手把手教你用Redis实现ChatMemory持久化(附完整代码)

Spring AI聊天记录持久化实战:Redis解决方案与工程实践 在构建智能对话系统时,聊天记录的持久化是一个经常被忽视却至关重要的环节。想象一下这样的场景:用户昨天与你的客服机器人进行了长达30分钟的咨询,今天再次访问时却发现系统…...

WarcraftHelper:魔兽争霸3兼容性救星,让经典游戏在现代电脑上重生!

WarcraftHelper:魔兽争霸3兼容性救星,让经典游戏在现代电脑上重生! 【免费下载链接】WarcraftHelper Warcraft III Helper , support 1.20e, 1.24e, 1.26a, 1.27a, 1.27b 项目地址: https://gitcode.com/gh_mirrors/wa/WarcraftHelper …...

Unity URP描边效果终极指南:5分钟实现专业级游戏轮廓的完整教程

Unity URP描边效果终极指南:5分钟实现专业级游戏轮廓的完整教程 【免费下载链接】Unity-URP-Outlines A custom renderer feature for screen space outlines 项目地址: https://gitcode.com/gh_mirrors/un/Unity-URP-Outlines 你是否曾经为游戏角色在复杂场…...

OpenCore配置效率工具:从入门到精通的黑苹果EFI管理方案

OpenCore配置效率工具:从入门到精通的黑苹果EFI管理方案 【免费下载链接】OCAuxiliaryTools Cross-platform GUI management tools for OpenCore(OCAT) 项目地址: https://gitcode.com/gh_mirrors/oc/OCAuxiliaryTools 在黑苹果配置领…...

5分钟Mac本地跑通32B Qwen!免费GPT-4o替代,还能5分钟造个会开浏览器+执行Shell的AI Agent

1. 硬件与模型选择 配置:Apple M2 Pro(19 核 GPU)、32GB 统一内存。 推荐模型:mlx-community/Qwen2.5-Coder-32B-Instruct-4bit 4bit 量化后只占 18-22GB 内存专为代码和 Agent 优化,Tool Calling 能力强MLX 原生支持…...

Windows环境下Dlib库安装完全指南:从报错到成功的实战手册

Windows环境下Dlib库安装完全指南:从报错到成功的实战手册 【免费下载链接】Dlib_Windows_Python3.x Dlib compiled binaries (.whl) for Python 3.7-3.14 and Windows x64 项目地址: https://gitcode.com/gh_mirrors/dl/Dlib_Windows_Python3.x 问题定位&am…...