FPGA的配置状态字寄存器Status Register

目录

简介

状态字定义

Unknown Device/Many Unknow Devices

解决办法

一般原因

简介

Xilinx的FPGA有多种配置接口,如SPI,BPI,SeletMAP,Serial,JTAG等;如果从时钟发送者的角度分,还可以分为主动Master(即由FPGA自己发送配置时钟信号CCLK)和被动Slave(即由外部器件提供配置所需要的时钟信号);另外还可由板上稳定晶振提供时钟信号,经由FPGA的EMCCLK接口,再从CCLK端口送出。

如此多的配置形式,一旦发生配置失败怎么办?大家都知道先要查看一下板子上FPGA的DONE管脚。但绝大多数情况下,DONE管脚此时会是低电平,只能证明配置确实失败了。但是失败的原因到底是什么呢?调试到底应该如何入手呢?

FPGA的状态字寄存器Status Register能直接告诉你或者极大地辅助判断失败的原因,Xilinx FPGA的状态字,在赛灵思所有器件系列中都基本保持一致的定义(个别位由于系列特性不同可能有细微区别,这些不是最重要的,不在我们今天讨论的范围内)。

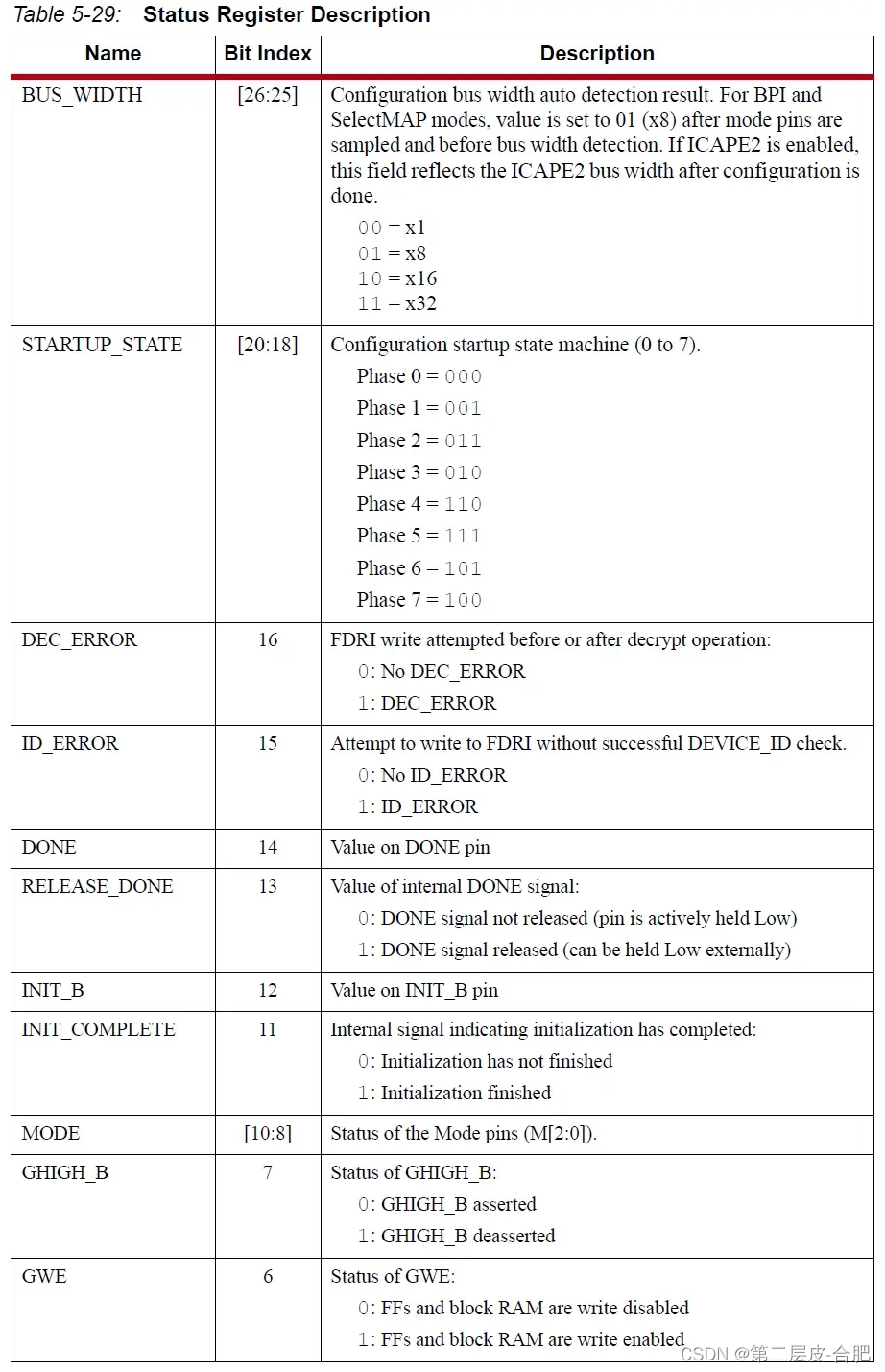

状态字定义

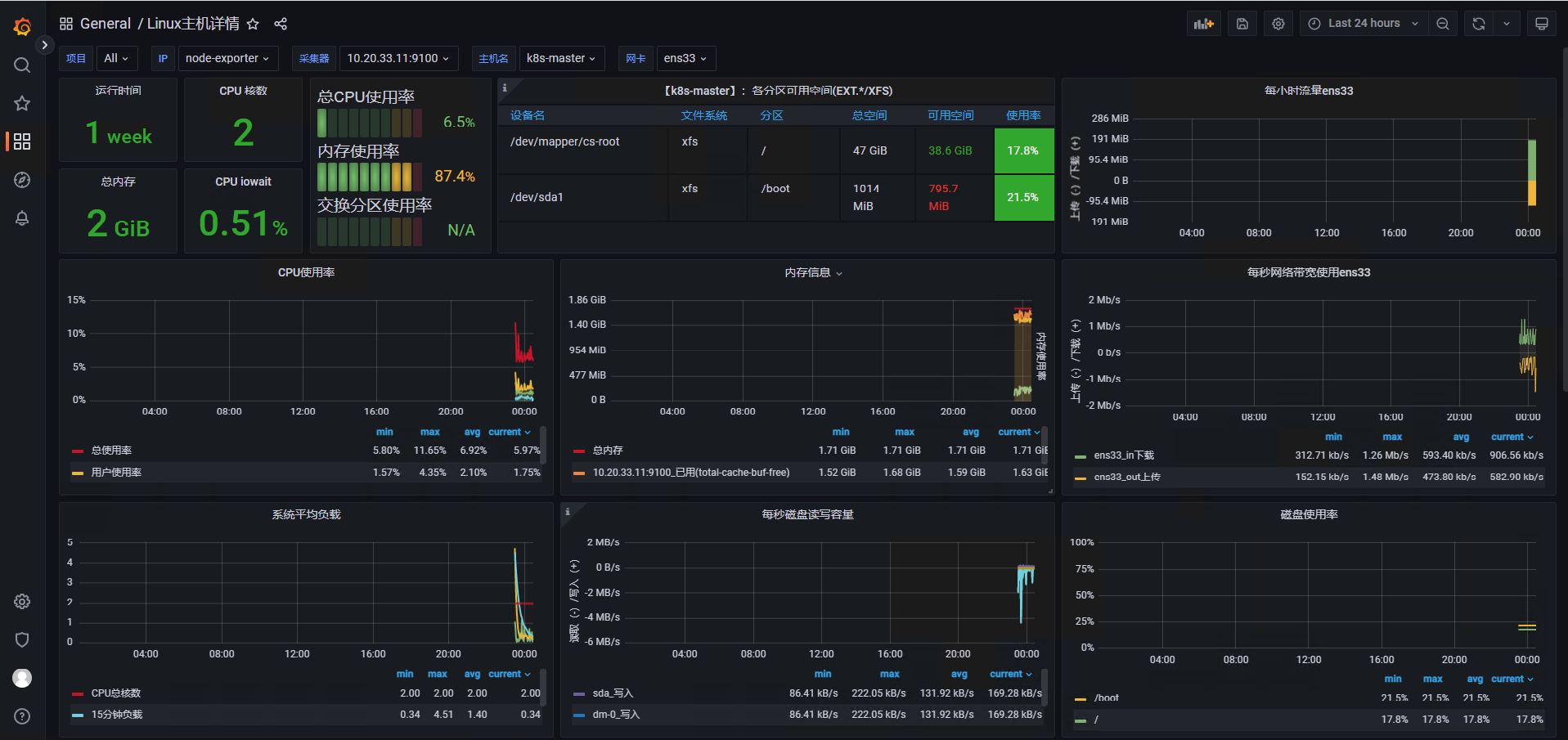

以7系列 FPGA为例,我们看看UG470上对状态字的完整定义:

首先,用下载线连接好板子和电脑,板子上好电。打开Vivado硬件管理器,扫描板子上的JTAG链 (Open target -AutoConnect), 板子上的JTAG链中的器件会显示在Hardware窗口中:

鼠标选中扫描出的FPGA器件,在下方的Hardware Device Properties窗口中,选择Properties项,会出现该FPGA的一系列属性。找到其中的REGISTER分类,展开,第二个寄存器CONFIG_STATUS, 即是我们要讨论的状态字了。

这里可以看到的是一个配置前的状态字的标准状态:

只有BIT02 PLL_LOCK, BIT03 DCI_MATCH, BIT11 INIT_B_INTERNAL, BIT12 INIT_B_PIN的值必须是1;

BIT08-10 MODE PINS,BIT21 SECURITY_STATUS, BIT25-26 BUS_WIDTH,BIT28 PUDC_B根据FPGA和板子具体的设定,可以为1或者0,其他都必须是0。

如果一上电,状态字就表现出了非典型值,那么大概率硬件上就有错误或者不合理的地方了。比较典型的几个例子:

1. 状态字全0

REGISTER.CONFIG_STATUS 00000000000000000000000000000000

这种情况,说明FPGA被强行控制在全局复位状态了。一般是硬件上PROGRAM_B管脚,或者INIT_B管脚被错误的拉到了地上,两个管脚上的有效电平为0.

非常偶尔的情况下,当DONE管脚被错误拉为0电平时也能出现此种状态字。

2. 状态字全1,或者一串1后面跟着一个到数个0(一般不超过4个)

REGISTER.CONFIG_STATUS 11111111111111111111111111111111

REGISTER.CONFIG_STATUS 11111111111111111111111111111110

REGISTER.CONFIG_STATUS 11111111111111111111111111111100

这种一般是板子上设计的JTAG链里面不只一个FPGA器件,比如是Xilinx的FPGA和一个第三方的CPLD串联等。

由于Vivado里面并没有第三方器件的BSDL文件,那么在扫描整个JTAG链时,它无法识别链中各器件的型号以及数目,所以往往从TDO管脚中移位出一串1来。如果Xilinx的FPGA位于链的末端(接近TDO的位置),那么有时可以识别出正确的FPGA型号。但是这种情况仍然无法正确进行将要进行的配置操作。另外很多例子中则是FPGA的型号也被识别错误了。

解决方案如下:

https://www.xilinx.com/support/answers/61312.html

Unknown Device/Many Unknow Devices

此时,不要说状态字无法检测了,整个JTAG已经无法正确扫描,Vivado里面无法识别出任何器件。这一般是板子上的JTAG接口的TDO或者链中最后一个器件的输出管脚TDO,被短接到了地平面上。

除了上述典型情况,当然还有很多一上电就无法继续配置的情况,原因不胜枚举。这种情况下请详细描述你的JTAG链构成,读出当前的状体字(如何还能够读的话),如果状态字正常,可以接下来进行配置操作。或者是在你的配置失败后,保留失败现场再连接好板子和电脑继续读出状态字。

如果你的板子已经重新上下电了,那么当时失败的场景也就消失了。这也就是我们一再强调失败后要保留现场,板子上要保留JTAG接口的原因。当然在设计成熟后,或者实验室调试工作结束后,可以去掉JTAG接口以期得到产品更高的安全性。

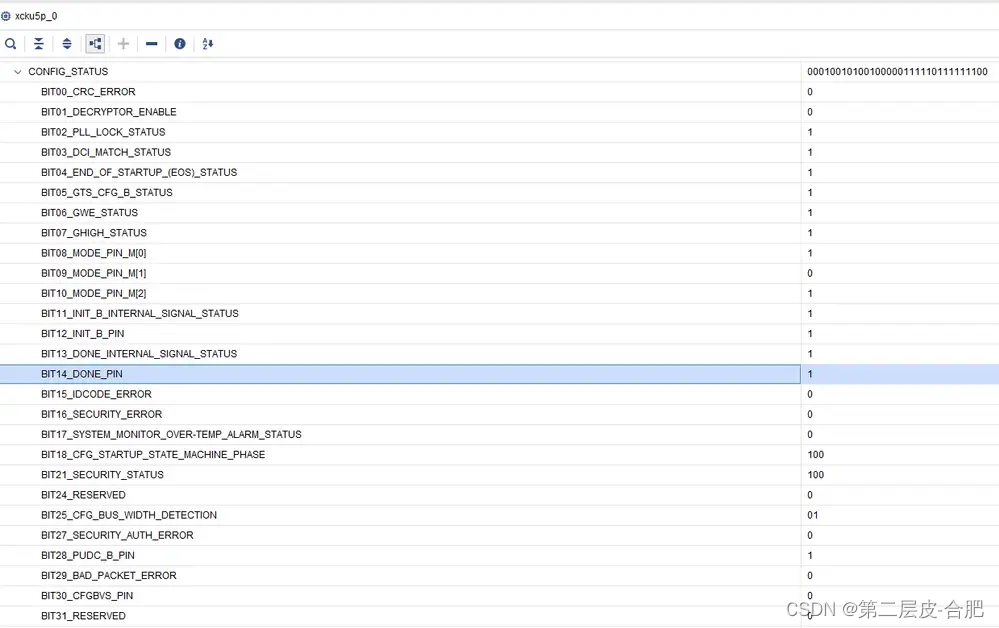

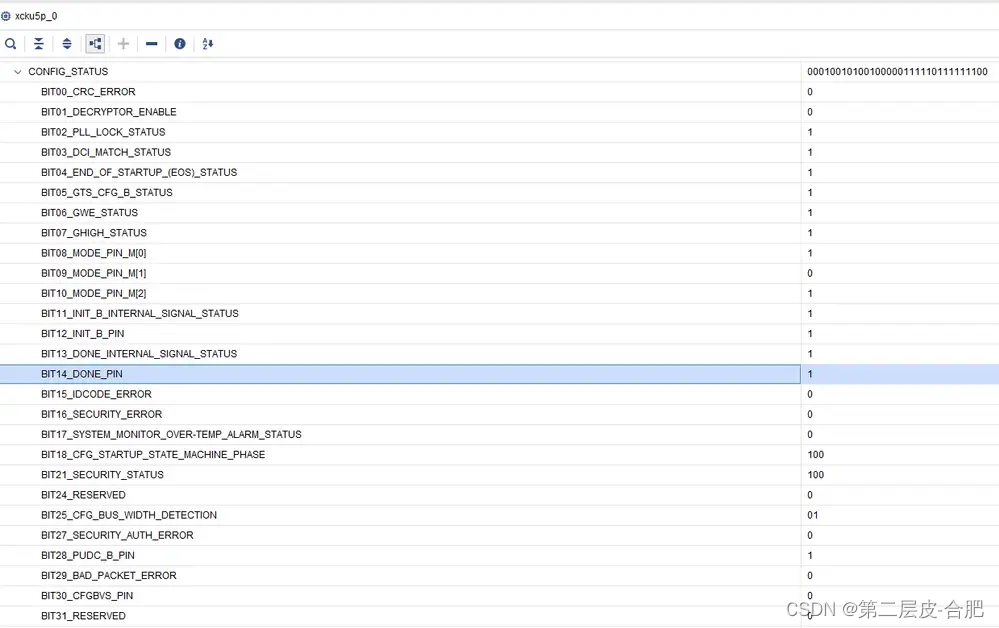

配置完成后,得到的状态字如下:

REGISTER.CONFIG_STATUS 00010010100100000111110111111100

注意其中的:

BIT02 PLL_LOCK, BIT03 DCI_MATCH, 绝大多数情况已经变为1;

BIT04 EOS,BIT05 GTS, BIT06 GWE, BIT07 GHITH,以及BIT11 INIT_BINTERNAL, BIT12 INIT_B_PIN,BIT13 DONE_INTERNAL, BIT14 DONE_PIN必然是1;

BIT18-20 STARTUP_STATTE应该是100;

BIT25-26 BUS_WIDTH应该是检测出了正确的配置位宽,或者在serial的情况下,保持默认的01值;

其他BIT01 DECRYPTOR, BIT09-10 MODE_PINS, BIT21-23 SECURITY_STATUS, BIT28 PUDC_B, BIT30CFGBVS_PIN, 根据你的使用,有可能是其他的0或者1组合。

RESERVED的不用管。

如果不是这种结果,那么就要看看出什么问题了。

在一些相对简单,典型的情况下,只看某一位就可以直接得到想要的答案。

BIT00的CRC error为1

在不是状态字全1的情况下CRC error位为1,说明配置出现了CRC错误。这是一种很常见,但比较难修复的错误,因为CRC错误的原因一般是因为板子上的信号质量(SI, Signal Integrity)不行,传输数据的过程中0/1电平判决错误,导致配置数据写入失败。

如何确定真的是SI问题呢?看失败概率。CRC错误一般是随机出错的,并不一定100%失败(除非板子的信号差得没法用了,这个一般不会)。那么配置文件中01翻转的次数越少,出错的概率越小。你可以生成一个只点亮板上一盏LED的小测试设计,此时bit文件中有效数据(1)非常少,试着下载该bit看看,是不是配置失败率降低了?如果是,那么基本可以确定了。

解决办法

一旦出现这种情况,可以尝试的办法有:

1. 降低CCLK频率

2. 在CCLK的输入端(以及输出端),加入合适的端接电路

3. 换用更高质量的配置时钟(比如使用质量较好的晶振通过EMCCLK提供时钟)

4. 改善数据链路的信号质量,如果对待CCLK,同样在数据通路上加入合适的端接匹配电路。

总而言之,要做的就是改善板上的信号质量。如果板子SI实在太差,那只有改板,或者尝试下其他配置方式了。

其他位都正常,BIT13 DONE_INTERNAL也为1了,但是BIT14 DONE_PIN为0,FPGA不工作!

这种情况,其实配置数据已经完整、正确的送入FPGA并且被接收了,但是FPGA的DONE管脚连接不正确,导致DONE没有或者没有在规定时间内上拉到要求的电平,从而导致FPGA最终的启动失败。

Xilinx的FPGA,一般要求DONE管脚上外加一个上拉电阻(330欧, 4.7K欧等,不同系列要求不同,请参照对应的Configuration User Guide)。如果这个上拉电阻没有加,或者加的阻值过大或过小,那么DONE管脚无法在规定的时间里面达到高电平,此时内部配置控制器会认为配置失败了,典型情况就是DONE internal为高(内部数据接收完毕,内部释放了),但是DONE外部管脚为低。

此时需要做的,就是检查PCB上DONE部分的设计,看看是不是有和其他管脚相连的情况,被其他管脚强行拉低了。或者是设计的DONE点亮LED灯电路不合理, LED通电后把DONE管脚的电平降为低电平。

如果你不清楚如何设计这部分电路,从 www.xilinx.com 上,找到一款和你使用的FPGA型号相同或者同系列的开发板,参考它的原理图设计。

BIT29 BAD PACKET error

Bit29为1,大概率也是CRC错误。这不过这个CRC错误比较特殊,出错位跑到了配置文件里面的命令上,导致配置命令变成了一个无效无意义的指令。此时状态字会报出bad packet error。

和CRC错误的随机性一样,多次重复加载过程,大概率出错的数据位下次落到其他的数据上。由于配置数据的数量远远大于配置命令,那么很有可能下次出错看到的是BIT00 CRC ERROR为1.

如果每次都是BAD PACKET error,更要怀疑使用的配置文件已经损坏。比如进行了非法改写。Xilinx的任何配置文件,都是禁止手工修改的。

BIT15 IDCODE Error为1

配置文件下载时,都要先经过FPGA的IDCODE校验。如果这一步通不过,那么后续的配置不会进行。这种情况下,看看配置文件的bit/bin/mcs是不是给错了。或者FPGA器件有silicon revision的变化。举个例子,有的系列ES芯片和Production芯片的配置文件是不能兼容的。这种错误情况,如果是用JTAG通过Vivado下载,那么log里面也会有相应的提示。

BIT13 DONE_INTERNAL+ BIT14 DONE_PIN均为0

这也是一种较常见的错误。此时要重点检查一下BIT07 GHIGH位,看看它是不是1。如果是,那么大概率是,你的CCLK时钟给的不够多。FPGA在接收完所有的配置数据后,还需要一定数量的CCLK时钟去完成内部的初始化。如果发送端,此时常常是一个CPU用Slave模式加载,认为有效数据结束,强行停止了进一步的时钟发送,那么有时可以观测到此种状况。此时去检查BIT18-20 STARTUP_STATE,根据具体的情况,也有一定概率看到不是预期的100.

标准的做法是,在默认设置下持续发送CCLK时钟,直至检测到DONE管脚已经拉高,然后再多发送至少64个时钟信号。如果修改了配置默认设置,比如选择了wait for PLL to lock,那么需要更多的时钟信号。

状态字看起来和没有发出配置数据,即和刚上电的表现一样。

这种情况,说明所有发出的配置数据都被FPGA忽略掉了,因为它不认为你发送过来的是有效配置数据。

FPGA的配置文件里面,有一个数据同步头,一般是AA 99 55 66。如果由于某种原因,这个同步头FPGA都没有认出来,那么后续的数据会被它全部忽略。

一般原因

1. 在非serial配置模式中,没有正确的做Byte Swap;

2. 配置文件生成时,BPI数据线宽设置不对(x8, x16, x32选错了)

3. SPI的x1, x2, x4选择错误;

4. 严重的板级SI问题导致的CRC错误;

以上列举了常见的一些配置错误和其状态字的相应表现。需要注意的是,状态字寄存器有32位,其组合可以说是相当多的。除了上述情况,配置失败定位还可能需要结合状态字,加载过程中log文件,硬件设计原理图和工具版本信息,以及通过其他一些配置接口在不同条件下去对比测试才能逐步定位。 作者:硬件光阴 https://www.bilibili.com/read/cv26835920/?spm_id_from=333.999.0.0 出处:bilibili

相关文章:

FPGA的配置状态字寄存器Status Register

目录 简介 状态字定义 Unknown Device/Many Unknow Devices 解决办法 一般原因 简介 Xilinx的FPGA有多种配置接口,如SPI,BPI,SeletMAP,Serial,JTAG等;如果从时钟发送者的角度分,还可以…...

【HarmonyOS Arkts笔记】http网络请求封装

common.ts export default class CommonConstant {/*** The host address of the server.*/static readonly SERVER: string 请求接口地址;/*** The request success code.*/static readonly SUCCESS_CODE: number 200;/*** Read timeout.*/static readonly READ_TIMEOUT: n…...

html前端的几种加密/解密方式

HTML前端的加密解密方式有以下几种: 一、base64加密 Base64编码:Base64是一种将二进制数据转换为可打印字符的编码方式。在前端,可以使用JavaScript的btoa()函数进行Base64编码,使用atob()函数进行解码。 var str "hello…...

算法学习01:排序二分

算法学习01:排序&&二分 文章目录 算法学习01:排序&&二分前言需要记忆的模版:快速排序归并排序:整数二分:浮点数二分 一、排序1.快速排序2.归并排序: 二、二分1.整数2.浮点数 总结 前言 需要…...

OpenAI (ChatGPT)中国免费试用地址

GitHub - click33/chatgpt---mirror-station-summary: 汇总所有 chatgpt 镜像站,免费、付费、多模态、国内外大模型汇总等等 持续更新中…… 个人能力有限,搜集到的不多,求大家多多贡献啊!众人拾柴火焰高!汇总所有 cha…...

IOS面试题object-c 11-20

11、解释self [super init]方法? 容错处理, 当父类初始化失败,会返回一个nil, 表示初始化失败。 由于继承的关系, 子类是需要拥有父类的实例和行为, 因此, 我们必须先初始化父类,然后再初始化子类 12、简述使用block有什么优点?代码紧凑,传值…...

方法(算法公式))

北斗导航 | 十四种抗差稳健估计(抗差M估计)方法(算法公式)

===================================================== github:https://github.com/MichaelBeechan CSDN:https://blog.csdn.net/u011344545 ===================================================== 稳健估计(M估计) 1、Huber法2、残差绝对和最小法3、L1-L2法...

【JavaEE】_Spring MVC项目使用数组与集合传参

目录 1. 使用数组传参 1.2 传递单个参数 1.3 传递多个名称相同的参数 1.3.1 关于urlencode 2. 使用集合传参 1. 使用数组传参 创建一个Spring MVC项目,其中 .java文件内容如下: package com.example.demo.controller;import com.example.demo.Per…...

Centos 9 安装 k8s

为了尽可能契合生产环境的部署情况,这里用kubeadm安装集群,同时方便跟随笔记一步步实践的过程,也更加了解k8s的一些特性和基础知识。 先决条件 这里将通过虚拟机安装3台centos stream 9服务器,并组成kubeneters集群(…...

WiFi模块助力少儿编程:创新学习与实践体验

随着科技的飞速发展,少儿编程已经成为培养孩子们创造力和问题解决能力的重要途径之一。在这个过程中,WiFi模块的应用为少儿编程领域注入了新的活力,使得学习编程不再是单一的代码教学,而是一个充满创新与实践的综合性体验。 物联网…...

最新:Selenium操作已经打开的Chrome(免登录)

最近重新尝试了一下,之前写的博客内容。重新捋了一下思路。 目的就是,selenium在需要登录的网站面前,可能就显得有些乏力,因此是不是有一种东西,可以操作它打开我们之前打开过的网站,这样就不用登录了。 …...

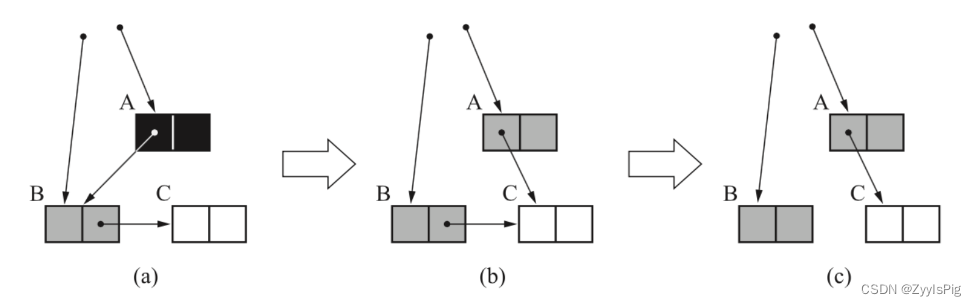

三色标记过程

可达性分析 GC过程中需要对对象图遍历做可达性分析。使用了三色标记法进行分析。 什么三色? 白色:尚未访问过。 黑色:本对象已访问过,而且本对象 引用到 的其他对象 也全部访问过了。 灰色:本对象已访问过࿰…...

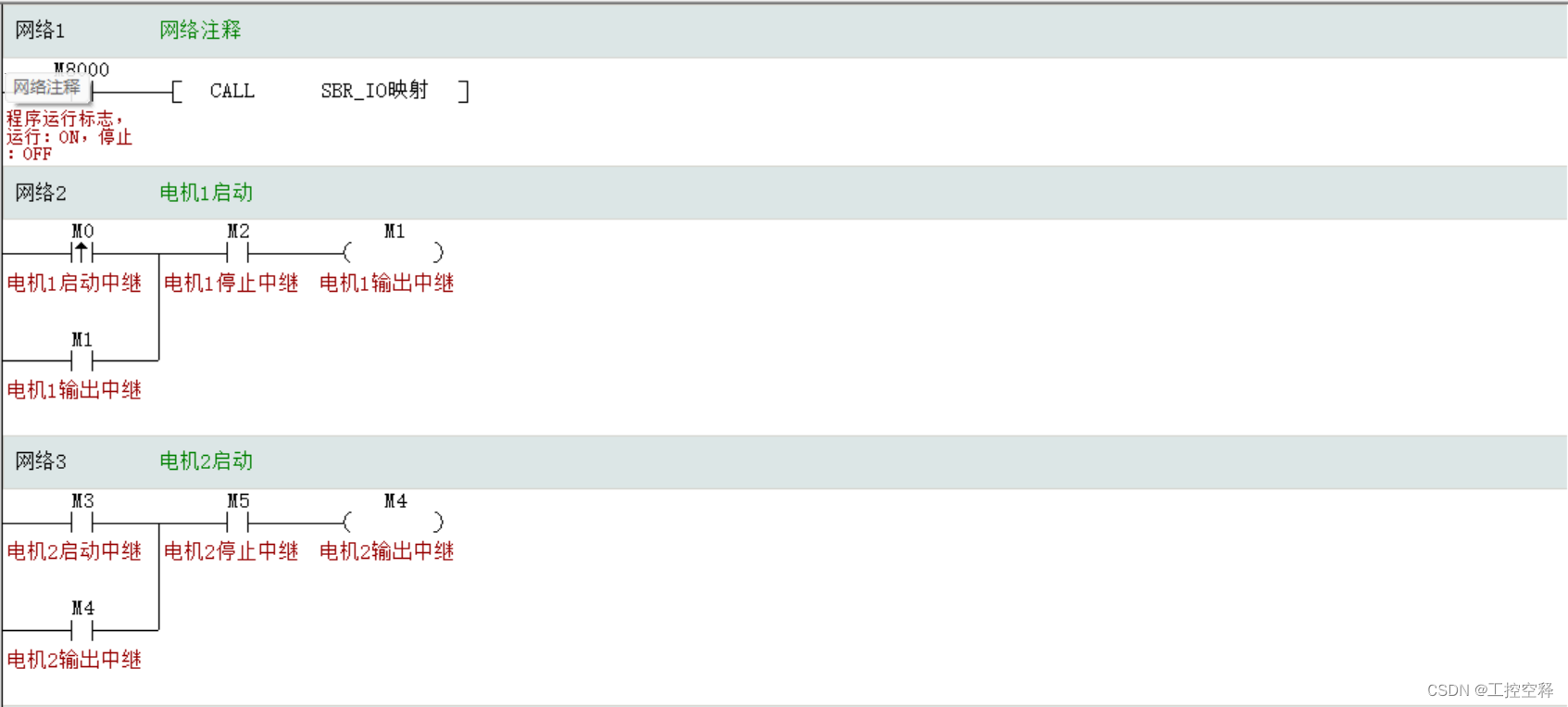

记录汇川:IO隔离编程

IO隔离:方便程序修改 无论是输入点坏了还是输出点坏了,或者人为接错线,或者对调点,我们只需要更改IO隔离得输入输出就可以了。方便。 停止按钮外接常闭,里面也使用常闭,为了断线检测功能(安全)ÿ…...

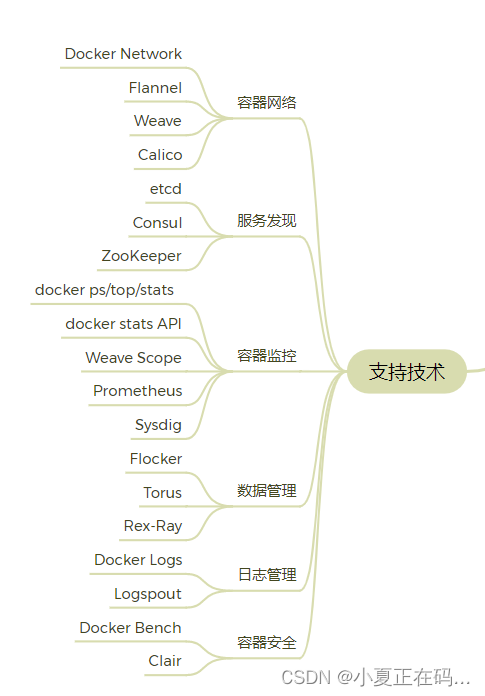

【Docker】容器的生态系统

Docker提供了一整套技术支持,包括核心技术、平台技术、支持技术。 核心技术 容器核心技术是指能让Container(容器)在host(集群、主机)上运行起来的那些技术。 1)容器规范:OCI(runt…...

AVL树讲解

AVL树 1. 概念2. AVL节点的定义3. AVL树插入3.1 旋转 4.AVL树的验证 1. 概念 AVL树是一种自平衡二叉搜索树。它的每个节点的左子树和右子树的高度差(平衡因子,我们这里按右子树高度减左子树高度)的绝对值不超过1。AVL的左子树和右子树都是AV…...

20240308-1-校招前端面试常见问题CSS

校招前端面试常见问题【3】——CSS 1、盒模型 Q:请简述一下 CSS 盒模型? W3C 模式:盒子宽widthpaddingbordermargin 怪异模式:盒子宽widthmargin Q:inline、block、inline-block 元素的区别? inline&am…...

linux系统简述docker

简述docker docker理念docker三要素docker平台架构docker运行的基本流程 docker理念 一次镜像,处处运行 基于go语言实现的项目 解决了运行环境和配置问题的软件容器,方便做持续集成并有助于整体发布的容器虚拟化技术 能够使硬件、操作系统和应用程序三者…...

【论文阅读】Mamba:选择状态空间模型的线性时间序列建模(一)

文章目录 Mamba:选择状态空间模型的线性时间序列建模介绍状态序列模型选择性状态空间模型动机:选择作为一种压缩手段用选择性提升SSM 选择性SSM的高效实现先前模型的动机选择扫描总览:硬件感知状态扩展 Mamba论文 Mamba:选择状态空间模型的线性时间序列建…...

漏洞复现-蓝凌LandrayOA系列

蓝凌OA系列 🔪 是否利用过 优先级从高到低 发现日期从近到远 公司团队名_产品名_大版本号_特定小版本号_接口文件名_漏洞类型发现日期.载荷格式LandrayOA_Custom_SSRF_JNDI漏洞 LandrayOA_sysSearchMain_Rce漏洞 LandrayOA_Custom_FileRead漏洞...

计算机网络 路由算法

路由选择协议的核心是路由算法,即需要何种算法来获得路由表中的各个项目。 路由算法的目的很明显,给定一组路由器以及连接路由器的链路,路由算法需要找到一条从源路由器到目的路由器的最佳路径,通常,最佳路径是由最低…...

如何5步掌握B站视频下载?BilibiliDown跨平台解决方案终极指南

如何5步掌握B站视频下载?BilibiliDown跨平台解决方案终极指南 【免费下载链接】BilibiliDown (GUI-多平台支持) B站 哔哩哔哩 视频下载器。支持稍后再看、收藏夹、UP主视频批量下载|Bilibili Video Downloader 😳 项目地址: https://gitcode.com/gh_mi…...

)

PyTorch实战:手把手教你为CT重建任务封装可微分的正反投影模块(附完整代码)

PyTorch实战:构建可微分CT正反投影模块的工程化实践 医疗影像重建领域正经历着深度学习的革命性变革。传统CT重建算法如滤波反投影(FBP)虽然计算高效,但在低剂量或有限角度扫描场景下表现欠佳。本文将带你从零实现一个可直接嵌入神…...

玻璃幕墙建筑节能技术分析及其经济评价

玻璃幕墙建筑节能技术分析及其经济评价 玻璃幕墙(以下简称“幕墙”)是现代化建筑的主要外围护结构之一,其节能已成为我国建筑节能的重要一环。 本文就幕墙的节能进行技术分析、计算,对节能效果进行经济评价。 1 幕墙建筑节能的设计原则本文提出下列措施,作为幕墙建筑节能…...

SQLite4Unity3d终极教程:在Unity中快速集成SQLite数据库的完整指南

SQLite4Unity3d终极教程:在Unity中快速集成SQLite数据库的完整指南 【免费下载链接】SQLite4Unity3d SQLite made easy for Unity3d 项目地址: https://gitcode.com/gh_mirrors/sq/SQLite4Unity3d SQLite4Unity3d是专为Unity开发者设计的强大数据库集成解决方…...

和样本权重(scale_pos_weight)搞定不平衡数据)

XGBoost调参进阶:用特征权重(feature_weights)和样本权重(scale_pos_weight)搞定不平衡数据

XGBoost权重调参实战:用特征与样本双重加权破解不平衡分类难题 金融风控中1%的欺诈交易可能造成99%的损失,广告点击数据里正样本占比往往不足5%。面对这些典型的不平衡分类场景,仅靠调整阈值或过采样难以从根本上解决问题。XGBoost提供的feat…...

5分钟掌握Winhance中文版:Windows系统优化终极指南

5分钟掌握Winhance中文版:Windows系统优化终极指南 【免费下载链接】Winhance-zh_CN A Chinese version of Winhance. C# application designed to optimize and customize your Windows experience. 项目地址: https://gitcode.com/gh_mirrors/wi/Winhance-zh_CN…...

m4s-converter:5分钟快速上手,拯救你的B站缓存视频

m4s-converter:5分钟快速上手,拯救你的B站缓存视频 【免费下载链接】m4s-converter 一个跨平台小工具,将bilibili缓存的m4s格式音视频文件合并成mp4 项目地址: https://gitcode.com/gh_mirrors/m4/m4s-converter 你是否曾经历过这样的…...

LOSEHU固件终极指南:解锁泉盛UV-K5/K6对讲机全部潜能

LOSEHU固件终极指南:解锁泉盛UV-K5/K6对讲机全部潜能 【免费下载链接】uv-k5-firmware-custom 全功能泉盛UV-K5/K6固件 Quansheng UV-K5/K6 Firmware 项目地址: https://gitcode.com/gh_mirrors/uvk5f/uv-k5-firmware-custom 还在为原厂固件的功能限制而烦恼…...

Zotero-SciHub插件:一键获取学术文献的终极解决方案

Zotero-SciHub插件:一键获取学术文献的终极解决方案 【免费下载链接】zotero-scihub A plugin that will automatically download PDFs of zotero items from sci-hub 项目地址: https://gitcode.com/gh_mirrors/zo/zotero-scihub 在学术研究的世界里&#x…...

WebLaTeX:革命性免费在线LaTeX编辑器,3分钟开启高效学术写作

WebLaTeX:革命性免费在线LaTeX编辑器,3分钟开启高效学术写作 【免费下载链接】WebLaTex A complete alternative for Overleaf with VSCode Web Git Integration Copilot Grammar & Spell Checker Live Collaboration Support. Based on GitHub…...