FPGA高端项目:FPGA基于GS2971的SDI视频接收+GTX 8b/10b编解码SFP光口传输,提供2套工程源码和技术支持

目录

- 1、前言

- 免责声明

- 2、相关方案推荐

- 本博已有的 SDI 编解码方案

- 本方案的SDI接收转HDMI输出应用

- 本方案的SDI接收+图像缩放应用

- 本方案的SDI接收+纯verilog图像缩放+纯verilog多路视频拼接应用

- 本方案的SDI接收+HLS图像缩放+Video Mixer多路视频拼接应用

- 本方案的SDI接收+OSD动态字符叠加输出应用

- 本方案的SDI接收+HLS多路视频融合叠加应用

- FPGA的SDI视频编解码项目培训

- 3、详细设计方案

- 设计原理框图

- SDI 相机

- GS2971

- BT1120转RGB

- 视频数据组包

- GTX aurora 8b/10b 详解

- GTX IP 简介

- GTX 基本结构

- GTX 发送和接收处理流程

- GTX 的参考时钟

- GTX 发送接口

- GTX 接收接口

- GTX IP核调用和使用

- 数据对齐

- 视频数据解包

- 图像缓存

- HDMI输出

- 工程源码架构

- 4、工程源码21详解-->SDI接收+GTX 8b/10b编解码 图像缓存至PL端DDR3

- 5、工程源码22详解-->SDI接收+GTX 8b/10b编解码 图像缓存至PS端DDR3

- 6、工程移植说明

- vivado版本不一致处理

- FPGA型号不一致处理

- 其他注意事项

- 7、上板调试验证

- 准备工作

- GTX 8b/10b编解码SFP光口传输-->输出视频演示

- 8、福利:工程代码的获取

FPGA高端项目:FPGA基于GS2971的SDI视频接收+GTX 8b/10b编解码SFP光口传输,提供2套工程源码和技术支持

1、前言

目前FPGA实现SDI视频编解码有两种方案:一是使用专用编解码芯片,比如典型的接收器GS2971,发送器GS2972,优点是简单,比如GS2971接收器直接将SDI解码为并行的YCrCb422,GS2972发送器直接将并行的YCrCb422编码为SDI视频,缺点是成本较高,可以百度一下GS2971和GS2972的价格;另一种方案是使用FPGA逻辑资源部实现SDI编解码,利用Xilinx系列FPGA的GTP/GTX资源实现解串,利用Xilinx系列FPGA的SMPTE SDI资源实现SDI编解码,优点是合理利用了FPGA资源,GTP/GTX资源不用白不用,缺点是操作难度大一些,对FPGA开发者的技术水平要求较高。有意思的是,这两种方案在本博这里都有对应的解决方案,包括硬件的FPGA开发板、工程源码等等。

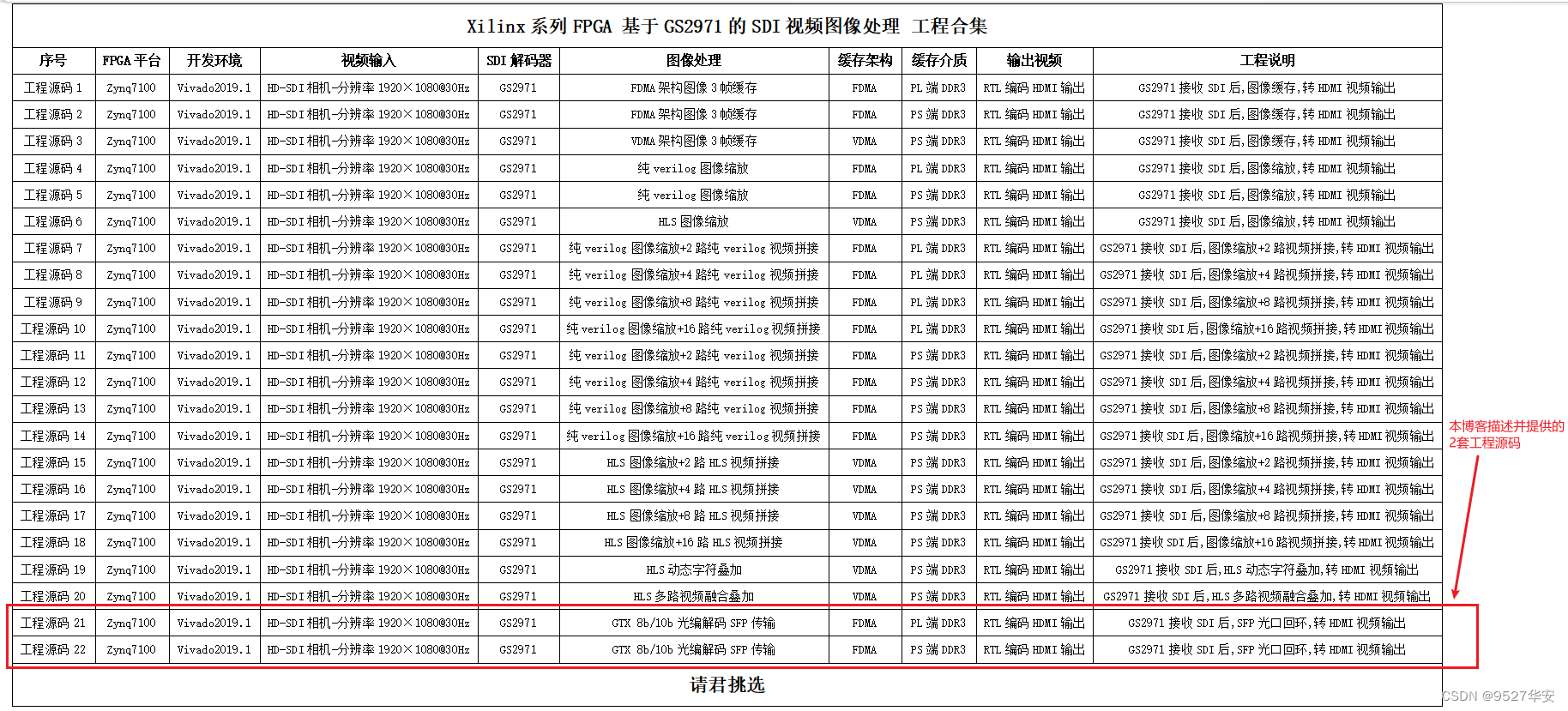

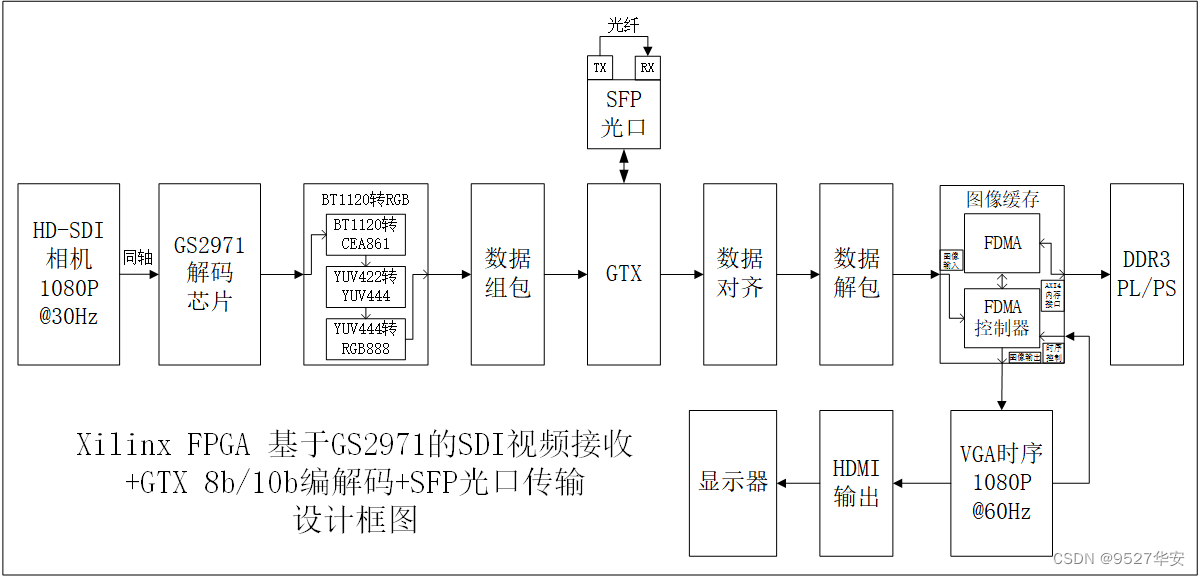

本设计基于Xilinx的Zynq7100-xc7z100ffg900-2中端FPGA开发板使用GS2971实现SDI视频接收转HDMI输出,输入源为一个HD-SDI相机,也可以使用SD-SDI或者3G-SDI相机,因为本设计是三种SDI视频自适应的;同轴的SDI视频通过同轴线连接到GS2971转接板,GS2971解码芯片将同轴的串行的SDI视频解码为并行的BT1120格式视频,至此,SDI视频解码操作已经完成,可以进行常规的图像处理操作了;本设计的目的是做GTX 8b/10b编解码SFP光口传输,针对目前市面上的主流项目需求,本博设计了HDMI输出方式,需要进行BT1120视频转RGB+数据组包+GTX 8b/10b编解码+数据对齐+数据解包+图像缓存操作;本设计使用BT1120转RGB模块实现视频格式转换;使用纯verilog代码实现视频数据组包,即加上具有链路训练和自定义协议的数据包头和包尾;调用Xilinx官方特有的GTX实现8b/10b编解码,GTX线速率配置为5G;使用板载的SFP光口实现高速串行数据回环;使用纯verilog代码实现GTX解密数据的数据对齐;使用纯verilog代码实现视频数据解包,即解析并丢弃具有链路训练和自定义协议的数据包头和包尾,然后恢复出发送视频的场同步信号、数据有效信号和有效数据;使用本博常用的FDMA架构实现图像三帧缓存,缓存介质包括PL端DDR3和PS端DDR3;图像从DDR3读出后,进入HDMI发送模块输出HDMI显示器;本博客提供2套工程源码,具体如下,请点击图片放大查看:

现对上述2套工程源码做如下解释,方便读者理解:

工程源码21:

输入视频为HD-SDI相机,输入分辨率为1920x1080@30Hz,经过GS2971解码+BT1120视频转RGB+数据组包+GTX 8b/10b编解码(SFP光口回环)+数据对齐+数据解包+FDMA图像缓存+HDMI输出模块后,以HDMI接口方式输出,输出分辨率为1920x1080@60Hz;此工程的FDMA图像缓存架构将视频缓存到PL端DDR3,适应于纯FPGA项目,比如可用于Xilinx的Artix7、Kintex7、Virtex7等FPGA;

工程源码22:

输入视频为HD-SDI相机,输入分辨率为1920x1080@30Hz,经过GS2971解码+BT1120视频转RGB+数据组包+GTX 8b/10b编解码(SFP光口回环)+数据对齐+数据解包+FDMA图像缓存+HDMI输出模块后,以HDMI接口方式输出,输出分辨率为1920x1080@60Hz;此工程的VDMA图像缓存架构将视频缓存到PS端DDR3,即可用于纯FPGA项目,比如可用于Xilinx的Artix7、Kintex7、Virtex7等FPGA,配合MicroBlaze;也可用于Zynq系列FPGA项目,比如可用于Xilinx的Zynq7000系列、Zynq7000、Zynq UltraScale等FPGA;

本文详细描述了Xilinx的Zynq7100-xc7z100ffg900-2中端FPGA开发板使用GS2971实现SDI视频接收+GTX 8b/10b编解码SFP光口传输,工程代码编译通过后上板调试验证,可直接项目移植,适用于在校学生做毕业设计、研究生项目开发,也适用于在职工程师做项目开发,可应用于医疗、军工等行业的数字成像和图像传输领域;

提供完整的、跑通的工程源码和技术支持;

工程源码和技术支持的获取方式放在了文章末尾,请耐心看到最后;

免责声明

本工程及其源码即有自己写的一部分,也有网络公开渠道获取的一部分(包括CSDN、Xilinx官网、Altera官网等等),若大佬们觉得有所冒犯,请私信批评教育;基于此,本工程及其源码仅限于读者或粉丝个人学习和研究,禁止用于商业用途,若由于读者或粉丝自身原因用于商业用途所导致的法律问题,与本博客及博主无关,请谨慎使用。。。

2、相关方案推荐

本博已有的 SDI 编解码方案

我的博客主页开设有SDI视频专栏,里面全是FPGA编解码SDI的工程源码及博客介绍;既有基于GS2971/GS2972的SDI编解码,也有基于GTP/GTX资源的SDI编解码;既有HD-SDI、3G-SDI,也有6G-SDI、12G-SDI等;专栏地址链接:点击直接前往

本方案的SDI接收转HDMI输出应用

本方案采用GS2971接收SDI视频,然后进行图像缓存操作(图像缓存方案包括FDMA方案和VDMA方案,缓存介质包括PL端DDR3、PS端DDR3),最后以HDMI方式输出,提供3套工程源码,3套工程源码详情请参考“1、前言”中的截图,详细设计方案请参考我专门的博客,博客链接如下:

点击直接前往

本方案的SDI接收+图像缩放应用

本方案采用GS2971接收SDI视频,然后进行图像缩放操作(图像缩放方案包括纯verilog图像缩放方案和HLS图像缩放方案),再进行图像缓存操作(图像缓存方案包括FDMA方案和VDMA方案,缓存介质包括PL端DDR3、PS端DDR3),最后以HDMI方式输出,提供3套工程源码,3套工程源码详情请参考“1、前言”中的截图,详细设计方案请参考我专门的博客,博客链接如下:

点击直接前往

本方案的SDI接收+纯verilog图像缩放+纯verilog多路视频拼接应用

本方案采用GS2971接收SDI视频,然后进行图像缩放操作(图像缩放方案为纯verilog图像缩放),再进行多路视频拼接(包括2路、4路、8路、16路视频拼接,拼接方案为纯verilogFDMA方案,视频拼接和图像缓存为一个整体,缓存介质包括PL端DDR3、PS端DDR3),最后以HDMI方式输出,提供8套工程源码,8套工程源码详情请参考“1、前言”中的截图,详细设计方案请参考我专门的博客,博客链接如下:

点击直接前往

本方案的SDI接收+HLS图像缩放+Video Mixer多路视频拼接应用

本方案采用GS2971接收SDI视频,然后进行图像缩放操作(图像缩放方案为HLS图像缩放),再进行多路视频拼接(拼接方案为Xilinx官方的Video Mixer方案,包括2路、4路、8路、16路视频拼接),再进行图像缓存操作(图像缓存方案为VDMA方案,缓存介质包括PS端DDR3),最后以HDMI方式输出,提供4套工程源码,4套工程源码详情请参考“1、前言”中的截图,详细设计方案请参考我专门的博客,博客链接如下:

点击直接前往

本方案的SDI接收+OSD动态字符叠加输出应用

本方案采用GS2971接收SDI视频,然后进行动态字符叠加(方案为HLS动态字符叠加),再进行图像缓存操作(图像缓存方案为VDMA方案,缓存介质包括PS端DDR3),最后以HDMI方式输出,提供1套工程源码,工程源码详情请参考“1、前言”中的截图,详细设计方案请参考我专门的博客,博客链接如下:

点击直接前往

本方案的SDI接收+HLS多路视频融合叠加应用

本方案采用GS2971接收SDI视频,然后进行多路视频融合叠加(方案为HLS多路视频融合叠加),再进行图像缓存操作(图像缓存方案为VDMA方案,缓存介质包括PS端DDR3),最后以HDMI方式输出,提供1套工程源码,工程源码详情请参考“1、前言”中的截图,详细设计方案请参考我专门的博客,博客链接如下:

点击直接前往

FPGA的SDI视频编解码项目培训

基于目前市面上FPGA的SDI视频编解码项目培训较少的特点,本博专门开设了FPGA的SDI视频编解码高级项目培训班,专门培训SDI视频的编解码,具体培训计划细节如下:

1、我发你上述全套工程源码和对应的工程设计文档网盘链接,你保存下载,作为培训的核心资料;

2、你根据自己的实际情况安装好对应的开发环境,然后对着设计文档进行浅层次的学习;

3、遇到不懂的随时问我,包括代码、职业规划、就业咨询、人生规划、战略规划等等;

4、每周末进行一次腾讯会议,我会检查你的学习情况和面对面沟通交流;

5、你可以移植代码到你自己的FPGA开发板上跑,如果你没有板子,你根据你自己的需求修改代码后,编译工程,把bit发我,我帮你下载到我的板子上验证;或者你可以买我的开发板;

3、详细设计方案

设计原理框图

两套工程源码的设计原理框图如下:

SDI 相机

我用到的是SDI相机为HD-SDI相机,输出分辨率为1920x1080@30Hz,本工程对SDI相机的选择要求范围很宽,可以是SD-SDI、HD-SDI、3G-SDI,因为很设计对这三种SDI视频是自动识别并自适应的;如果你的手里没有SDI相机,也可以去某宝买HDMI转SDI盒子,一百多块钱就可以搞定,使用笔记本电脑模拟视频源,用HDMI线连接HDMI转SDI盒子,输出SDI视频做事视频源,可以模拟SDI相机;

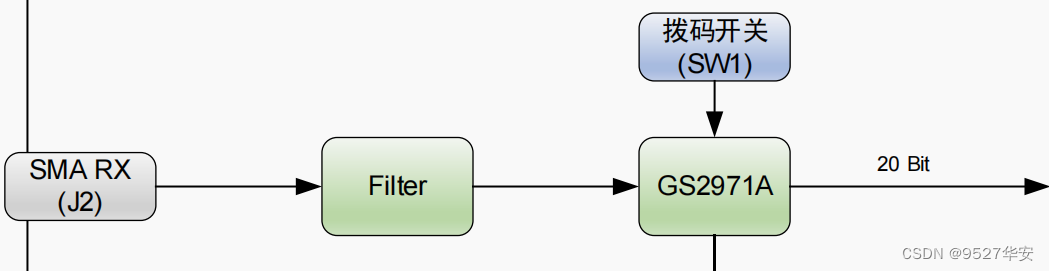

GS2971

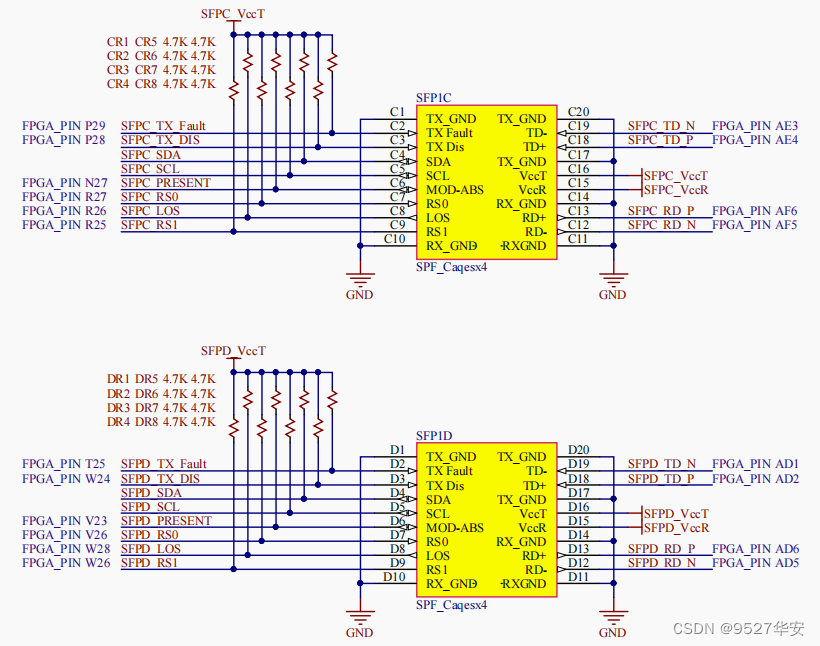

本设计采用GS2971芯片解码SDI,GS2971不需要软件配置,硬件电阻上下拉即可完成配置,本设计配置为输出BT1120格式视频,当然,你在设计电路时也可以配置为输出CEA861格式视频;GS2971硬件架构如下,提供PDF格式原理图:

BT1120转RGB

BT1120转RGB模块的作用是将SMPTE SD/HD/3G SDI IP核解码输出的BT1120视频转换为RGB888视频,它由BT1120转CEA861模块、YUV422转YUV444模块、YUV444转RGB888三个模块组成,该方案参考了Xilinx官方的设计;BT1120转RGB模块代码架构如下:

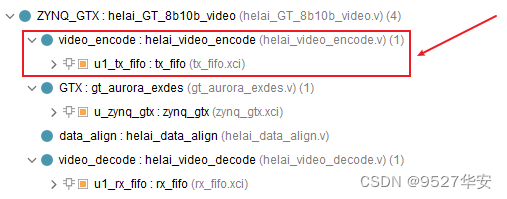

视频数据组包

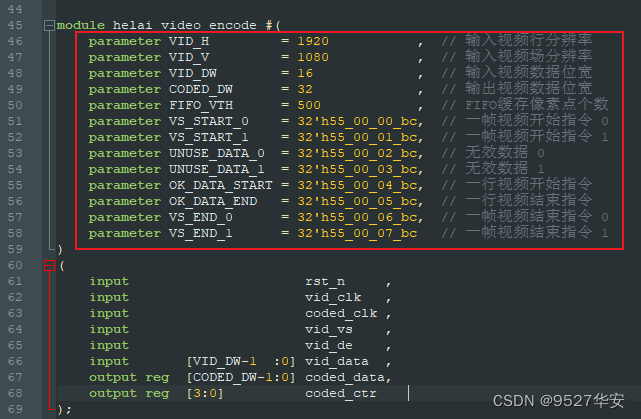

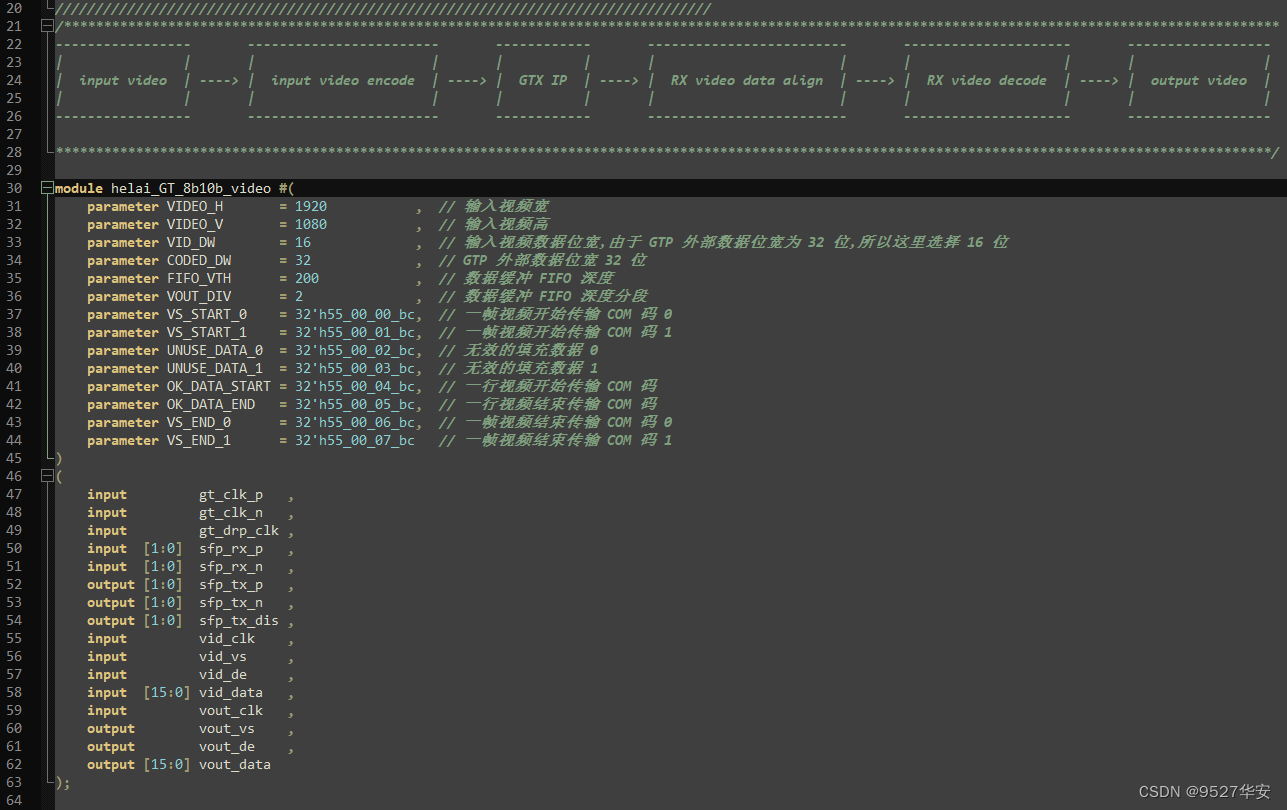

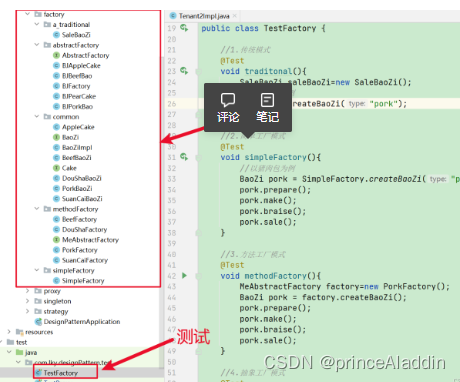

由于视频需要在GTX中通过aurora 8b/10b协议收发,所以数据必须进行组包,以适应aurora 8b/10b协议标准;视频数据组包模块代码位置如下:

首先,我们将16bit的视频存入FIFO中,存满一行时就从FIFO读出送入GTX发送;在此之前,需要对一帧视频进行编号,也叫作指令,GTX组包时根据固定的指令进行数据发送,GTX解包时根据固定的指令恢复视频的场同步信号和视频有效信号;当一帧视频的场同步信号上升沿到来时,发送一帧视频开始指令 0,当一帧视频的场同步信号下降沿到来时,发送一帧视频开始指令 1,视频消隐期间发送无效数据 0 和无效数据 1,当视频有效信号到来时将每一行视频进行编号,先发送一行视频开始指令,在发送当前的视频行号,当一行视频发送完成后再发送一行视频结束指令,一帧视频发送完成后,先发送一帧视频结束指令 0,再发送一帧视频结束指令 1;至此,一帧视频则发送完成,这个模块不太好理解,所以我在代码里进行了详细的中文注释,需要注意的是,为了防止中文注释的乱序显示,请用notepad++编辑器打开代码;指令定义如下:

注意!!!指令可以任意更改,但最低字节必须为bc;

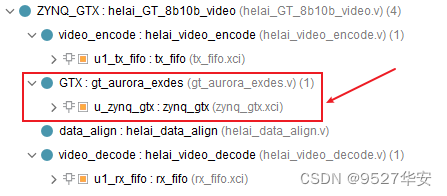

GTX aurora 8b/10b 详解

这个就是调用GTX做aurora 8b/10b协议的数据编解码,代码位置如下:

GTX IP 简介

关于GTX介绍最详细的肯定是Xilinx官方的《ug476_7Series_Transceivers》,我们以此来解读:《ug476_7Series_Transceivers》的PDF文档我已放在了资料包里,文章末尾有获取方式;我用到的开发板FPGA型号为Xilinx Zynq7100;带有8路GTX资源,其中2路连接到了2个SFP光口,每通道的收发速度为 500 Mb/s 到 10.3125 Gb/s 之间。GTX收发器支持不同的串行传输接口或协议,比如 PCIE 1.1/2.0 接口、万兆网 XUAI 接口、OC-48、串行 RapidIO 接口、 SATA(Serial ATA) 接口、数字分量串行接口(SDI)等等;

GTX 基本结构

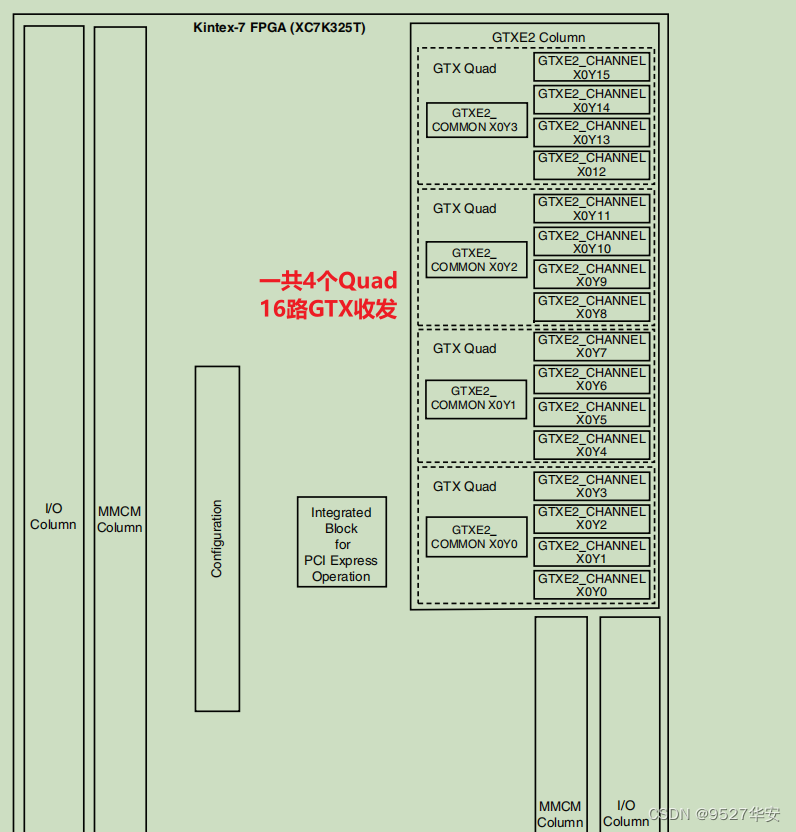

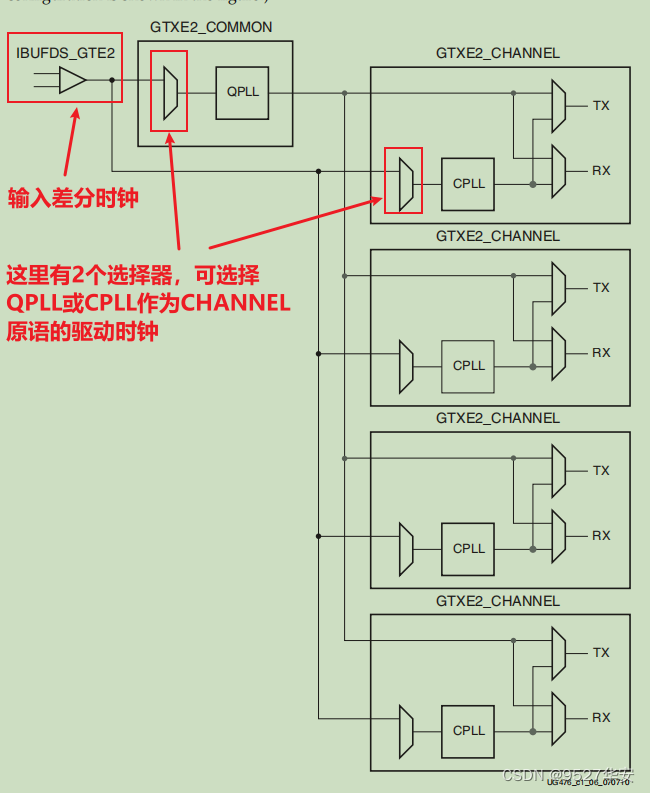

Xilinx 以 Quad 来对串行高速收发器进行分组,四个串行高速收发器和一个 COMMOM(QPLL)组成一个 Quad,每一个串行高速收发器称为一个 Channel(通道),下图为四路 GTX 收发器在Kintex7 FPGA 芯片中的示意图:《ug476_7Series_Transceivers》第24页;

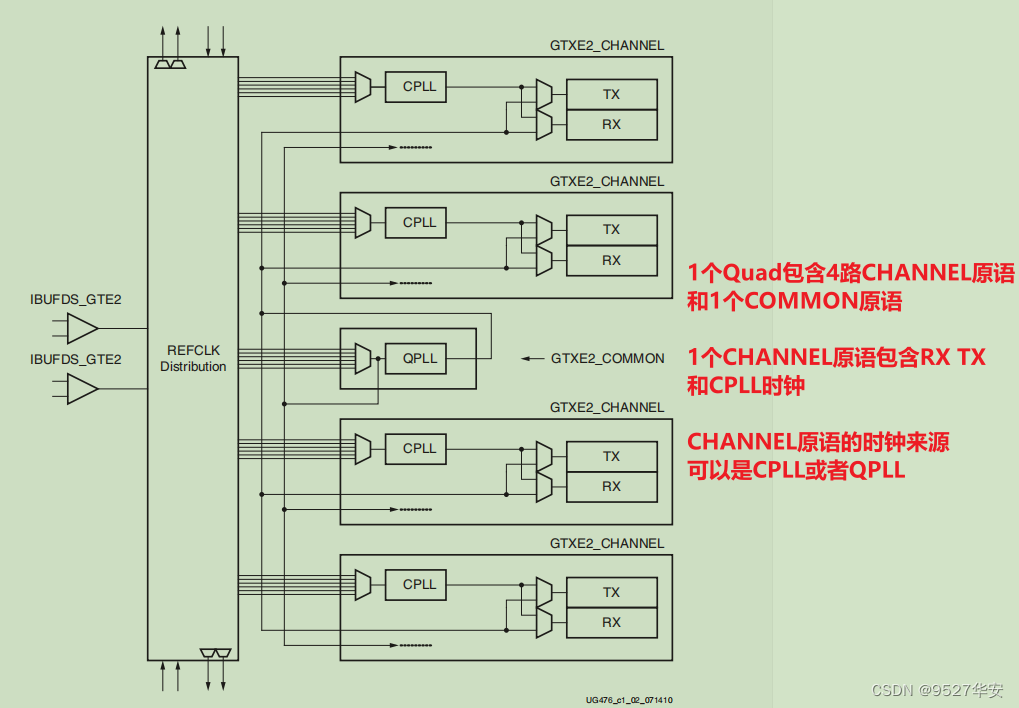

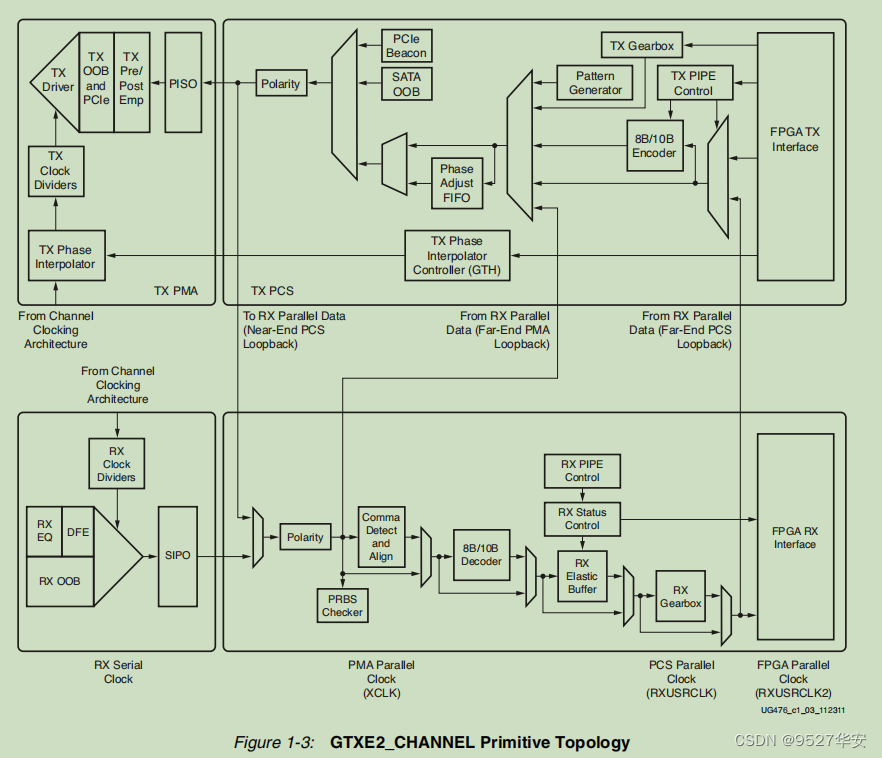

GTX 的具体内部逻辑框图如下所示,它由四个收发器通道 GTXE2_CHANNEL原语 和一个GTXE2_COMMON 原语组成。每路GTXE2_CHANNEL包含发送电路 TX 和接收电路 RX,GTXE2_CHANNEL的时钟可以来自于CPLL或者QPLL,可在IP配置界面里配置;《ug476_7Series_Transceivers》第25页;

每个 GTXE2_CHANNEL 的逻辑电路如下图所示:《ug476_7Series_Transceivers》第26页;

GTXE2_CHANNEL 的发送端和接收端功能是独立的,均由 PMA(Physical Media Attachment,物理媒介适配层)和 PCS(Physical Coding Sublayer,物理编码子层)两个子层组成。其中 PMA 子层包含高速串并转换(Serdes)、预/后加重、接收均衡、时钟发生器及时钟恢复等电路。PCS 子层包含8B/10B 编解码、缓冲区、通道绑定和时钟修正等电路。

这里说多了意义不大,因为没有做过几个大的项目是不会理解这里面的东西的,对于初次使用或者想快速使用者而言,更多的精力应该关注IP核的调用和使用,后面我也会重点将到IP核的调用和使用;

GTX 发送和接收处理流程

首先用户逻辑数据经过 8B/10B 编码后,进入一个发送缓存区(Phase Adjust FIFO),该缓冲区主要是 PMA 子层和 PCS 子层两个时钟域的时钟隔离,解决两者时钟速率匹配和相位差异的问题,最后经过高速 Serdes 进行并串转换(PISO),有必要的话,可以进行预加重(TX Pre-emphasis)、后加重。值得一提的是,如果在 PCB 设计时不慎将 TXP 和 TXN 差分引脚交叉连接,则可以通过极性控制(Polarity)来弥补这个设计错误。接收端和发送端过程相反,相似点较多,这里就不赘述了,需要注意的是 RX 接收端的弹性缓冲区,其具有时钟纠正和通道绑定功能。这里的每一个功能点都可以写一篇论文甚至是一本书,所以这里只需要知道个概念即可,在具体的项目中回具体用到,还是那句话:对于初次使用或者想快速使用者而言,更多的精力应该关注IP核的调用和使用。

GTX 的参考时钟

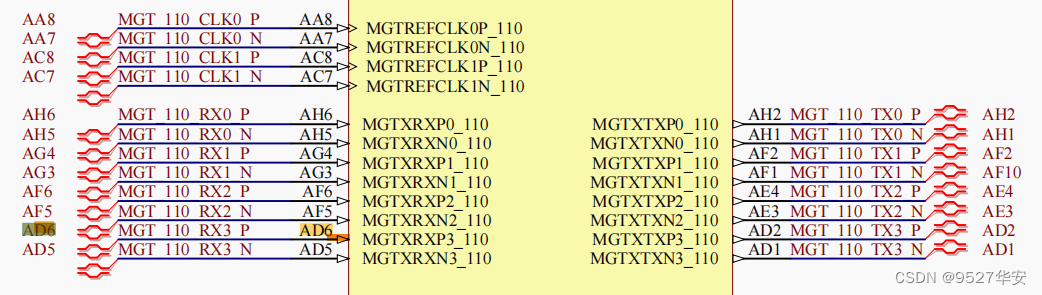

GTX 模块有两个差分参考时钟输入管脚(MGTREFCLK0P/N 和 MGTREFCLK1P/N),作为 GTX 模块的参考时钟源,用户可以自行选择。一般的A7系列开发板上,都有一路 148.5Mhz 的 GTX 参考时钟连接到 MGTREFCLK0上,作为 GTX 的参考时钟。差分参考时钟通过IBUFDS 模块转换成单端时钟信号进入到 GTXE2_COMMOM 的QPLL或CPLL中,产生 TX 和 RX 电路中所需的时钟频率。TX 和 RX 收发器速度相同的话,TX 电路和 RX 电路可以使用同一个 PLL 产生的时钟,如果 TX 和 RX收发器速度不相同的话,需要使用不同的 PLL 时钟产生的时钟。参考时钟这里Xilinx给出的GT参考例程已经做得很好了,我们调用时其实不用修改;GTX 的参考时钟结构图如下:《ug476_7Series_Transceivers》第31页;

GTX 发送接口

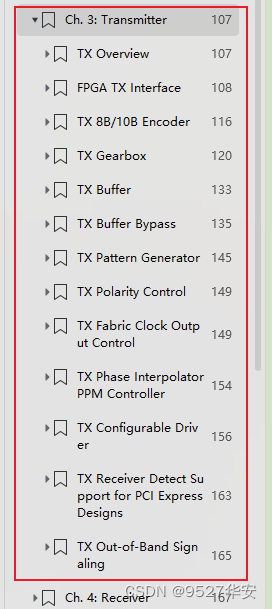

《ug476_7Series_Transceivers》的第107到165页详细介绍了发送处理流程,其中大部分内容对于用户而言可以不去深究,因为手册讲的基本都是他自己的设计思想,留给用户可操作的接口并不多,基于此思路,我们重点讲讲GTX例化时留给用户的发送部分需要用到的接口;

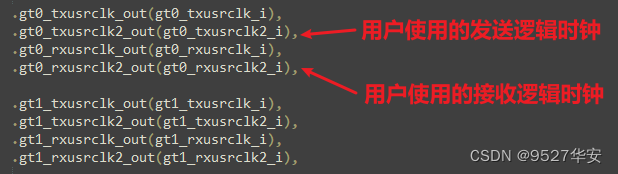

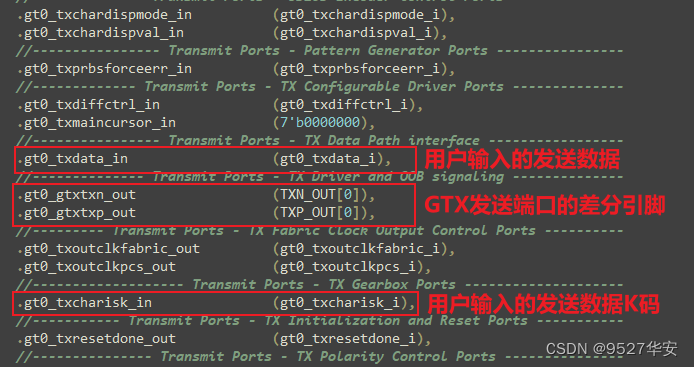

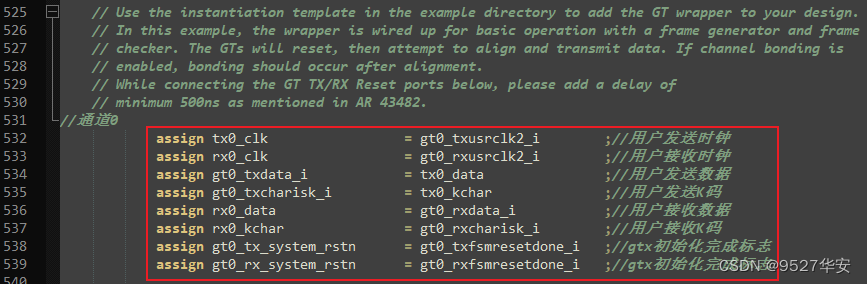

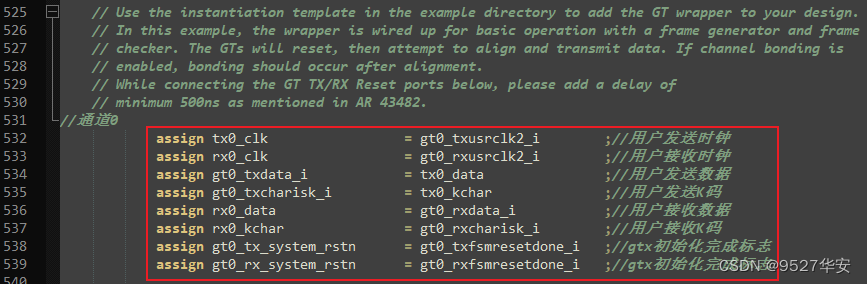

用户只需要关心发送接口的时钟和数据即可,GTX例化模块的这部分接口如下:

在代码中我已为你们重新绑定并做到了模块的顶层,代码部分如下:

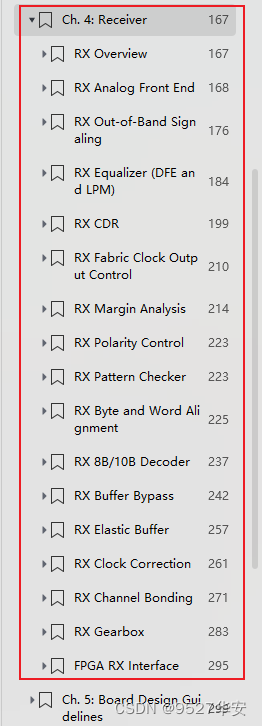

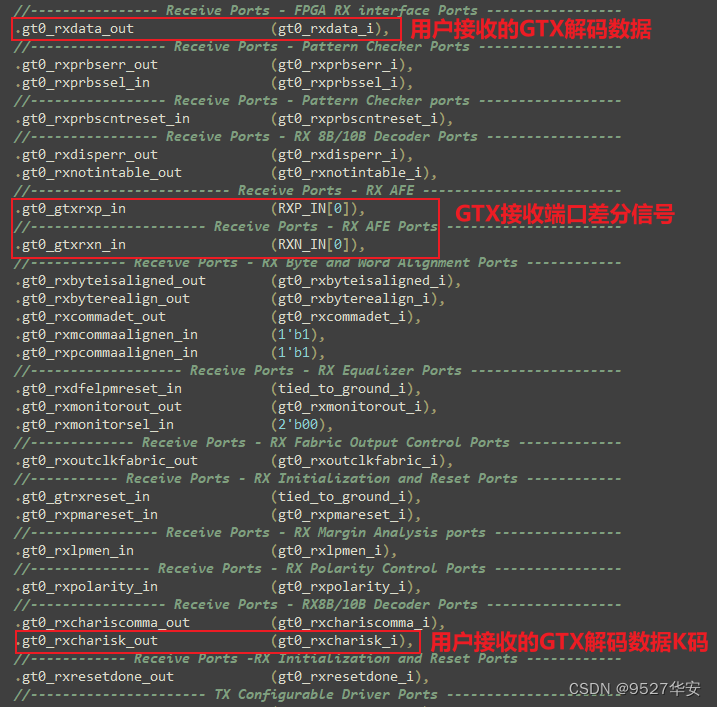

GTX 接收接口

《ug476_7Series_Transceivers》的第167到295页详细介绍了接收处理流程,其中大部分内容对于用户而言可以不去深究,因为手册讲的基本都是他自己的设计思想,留给用户可操作的接口并不多,基于此思路,我们重点讲讲GTX例化时留给用户的发送部分需要用到的接口;

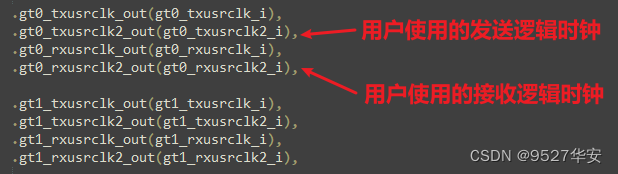

用户只需要关心接收接口的时钟和数据即可,GTX例化模块的这部分接口如下:

在代码中我已为你们重新绑定并做到了模块的顶层,代码部分如下:

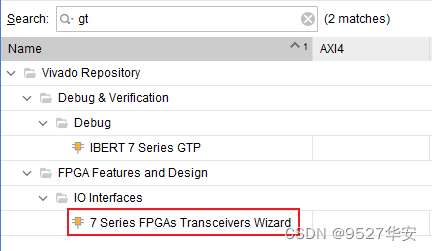

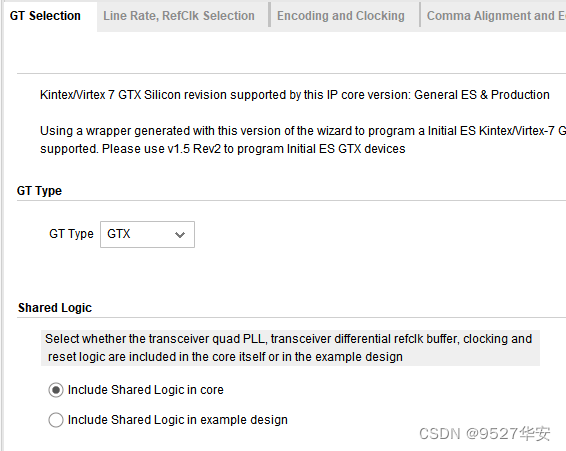

GTX IP核调用和使用

GTX IP核调用和使用很简单,通过vivado的UI界面即可完成,如下:

有别于网上其他博主的教程,我个人喜欢用如下图的共享逻辑:

这样选择的好处有两个,一是方便DRP变速,二是便于IP核的修改,修改完IP核后直接编译即可,不再需要打开example工程,再复制下面的一堆文件放到自己的工程什么的,玩儿个GTX需要那么复杂么?

这里对上图的标号做解释:

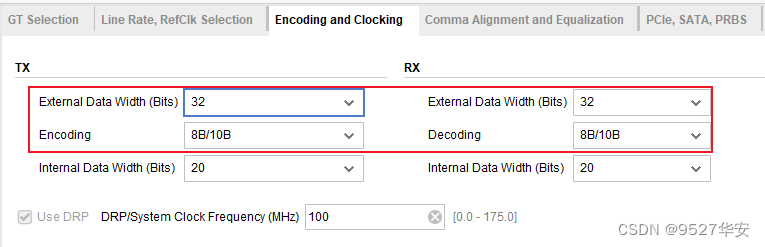

1:线速率,根据自己的项目需求来,GTX 的范围是0.5到10.3125G,由于我的项目是视频传输,所以在GTX 的速率范围内均可,本例程选择了5G;

2:参考时钟,这个得根据你的原理图来,可以是80M、125M、148.5M、156.25M等等,我的开发板是125M;

4:GTX 组的绑定,这个很重要,他的绑定参考依据有两个,已是你的开发板原理图,而是官方的参考资料《ug476_7Series_Transceivers》,官方根据BANK不同将GTX资源分成了多组,由于GT资源是Xilinx系列FPGA的专用资源,占用专用的Bnak,所以引脚也是专用的,那么这些GTX组和引脚是怎么对应的呢?《ug476_7Series_Transceivers》有说明;

我的板子原理图如下:

选择外部数据位宽32bit的8b/10b编解码,如下:

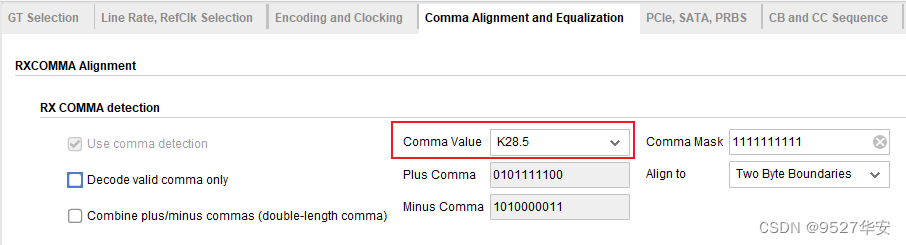

下面这里讲的是K码检测:

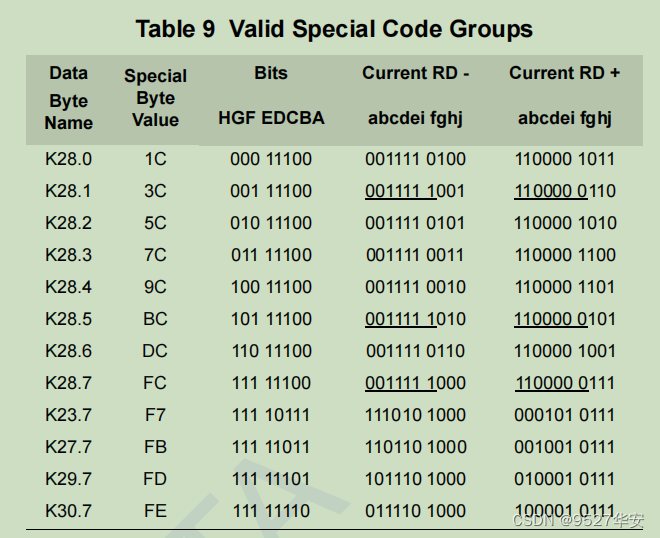

这里选择K28.5,也就是所谓的COM码,十六进制为bc,他的作用很多,可以表示空闲乱序符号,也可以表示数据错位标志,这里用来标志数据错位,8b/10b协议对K码的定义如下:

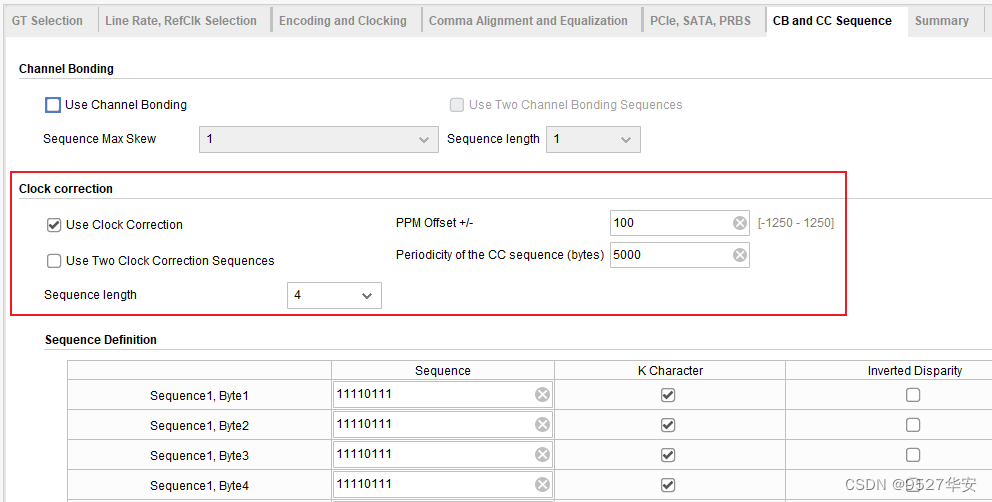

下面讲的是时钟矫正,也就是对应GTX内部接收部分的弹性buffer;

这里有一个时钟频偏的概念,特别是收发双方时钟不同源时,这里设置的频偏为100ppm,规定每隔5000个数据包发送方发送一个4字节的序列,接收方的弹性buffer会根据这4字节的序列,以及数据在buffer中的位置来决定删除或者插入一个4字节的序列中的一个字节,目的是确保数据从发送端到接收端的稳定性,消除时钟频偏的影响;

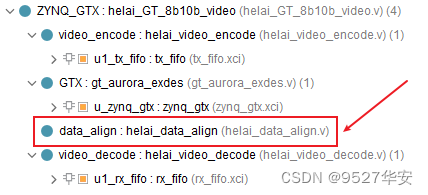

数据对齐

由于GT资源的aurora 8b/10b数据收发天然有着数据错位的情况,所以需要对接受到的解码数据进行数据对齐处理,数据对齐模块代码位置如下:

我定义的 K 码控制字符格式为:XX_XX_XX_BC,所以用一个rx_ctrl 指示数据是否为 K 码 的 COM 符号;

rx_ctrl = 4’b0000 表示 4 字节的数据没有 COM 码;

rx_ctrl = 4’b0001 表示 4 字节的数据中[ 7: 0] 为 COM 码;

rx_ctrl = 4’b0010 表示 4 字节的数据中[15: 8] 为 COM 码;

rx_ctrl = 4’b0100 表示 4 字节的数据中[23:16] 为 COM 码;

rx_ctrl = 4’b1000 表示 4 字节的数据中[31:24] 为 COM 码;

基于此,当接收到有K码时就对数据进行对齐处理,也就是将数据打一拍,和新进来的数据进行错位组合,这是FPGA的基础操作,这里不再赘述;

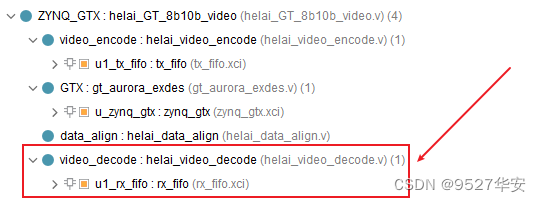

视频数据解包

数据解包是数据组包的逆过程,代码位置如下:

GTX解包时根据固定的指令恢复视频的场同步信号和视频有效信号;这些信号是作为后面图像缓存的重要信号;

至此,数据进出GTX部分就已经讲完了,整个过程的框图我在代码中描述了,如下:

图像缓存

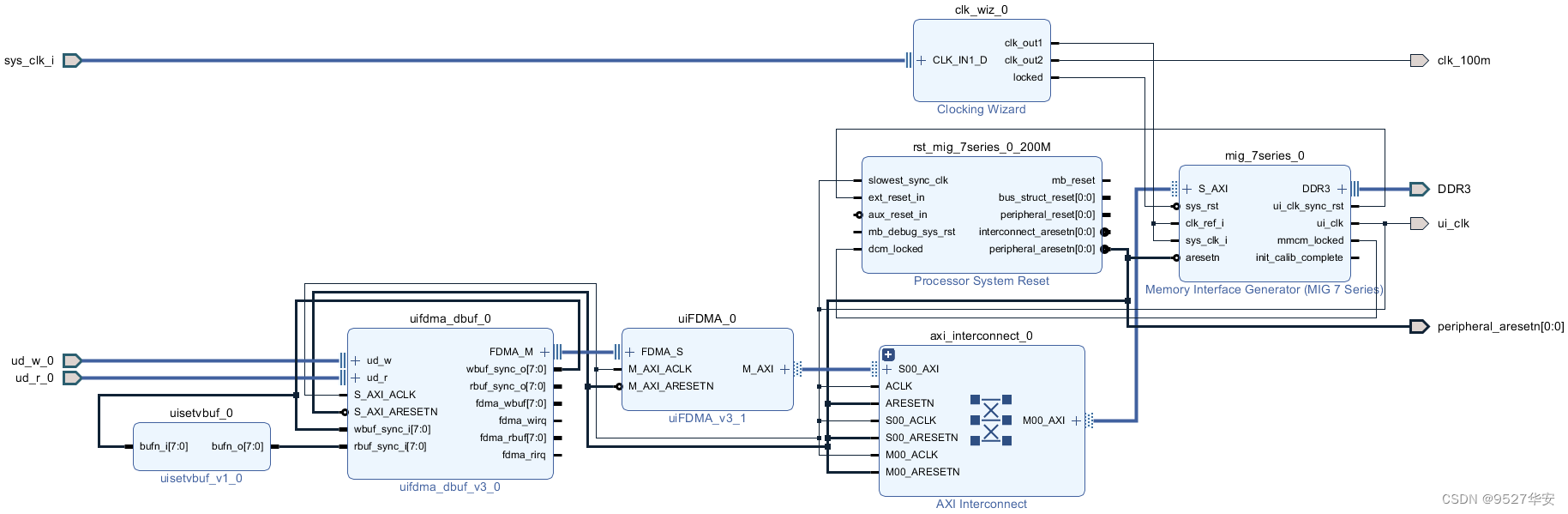

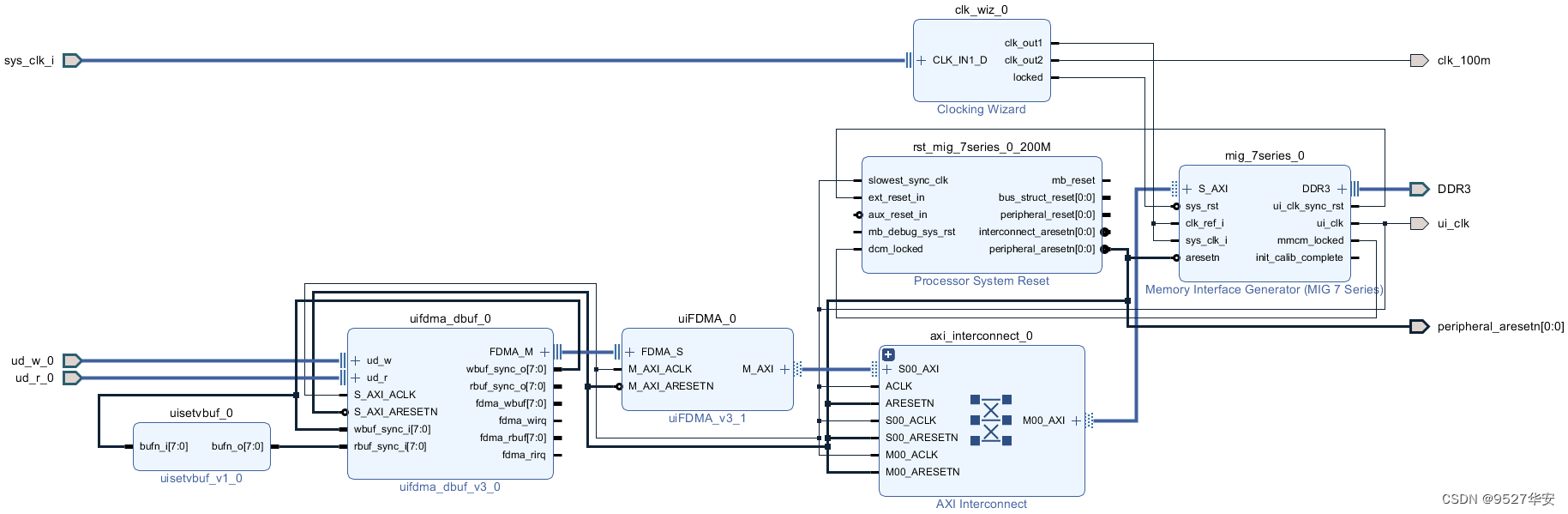

使用本博常用的FDMA图像缓存架构实现图像3帧缓存,缓存介质为板载的DDR3;FDMA图像缓存架构由FDMA、FDMA控制器、缓存帧选择器构成、Xilinx MIG IP核(PL端)、Zynq软核(PS端)构成;图像缓存使用Xilinx vivado的Block Design设计,以工程源码21为例如下图:

关于FDMA更详细的介绍,请参考我之前的博客,博文链接如下:

点击直接前往

HDMI输出

HDMI输出架构由VGA时序和HDMI输出模块构成,VGA时序负责产生输出的1920x1080@60Hz的时序,并控制FDMA数据读出,HDMI输出模块负责将VGA的RGB视频转换为差分的TMDS视频,代码架构如下:

HDMI输出模块采用verilog代码手写,可以用于FPGA的HDMI发送应用,关于这个模块,请参考我之前的博客,博客地址:点击直接前往

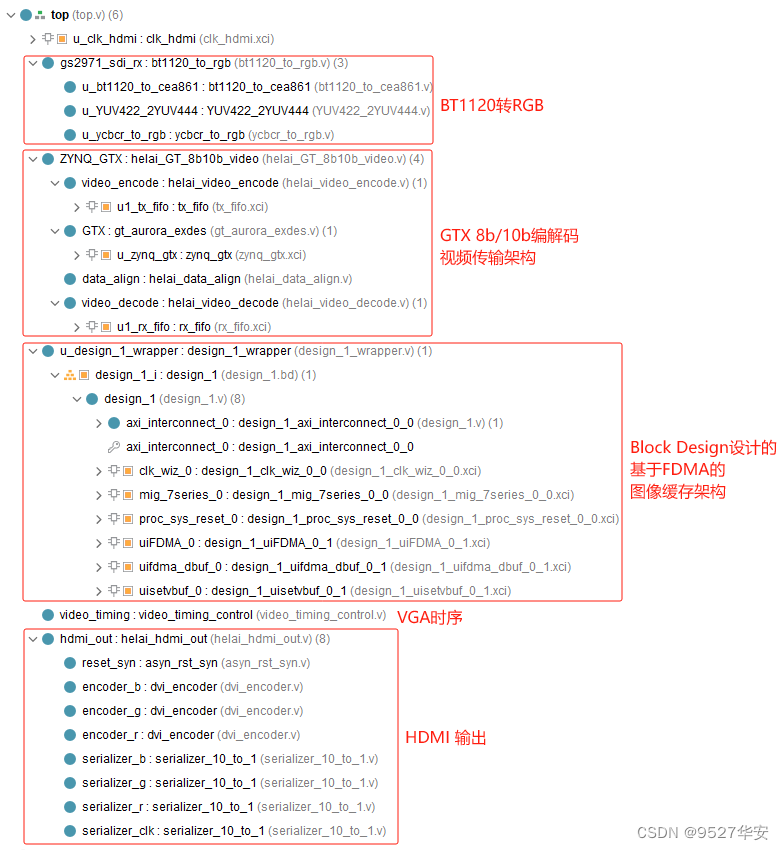

工程源码架构

以工程源码21为例,工程Block Design和源码架构如下,Block Design设计为图像缓存架构的部分,缓存PL端DDR3,工程源码22与之类似,但缓存PS端DDR3:

以工程源码21为例,总体源码架构如下,工程源码22与之类似,但Block Design中有Zynq软核:

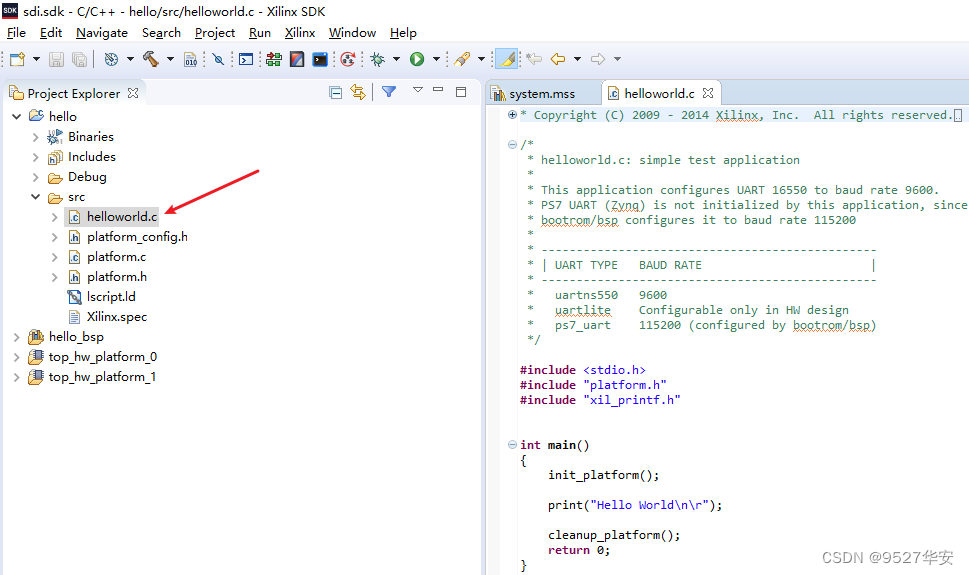

工程源码22使用了自定义的FDMA方案,虽然不需要SDK配置,但FDMA的AXI4接口时钟由Zynq提供,所以需要运行SDK程序才能启动Zynq,从而为PL端逻辑提供时钟;由于不需要SDK配置,所以SDK软件代码就变得极度简单,只需运行一个“Hello World”即可,如下:

4、工程源码21详解–>SDI接收+GTX 8b/10b编解码 图像缓存至PL端DDR3

开发板FPGA型号:Xilinx–Zynq7100–xc7z100ffg900-2;

开发环境:Vivado2019.1;

输入:HD-SDI相机,分辨率1920x1080@30Hz;

输出:HDMI ,分辨率1920x1080@60Hz;

图像处理:GTX 8b/10b编解码,SFP光口回环;

图像缓存方案:FDMA方案;

图像缓存路径:PL端DDR3;

工程作用:此工程目的是让读者掌握FPGA实现SDI+GTX 8b/10b编解码传输的设计能力,以便能够移植和设计自己的项目;

工程Block Design和工程代码架构请参考第3章节“工程源码架构“小节内容;

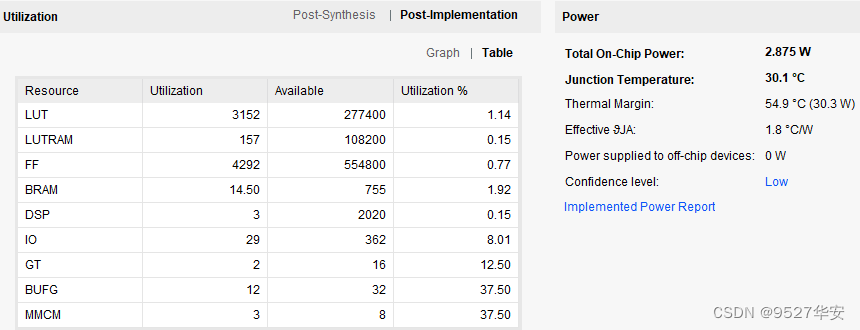

工程的资源消耗和功耗如下:

5、工程源码22详解–>SDI接收+GTX 8b/10b编解码 图像缓存至PS端DDR3

开发板FPGA型号:Xilinx–Zynq7100–xc7z100ffg900-2;

开发环境:Vivado2019.1;

输入:HD-SDI相机,分辨率1920x1080@30Hz;

输出:HDMI ,分辨率1920x1080@60Hz;

图像处理:GTX 8b/10b编解码,SFP光口回环;

图像缓存方案:FDMA方案;

图像缓存路径:PS端DDR3;

工程作用:此工程目的是让读者掌握FPGA实现SDI+GTX 8b/10b编解码传输的设计能力,以便能够移植和设计自己的项目;

工程Block Design和工程代码架构请参考第3章节“工程源码架构“小节内容;

工程的资源消耗和功耗如下:

6、工程移植说明

vivado版本不一致处理

1:如果你的vivado版本与本工程vivado版本一致,则直接打开工程;

2:如果你的vivado版本低于本工程vivado版本,则需要打开工程后,点击文件–>另存为;但此方法并不保险,最保险的方法是将你的vivado版本升级到本工程vivado的版本或者更高版本;

3:如果你的vivado版本高于本工程vivado版本,解决如下:

打开工程后会发现IP都被锁住了,如下:

此时需要升级IP,操作如下:

FPGA型号不一致处理

如果你的FPGA型号与我的不一致,则需要更改FPGA型号,操作如下:

更改FPGA型号后还需要升级IP,升级IP的方法前面已经讲述了;

其他注意事项

1:由于每个板子的DDR不一定完全一样,所以MIG IP需要根据你自己的原理图进行配置,甚至可以直接删掉我这里原工程的MIG并重新添加IP,重新配置;

2:根据你自己的原理图修改引脚约束,在xdc文件中修改即可;

3:纯FPGA移植到Zynq需要在工程中添加zynq软核;

7、上板调试验证

准备工作

需要准备的器材如下:

FPGA开发板;

SDI摄像头;

SDI转HDMI盒子;

HDMI显示器;

我的开发板了连接如下:

GTX 8b/10b编解码SFP光口传输–>输出视频演示

FPGA基于GS2971的SDI视频接收+GTX 8b/10b编解码SFP光口传输输出效果如下:

GS2971的SDI接收+GTX光编码SFP光口传输

8、福利:工程代码的获取

福利:工程代码的获取

代码太大,无法邮箱发送,以某度网盘链接方式发送,

资料获取方式:私,或者文章末尾的V名片。

网盘资料如下:

相关文章:

FPGA高端项目:FPGA基于GS2971的SDI视频接收+GTX 8b/10b编解码SFP光口传输,提供2套工程源码和技术支持

目录 1、前言免责声明 2、相关方案推荐本博已有的 SDI 编解码方案本方案的SDI接收转HDMI输出应用本方案的SDI接收图像缩放应用本方案的SDI接收纯verilog图像缩放纯verilog多路视频拼接应用本方案的SDI接收HLS图像缩放Video Mixer多路视频拼接应用本方案的SDI接收OSD动态字符叠加…...

【源码编译】Apache SeaTunnel-Web 适配最新2.3.4版本教程

Apache SeaTunnel新版本已经发布,感兴趣的小伙伴可以看之前版本发布的文章 本文主要给大家介绍为使用2.3.4版本的新特性,需要对Apache SeaTunnel-Web依赖的版本进行升级,而SeaTunnel2.3.4版本部分API跟之前版本不兼容,所以需要对 …...

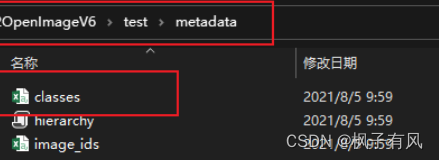

数据集下载

一、数据集下载——谷歌Open images 谷歌Open-image-v6是由谷歌出资标注的一个超大型数据集,数据大小达到600多G,类别达到600多种分类,对于普通研究者而言,根本没办法全部下载下来做测试,也没必要。只需要下载与自己任…...

3、设计模式之工厂模式2(Factory)

一、什么是工厂模式 工厂模式属于创建型设计模式,它用于解耦对象的创建和使用。通常情况下,我们创建对象时需要使用new操作符,但是使用new操作符创建对象会使代码具有耦合性。工厂模式通过提供一个公共的接口,使得我们可以在不暴露…...

npm、nodejs和vue之间关系和区别介绍

本文讲解npm、Node.js和Vue.js这三者之间的关系和区别,以及它们各自的特点。 首先,让我们来了解一下Node.js。 **Node.js** 是一个开源的服务器端运行环境,它允许开发者使用JavaScript来编写服务器端的代码。在传统的Web开发中&#…...

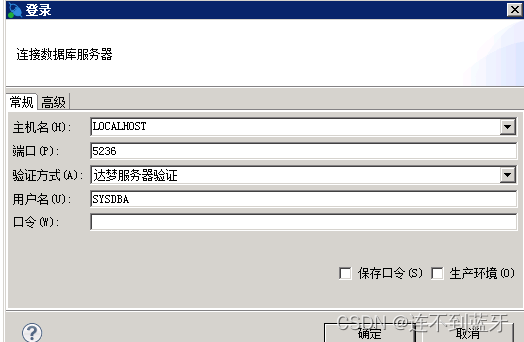

DM数据库安装(Windows)

先解压安装包 点击setup安装 下一步 勾选接受然后下一步 下一步 选择典型安装下一步 下一步 搜索DM数据库配置助手然后一直下一步 然后搜索DM管理工具 登录 登录成功 widows版本安装成功...

Python的asyncio 多线程

-- 多线程、进程、协程是什么就不讲了,(就是你理解的一边呼吸,一边看文章) 仅解决问题的话,下边两篇不用看, Python 中的 async await 概念-CSDN博客 再深一点的看这个 Python中的多线程、进程、协程、…...

【分类讨论】【解析几何】【 数学】【推荐】1330. 翻转子数组得到最大的数组值

作者推荐 视频算法专题 本文涉及知识点 分类讨论 解析几何 LeetCode1330. 翻转子数组得到最大的数组值 给你一个整数数组 nums 。「数组值」定义为所有满足 0 < i < nums.length-1 的 |nums[i]-nums[i1]| 的和。 你可以选择给定数组的任意子数组,并将该子…...

一文了解Spring的SPI机制

文章目录 一文了解Spring的SPI机制Java SPIServiceLoader Spring SPISpringboot利用Spring SPI开发starter 一文了解Spring的SPI机制 Java SPI SPI 全称 Service Provider Interface ,是 Java提供的一套用来被第三方实现或者扩展的接口,它可以用来启用…...

动态修改表名--方法一)

django根据时间(年月日)动态修改表名--方法一

方法一: 第一步:在models创建一个类,里边存放数据表中需要的字段,如下 class TemplateModel(models.Model):NowTime models.CharField(max_length5)name models.CharFiedld(max_length5)class Meta:abstract True # 基础类设…...

实现基本的登录功能

一、登录功能的前端处理过程 1、导入项目所需的图片和CSS等静态文件 参考代码存放client节点的/opt/code目录下 执行如下命令: [rootclient ~]# cp -r /opt/code/kongguan_web/src/assets/* /root/kongguan_web/src/assets/ 将参考代码中的css、icon、images等文…...

Java线程池实现原理及其在美团业务中的实践

随着计算机行业的飞速发展,摩尔定律逐渐失效,多核CPU成为主流。使用多线程并行计算逐渐成为开发人员提升服务器性能的基本武器。 J.U.C提供的线程池:ThreadPoolExecutor类,帮助开发人员管理线程并方便地执行并行任务。了解并合理…...

让AI给你写代码(四)—— 初步利用LangChain Agent根据输入生成,保存,执行

要进一步提升智能编码助手的效率,我觉得需要做到两点 1) 进一步让主人聚焦于设计输入以及结果验证的循环 2) 进一步让智能编码助手聚焦于代码实现和程序流程(保存、打开,修订、执行、合并…) 正好接触到LLM…...

Flutter does not exist

Flutter does not exist 原因:Generated.config 配置文件内路径缺失 原因:Flutter SDK缺失 通过配置文件查到Flutter SDK在本地的存放位置FLUTTER_FRAMEWORK_DIR/Users/haijunyan/Documents/flutter/bin/cache/artifacts/engine/ios 真机所需…...

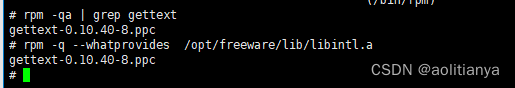

AIX上安装gcc和g++

AIX的iso镜像中没有gcc的软件包,需要我们自己下载,我们可以在 Index of /download/rpmdb/deplists/aix72 下载对应gcc和g版本的依赖文件deps 我们使用的是4.9.4版本的软件包 我们首先安装gcc,在http://www.oss4aix.org/download/everythi…...

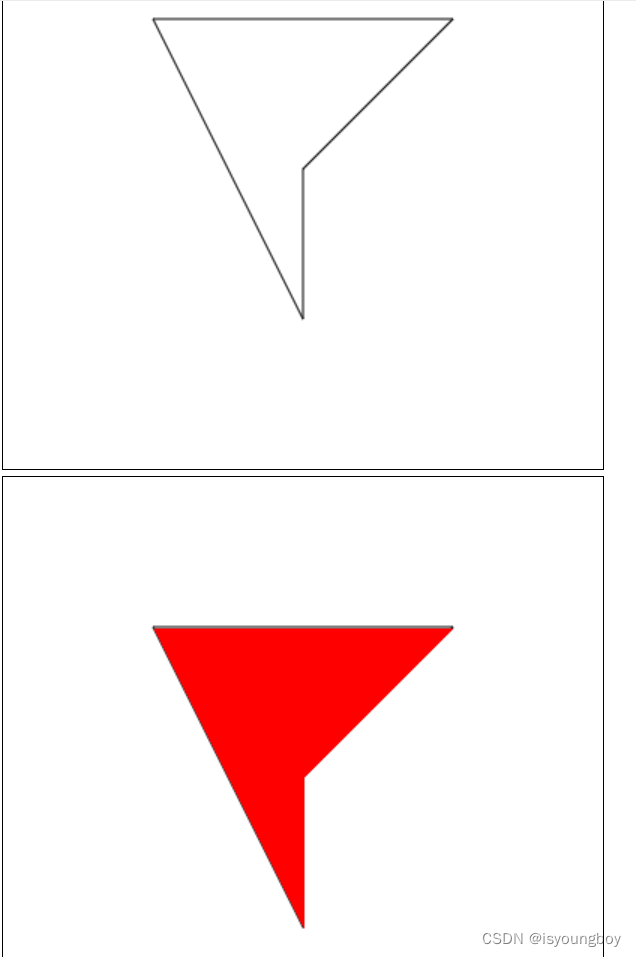

js实现扫描线填色算法使用canvas展示

算法原理 扫描线填色算法的基本思想是:用水平扫描线从上到下扫描由点线段构成的多段构成的多边形。每根扫描线与多边形各边产生一系列交点。将这些交点按照x坐标进行分类,将分类后的交点成对取出,作为两个端点,以所填的色彩画水平…...

考研模拟面试-题目【攻略】

考研模拟面试-题目【攻略】 前言版权推荐考研模拟面试-题目前面的问题通用问题专业题数据结构计算机网络操作系统数据库网络安全 手写题数据结构操作系统计算机网络 代码题基础代码题其他代码题 后面的问题补充题目 最后 前言 2023-10-19 12:00:57 以下内容源自《考研模拟面试…...

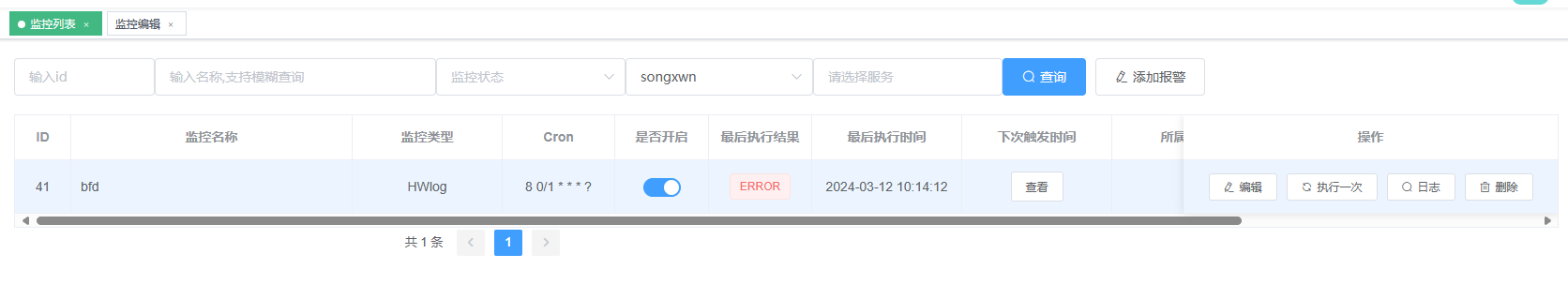

Frostmourne - Elasticsearch源日志告警配置

简介 配置Frostmourne 接入Elasticsearch源进行日志匹配告警,并静默规则,告警消息发送到企业微信,告警信息使用Markdown。 部署安装教程查看: https://songxwn.com/frostmourne_install ELK 安装教程:https://songx…...

GPT出现Too many requests in 1 hour. Try again later.

换节点 这个就不用多说了,你都可以上GPT帐号了,哈…… 清除cooki 然后退出账号,重新登录即可...

python爬虫实战——小红书

目录 1、博主页面分析 2、在控制台预先获取所有作品页的URL 3、在 Python 中读入该文件并做准备工作 4、处理图文类型作品 5、处理视频类型作品 6、异常访问而被中断的现象 7、完整参考代码 任务:在 win 环境下,利用 Python、webdriver、JavaS…...

springboot+vue基于web的蛋糕商城论坛交流系统的设计系统

目录同行可拿货,招校园代理 ,本人源头供货商系统功能模块分析核心功能模块特色功能实现技术难点解决方案性能优化措施项目技术支持源码获取详细视频演示 :文章底部获取博主联系方式!同行可合作同行可拿货,招校园代理 ,本人源头供货商 系统功能模块分析 …...

Aurix TC397内存不够用?三种方法教你手动指定变量到LMU或DSRR地址空间

Aurix TC397内存优化实战:精准分配变量到LMU与DSRR的三大策略 当你在Aurix TC397项目开发中遇到"PSPR空间不足"的报错时,那种突如其来的编译中断感就像赛车手在弯道突然失去动力。这款强大的多核微控制器虽然配备了PSRR、DSRR、DLMU、LMU等多…...

PFC整流器快速动态响应)

手把手教你学Simulink——基于Simulink的模型预测控制(MPC)PFC整流器快速动态响应

目录 手把手教你学Simulink ——基于Simulink的模型预测控制(MPC)PFC整流器快速动态响应 一、问题背景 二、系统建模与控制目标 1. 单相 Boost PFC 拓扑 2. 动态方程(αβ 静止坐标系) 3. 控制目标 三、有限控制集 MPC(FCS-MPC)设计 1. 预测模型(离散化) 2. 代…...

Power BI 网页数据抓取实战:以新浪外汇为例,教你5分钟搞定动态表格导入与清洗

Power BI 网页数据抓取实战:新浪外汇动态表格导入与清洗全流程解析 外汇市场瞬息万变,作为业务分析师,每天手动记录汇率数据既耗时又容易出错。今天我们就以新浪财经外汇数据为例,手把手教你用Power BI实现5分钟自动化抓取清洗的完…...

的跨模态融合应用)

Mirage Flow 与卷积神经网络(CNN)的跨模态融合应用

Mirage Flow 与卷积神经网络(CNN)的跨模态融合应用 你有没有想过,让机器不仅能“看见”图片,还能像人一样“理解”并“描述”图片里的故事?比如,给一张复杂的医学影像,它不仅能圈出病灶&#x…...

3大创新让OpenRocket成为开源工程工具的典范:从问题到实践的完整指南

3大创新让OpenRocket成为开源工程工具的典范:从问题到实践的完整指南 【免费下载链接】openrocket Model-rocketry aerodynamics and trajectory simulation software 项目地址: https://gitcode.com/GitHub_Trending/op/openrocket OpenRocket是一款基于Jav…...

Qwen3.5-9B-AWQ-4bit多场景落地:零售货架图分析+缺货识别+SKU自动计数

Qwen3.5-9B-AWQ-4bit多场景落地:零售货架图分析缺货识别SKU自动计数 1. 零售场景中的视觉理解挑战 在零售行业,货架管理一直是运营效率的关键指标。传统的人工巡检方式存在几个明显痛点: 效率低下:一个中型超市需要2-3小时完成…...

实战应用:基于快马平台ai,开发并部署一个功能齐全的instagram内容下载web应用

今天想和大家分享一个实战项目:基于InsCode(快马)平台快速开发并部署一个功能完备的Instagram内容下载Web应用。这个项目从需求分析到上线只用了不到半天时间,特别适合想验证产品原型的开发者。 项目需求分析 首先明确核心功能需求:需要支持I…...

Kettle转换里‘阻塞数据’控件为啥不灵?我用这个真实ETL案例给你讲透

Kettle转换中‘阻塞数据’控件的实战解析:从失效到精准控制 在ETL工具Kettle的实际应用中,数据流的精确控制往往是决定任务成败的关键。许多中高级用户在使用"阻塞数据直到步骤都完成"控件时,都曾遇到过看似配置正确却无法生效的困…...

)

保姆级教程:用OpenAI Whisper给视频自动生成字幕(附Python代码)

视频创作者必备:用Whisper打造高效字幕工作流 每次剪辑视频最头疼的就是加字幕?作为过来人,我完全理解那种对着时间轴逐帧调整的痛苦。直到发现Whisper这个神器,我的工作效率直接翻了三倍。今天就把这套全自动字幕生成方案完整分享…...