VGA显示器驱动设计与验证

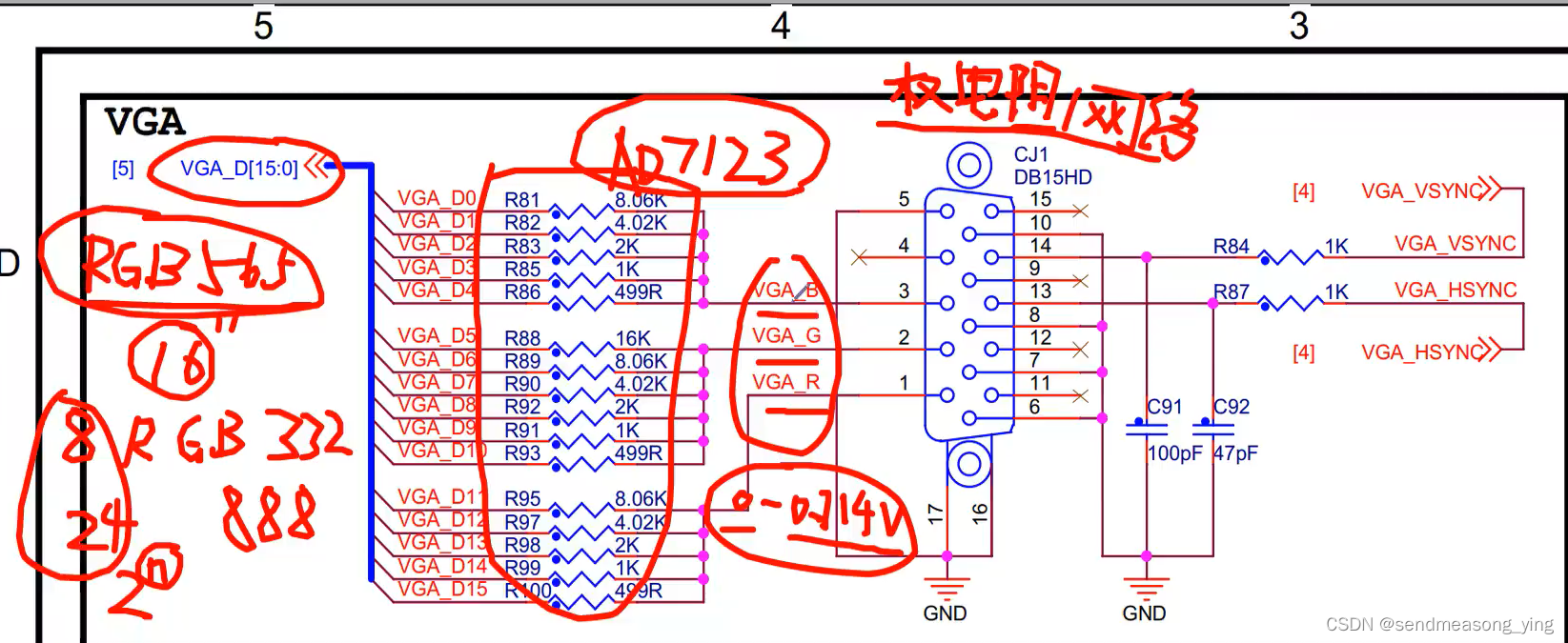

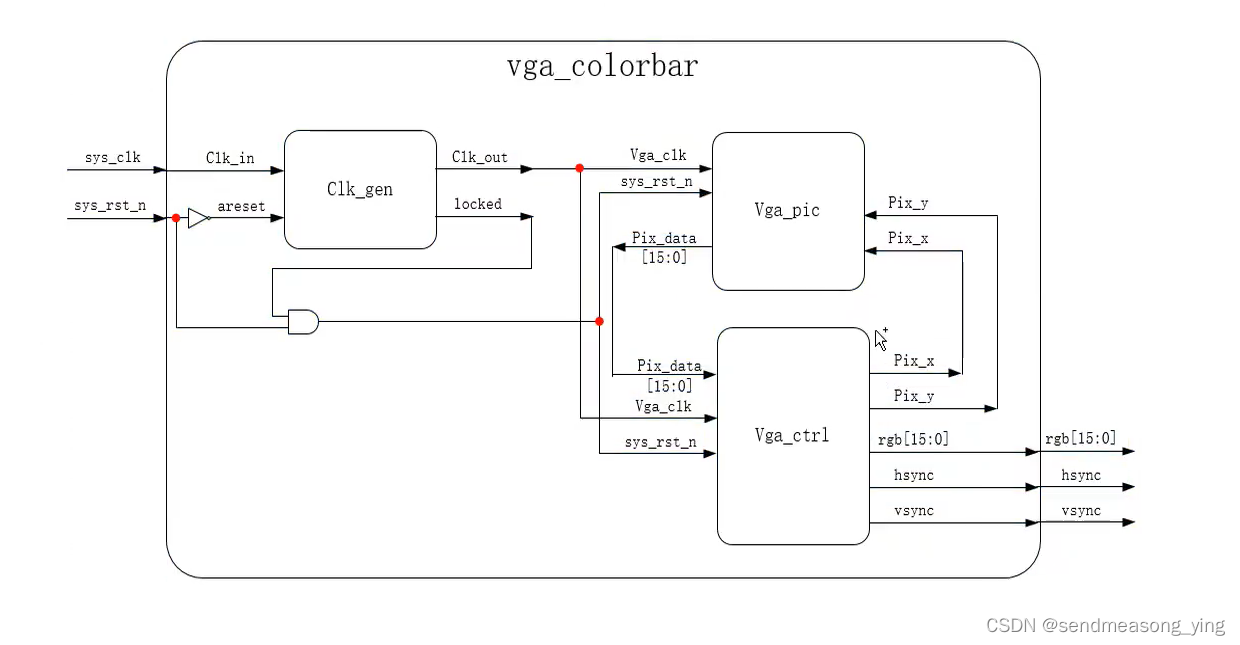

1.原理

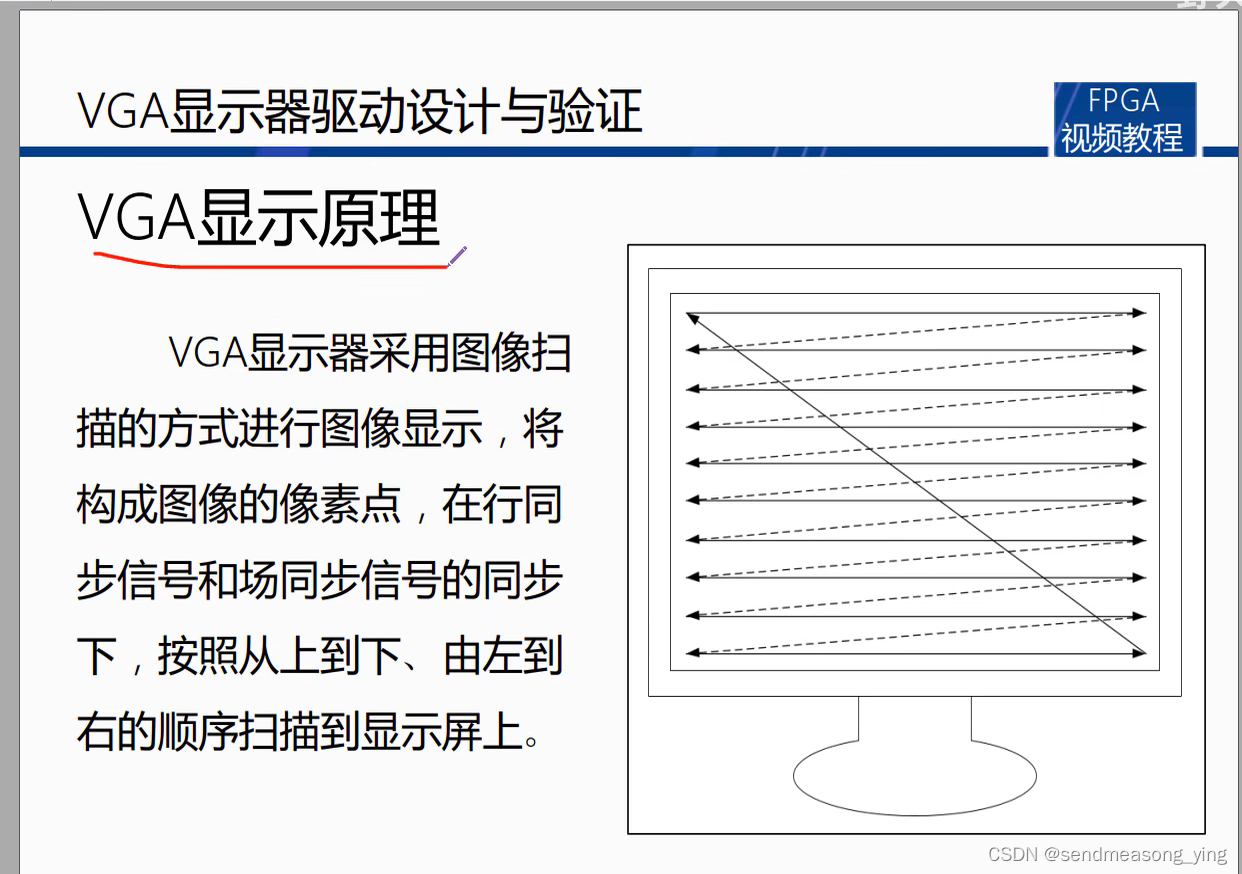

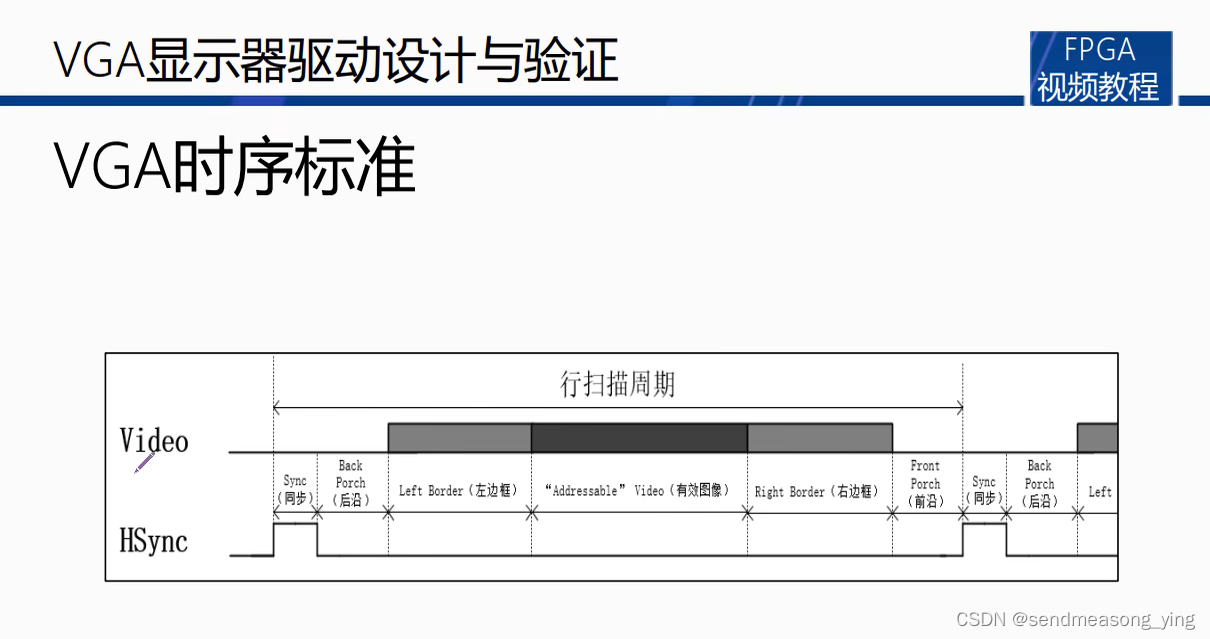

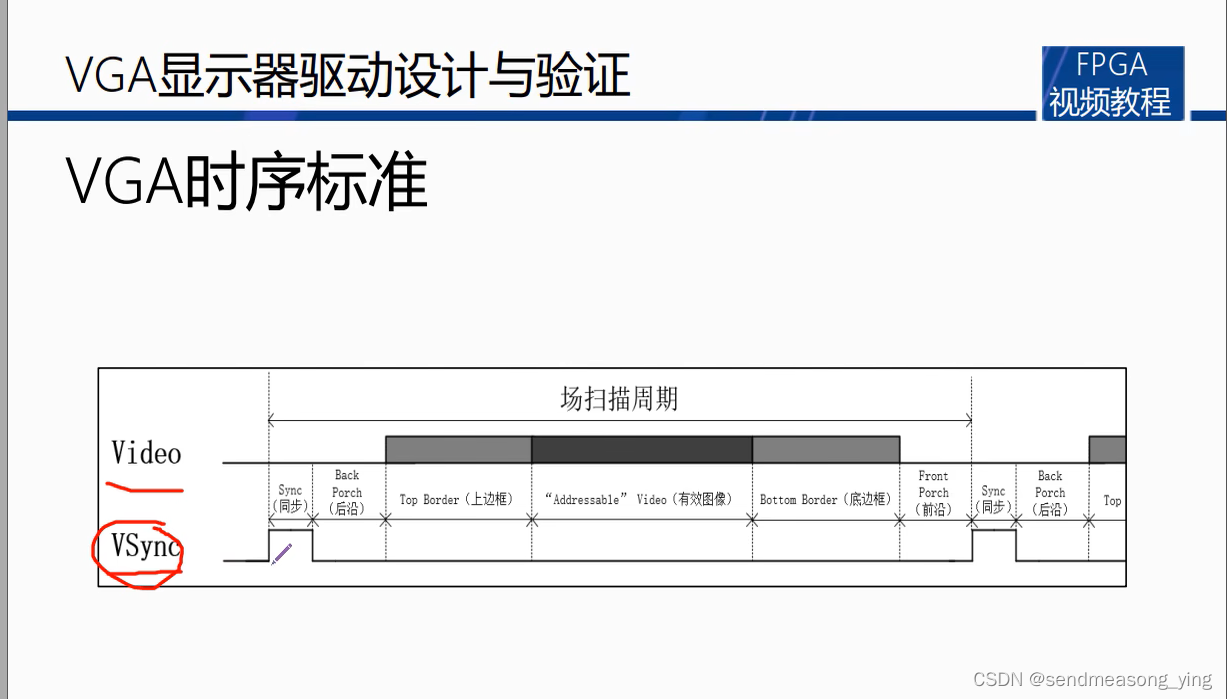

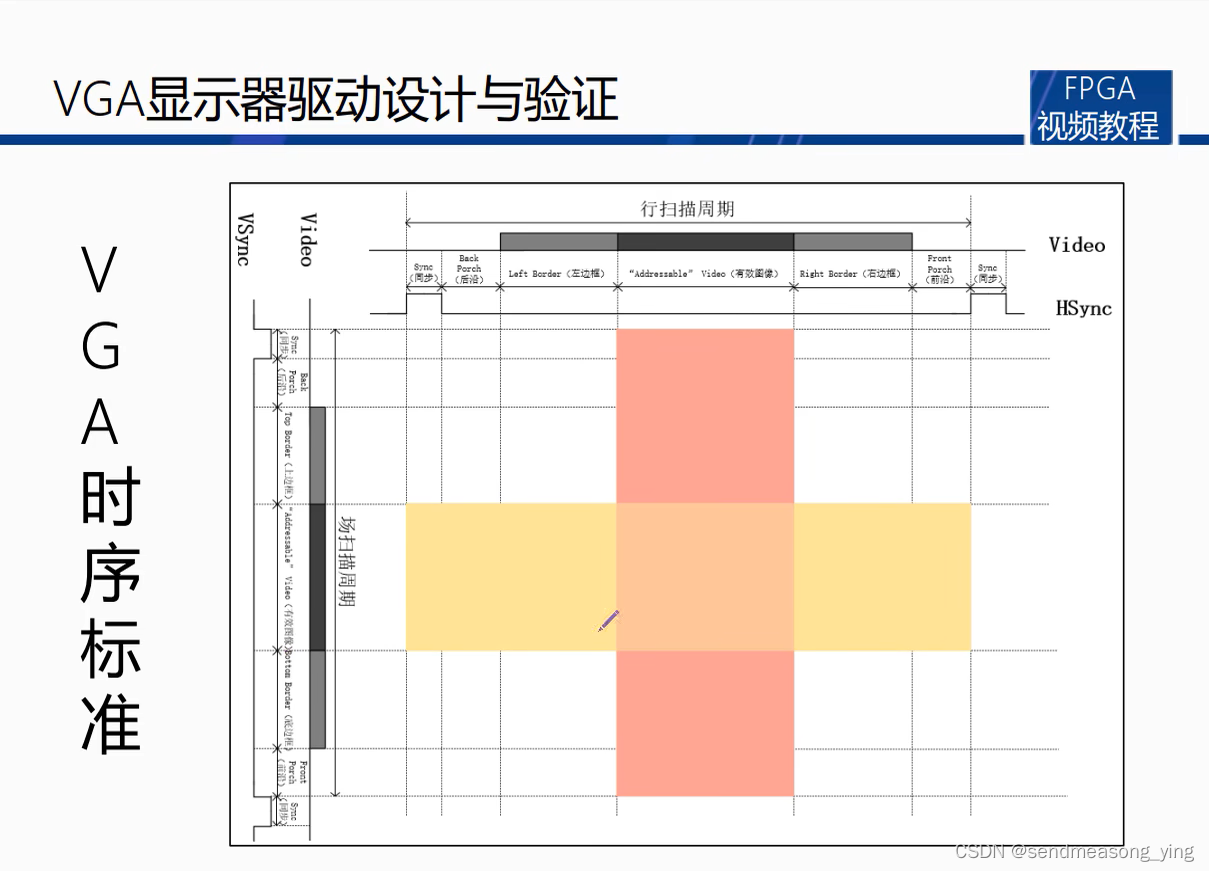

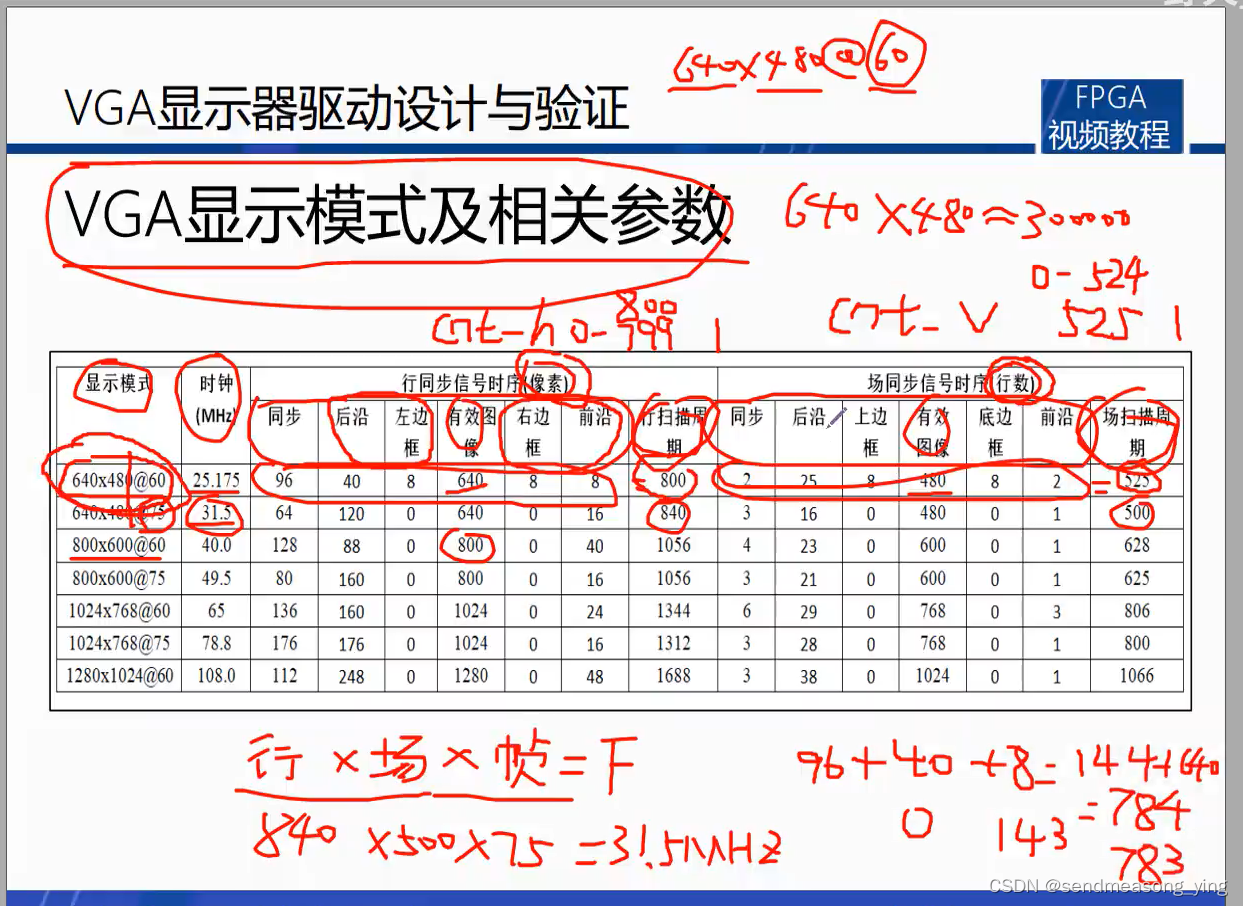

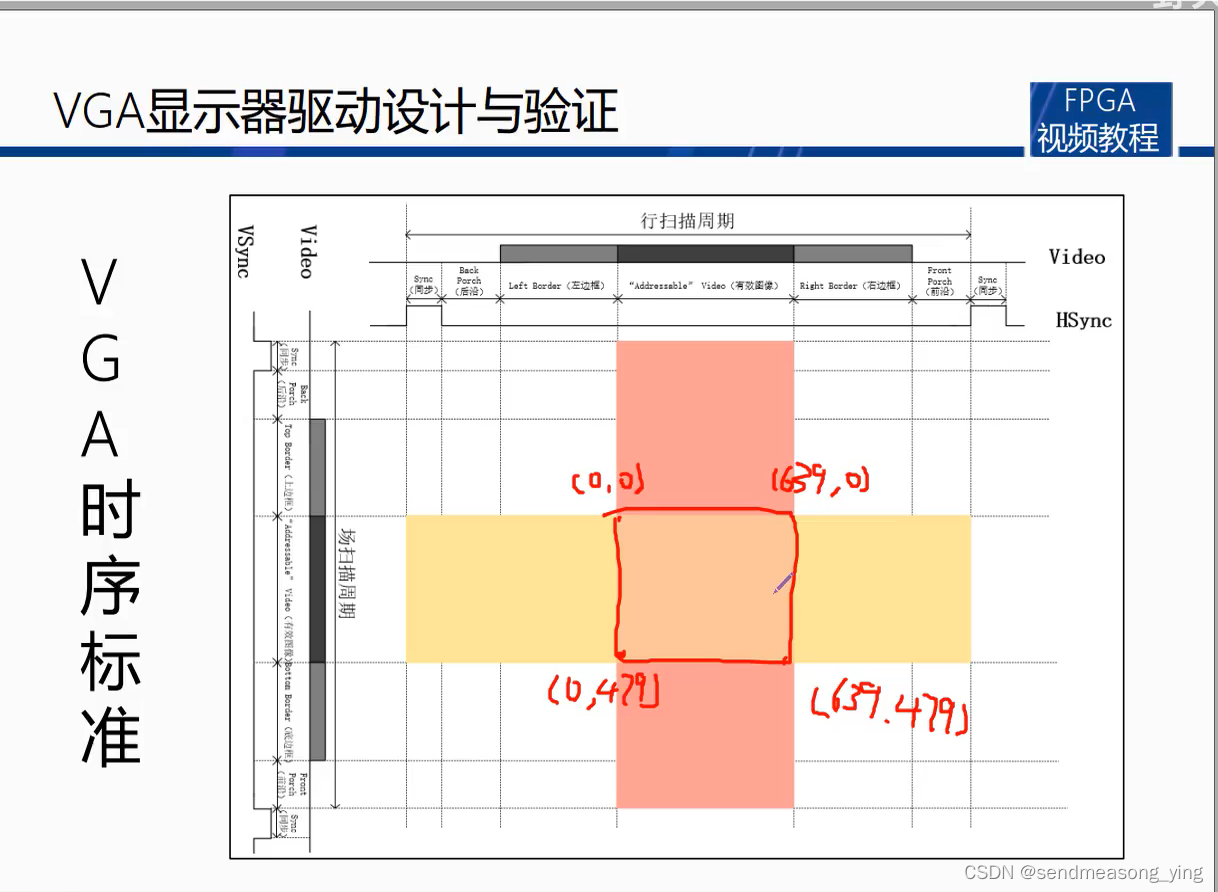

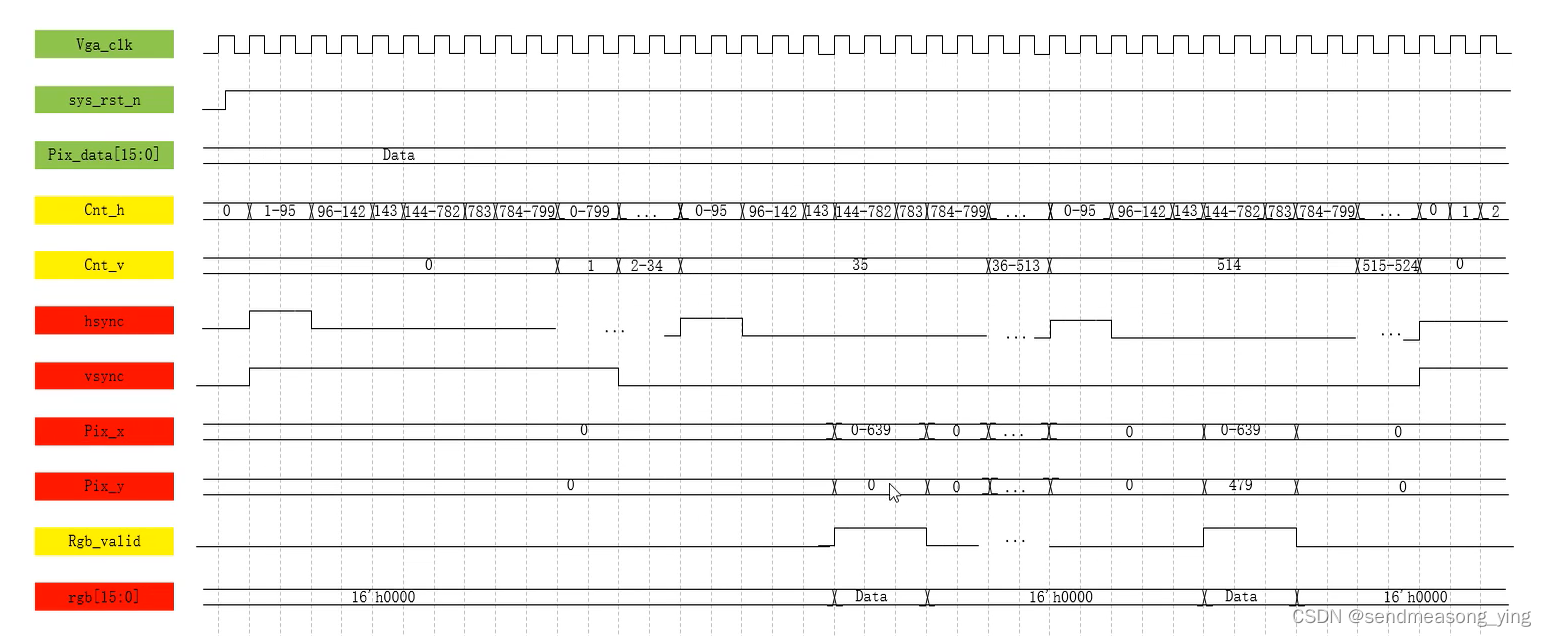

场同步信号的单位是像素点

场同步信号的单位是一行

@60的含义是每秒钟刷新60帧图像

全0表示黑色

2.1 CLK_gen.v

module CLK_gen(input wire sys_clk ,input wire sys_rst_n ,output wire CLK_out ,output wire locked

);parameter STATE=1'b0;

reg [1:0] cnt;

reg flag_clk;assign locked=STATE;

assign CLK_out=flag_clk;always@(posedge sys_clk or negedge sys_rst_n)if(sys_rst_n==1'b0)cnt<=2'b0;else if(cnt==2'd1)cnt<=2'b0;else cnt<=cnt+1'b1;always@(posedge sys_clk or negedge sys_rst_n)if(sys_rst_n==1'b0)flag_clk<=1'b0;else if(cnt==2'd1)flag_clk<=1'b1;elseflag_clk<=1'b0;endmodule2.2 Vga_ctrl.v

module Vga_ctrl(input wire Vga_clk ,input wire sys_rst_n ,input wire [15:0] Pix_data ,output wire [9:0] Pix_x ,output wire [9:0] Pix_y , output wire [15:0] rgb ,output wire hsync ,output wire vsync

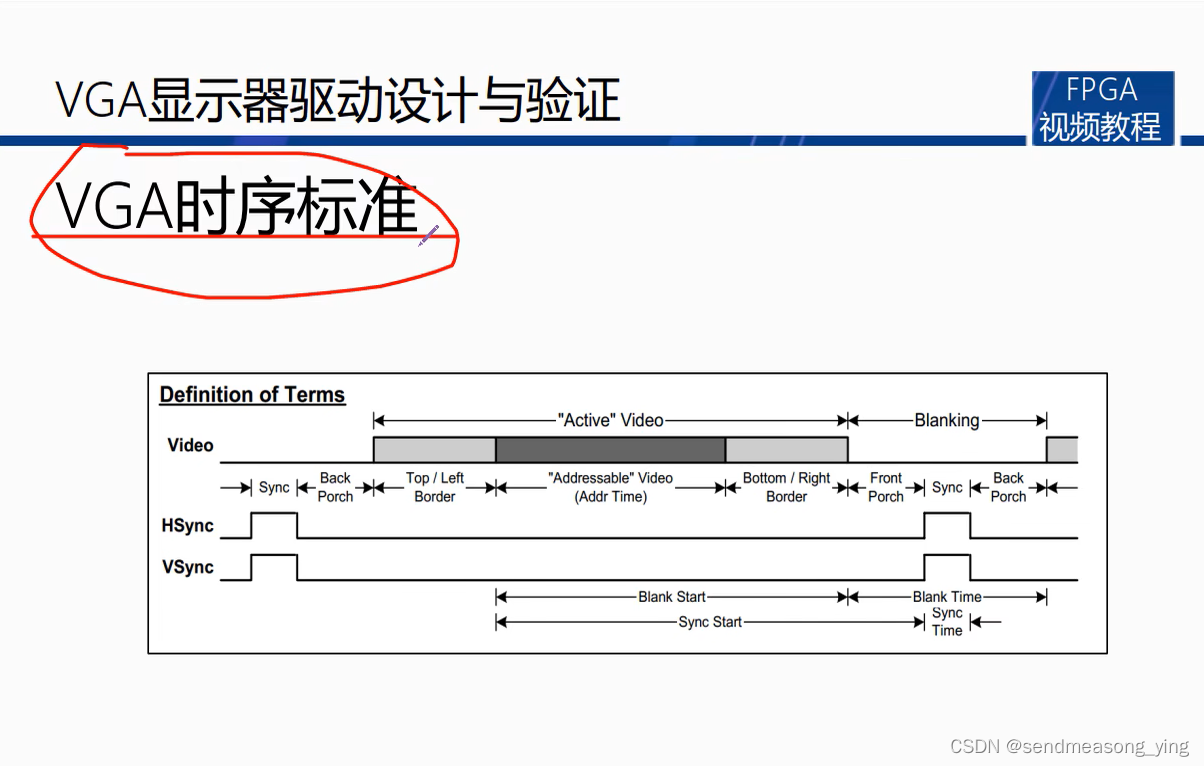

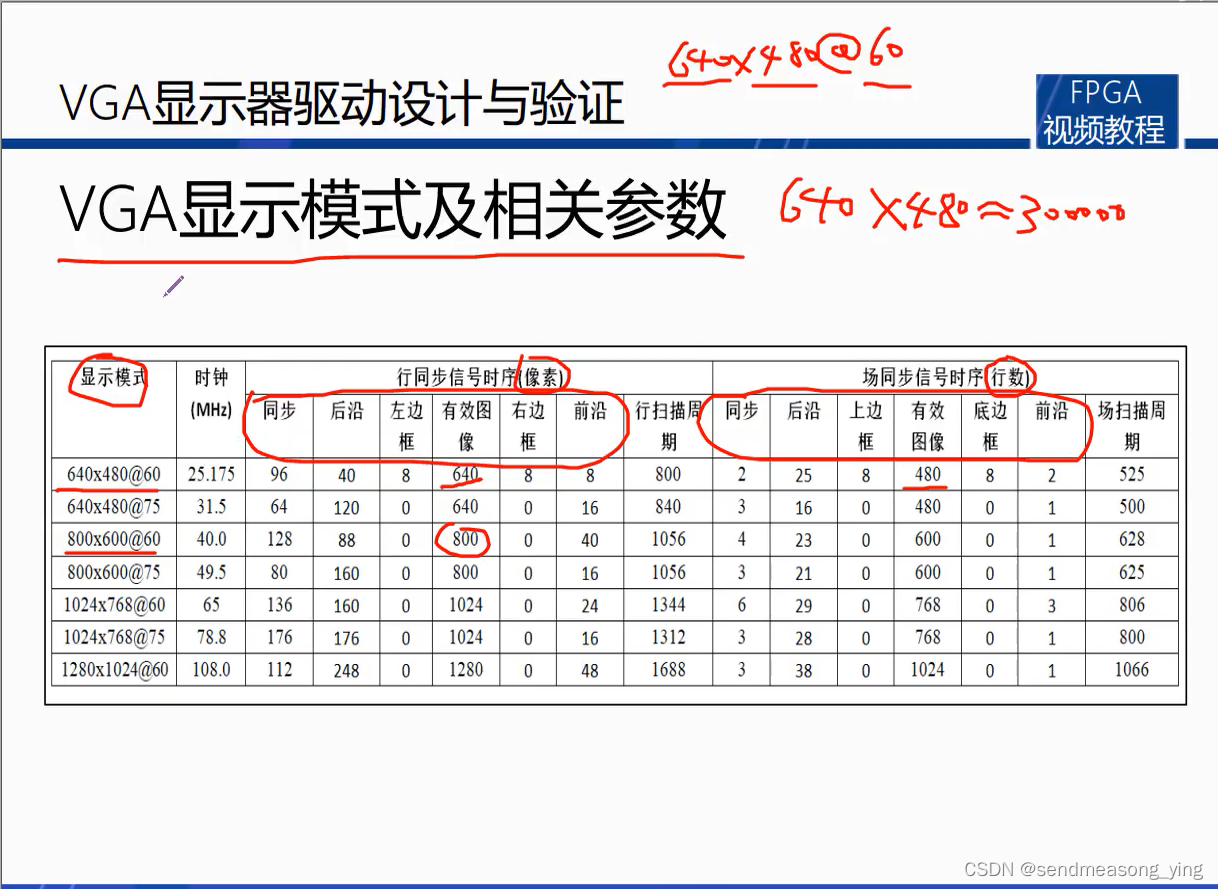

);parameter H_SYNC=10'd96 , H_BACK=10'd40 ,H_LEFT=10'd8 ,H_VALID=10'd640 ,H_RIGHT=10'd8 ,H_FRONT=10'd8 ,H_TOTAL=10'd800 ;parameter V_SYNC=10'd2 ,V_BACK=10'd25 ,V_TOP=10'd8 ,V_VALID=10'd480 ,V_BOTTOM=10'd8 ,V_FRONT=10'd2 ,V_TOTAL=10'd525;reg [9:0] Cnt_h;

reg [9:0] Cnt_v;

wire Rgb_valid;

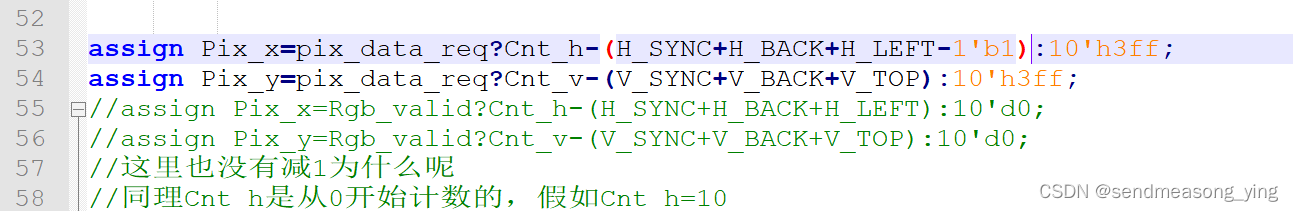

wire pix_data_req;assign Rgb_valid=(Cnt_h>=H_SYNC+H_BACK+H_LEFT&&Cnt_h<H_SYNC+H_BACK+H_LEFT+H_VALID&&Cnt_v>=V_SYNC+V_BACK+V_TOP&&Cnt_v<V_SYNC+V_BACK+V_TOP+V_VALID)?1'b1:1'b0;//这里为什么不减1呢,画个简单的图就知道了//因为前面的时间要满足H_SYNC+H_BACK+H_LEFT,//有效信号是从他们之和加1开始计数的//比如Cnt_h=10,就是计数了11个,//而H_SYNC+H_BACK+H_LEFT=1+2+3=5//所以前面要计满5个,也就是计数到4,10-5=5刚好是大于等于5开始信号有效assign pix_data_req=(Cnt_h>=H_SYNC+H_BACK+H_LEFT-1'b1&&Cnt_h<H_SYNC+H_BACK+H_LEFT+H_VALID-1'b1&&Cnt_v>=V_SYNC+V_BACK+V_TOP&&Cnt_v<V_SYNC+V_BACK+V_TOP+V_VALID)?1'b1:1'b0;assign Pix_x=pix_data_req?Cnt_h-(H_SYNC+H_BACK+H_LEFT-1'b1):10'h3ff;

assign Pix_y=pix_data_req?Cnt_v-(V_SYNC+V_BACK+V_TOP):10'h3ff;

//assign Pix_x=Rgb_valid?Cnt_h-(H_SYNC+H_BACK+H_LEFT):10'd0;

//assign Pix_y=Rgb_valid?Cnt_v-(V_SYNC+V_BACK+V_TOP):10'd0;

//这里也没有减1为什么呢

//同理Cnt_h是从0开始计数的,假如Cnt_h=10

//H_SYNC+H_BACK+H_LEFT=1+2+3=5

//那么此时的行坐标就等于10-5=5,因为前面的0-4是5个周期

//如果此时在H_SYNC+H_BACK+H_LEFT的基础上减1的话

//那么10-4=6,前面就是0-5等于6个时钟周期了,时序不符合assign hsync=(Cnt_h<=H_SYNC-1'b1)?1'b1:1'b0;

assign vsync=(Cnt_v<=V_SYNC-1'b1)?1'b1:1'b0;

//为什么这里要减呢,因为Cnt_h是从0开始计数的,假如说计数到了10,就是0-11

//假如行同步信号是2个时钟周期,那么有效的就是第3个时钟周期,也就是计数到1.

//举个例子就能看出是不是需要减了assign rgb=(Rgb_valid==1'b1)?Pix_data:16'd0;always@(posedge Vga_clk or negedge sys_rst_n )if(sys_rst_n==1'b0)Cnt_h<=10'd0;else if(Cnt_h==H_TOTAL-1'b1)Cnt_h<=10'd0;elseCnt_h<=Cnt_h+1'b1;always@(posedge Vga_clk or negedge sys_rst_n )if(sys_rst_n==1'b0)Cnt_v<=10'd0;else if((Cnt_v==V_TOTAL-1'b1)&&(Cnt_h==H_TOTAL-1'b1))Cnt_v<=10'd0;else if(Cnt_h==H_TOTAL-1'b1)Cnt_v<=Cnt_v+1'b1;elseCnt_v<=Cnt_v;endmodule2.3 tb_Vga_ctrl.v

module tb_Vga_ctrl();reg sys_clk;

reg sys_rst_n ;

reg[15:0] Pix_data ;wire [9:0] Pix_x ;

wire [9:0] Pix_y ;

wire [15:0]rgb ;

wire hsync ;

wire vsync ;

wire CLK_out ;

wire locked ;

wire rst_n;initial beginsys_clk=1'b1;sys_rst_n<=1'b0;#20sys_rst_n=1'b1;end assign rst_n=(sys_rst_n&&locked);always#10 sys_clk=~sys_clk;always@(posedge CLK_out or negedge rst_n)if(rst_n==1'b0)Pix_data<=16'h0000;else if (Pix_x>=10'd0&&Pix_x<=10'd639&&Pix_y>=10'd0&&Pix_y<=10'd479)Pix_data<=16'hffff;elsePix_data<=16'h0000;defparam CLK_gen_inst.STATE=1'b1; Vga_ctrl Vga_ctrl_inst(.Vga_clk (CLK_out) ,.sys_rst_n (rst_n),.Pix_data (Pix_data),.Pix_x (Pix_x ),.Pix_y (Pix_y ), .rgb (rgb ) ,.hsync (hsync ),.vsync (vsync )

);CLK_gen CLK_gen_inst(.sys_clk (sys_clk ) ,.sys_rst_n (sys_rst_n ),.CLK_out (CLK_out ) ,.locked (locked )

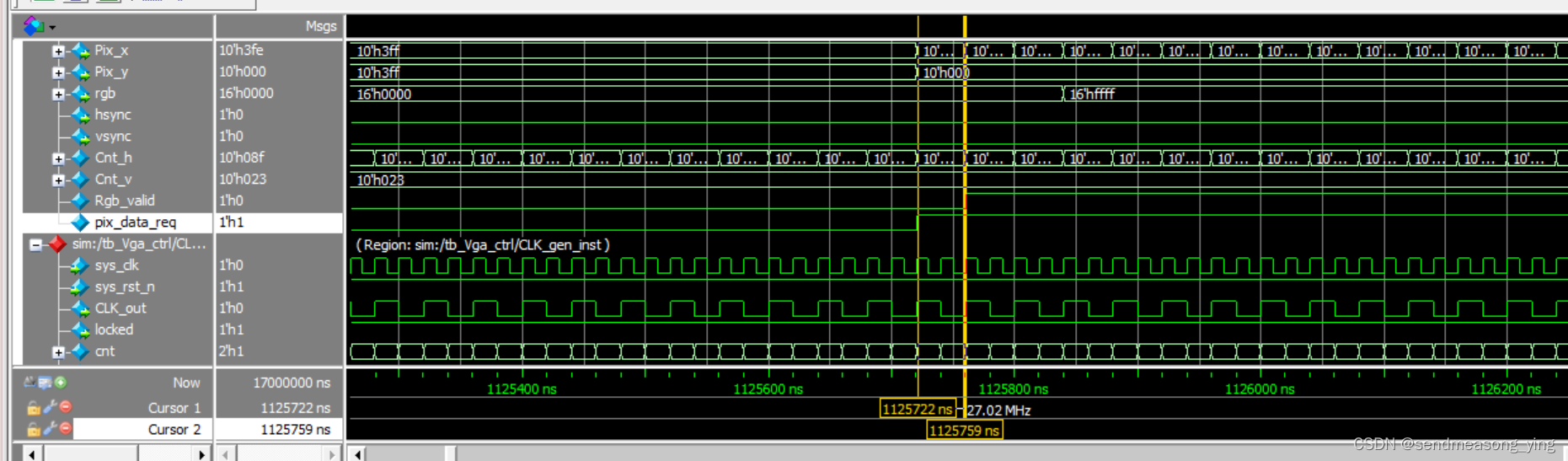

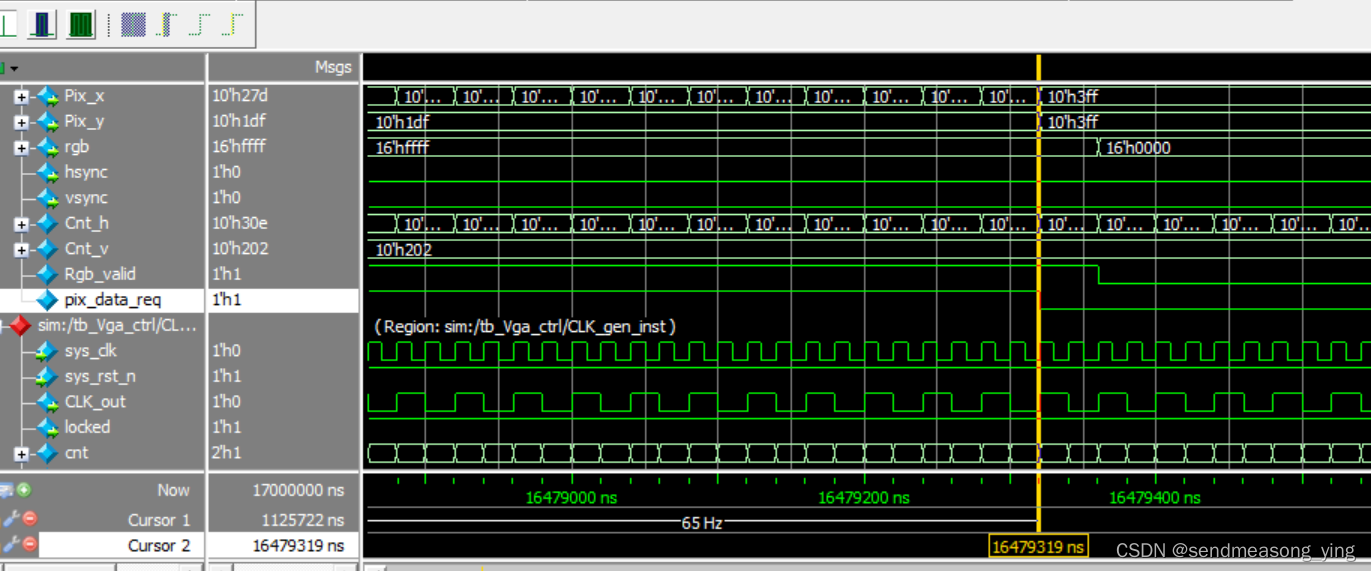

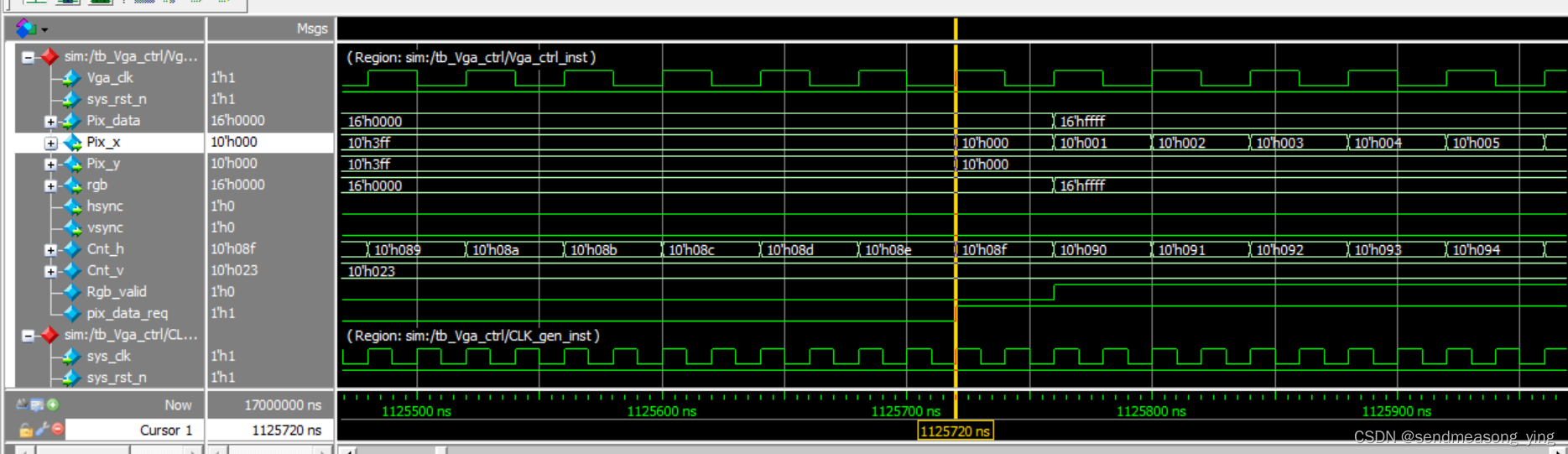

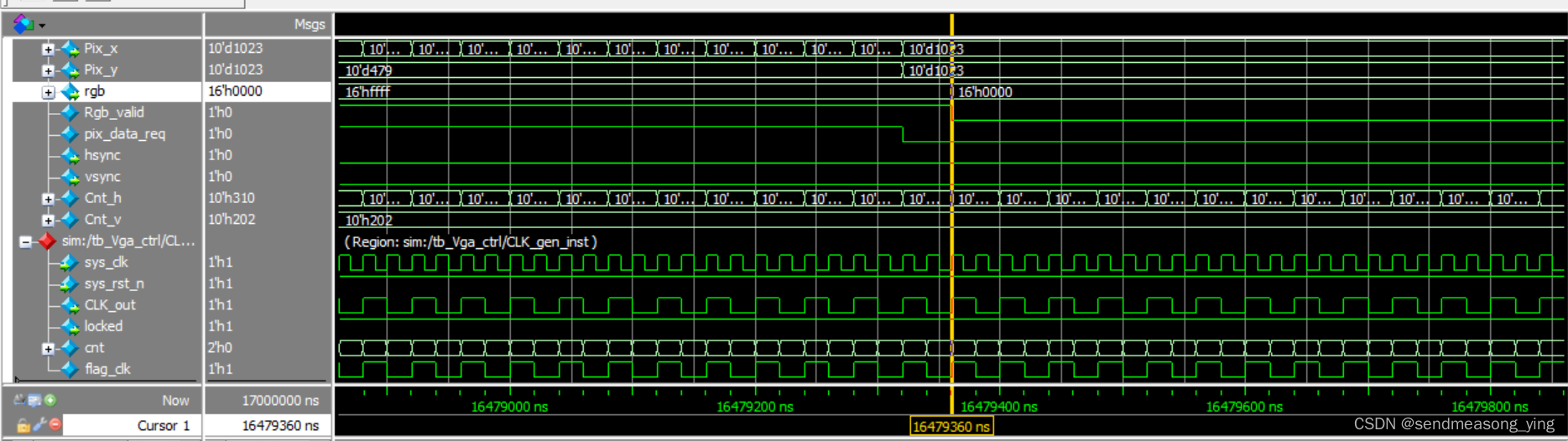

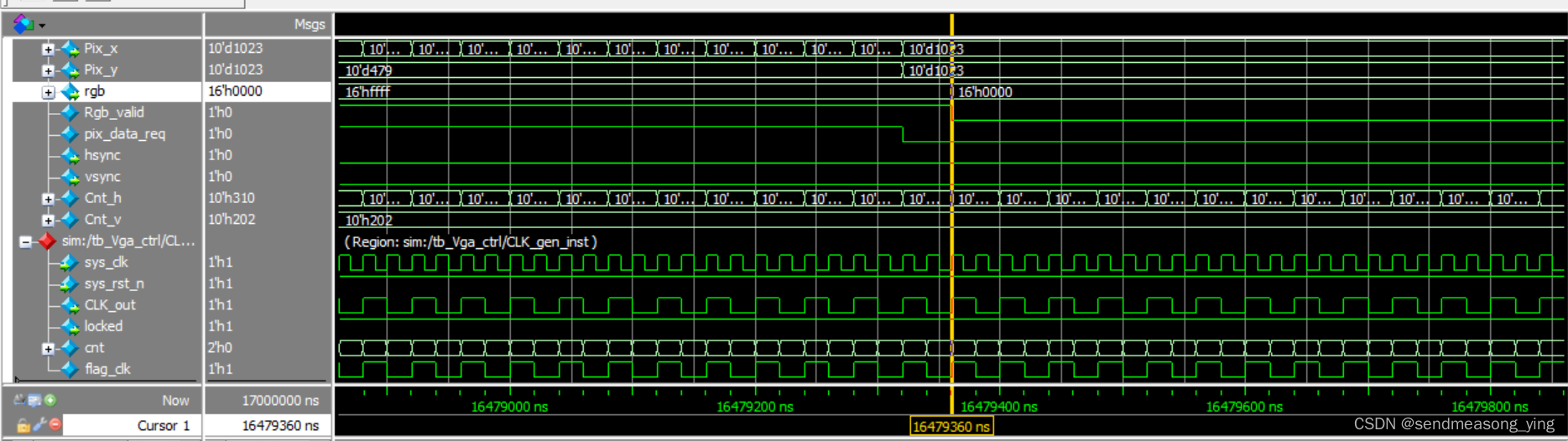

);endmodule要显示1帧图像,1s是60帧,1帧就是0.0167s,所以等于16.7ms

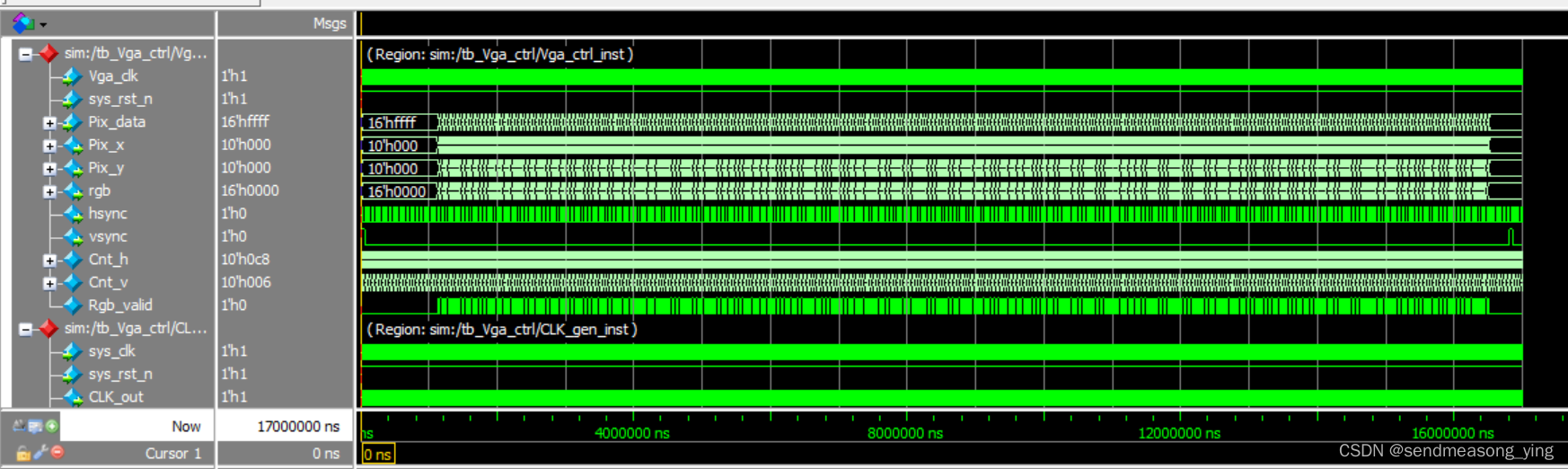

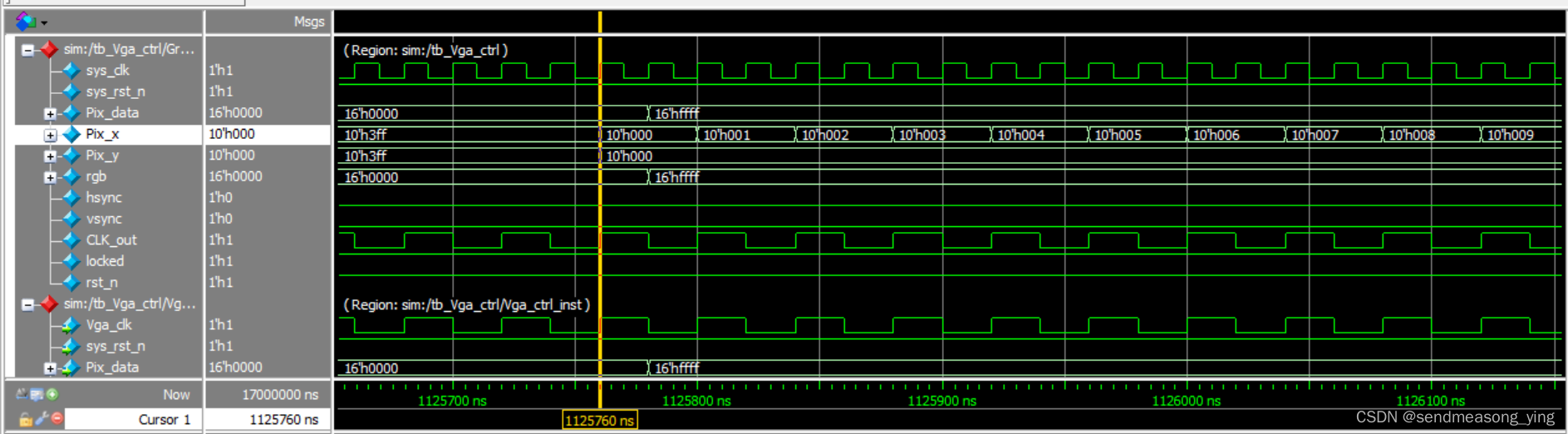

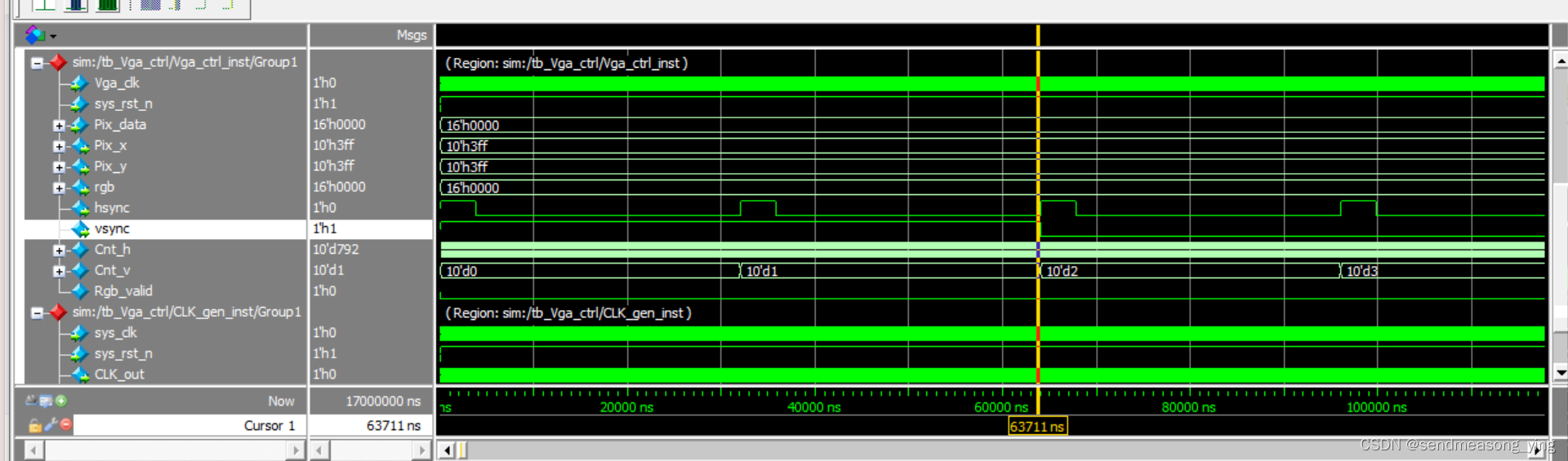

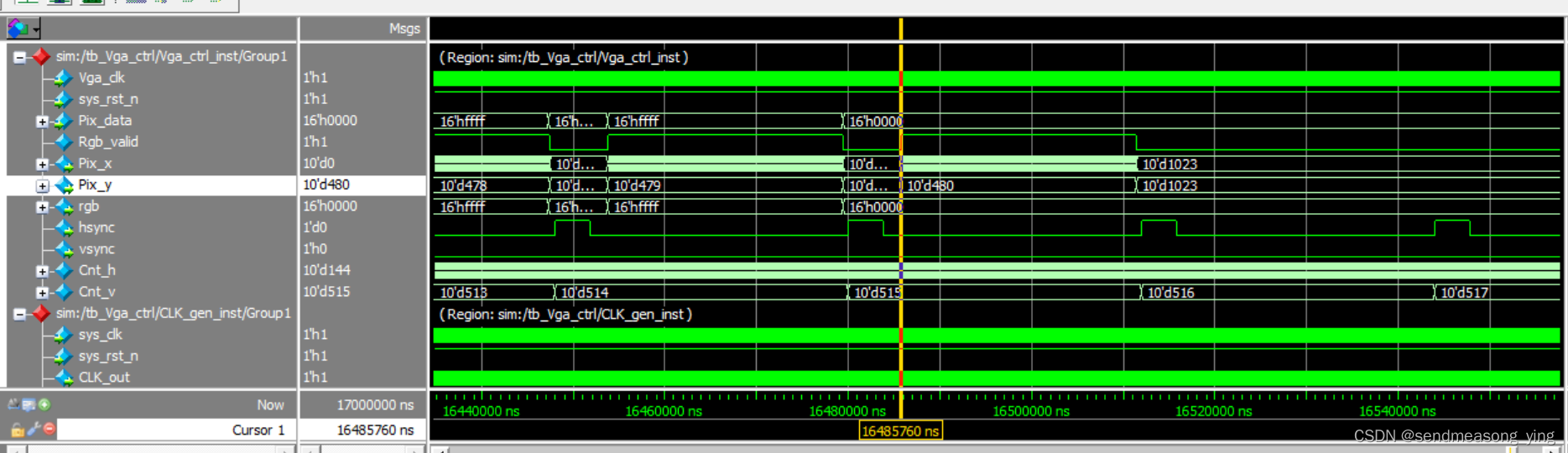

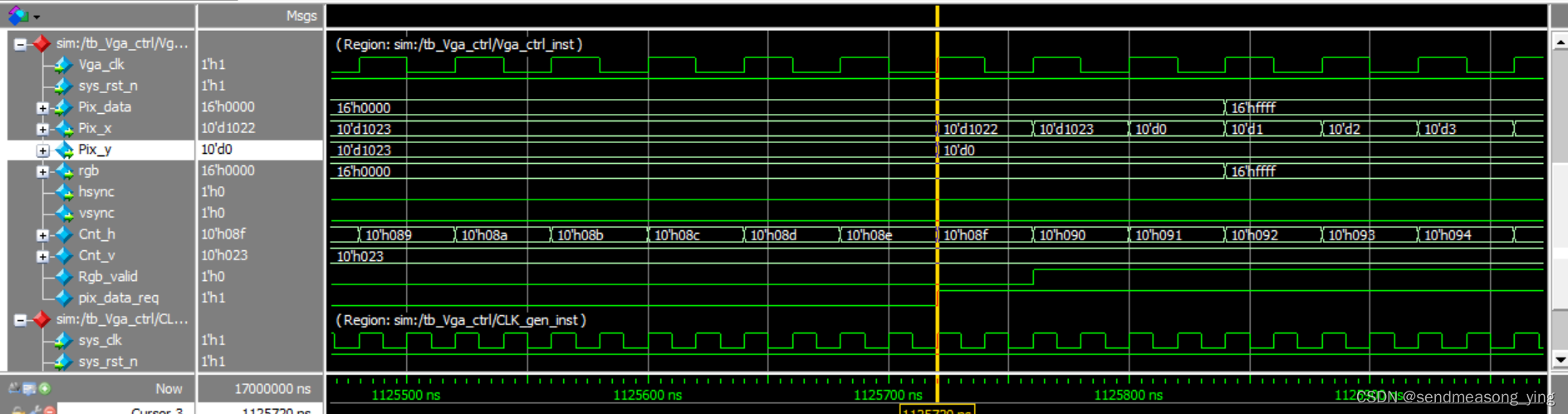

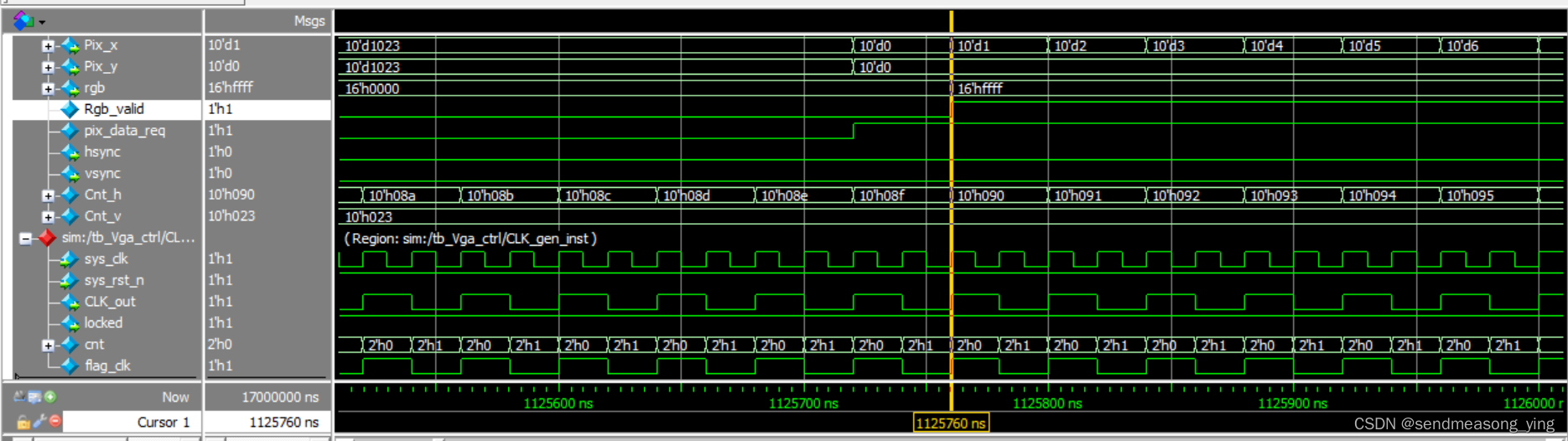

时钟正确25mhz,锁定信号是拉高的,表示锁定信号在高电平时,时钟的输出有效,因为若锁定信号为0,那么复位信号就一直为0,时钟就起不了作用。

复位信号为0,数据就为0,坐标信号大于等于0且小于一定范围就为全为白色ffff。否则就全为0。

完成一帧

场同步信号也正确。

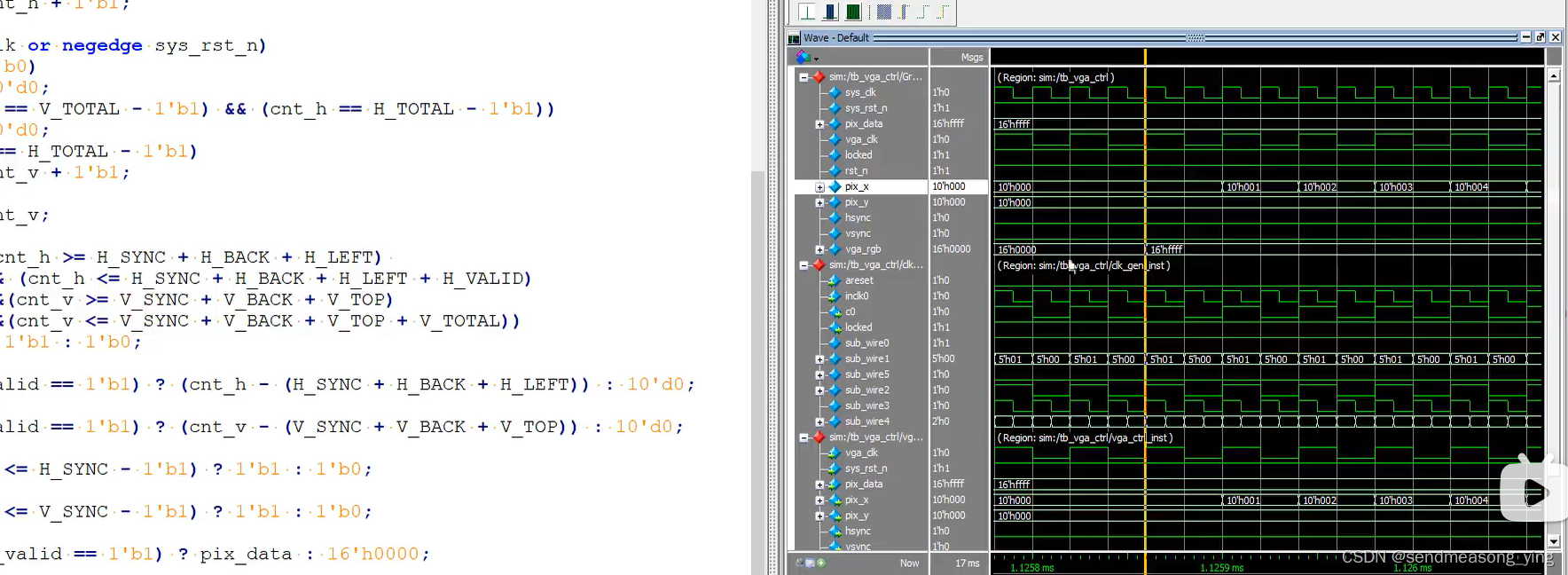

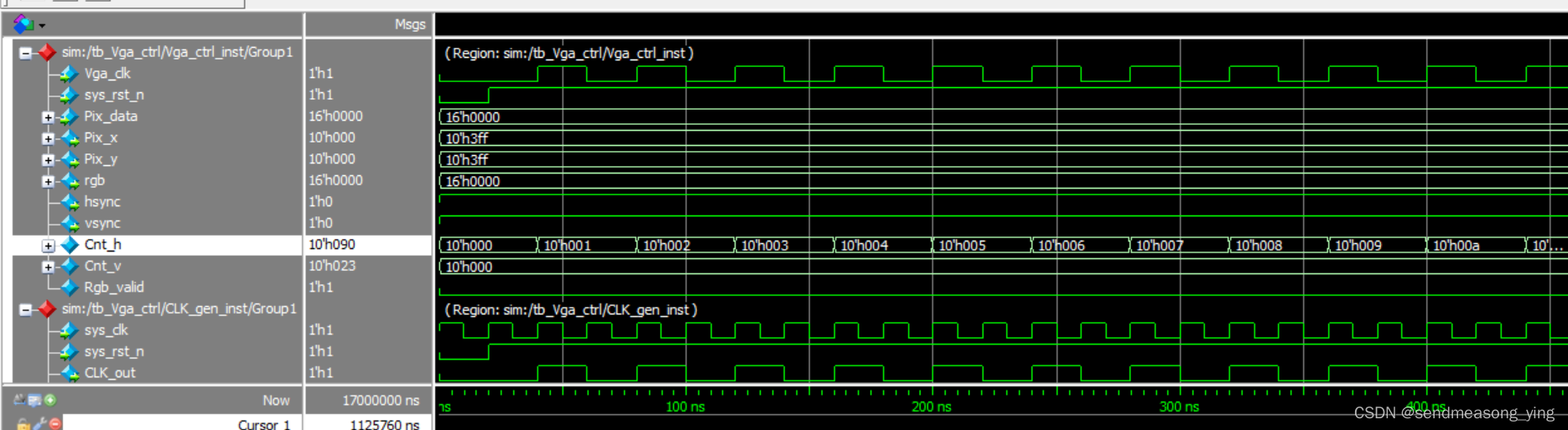

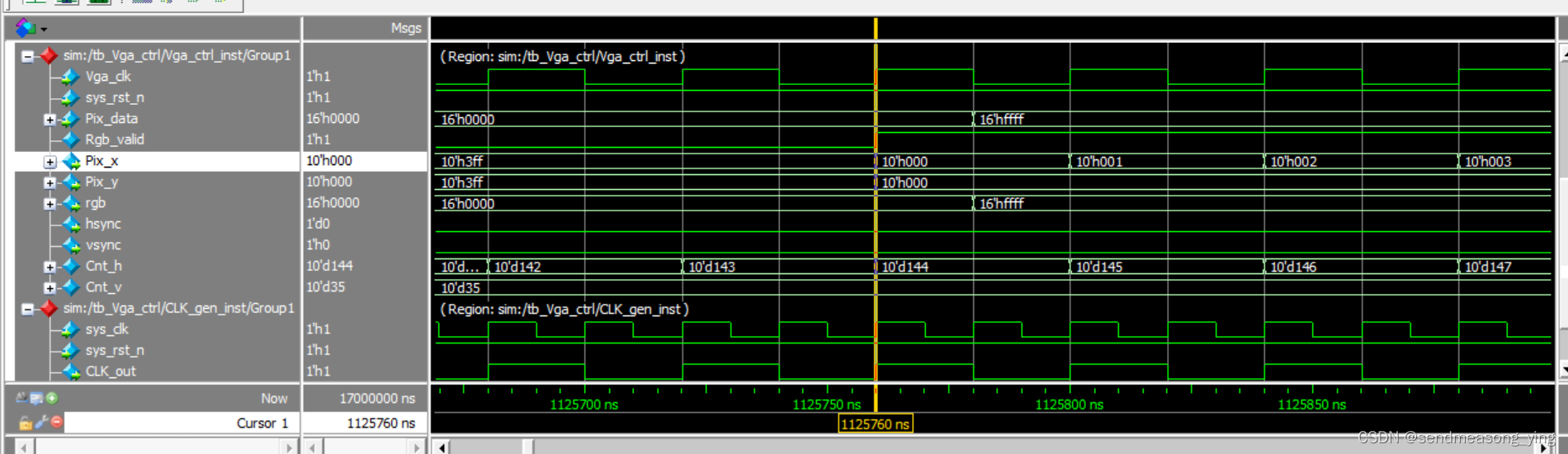

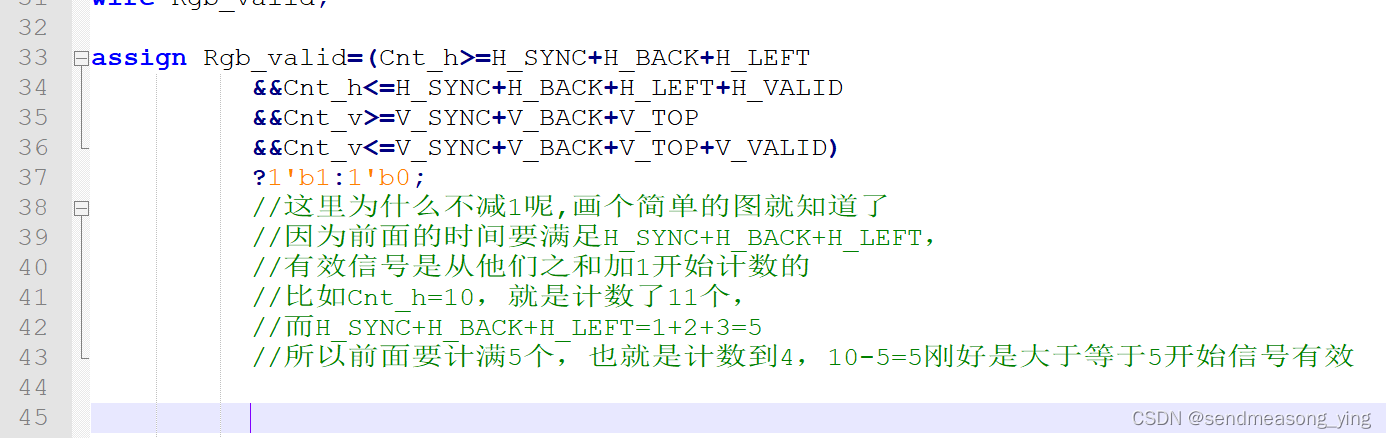

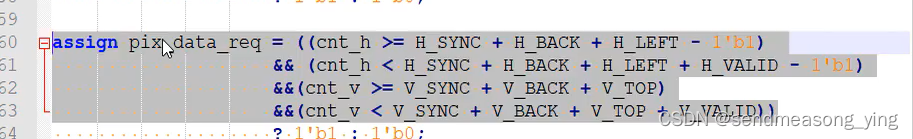

这里有错。因为有效信号多记了一个时钟周期

因此这里要修改数据有效信号

现在计数正确了

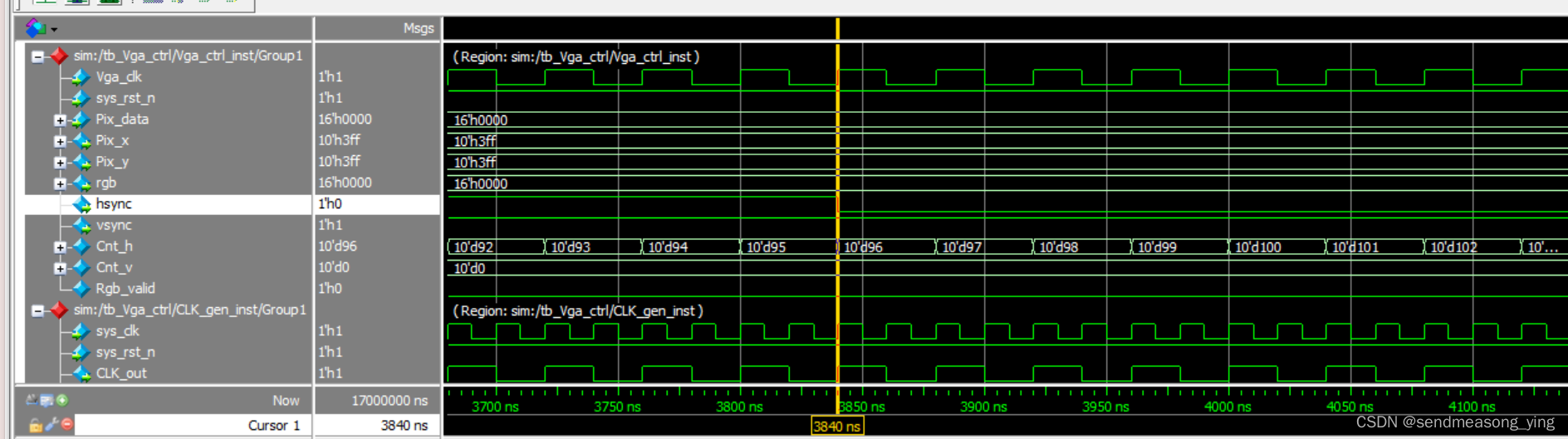

修改时钟换成分频后的信号

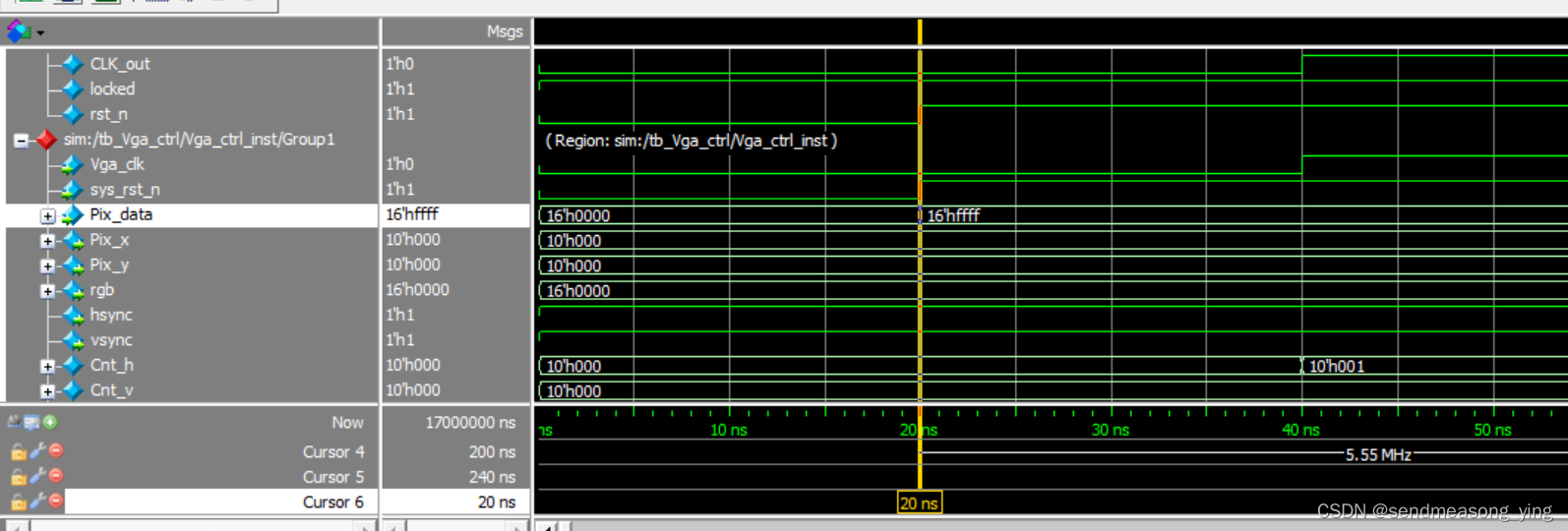

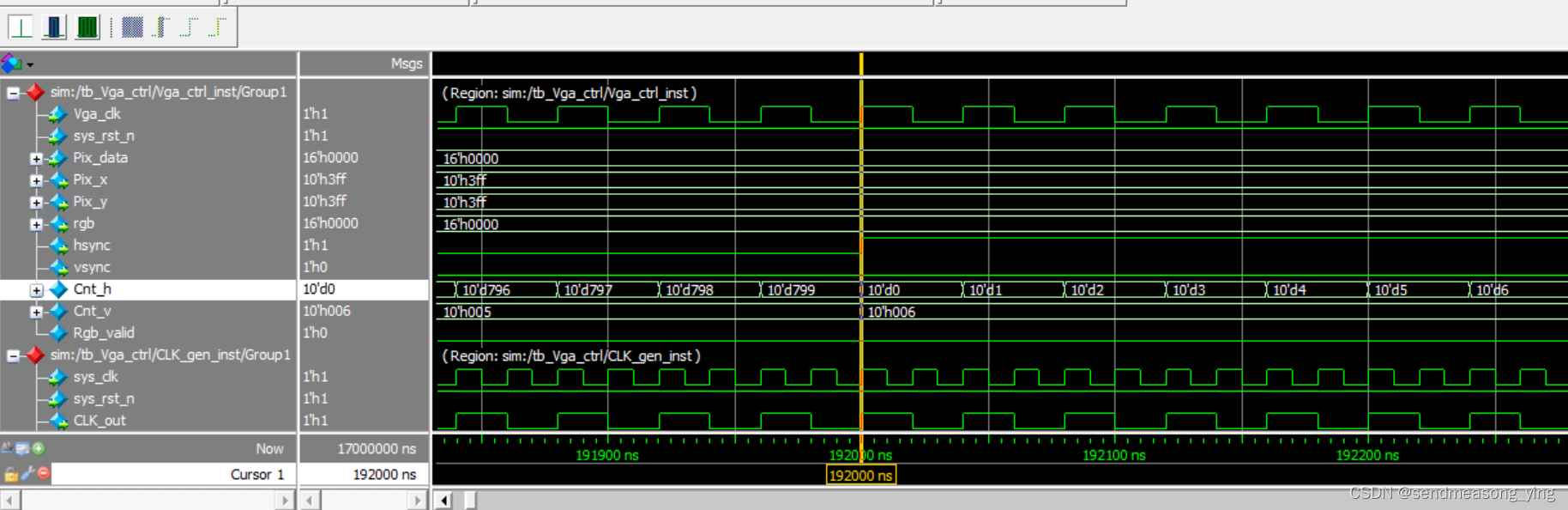

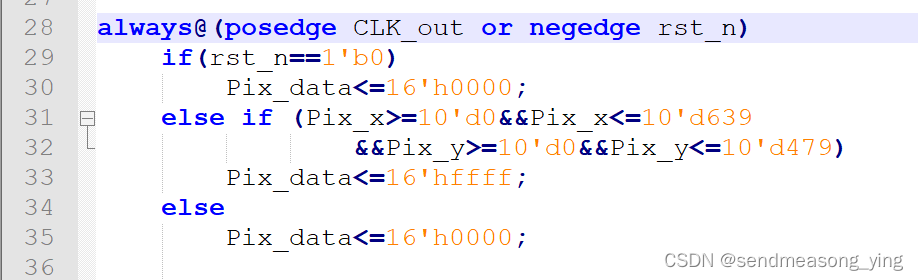

还是有问题,当数据有效时,数据仍为0。说明数据滞后数据有效信号一个时钟周期,所以得让数据提前一个时钟周期,解决方法是增加一个数据请求信号,比数据有效信号提前1时钟周期,然后rgb刚好滞后数据请求信号一个时钟周期。就达到了rgb和数据有效信号同步得效果。

末尾没有问题,原因是因为是时序逻辑,修改代码

行可以超前,但是场不用,场超前就是超前一行了,而行超前就是超前一个时钟周期。这里修改是要将pix_x超前一个时钟周期,然后再pi_data滞后一个周期,从而达到同步的效果

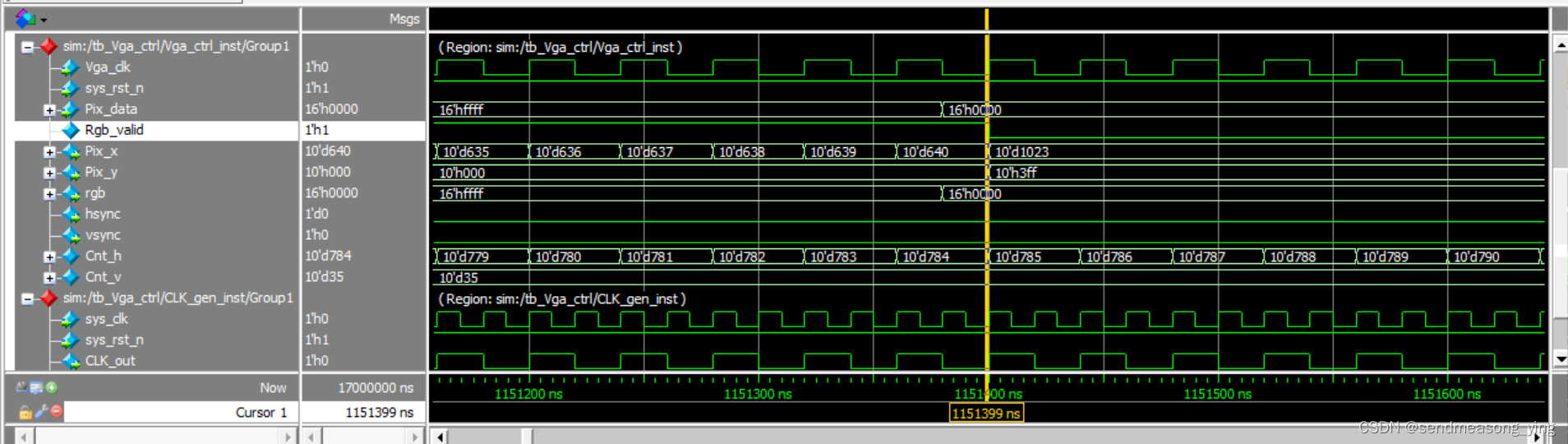

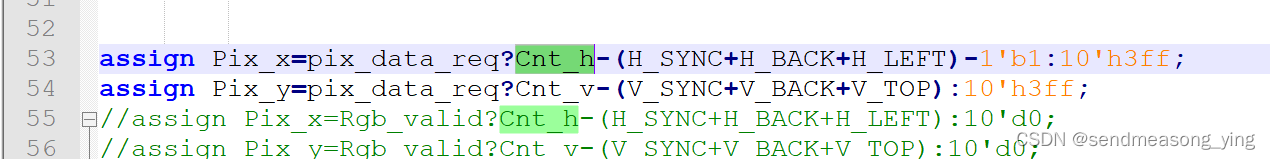

行计数器这里也要减1

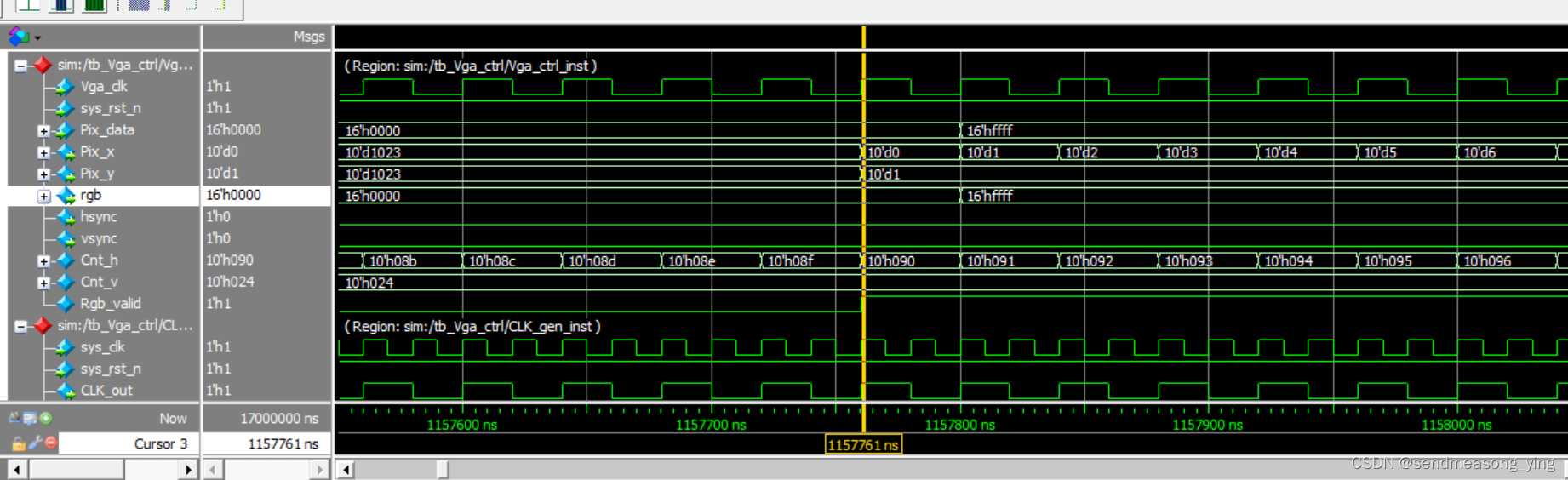

请求信号确实超前有效信号一个时钟周期

末尾也正确

但是坐标还是不对

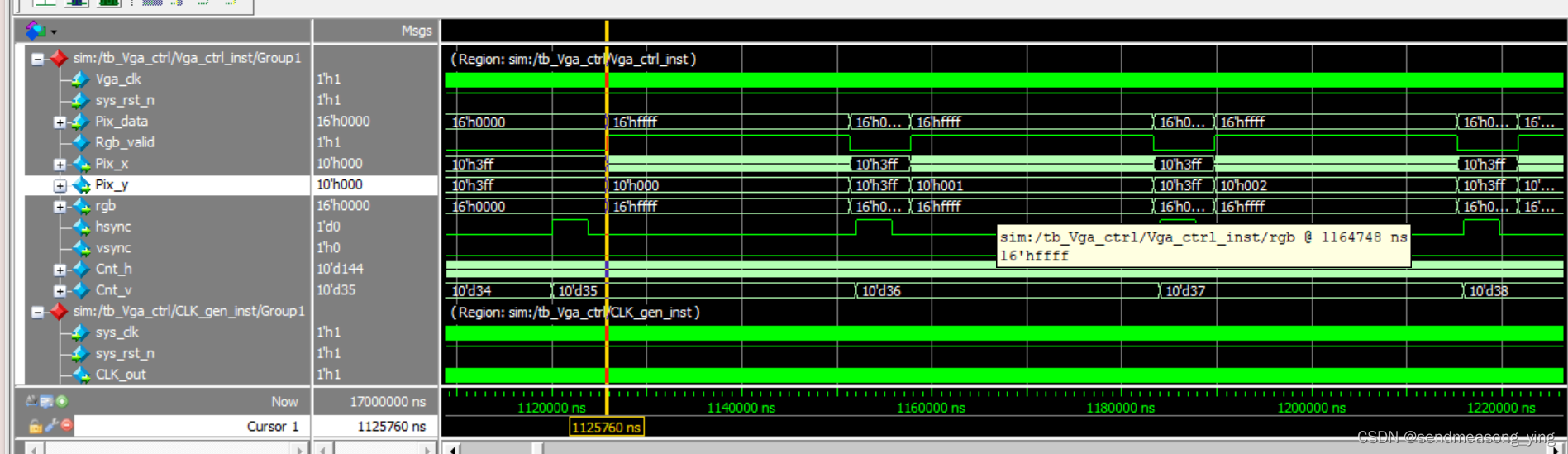

这下对了,为什么要让括号里面的信号减1呢?因为pix_data_req比数据有效信号提前了一个时钟周期,如果按照原来的不减1,那么坐标就会变小,提前数据有效信号一个时钟周期,要让坐标不变,就得让计数得值变大,所以减1。

数据和有效信号是同步的

相关文章:

VGA显示器驱动设计与验证

1.原理 场同步信号的单位是像素点 场同步信号的单位是一行 60的含义是每秒钟刷新60帧图像 全0表示黑色 2.1 CLK_gen.v module CLK_gen(input wire sys_clk ,input wire sys_rst_n ,output wire CLK_out ,output wire locked );parameter STATE1b0; reg [1:0] cnt; r…...

jupyter notebook 配置默认文件路径

Jupyter是一种基于Web的交互式计算环境,支持多种编程语言,如Python、R、Julia等。使用Jupyter可以在浏览器中编写和运行代码,同时还可以添加Markdown文本、数学公式、图片等多种元素,非常适合于数据分析、机器学习等领域。 安装 …...

强大缓存清理工具 NetShred X for Mac激活版

NetShred X for Mac是一款专为Mac用户设计的强大缓存清理工具,旨在帮助用户轻松管理和优化系统性能。这款软件拥有直观易用的界面,即使是初次使用的用户也能快速上手。 软件下载:NetShred X for Mac激活版下载 NetShred X能够深入扫描Mac系统…...

在ssh 工具 Linux screen会话中使用鼠标进行上下滚动

经过几次发现 除xshell外, WindTerm finalshell MobaXterm 都是进入会话后,发现其界面无法滚动屏幕向上查看 如果想要在Linux screen会话中使用鼠标进行上下滚动。必须首先进入该screen的回滚(scrollback模式)才能进行上下滚动 第一步ÿ…...

Github2024-04-03 开源项目日报 Top10

根据Github Trendings的统计,今日(2024-04-03统计)共有10个项目上榜。根据开发语言中项目的数量,汇总情况如下: 开发语言项目数量Python项目4TypeScript项目2Jupyter Notebook项目2C++项目1Shell项目1Go项目1非开发语言项目1Rust项目1从零开始构建你喜爱的技术 创建周期:21…...

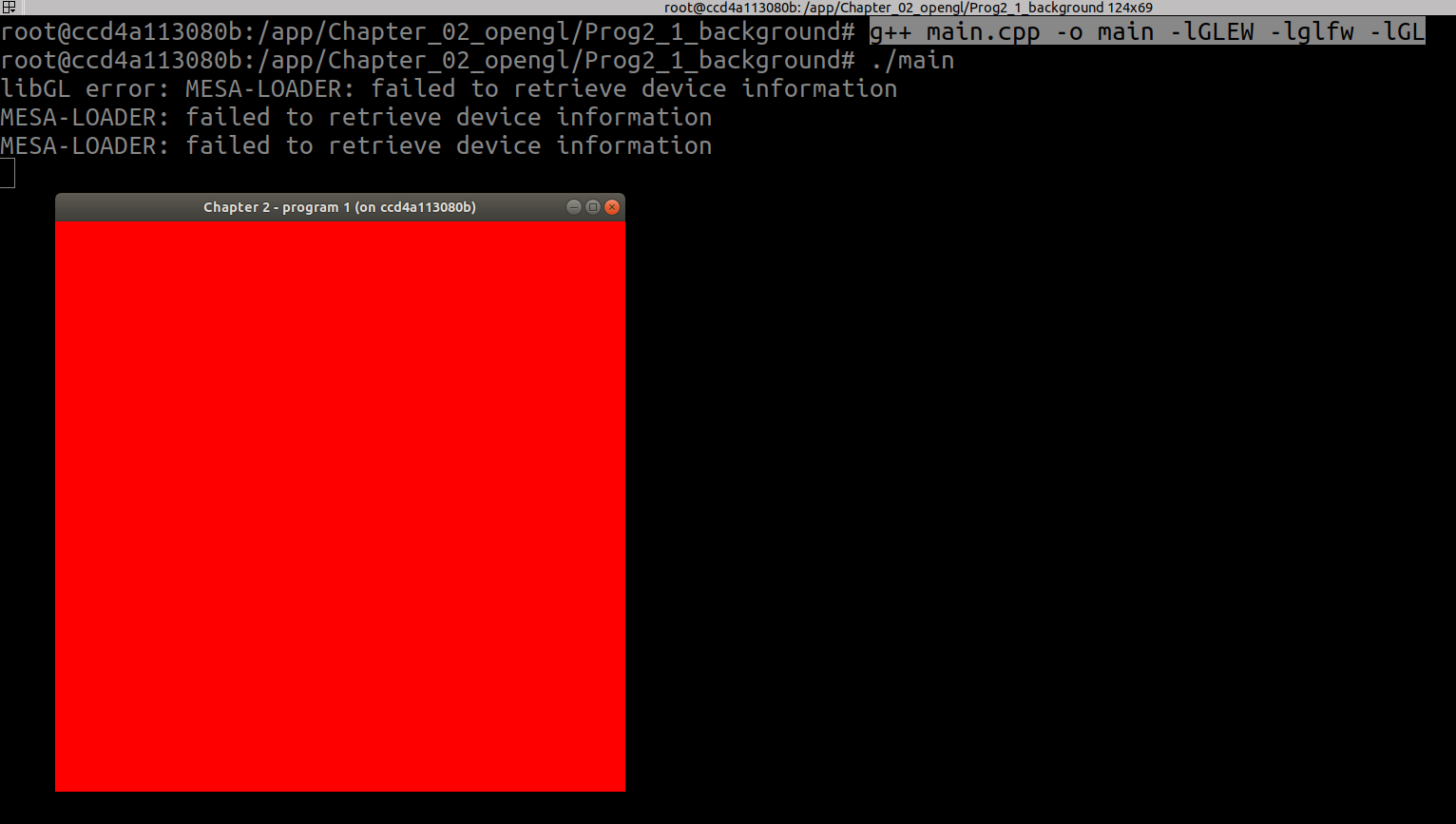

Linux笔记之制作基于ubuntu20.4的最小OpenGL C++开发docker镜像

Linux笔记之制作基于ubuntu20.4的最小OpenGL C开发docker镜像 —— 2024-04-03 夜 code review! 文章目录 Linux笔记之制作基于ubuntu20.4的最小OpenGL C开发docker镜像1.这里把这本书的例程代码放在了Dockerfile所在的文件夹内以使镜像预装例程代码2.创建Dockerfile3.构建Do…...

企业为什么选择高防服务器?

高防服务器顾名思义就是一种具有高度安全性的服务器,有着很高的防御能力,可以提供更加安全可靠的服务,能够有效地避免分布式拒绝服务攻击和其它的网络安全威胁,以下就是企业选择高防服务器的原因。 高防服务器在硬件安全方面有着很…...

OpenHarmony实战:轻量级系统之配置其他子系统

除上述子系统之外,还有一些必要但是无需进行移植的子系统。如:分布式任务调度子系统、DFX子系统。 这些子系统添加方式比较简单,在“vendor/MyVendorCompany/MyProduct/config.json”文件中进行如下配置即可: {"subsystem&…...

关于VueCli项目中如何加载调试Worker和SharedWorker

安装Webpack插件 VueCli 项目中默认是没有加载 worker 的配置,需要额外安装 webpack 插件来实现,让我们开始安装 worker-loader 插件 # npm npm install worker-loader # pnpm pnpm install worker-loader # yarn yarn add worker-loader配置Webpack插…...

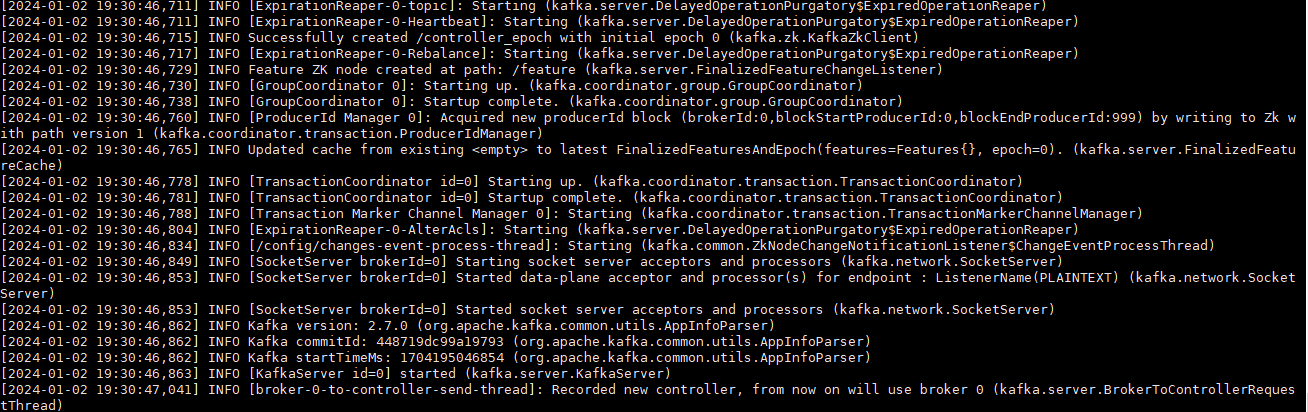

Centos7安装单机版Kafka

下载 链接:https://pan.baidu.com/s/1W8lVEF6Y-xlg6zr3l9QAbg?pwdhbkt 提取码:hbkt 上传到服务器/opt目录 安装 # kafka安装目录为 /opt/kafka cd /opt; mkdir kafka; mv kafka_2.13-2.7.0.tgz ./kafka;cd kafka; #解压 tar -zxvf kafka_2.13-2.7.0…...

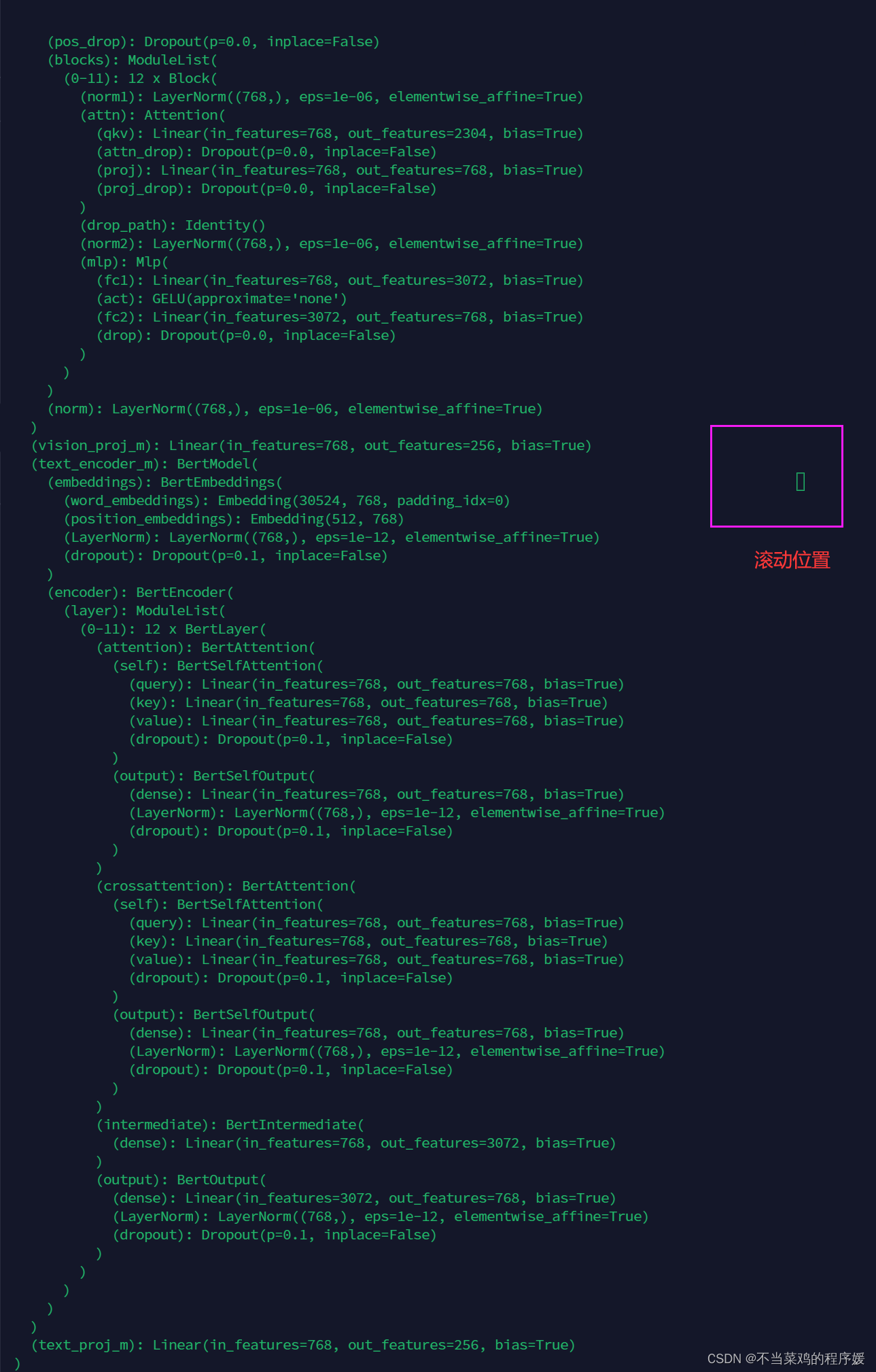

基于深度学习的钢材表面缺陷检测系统(网页版+YOLOv8/v7/v6/v5代码+训练数据集)

摘要:本文深入研究了基于YOLOv8/v7/v6/v5的钢材表面缺陷检测系统,核心采用YOLOv8并整合了YOLOv7、YOLOv6、YOLOv5算法,进行性能指标对比;详述了国内外研究现状、数据集处理、算法原理、模型构建与训练代码,及基于Strea…...

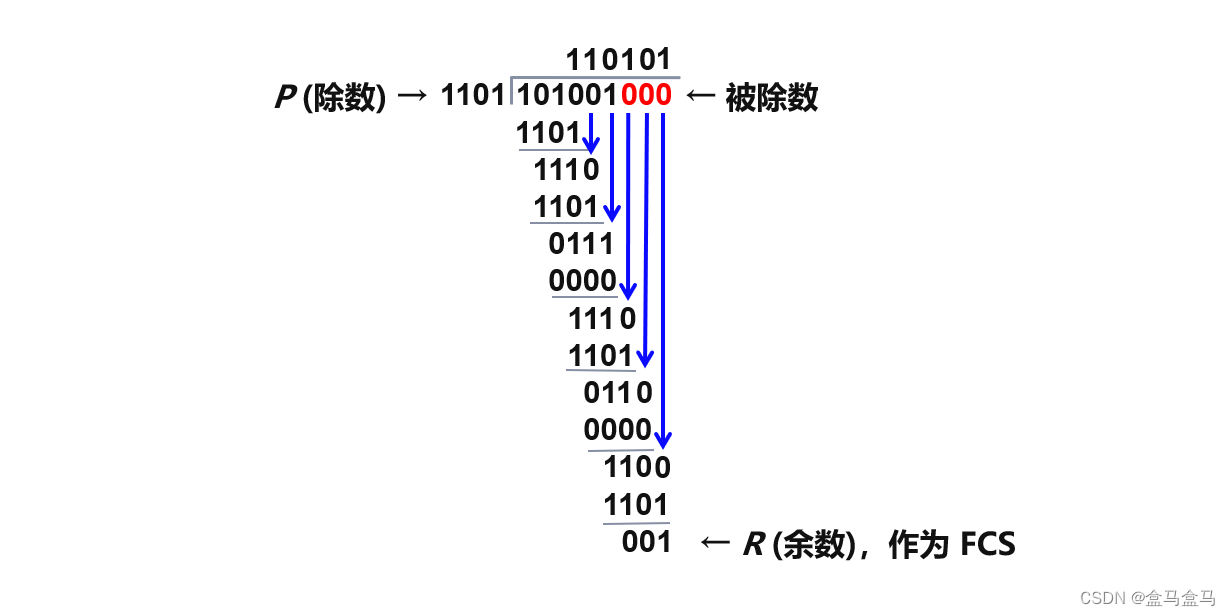

计算机网络:数据链路层 - 点对点协议PPP

计算机网络:数据链路层 - 点对点协议PPP PPP协议的帧格式透明传输字节填充法零比特填充法 差错检测循环冗余校验 对于点对点链路,PPP协议是目前使用最广泛的数据链路层协议。比如说,当用户想要接入互联网,就需要通过因特网服务提供…...

Springboot集成token认证

一、引出session问题以及token、鉴权 session都是保存在内存中,认证用户增多,服务端开销明显增大。若是认证的记录保存在某台服务器内存中时,意味着用户的下次请求只能够在该服务器内存中进行认证。CSRF跨站攻击 token的鉴权机制࿱…...

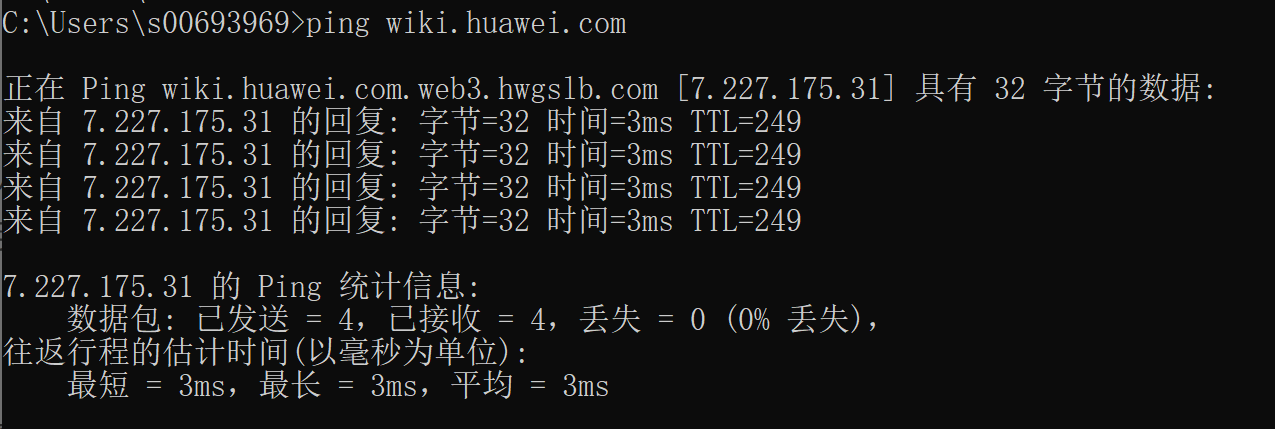

计算机网络_工具

从你的电脑到指定ip网站,用时3ms ttl TTL Time To Live 数据包存活时间 指一个数据包在经过一个路由器时,可传递的最长距离(跃点数)。每当数据包经过一个路由器时,其存活次数就会被减一 256 - 249 7&…...

如何实现一个Java的@注解?

先看一段代码: ControllerAdvice public class GlobalExceptionHandler {ExceptionHandler(value Exception.class)public ResponseEntity defaultErrorHandler(Exception e) {// 将错误信息转成字符串String errorMessage ExceptionUtils.getStackTrace(e);// 创…...

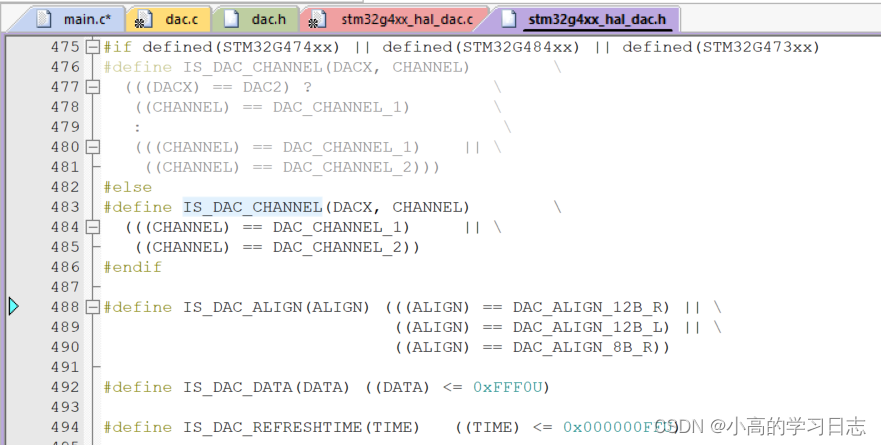

嵌入式|蓝桥杯STM32G431(HAL库开发)——CT117E学习笔记12:DAC数模转换

系列文章目录 嵌入式|蓝桥杯STM32G431(HAL库开发)——CT117E学习笔记01:赛事介绍与硬件平台 嵌入式|蓝桥杯STM32G431(HAL库开发)——CT117E学习笔记02:开发环境安装 嵌入式|蓝桥杯STM32G431(…...

迅饶科技 X2Modbus 网关 GetUser 信息泄露漏洞复现

0x01 产品简介 X2Modbus是上海迅饶自动化科技有限公司Q开发的一款功能很强大的协议转换网关, 这里的X代表各家不同的通信协议, 2是T0的谐音表示转换, Modbus就是最终支持的标准协议是Modbus协议。用户可以根据现场设备的通信协议进行配置,转成标准的Modbus协议。在PC端仿真…...

修改亚马逊云科技账户的密码和MFA

要使用AWS CLI删除当前账户的多因素认证(MFA)设备并修改密码,你需要先确保已安装并配置了AWS CLI,并且你的账户有足够的权限执行这些操作。下面是如何分步进行的指导: 1. 删除MFA设备 首先,你需要找出MFA设备的序列号或ARN。可以…...

提升性能与精准追踪:SkyWalking自定义跟踪忽略插件

前言 当使用分布式追踪系统时,有时需要排除某些端点或路径,以减轻追踪系统的负载或减少不必要的数据收集。为了满足这种需求,SkyWalking 提供了一个可选的插件,即 apm-trace-ignore-plugin,它允许自定义需要跳过的路径…...

第十三届蓝桥杯大赛软件赛省赛CC++大学B组

第十三届蓝桥杯大赛软件赛省赛CC 大学 B 组 文章目录 第十三届蓝桥杯大赛软件赛省赛CC 大学 B 组1、九进制转十进制2、顺子日期3、刷题统计4、修建灌木5、x进制减法6、统计子矩阵7、积木画8、扫雷9、李白打酒加强版10、砍竹子 1、九进制转十进制 计算器计算即可。2999292。 2、…...

BetterGI:原神自动化助手终极指南 - 告别重复劳动,智能解放双手

BetterGI:原神自动化助手终极指南 - 告别重复劳动,智能解放双手 【免费下载链接】better-genshin-impact 📦BetterGI 更好的原神 - 自动拾取 | 自动剧情 | 全自动钓鱼(AI) | 全自动七圣召唤 | 自动伐木 | 自动刷本 | 自动采集/挖矿/锄地 | 一…...

当你的客户想运行自己的工作流,你该怎么办

一个平台开发者绕不开的困境 假设你在构建一个 SaaS 平台,你的客户可以在上面写自己的业务逻辑——也许是一个低代码工具,也许是一个 AI 驱动的自动化平台,也许是一个让每个团队定义自己 CI 流水线的开发工具。 客户的逻辑各不相同࿰…...

在Node.js后端项目中集成Taotoken实现稳定的大模型调用

🚀 告别海外账号与网络限制!稳定直连全球优质大模型,限时半价接入中。 👉 点击领取海量免费额度 在Node.js后端项目中集成Taotoken实现稳定的大模型调用 对于需要构建AI功能的后端开发者而言,直接对接多个大模型厂商的…...

告别DataGridView!用DataExcel控件在Winform里快速搭建一个Excel风格的数据录入界面

告别DataGridView!用DataExcel控件在Winform里快速搭建Excel风格的数据录入界面 在开发ERP、CRM或进销存系统时,数据录入表单的设计往往成为影响开发效率和用户体验的关键因素。传统Winform开发中,DataGridView控件虽然功能强大,但…...

揭秘2026奇点智能大会KG实践链路:从LLM增强抽取到动态本体演化的5步工业级闭环

更多请点击: https://intelliparadigm.com 第一章:AI原生知识图谱构建:2026奇点智能技术大会KG实践指南 AI原生知识图谱(AI-Native KG)不再将图谱视为静态结构化知识库,而是作为大模型推理的实时协同体——…...

为什么92%的AI系统在L3自治阶段遭遇安全断层?奇点大会安全专家组深度拆解AI原生框架的4个不可绕过的设计拐点

更多请点击: https://intelliparadigm.com 第一章:AI原生安全框架:2026奇点智能技术大会安全专家解读 在2026奇点智能技术大会上,来自全球12家顶尖AI安全实验室的联合工作组正式发布《AI原生安全框架(AISF v1.0&#…...

从ROS到飞控:ENU与NED坐标系转换的实战解析与避坑指南

1. 为什么ENU和NED坐标系让开发者头疼? 第一次接触无人机开发时,我被ROS和飞控之间的坐标系问题坑得不轻。明明在ROS里跑得好好的导航算法,一接入PX4飞控就出现飞机往反方向飞、高度控制错乱的情况。后来才发现,这全是ENU和NED坐标…...

2025年八大网盘直链下载助手:LinkSwift完整使用指南

2025年八大网盘直链下载助手:LinkSwift完整使用指南 【免费下载链接】Online-disk-direct-link-download-assistant 一个基于 JavaScript 的网盘文件下载地址获取工具。基于【网盘直链下载助手】修改 ,支持 百度网盘 / 阿里云盘 / 中国移动云盘 / 天翼云…...

终极指南:3步掌握《塞尔达传说:旷野之息》存档编辑器,打造完美游戏体验

终极指南:3步掌握《塞尔达传说:旷野之息》存档编辑器,打造完美游戏体验 【免费下载链接】BOTW-Save-Editor-GUI A Work in Progress Save Editor for BOTW 项目地址: https://gitcode.com/gh_mirrors/bo/BOTW-Save-Editor-GUI 你是否曾…...

别再关DRC警告了!手把手教你用AD19正确设置3D封装高度偏移,解决PCB叠层干涉

彻底解决PCB叠层干涉:Altium Designer 19中3D封装高度偏移的实战指南 在PCB设计领域,3D封装的高度管理一直是工程师们容易忽视却又至关重要的环节。许多硬件工程师在遇到DRC(设计规则检查)警告时,第一反应往往是寻找关…...