ADC模-数转换原理与实现

1. 今日摸鱼计划

| 今天来学习一下ADC的原理,然后把ADC给实现 ADC芯片:ADC128S102 |

| 视频: 18A_基于SPI接口的ADC芯片功能和接口时序介绍_哔哩哔哩_bilibili 18B_使用线性序列机思路分析SPI接口的ADC芯片接口时序_哔哩哔哩_bilibili 18C_基于线性序列机的SPI接口ADC控制逻辑设计_哔哩哔哩_bilibili |

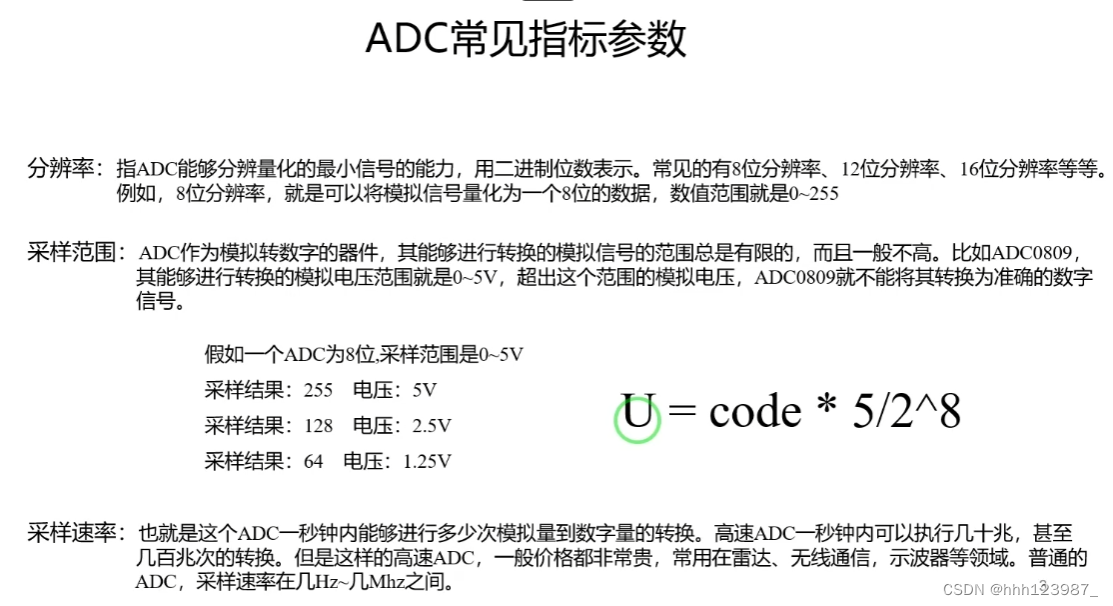

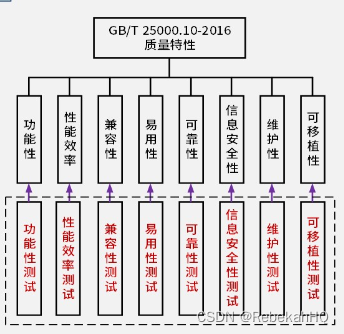

2. ADC指标参数

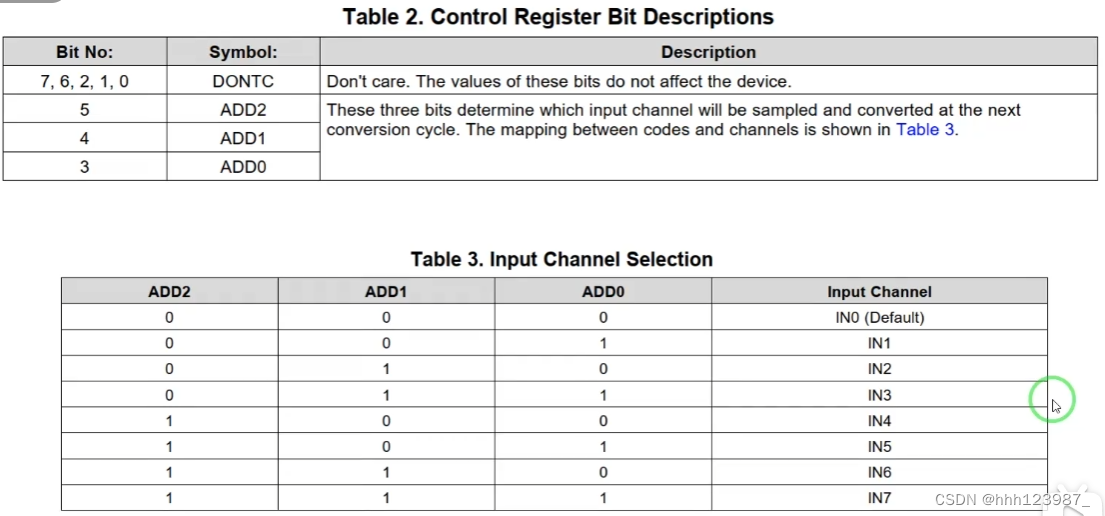

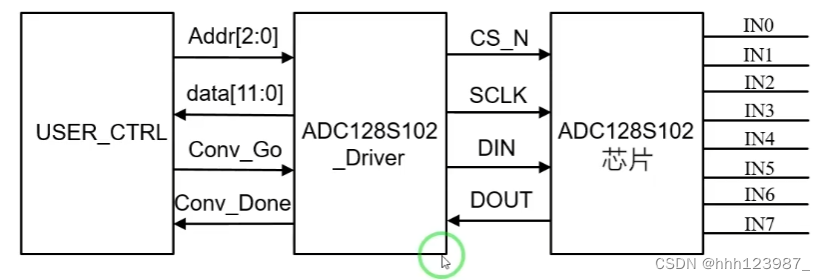

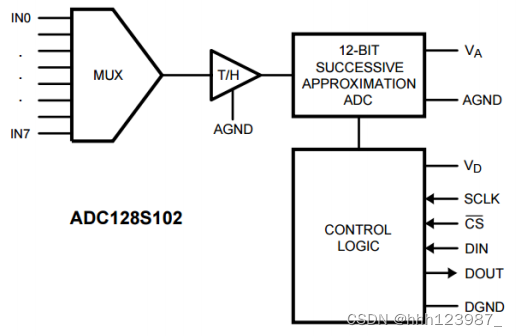

3. ADC128S102

在 ACZ702 EDA 扩展板上使用的模数转换器为逐次逼近型的低功耗芯片ADC128S102,其具有 8 通道以及 12 位的分辨率。电源采用独立的模拟供电以及数字供电,其中模拟电源 VA输入范围为 2.7V~5.25V,数字电源 VD输入范围为 2.7V~VA。其与外部通信支持多种接口如:SPI、QSPI、MICROWIRE以及通用的 DSP 接口。转换速度在 500 kps~1 Mkps,典型情况下当 3V 供电时功耗为2.3mW,5V 供电时为 10.7mW,如下图为该 ADC 芯片的内部结构图。

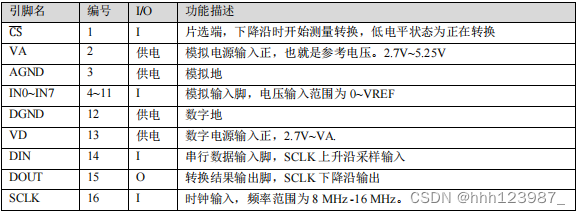

芯片引脚功能如下:

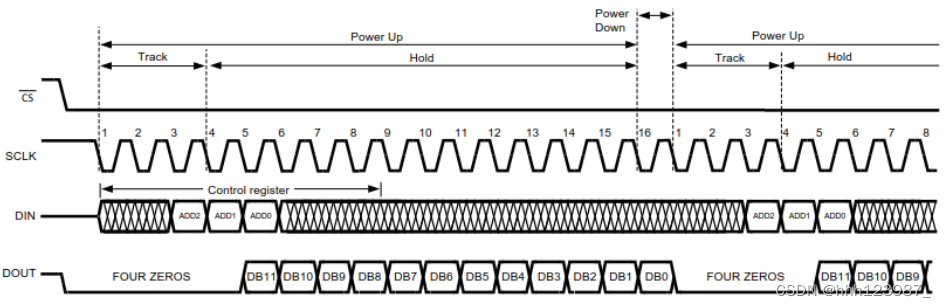

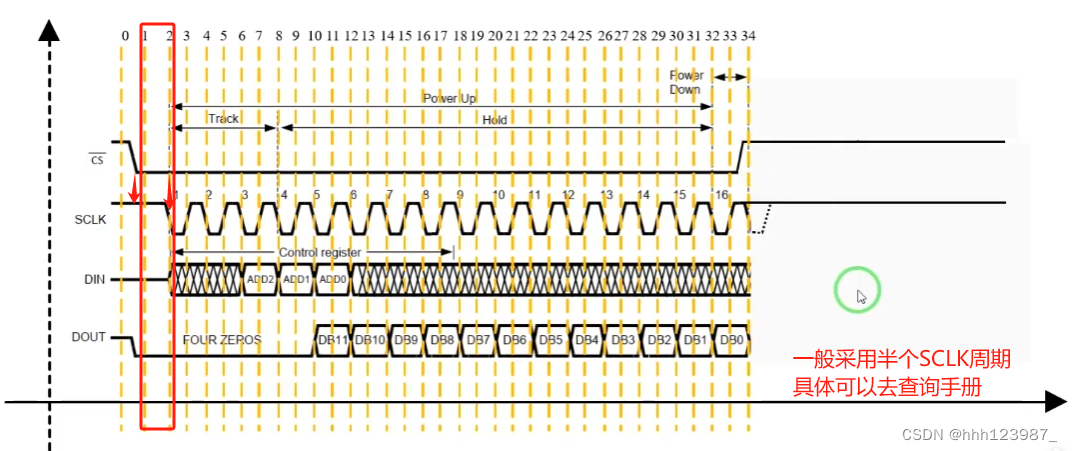

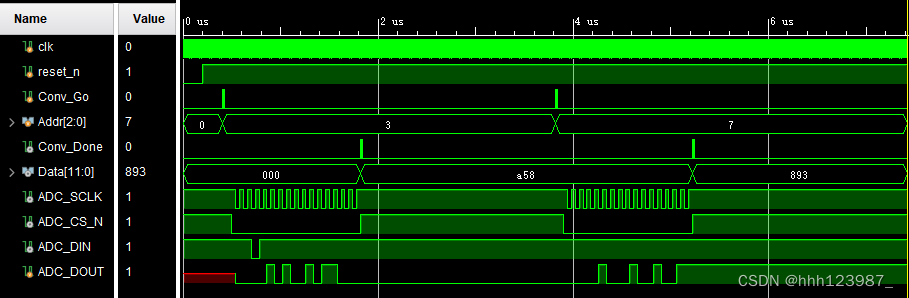

ADC128S102通过 SPI接口与控制器进行通信的时序图如下图所示:

四线SPI分析:

| CS | 片选信号(本摸鱼怪不会加横线) CS拉低,表示通信的开始,CS拉高表示通信结束 |

| SCLK | CS 为高时 SCLK 默认高 一帧包含 16 个上升沿 SCLK |

| DIN | SCLK的上升沿,DIN上的信号要保持稳定,此时ADC芯片会对DIN上的信号采样

|

| DOUT | 当CS 为高时代表空闲状态,当为低时为传输状态 |

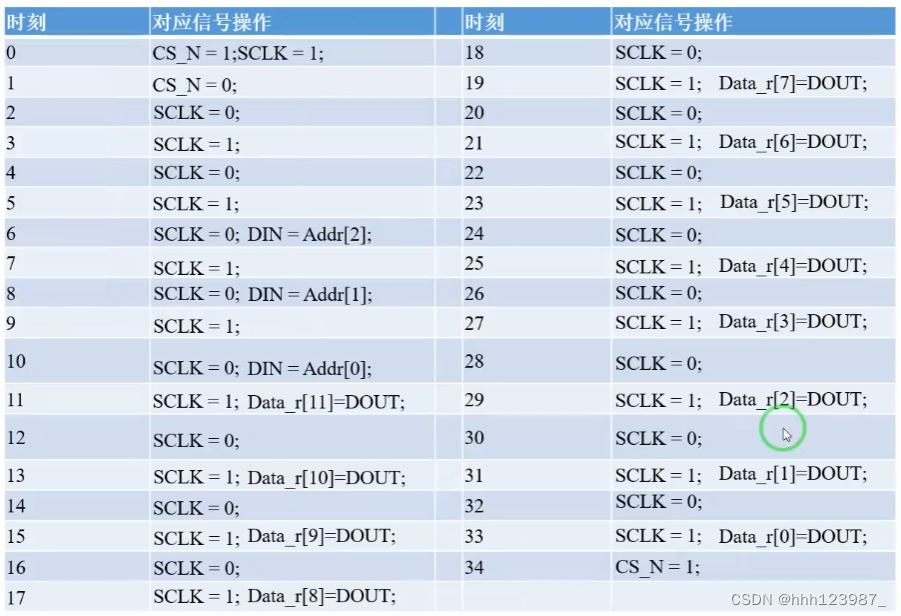

4. 线性序列机实现ADC

|

|

|

|

| module adc128s102( reg[7:0]DIV_CNT; reg [11:0]Data_r; always@(posedge Clk or negedge Reset_n)

always@(posedge Clk or negedge Reset_n ) endmodule |

5. adc128s102_tb

| `timescale 1ns/1ns module adc128s102_tb; reg clk; adc128s102 adc128s102( .Conv_Done(Conv_Done), |

相关文章:

ADC模-数转换原理与实现

1. 今日摸鱼计划 今天来学习一下ADC的原理,然后把ADC给实现 ADC芯片:ADC128S102 视频: 18A_基于SPI接口的ADC芯片功能和接口时序介绍_哔哩哔哩_bilibili 18B_使用线性序列机思路分析SPI接口的ADC芯片接口时序_哔哩哔哩_bilibili 18C_基于线性序列机的S…...

Android 文件传输

目录 device explorer 文件目录关系对应: device explorer 经常写adb命令传文件,结果发现Android studio有自带的文件管理器,可以上传下载文件。 tool windows ->device explorer 文件目录关系对应: Android java获取的程序…...

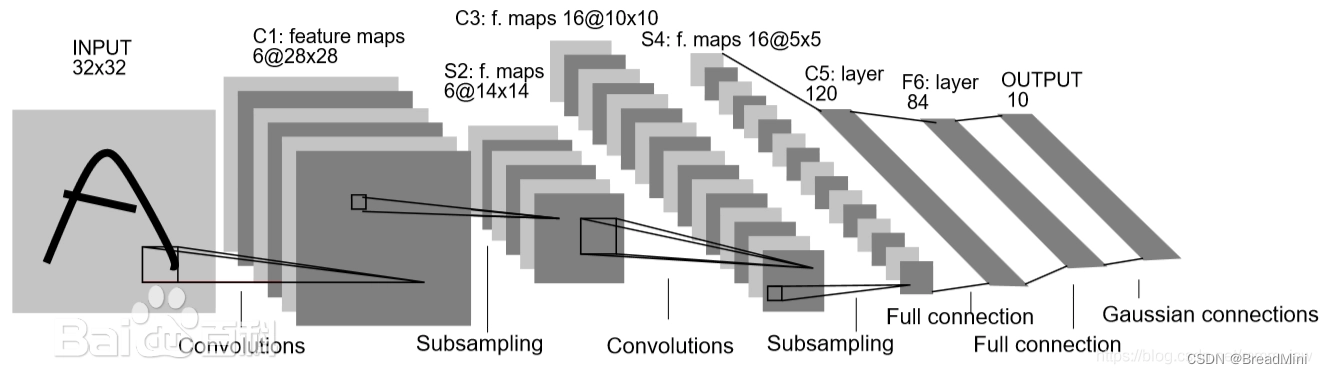

一起深度学习

CIFAR-10 卷积神经网络 下载数据集构建网络运行测试 下载数据集 batchsz 32cifar_train datasets.CIFAR10(data,trainTrue,transformtorchvision.transforms.Compose([torchvision.transforms.Resize((32,32)),torchvision.transforms.ToTensor()]),downloadTrue)cifar_train …...

servlet-会话(cookie与session)

servlet会话技术 会话技术cookie创建Cookieindex.jspCookieServlet 获取Cookieindex.jspshowCookie session创建sessionindex.jsplogin.jspLoginServlet 获取sessionRedurectServket 清除会话login.jspClearItmeServlet 会话技术 两种会话:cookie,sessi…...

windows11忘记登录密码怎么办?

STEP1:进入Win RE界面 1.按住shift不要松手,点击重新启动,进入WINRE界面 2.选择疑难解答 选择高级选项 点击命令提示符 STEP2:替换utilman 1.输入以下代码查看所在windows所在盘 diskpart list volume exit 2.根据所在盘输入命令(以C盘为…...

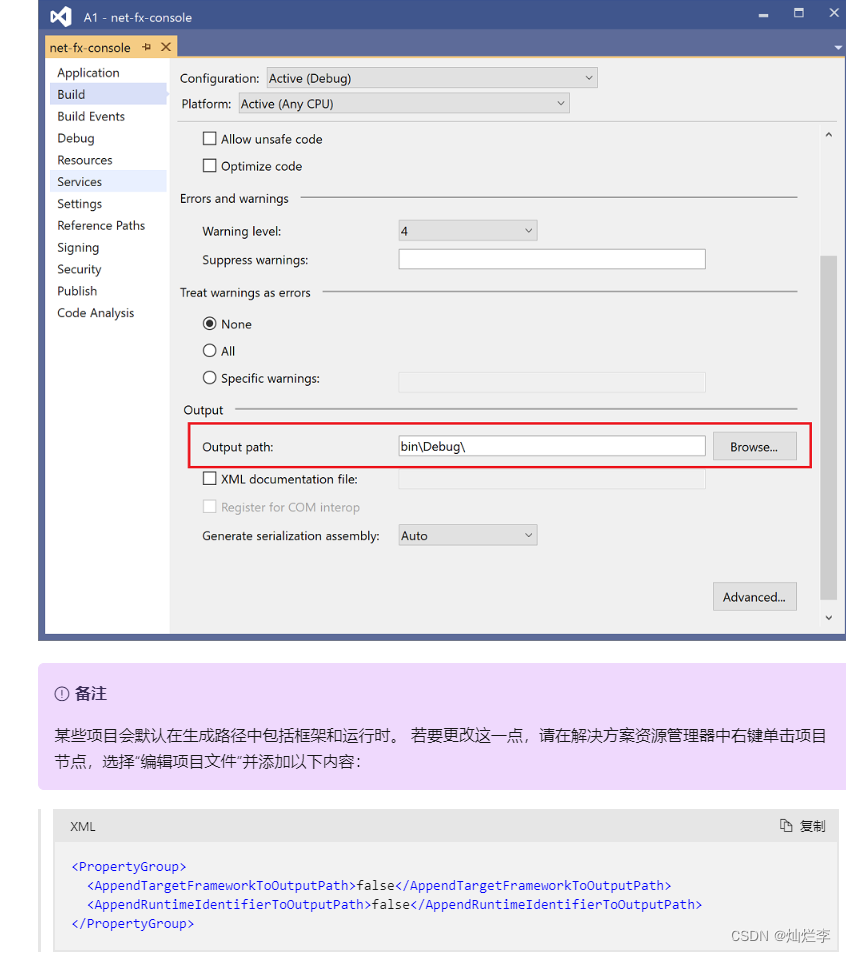

C#里如何设置输出路径,不要net7.0-windows

官网介绍: 更改生成输出目录 - Visual Studio (Windows) | Microsoft Learn <PropertyGroup> <AppendTargetFrameworkToOutputPath>false</AppendTargetFrameworkToOutputPath> <AppendRuntimeIdentifierToOutputPath>false</Appen…...

知名员工上网行为管理系统推荐榜单

上网行为管理软件旨在帮助组织监控和管理员工的网络活动,以提高工作效率、确保网络安全和合规性。以下是一些常见的上网行为管理软件: Ping32:Ping32是一款专业的员工上网行为管理系统,Ping32作为一款专业的员工上网行为管理系统&…...

第12章 软件测试基础(第三部分)测试类型、测试工具

七、测试类型(按工程阶段划分) 单集系确收 (一)单元测试 1、单元测试/模块测试 单元就是软件中最小单位(或模块)。可以是一个函数、一个过程、一个类。主要依据是模块的详细设计文档。价值在于尽早发现…...

open-vm-tools使用虚机的拷贝/粘切

open-vm-tools 是一组用于 VMware 虚拟机中的开源工具,它们提供了一些与虚拟机操作和管理相关的功能。这些工具与 VMware 虚拟化平台集成,可以在虚拟机中提供更好的性能和功能。以下是一些 open-vm-tools 提供的功能: 1. 虚拟机增强功能: open-vm-tools 提供了与 VMware 虚…...

CKEditor编辑器的简单使用方法,取值,赋值

先从官网下载包。CKEditor 4 - Download Latest Version. 一:在项目里引用JQ基础包和CK的JS包 <script src"/JS/jquery-3.4.1.js?v1.0"></script><script src"/ckeditor/ckeditor.js"></script> 二:在表…...

创建一个线程对象需要花费多少内存空间

创建一个std::thread对象所需的内存空间大小并不是固定的,因为它取决于多种因素,包括C运行时库的实现、编译器优化、以及可能的平台和架构差异。 std::thread对象本身是一个轻量级的控制块,它主要用于管理线程的执行,包括保存线程…...

Java -- (part23)

一.网络编程 1.概述 在网络通信协议下,不同计算机上运行的程序,进行数据传输 2.软件架构 CS架构:客户端和服务端 BS架构:浏览器和服务端 3.服务器概念 安装了服务器软件的计算机 4.通信三要素 IP地址 a.概述 计算机的唯一标识,用于两台计算机之间的链接 b.特殊的IP…...

1. C++入门:命名空间及输入输出

C相比C的变化 兼容C面向对象泛型C的不足的弥补 为什么要有命名空间 在C/C中,变量、函数和后面要学到的类都是大量存在的,这些变量、函数和类的名称将都存在于全局作用域中,可能会导致很多冲突。使用命名空间的目的是对标识符的名称进行本地…...

【Kotlin】Java三目运算转成 kotlin 表达

这行代码会直接计算 array.size 1 的布尔值,并将其赋值给 result。在 Kotlin 中,不需要使用三元操作符,因为条件表达式本身就返回一个布尔值 java 中三木运算: int [] array new int[]{1, 2, 3, 4, 5}; boolean test array &g…...

如何安全可控地进行内外网跨网络传输文件?

跨网络传输文件通常指的是在不同的网络环境之间移动数据,这在现代企业运营中非常常见。随着网络技术的高速发展,为了有效地保护内部的核心数据资产,企业一般会采用内外网隔离的策略。在进行内外网跨网络传输文件时,需要考虑多种因…...

Python Json数据解析

本篇主要介绍Python 中json数据如何解析、转化、保存和加载。 目录 Json数据解析 概念 作用 Json文件组成 Json转化为Python数据类型 Python数据类型转化为json 写入本地json文件 读取本地的json文件 总结 Json数据解析 概念 一种保存数据的格式 作用 可以保存本地…...

pyinstaller打包pytorch和transformers程序

记录使用pyinstaller打包含有pytorch和transformers库的程序时遇到的问题和解决方法。 环境和版本信息 操作系统:Windows 11 Python:3.10.12 pyinstaller:5.13.0 torch:2.2.2 transformers:4.40.1 打包过程和问…...

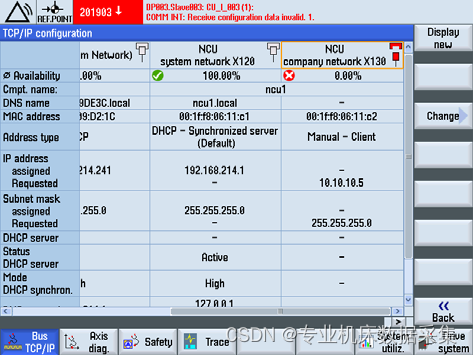

西门子数控网络IP设定配置

总结:menuselect-诊断-屏幕下方右翻页找到tcp/ip,进去选择tcp/ip诊断,进去选择x130网口,点击更改, 如果没有更改,menuselect-调试-口令,输入口令 sunrise 然后重新配置tcp/ip,配置完…...

[Unity]备份许可文件

原因:因Unity需要重新恢复出厂设置,所以需要先将许可文件本分到本地,以便重新初始化后输入许可。 1)登录管理网络web界面,在服务页面打开SSH 2)ssh到管理网络,使用service用户登录 3…...

第十五届蓝桥杯省赛大学B组(c++)

很幸运拿了辽宁赛区的省一,进入6月1号的国赛啦... 这篇文章主要对第十五届省赛大学B组(C)进行一次完整的复盘,这次省赛2道填空题6道编程题: A.握手问题 把握手情景看成矩阵: 粉色部分是7个不能互相捂手的情况 由于每个人只能和其他人捂手, 所以黑色情况是不算的 1和2握手2和…...

ThinkPHP8.x全面升级:现代化PHP开发新标杆

好的,我们来梳理一下 ThinkPHP 8.x 版本(通常指 8.0 及后续小版本)的主要特性和改进方向。相较于之前的版本(如 5.x),8.x 版本在架构、性能、规范性和安全性上都有显著提升:核心方向与重大变更&…...

TPFanCtrl2:ThinkPad智能风扇控制终极指南,彻底解决过热与噪音问题

TPFanCtrl2:ThinkPad智能风扇控制终极指南,彻底解决过热与噪音问题 【免费下载链接】TPFanCtrl2 ThinkPad Fan Control 2 (Dual Fan) for Windows 10 and 11 项目地址: https://gitcode.com/gh_mirrors/tp/TPFanCtrl2 你是否曾经在安静的会议室中…...

【免费下载】 探索双面神技:STM32G474的USB跨界应用

探索双面神技:STM32G474的USB跨界应用 在物联网与嵌入式开发的世界里,寻找一款能兼顾数据传输与控制沟通的神器是每个开发者的心头好。今天,我们就来揭秘这样一个宝藏项目——STM32G474实现USB的MSCCDC组合功能,它巧妙地将STM32G4…...

如何永久免费使用IDM下载管理器:无需破解的智能重置方案

如何永久免费使用IDM下载管理器:无需破解的智能重置方案 【免费下载链接】idm-trial-reset Use IDM forever without cracking 项目地址: https://gitcode.com/gh_mirrors/id/idm-trial-reset 想要永久免费使用Internet Download Manager这款强大的下载加速工…...

3分钟解锁音乐自由:ncmdump让网易云音乐NCM文件随处播放

3分钟解锁音乐自由:ncmdump让网易云音乐NCM文件随处播放 【免费下载链接】ncmdump 项目地址: https://gitcode.com/gh_mirrors/ncmd/ncmdump 还在为网易云音乐下载的歌曲只能在特定客户端播放而烦恼吗?当您精心收藏的音乐被NCM加密格式束缚&…...

终极指南:如何在Mac上免费实现NTFS读写功能

终极指南:如何在Mac上免费实现NTFS读写功能 【免费下载链接】Free-NTFS-for-Mac Nigate: An open-source NTFS utility for Mac. It supports all Mac models (Intel and Apple Silicon), providing full read-write access, mounting, and management for NTFS dri…...

Cling实时编码音乐应用:探索编程与艺术的跨界融合

Cling实时编码音乐应用:探索编程与艺术的跨界融合 【免费下载链接】cling The interactive C interpreter Cling 项目地址: https://gitcode.com/gh_mirrors/cli/cling Cling作为一款强大的交互式C解释器,不仅能提升编程效率,更能成为…...

为什么选择Hydrogen:对比传统电商平台的5大优势 [特殊字符]

为什么选择Hydrogen:对比传统电商平台的5大优势 🚀 【免费下载链接】hydrogen Hydrogen lets you build faster headless storefronts in less time, on Shopify. 项目地址: https://gitcode.com/gh_mirrors/hyd/hydrogen 在当今快速发展的电商领…...

从原理到实战:晶体管开关电路设计与常见问题解析

1. 项目概述:为什么我们需要晶体管开关?如果你玩过Arduino或者树莓派,肯定遇到过这样的尴尬:想用单片机的一个GPIO引脚直接点亮一个12V的汽车大灯,或者驱动一个小马达,结果要么灯不亮,要么马达纹…...

别再只会用menuconfig了!手把手教你为ESP32项目定制专属Kconfig配置菜单

从配置使用者到设计者:ESP32项目中的Kconfig高级定制指南 在ESP-IDF开发环境中,menuconfig几乎是每个开发者每天都要接触的工具。但大多数开发者仅仅停留在"使用者"层面——他们知道如何勾选选项、调整参数,却很少思考这些配置菜单…...