Vivado 比特流编译时间获取以及FPGA电压温度获取(实用)

Vivado 比特流编译时间获取以及FPGA电压温度获取

语言 :Verilg HDL 、VHDL

EDA工具:ISE、Vivado

- Vivado 比特流编译时间获取以及FPGA电压温度获取

- 一、引言

- 二、 获取FPGA 当前程序的编译时间

- verilog中直接调用下面源语

- 2. FPGA电压温度获取

- (1)使用源语调用

- (2)温度和电压解析

- 温度解析公式

- 电压解析公式

- 测到的一组值:

- (2)调用xadc ip核

- 三、结尾

- 关键词: 调用,Vivado,

一、引言

在FPGA开发中,经常需要对整个系统进行健康信息监控以及版本信息管脚,这时,需要知道FPGA 当前程序的编译时间以及FPGA实时的温度电压信息,本文对这两个部分进行总结说明,方便诸君不时之需,直接调用便可,不需要多在这上面耗费时间和精力。

二、 获取FPGA 当前程序的编译时间

verilog中直接调用下面源语

reg[31:0] DATA ;USR_ACCESSE2 USR_ACCESSE2_inst (.CFGCLK( ), // 1-bit output: Configuration Clock output.DATA(DATA), // 32-bit output: Configuration Data output.DATAVALID( ) // 1-bit output: Active high data valid output);

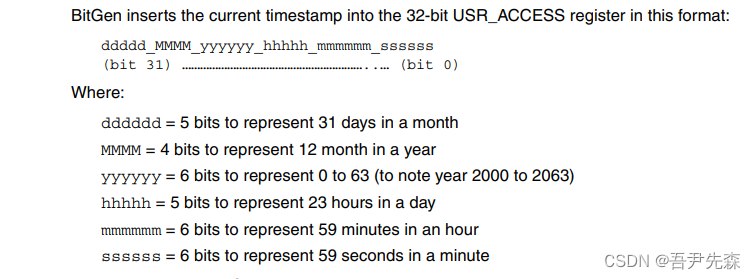

因为USR_ACCESSE2 为源语,所以直接在调用上面的模块,便可以得到32-bit 输出DATA,这便是当前bit(比特流)的详细编译时间,该数据的解析格式如下:

只需要把DATA中对应的位数取出来,即可解析出当前bit的编译时间年月日时分秒。

下面是 VHDL的调用。

inst_usr_access2: USR_ACCESSE2

port map (CFGCLK => open,DATA => bit_stream_info,DATAVALID => open

);2. FPGA电压温度获取

(1)使用源语调用

reg[15:0] vccint_doutxadc_test xadc_test_inst (.clk_100mhz(clk_50M), .rst_n(FPGA3_RST), .temperature_dout(temperature_dout), .vccint_dout(vccint_dout), .vccaux_dout(vccaux_dout), .vccbram_dout(vccbram_dout));

可以在下面链接中直接下载该模块,然后直接用上面的例化调用即可。

7系列以上xlinx FPGA +xadc模块+获取FPGA的温度电压+使用源语 直接调用模块

(2)温度和电压解析

温度解析公式

Temp(℃)=(MEASURED_TEMP[15:4]* 503.975)/4096-273.15

电压解析公式

VCCINT= (MEASURED_VCCINT[15:4]* 3)/4096

测到的一组值:

Tem: 16’hA534;

VCCINT: 16’h5478;

VCCAUX: 16’h988F;

VCCBRAM: 16’h535F;

([15:4]就是高12位,去掉低四位便是有效值。即:Tem有效值等于16’hA53)

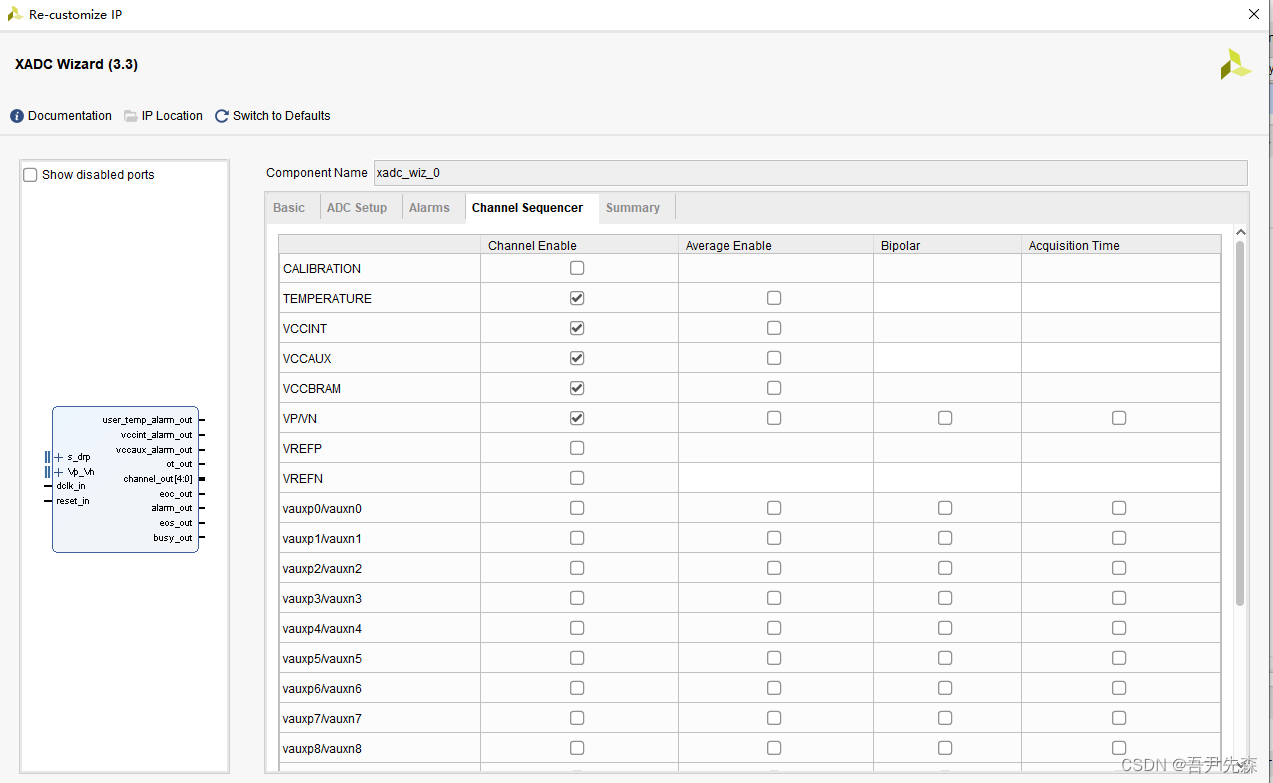

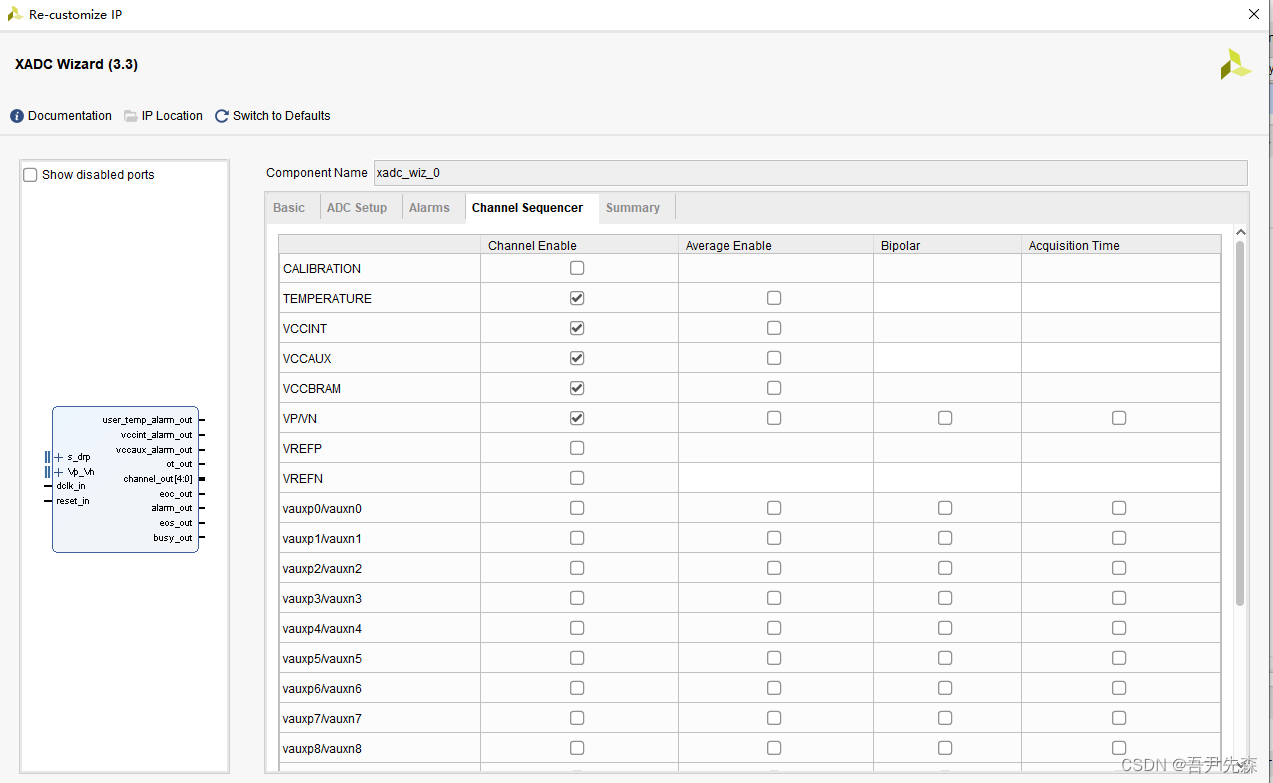

(2)调用xadc ip核

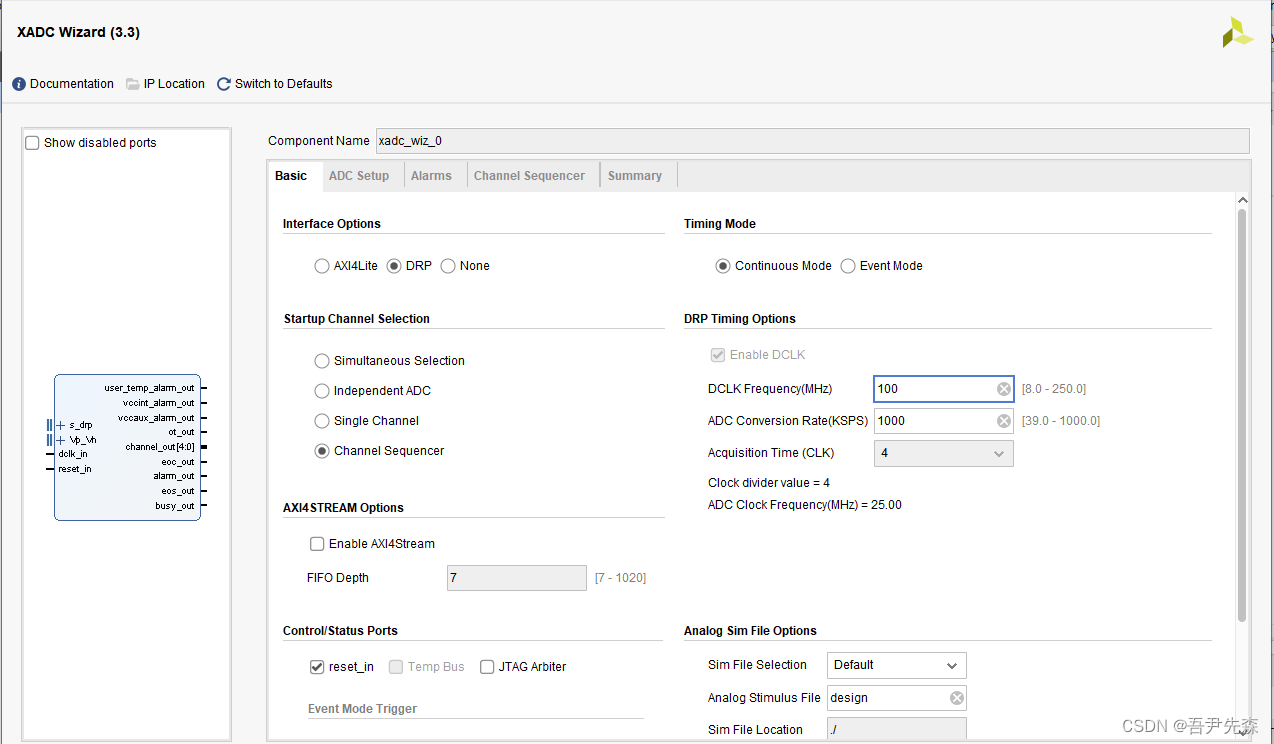

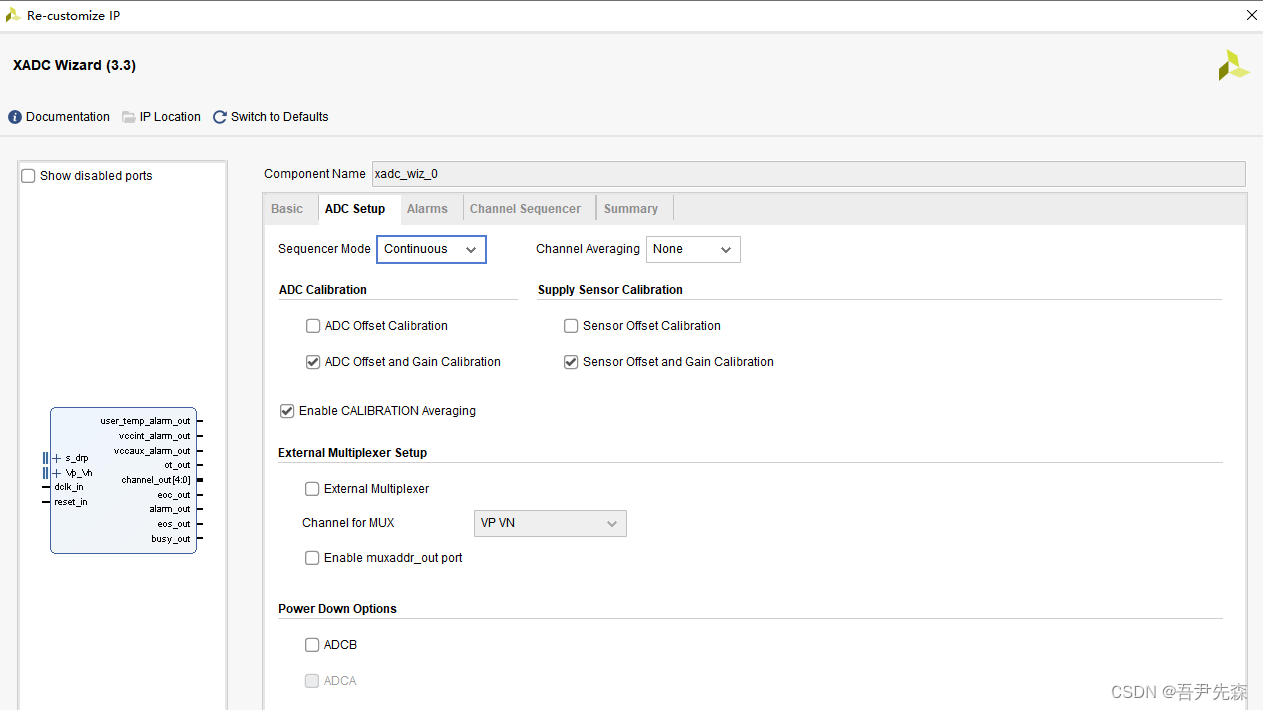

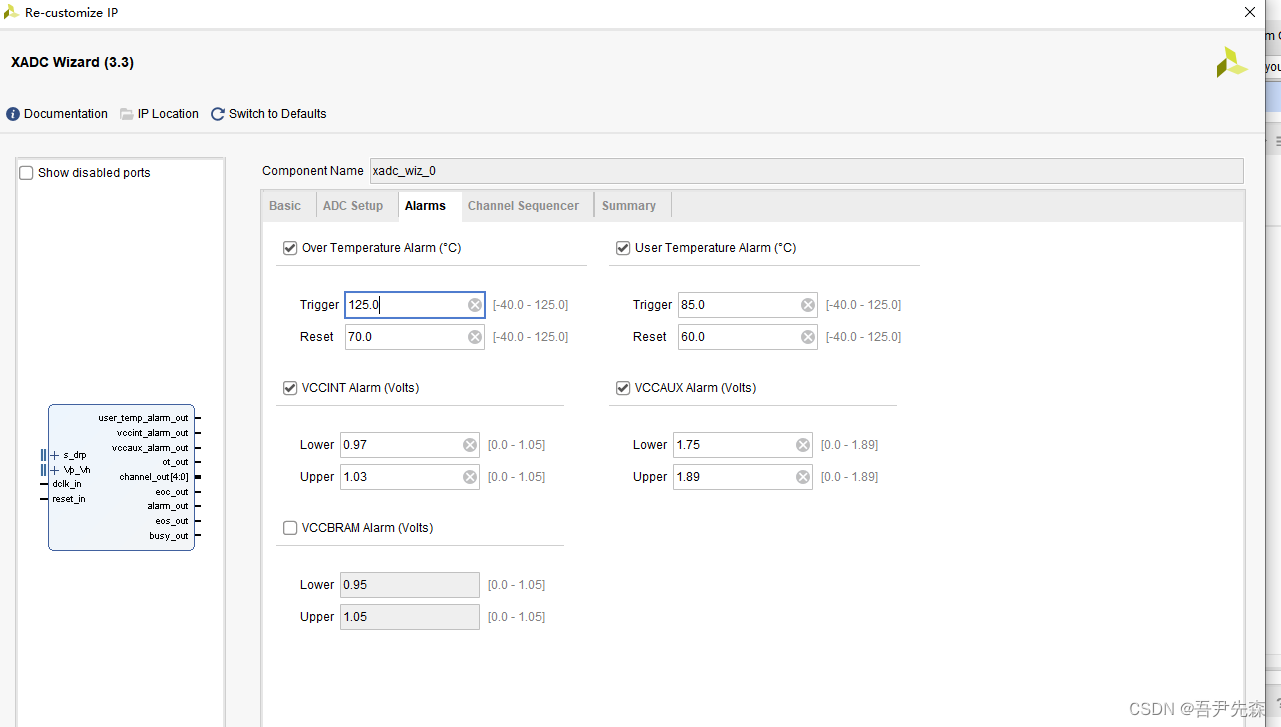

调用ip核与使用xadc源语本质是一样的,只是稍微有些繁琐。

IP核的主要设置如下:

(1)

(2)

(3)

(3)

IP的定层模块我也附上:

`timescale 1ns / 1psmodule xadc_test(

input clk_100mhz,

input rst_n ,

output reg[15:0] temp_dout , //Data

output reg [15:0] vccint_dout ,

output reg [15:0] vccaux_dout ,

output reg [15:0] vccbram_dout );wire clk;reg[15:0] temperature_dout;//-------------------------------------//---- XADC IP INST ------------- wire [15:0] di_in;wire [6:0] daddr_in;wire den_in;wire dwe_in;wire drdy_out;wire [15:0] do_out;wire [4:0] channel_out;wire eoc_out;wire eos_out;wire busy_out;assign clk = clk_100mhz;//XADC IP (Mode:Channel Sequencer)xadc_wiz_0 xadc_ip_inst (.di_in(di_in), // input wire [15 : 0] di_in.daddr_in(daddr_in), // input wire [6 : 0] daddr_in.den_in(den_in), // input wire den_in.dwe_in(dwe_in), // input wire dwe_in.drdy_out(drdy_out), // output wire drdy_out.do_out(do_out), // output wire [15 : 0] do_out.dclk_in(clk), // input wire dclk_in.reset_in(!rst_n), // input wire reset_in.vp_in(1'b0), // input wire vp_in.vn_in(1'b0), // input wire vn_in.user_temp_alarm_out(), // output wire user_temp_alarm_out.vccint_alarm_out(), // output wire vccint_alarm_out.vccaux_alarm_out(), // output wire vccaux_alarm_out.ot_out(), // output wire ot_out.channel_out(channel_out), // output wire [4 : 0] channel_out.eoc_out(eoc_out), // output wire eoc_out.alarm_out(), // output wire alarm_out.eos_out(eos_out), // output wire eos_out.busy_out(busy_out) // output wire busy_out);//only Readassign di_in = 16'd0; //not usedassign dwe_in = 1'b0; //not usedassign den_in = eoc_out;assign daddr_in = {2'd0,channel_out};//-------------------------------------//Read Temperature Datareg temperature_dout_en ;reg vccint_dout_en ;reg vccaux_dout_en ;reg vccbram__dout_en ;always @(posedge clk or negedge rst_n)beginif(!rst_n) begintemperature_dout <= 16'd0;vccint_dout <= 16'd0;vccaux_dout <= 16'd0;vccbram_dout <= 16'd0;temperature_dout_en <= 1'b0;vccint_dout_en <= 1'b0;vccaux_dout_en <= 1'b0;vccbram__dout_en <= 1'b0;endelse beginif((drdy_out) &&(channel_out == 5'd0)) // Latch ADCcode of On-chip-temperaturebegintemperature_dout <= (drdy_out==1'b1)?do_out:16'd0;temperature_dout_en <= drdy_out;endelse if((drdy_out) &&(channel_out == 5'd1)) // Latch ADCcode of VCCINTbeginvccint_dout <= (drdy_out==1'b1)?do_out:16'd0;vccint_dout_en <= drdy_out;endelse if((drdy_out) &&(channel_out == 5'd2)) // Latch ADCcode of VCCAUXbeginvccaux_dout <= (drdy_out==1'b1)?do_out:16'd0;vccaux_dout_en <= drdy_out;endelse if((drdy_out) &&(channel_out == 5'd6)) // Latch ADCcode of VCCBRAMbeginvccbram_dout <= (drdy_out==1'b1)?do_out:16'd0;vccbram__dout_en <= drdy_out;endelsebegintemperature_dout_en <= 1'b0;vccint_dout_en <= 1'b0;vccaux_dout_en <= 1'b0;vccbram__dout_en <= 1'b0;endendendwire[20:0] p;mult_x504 m504 (.CLK(clk), // input wire CLK.A(temperature_dout[15:4]), // input wire [11 : 0] A.P(p) // output wire [20 : 0] P

); always@( posedge clk) temp_dout = p[20:12] - 273 ; endmodule

其中mult_x504 是一个乘法器ip,输入值乘无符号数504,然后再减去273,就是结果temp_dout 就是真实的温度结果了。

三、结尾

本文总结了Vivado 比特流编译时间获取以及FPGA电压温度获取的方法,以及获取后将数据进行解析的公式,以上内容都是实际工程中验证过的,可放心使用,如有问题可私信博主,知无不言。

相关文章:

Vivado 比特流编译时间获取以及FPGA电压温度获取(实用)

Vivado 比特流编译时间获取以及FPGA电压温度获取 语言 :Verilg HDL 、VHDL EDA工具:ISE、Vivado Vivado 比特流编译时间获取以及FPGA电压温度获取一、引言二、 获取FPGA 当前程序的编译时间verilog中直接调用下面源语2. FPGA电压温度获取(1&a…...

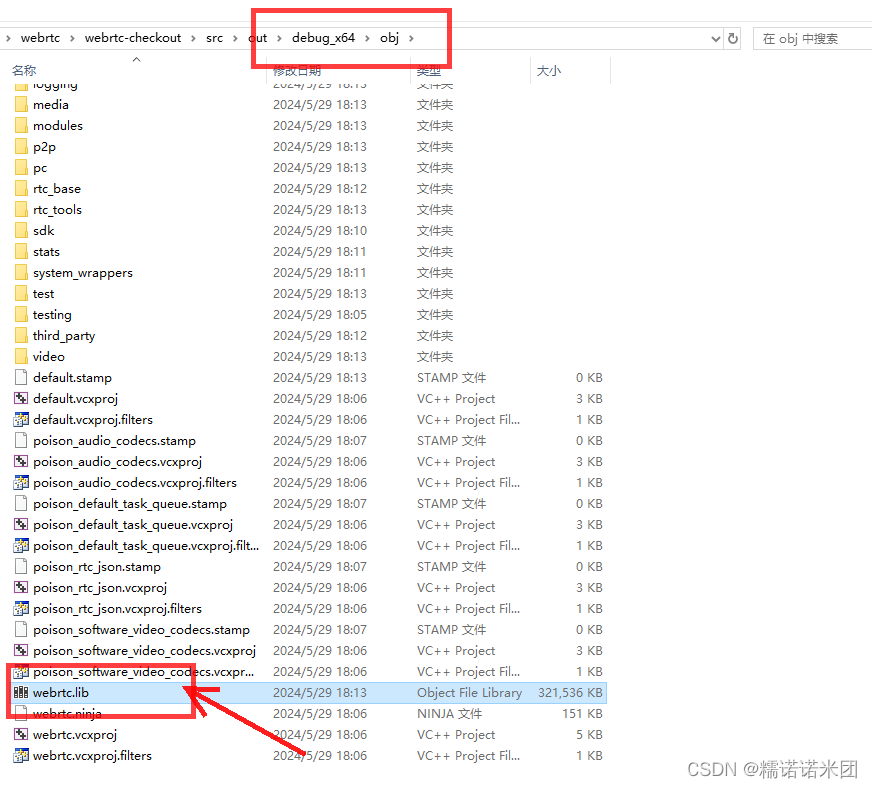

Window下VS2019编译WebRTC通关版

这段时间需要实现这样一个功能,使用WebRTC实现语音通话功能,第一步要做的事情就是编译WebRTC源码,也是很多码友会遇到的问题。 经过我很多天的踩坑终于踩出来一条通往胜利的大路,下面就为大家详细介绍,编译步骤以及踩…...

【云原生 | 60】Docker中通过docker-compose部署kafka集群

🍁博主简介: 🏅云计算领域优质创作者 🏅2022年CSDN新星计划python赛道第一名 🏅2022年CSDN原力计划优质作者 🏅阿里云ACE认证高级工程师 🏅阿里云开发者社区专…...

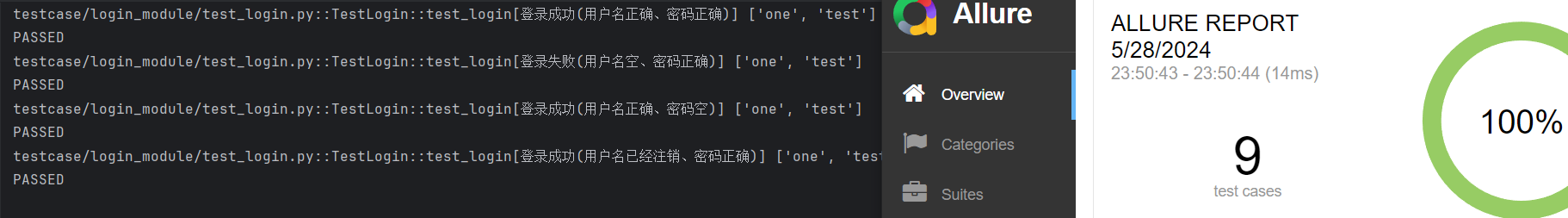

allure测试报告用例数和 pytest执行用例数不相同问题

我出现的奇怪问题: pytest执行了9条用例,但是测试报告确只显示3条用例 我将其中的一个代码删除后,发现allure测试报告又正常了 我觉得很奇怪这个代码只是删除了二维数组的第一列,我检查了半天都找不到问题,只有降低版本…...

Ubuntu 离线安装 gcc、g++、make 等依赖包

前言 项目现场的服务器无法连接互联网,需要提前获取 gcc、g、make 等依赖包。 一、如何获取依赖包 需要准备一台可以连接互联网的电脑(如:个人电脑上的虚拟机安装一个与服务器一样的系统),用于下载依赖包。之后把通过…...

Vxe UI vxe-upload 上传组件,显示进度条的方法

vxe-upload 上传组件 查看官网 https://vxeui.com 显示进度条很简单,需要后台支持进度就可以了,后台实现逻辑具体可以百度,这里只介绍前端逻辑。 上传附件 相关参数说明,具体可以看文档: multiple 是否允许多选 li…...

探索API接口:技术深度解析与应用实践

在当今的软件开发和数据交换领域,API(应用程序编程接口)已经成为了一个不可或缺的工具。它允许不同的软件应用程序或组件之间进行交互和通信,从而实现了数据的共享和功能的扩展。本文将深入探讨API接口的技术原理、设计原则以及在…...

系统架构之系统安全能力的系统隔离属性)

ARM-V9 RME(Realm Management Extension)系统架构之系统安全能力的系统隔离属性

安全之安全(security)博客目录导读 目录 一、系统隔离属性 1、系统配置完整性 1.1、时间隔离 2、关键错误的报告 一、系统隔离属性 1、系统配置完整性 MSD必须确保任何可能危及其安全保证的系统寄存器的正确性和完整性。例如,MSD必须确认内存控制器配置是一致…...

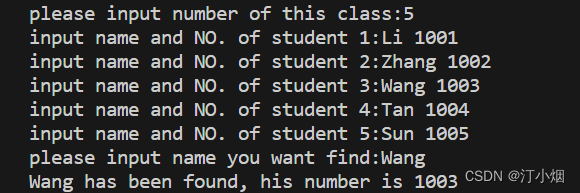

一个班有n个学生,需要把每个学生的简单材料(姓名和学号)输入计算机保存。然后可以通过输入某一学生的姓名查找其有关资料。

当输入一个姓名后,程序就查找该班中有无此学生,如果有,则输出他的姓名和学号,如果查不到,则输出"本班无此人"。 为解此问题,可以分别编写两个函数,函数input_data用来输人n个…...

函数)

python的range() 函数

range() 函数 《红楼梦》,又名《石头记》,实际上是一颗神石在人间游历的故事。而这块石头,就是我们的主人公贾宝玉。神石在投胎成宝玉前,向茫茫大士和渺渺真人讲起了自己的故事: 女娲氏炼石补天之时,于大…...

ClickHouse数据管理与同步的关键技术

2024年 5 月 18 日,ClickHouse官方首届杭州 Meetup 活动成功举行。本次活动由 ClickHouse 和阿里云主办,NineData 和云数据库技术社区协办。围绕ClickHouse的核心技术、应用案例、最佳实践、数据管理、以及迁移同步等方面,和行业专家展开交流…...

【一竞技DOTA2】东南亚Bleed战队官宣Emo正式加盟

1、近日东南亚Bleed战队正式发布公告官宣,中国选手Emo以及来自蒙古选手Se加盟战队。 【公告内容如下】 我们很高兴宣布,战队DOTA2名单中添加了两位新成员,请和我们一起欢迎来自中国经验丰富的老将Emo以及来自蒙古的后起之秀Se 一号位&#…...

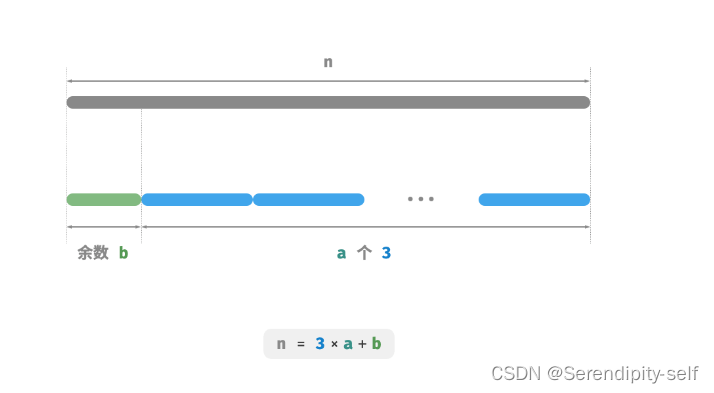

算法学习笔记(7.3)-贪心算法(最大切分乘问题)

目录 ##问题描述 ##问题思考 ##贪心策略确定 ##代码实现 ##时间复杂度 ##正确性验证 ##问题描述 给定一个正整数 𝑛 ,将其切分为至少两个正整数的和,求切分后所有整数的乘积最大是多少 ##问题思考 假设我们将 𝑛 切分为 &…...

大型企业用什么文件加密软件,五款适合企业的文件加密软件

大型企业在选择文件加密软件时,通常会倾向于那些能够提供全面数据保护、具有高度可定制性、易于管理且能适应复杂组织结构的解决方案。以下是一些适合大型企业使用的文件加密软件: 1.域智盾软件: 作为一款企业级文件加密软件,支持…...

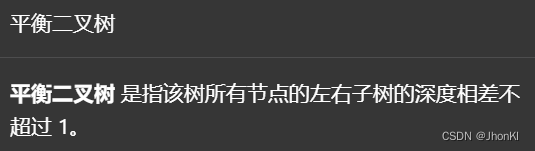

【数据结构】二叉树运用及相关例题

文章目录 前言查第K层的节点个数判断该二叉树是否为完全二叉树例题一 - Leetcode - 226反转二叉树例题一 - Leetcode - 110平衡二叉树 前言 在笔者的前几篇篇博客中介绍了二叉树的基本概念及基本实现方法,有兴趣的朋友自己移步看看。 这篇文章主要介绍一下二叉树的…...

Java基础知识点(反射、注解、JDBC、TCP/UDP/URL)

文章目录 反射反射的定义class对象反射的操作 注解注解的定义注解的应用注解的分类基准注解元注解 自定义注解自定义规则自定义demo JDBCTCP/UDP/URLTCPUDPURL 反射 反射的定义 Java Reflection是Java被视为动态语言的基础啊, 反射机制允许程序在执行期间接入Refl…...

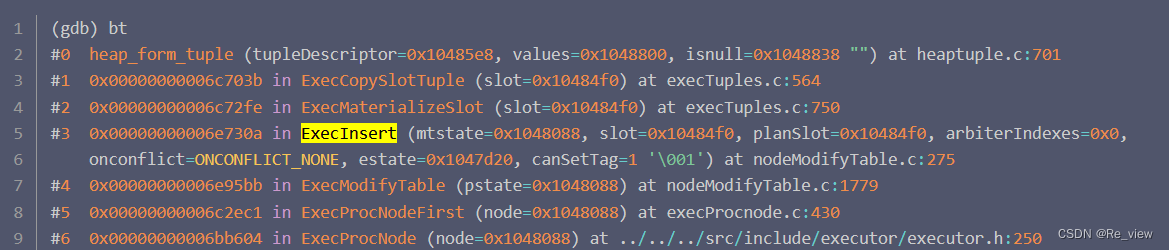

postgressql——Tuple学习(2)

Tuple含义 作用 PG并没有像Oracle那样的undo来存放旧数据,而且PG没有真正意义上的delete,而是将旧版本直接存放于relation文件中,也就是成为了dead tuple。我们可以理解成“过期的数据”含义 tuple就相当于一个存储数据的小容器,…...

Linux日志管理

文章目录 一、日志管理概述1.1、日志管理介绍1.2、日志管理的重要性1.3、日志管理的组件1.4、日志管理的流程1.5、日志管理的挑战 二、日志分类介绍2.1、windows日志类别2.1.1、Application Log2.1.2、Security Log2.1.3、System Log2.1.4、Setup Log2.1.5、ForwardedEvents Lo…...

【社区投稿】给 NdArray 装上 CUDA 的轮子

Ndarry是Rust编程语言中的一个高性能多维、多类型数组库。它提供了类似 numpy 的多种多维数组的算子。与 Python 相比 Rust 生态缺乏类似 CuPy, Jax 这样利用CUDA 进行加速的开源项目。虽然 Hugging Face 开源的 candle 可以使用 CUDA backend 但是 candle 项瞄准的是大模型的相…...

)

Linux|Linux常用命令合集(一)

想记录一下个人会用到的一些linux命令,持续更新中… chmod\chown 之前如果文件权限不足,直接就是 chmod 777 filename/dirname ,这并不是一个好习惯。 r(读权限):值为4w(写权限)&a…...

如何用Python免费下载B站4K大会员视频:bilibili-downloader完整指南

如何用Python免费下载B站4K大会员视频:bilibili-downloader完整指南 【免费下载链接】bilibili-downloader B站视频下载,支持下载大会员清晰度4K,持续更新中 项目地址: https://gitcode.com/gh_mirrors/bil/bilibili-downloader 还在为…...

)

ABAP - SMW0实现Excel模板下载与数据上传解析全流程指南(附完整代码)

1. 为什么需要Excel模板下载与上传功能 在企业级应用开发中,Excel模板的下载与上传功能几乎是标配。想象一下这样的场景:财务部门需要每月收集各部门的预算数据,如果让每个部门直接在SAP系统里录入,操作复杂且容易出错。而提供一个…...

告别官方文档!用IntelliJ IDEA 2023.3 + Flutter 3.19 搭建环境,我踩过的坑你别再踩了

告别官方文档!用IntelliJ IDEA 2023.3 Flutter 3.19 搭建环境,我踩过的坑你别再踩了 如果你正在寻找一份真正实用的Flutter环境搭建指南,那么你来对地方了。作为一个刚从官方文档和无数博客教程中"幸存"下来的开发者,我…...

ai辅助开发:借助快马平台ai模型打造智能自适应的openclaw chrome数据抓取插件

今天想和大家分享一个最近用AI技术增强网页数据抓取效率的实践——开发一个叫OpenClaw的智能Chrome插件。这个插件的特别之处在于,它不仅能抓取数据,还能通过AI理解网页结构,自动适应不同网站,大大减少了手动编写抓取规则的工作量…...

实战复盘——从日志到后门:一次完整的Linux挖矿病毒kswapd0应急响应

1. 异常告警:CPU占用300%的紧急响应 那天下午3点27分,监控系统突然弹出一条红色告警:某台核心服务器的CPU使用率飙升至300%。作为安全工程师,我立刻放下手中的咖啡,开始排查这个异常情况。这种CPU异常飙升通常只有两种…...

MySQL数据库基础聚合函数

聚合函数...

Nginx + FFmpeg 核心配置

Nginx FFmpeg 核心配置(2 种最实用方案)我给你最简、能直接用的配置,不用你自己改半天,分两种场景:Nginx 接收 FFmpeg 推流(直播)Nginx 调用 FFmpeg 自动转码(高清 / 标清ÿ…...

电话号码定位技术:三步实现手机号码精准定位的终极指南

电话号码定位技术:三步实现手机号码精准定位的终极指南 【免费下载链接】location-to-phone-number This a project to search a location of a specified phone number, and locate the map to the phone number location. 项目地址: https://gitcode.com/gh_mir…...

DFT工程师的隐藏技巧:深入解读TestMAX中Shared与Dedicated Wrapper Cell的选择策略

DFT工程师的隐藏技巧:深入解读TestMAX中Shared与Dedicated Wrapper Cell的选择策略 在芯片设计的可测试性设计(DFT)领域,Wrapper Cell的选择往往被视为一项"黑盒"操作——工程师们习惯依赖EDA工具自动完成,却…...

Qwen3-4B极速体验:流式输出+多轮记忆,打造丝滑文本交互

Qwen3-4B极速体验:流式输出多轮记忆,打造丝滑文本交互 在当今AI技术快速发展的背景下,文本交互模型已经成为日常工作和创作的重要助手。Qwen3-4B-Instruct-2507作为阿里通义千问系列中的纯文本优化版本,通过移除视觉模块冗余&…...