【FPGA项目】bin文件ram存取回环测试

🎉欢迎来到FPGA专栏~bin文件ram存取回环测试

- ☆* o(≧▽≦)o *☆嗨~我是小夏与酒🍹

- ✨博客主页:小夏与酒的博客

- 🎈该系列文章专栏:FPGA学习之旅

- 文章作者技术和水平有限,如果文中出现错误,希望大家能指正🙏

- 📜 欢迎大家关注! ❤️

🎉 目录-bin文件ram存取回环测试

- 一、效果演示

- 🥝演示视频

- 🥝结果分析

- 二、说明

- 三、bin文件的生成

- 🔸bin文件介绍

- 🔸为什么使用bin文件作为数据载体发送给FPGA

- 🔸matlab生成bin文件

- 四、串口收发模块

- 五、回环系统搭建

- 🍍系统功能描述

- 🍍ram ip核设置

- 🍍RTL视图

- 🍍系统完整代码

一、效果演示

使用matlab生成100个1-100的32位随机整型数据,并将数据保存为bin文件;通过带有bin文件收发功能的串口调试助手发送给FPGA,再接收FPGA的回环数据。

🥝演示视频

演示视频-【FPGA】bin文件ram存取回环测试

🥝结果分析

matlab生成的随机数:

串口助手接收结果:

分析:

将串口助手接收框内的数据转换成10进制,并与matlab生成的数据进行对比,数值一致;串口助手接收框内的有效数据个数为100个,与matlab生成的数据个数一致;接收框内最后出现了FF,这个数据并不是bin文件中的数据,而是串口助手最后发送给FPGA的发送指令,该指令也被存入到了ram中(为了避免该现象的出现,可以在FPGA中对数据进行相关的判断处理,或者使用vio进行控制,即可解决)。

二、说明

需要该项目中的串口助手软件或者项目工程文件的小伙伴,直接加入QQ群,在群文件中搜索下载即可,QQ群:862135231。

matlab版本:R2020b

vivado版本:2020.2

开发板型号:AXKU040

接口连接如下所示:

三、bin文件的生成

🔸bin文件介绍

bin文件是二进制文件的缩写,通常用于存储计算机程序或数据。它们可以包含各种类型的信息,例如操作系统、应用程序和媒体文件。bin文件是计算机系统中最基本的文件类型之一,通常需要特定的软件才能打开和读取。

不同类型的bin文件可能需要不同的软件来打开,例如,图像bin文件可能需要图像查看器来打开,而文档bin文件可能需要文本编辑器来打开。

重点在这:

bin文件可以储存大量数据的二进制形式!

🔸为什么使用bin文件作为数据载体发送给FPGA

ChatGPT的回答:

bin文件作为一种固定的二进制数据格式,具有以下优点,使其成为向FPGA发送数据的常用载体:

- 紧凑性:bin文件通常比其他格式更紧凑,减少了数据传输的带宽和存储空间需求。

- 高效性:FPGA可以直接读取和处理二进制数据,而不需要进行格式转换,提高了数据处理的效率。

- 准确性:bin文件中的数据以精确的二进制形式表示,确保了数据的准确性和完整性。

- 通用性:bin文件是一种广泛使用的格式,可以在不同的系统和硬件平台之间进行传输和使用。

🔸matlab生成bin文件

运行如下代码,会在matlab脚本的根目录下生成bin文件:

%% bin文件生成代码

%----------------------------------------------------

% 首先生成1-100的double类型随机整数;

% 将double类型随机整数转换为32位数据;

% 将转换后的数据保存为bin文件。

%----------------------------------------------------

clear;

clc;

close all;

% 生成1-100的double类型随机整数

random_numbers = randi([1 100], 1, 100);% 将double类型数据转换为uint32类型

random_numbers_uint32 = uint32(random_numbers);% 将数据保存为bin文件

fid = fopen('random_numbers.bin', 'wb');

fwrite(fid, random_numbers_uint32, 'uint32');

fclose(fid);disp('随机数已生成并保存为 random_numbers.bin');四、串口收发模块

关于串口收发模块的详细讲解,请点击如下两篇文章进行学习:

串口发送模块:【FPGA零基础学习之旅#13】串口发送模块设计与验证;

串口接收模块:【FPGA零基础学习之旅#15】串口接收模块设计与验证(工业环境)。

在此附上模块代码:

串口发送模块:

//

//模块名称:串口发送模块

//

module uart_byte_tx(input Clk,input Rst_n,input [7:0] data_byte,input send_en,input [2:0] baud_set,output reg uart_tx,output reg Tx_Done,output reg uart_state

);reg bps_clk;//波特率时钟reg [15:0]div_cnt;//分频计数器reg [15:0]bps_DR;//分频计数最大值reg [3:0]bps_cnt;//波特率计数时钟//定义数据的起始位和停止位localparam START_BIT = 1'b0;localparam STOP_BIT = 1'b1;reg [7:0]r_data_byte;//数据寄存器//--------<uart状态模块>-------- always@(posedge Clk or negedge Rst_n)beginif(!Rst_n)uart_state <= 1'b0;else if(send_en)uart_state <= 1'b1;else if(bps_cnt == 4'd11)//bps_cnt计数达到11次,即发送结束uart_state <= 1'b0;elseuart_state <= uart_state;end//--------<使能分频计数模块>-------

// assign en_cnt = uart_state;//--------<寄存待发送的数据,使数据保持稳定>--------always@(posedge Clk or negedge Rst_n)beginif(!Rst_n)r_data_byte <= 8'd0;else if(send_en)r_data_byte <= data_byte;elser_data_byte <= r_data_byte;end//--------<波特率查找表>-------- always@(posedge Clk or negedge Rst_n)beginif(!Rst_n)bps_DR <= 16'd5207;else begincase(baud_set)0:bps_DR <= 16'd5207;1:bps_DR <= 16'd2603;2:bps_DR <= 16'd1301;3:bps_DR <= 16'd867;4:bps_DR <= 16'd433;default:bps_DR <= 16'd5207;endcaseend end//--------<Div_Cnt模块>--------

//得到不同计数周期的计数器always@(posedge Clk or negedge Rst_n)beginif(!Rst_n)div_cnt <= 16'd0;else if(uart_state)begin // assign en_cnt = uart_state;if(div_cnt == bps_DR)div_cnt <= 16'd0;elsediv_cnt <= div_cnt + 1'b1;endelsediv_cnt <= 16'd0;end

//--------<bps_clk信号的产生>-------- always@(posedge Clk or negedge Rst_n)beginif(!Rst_n)bps_clk <= 1'b0;else if(div_cnt == 16'd1)bps_clk <= 1'b1;elsebps_clk <= 1'b0;end//--------<bps_cnt计数模块>-------- always@(posedge Clk or negedge Rst_n)beginif(!Rst_n)bps_cnt <= 4'd0;else if(bps_cnt == 4'd11)//clr信号bps_cnt <= 4'd0;else if(bps_clk)bps_cnt <= bps_cnt + 1'b1;elsebps_cnt <= bps_cnt;end//--------<Tx_Done模块>-------- always@(posedge Clk or negedge Rst_n)beginif(!Rst_n)Tx_Done <= 1'b0;else if(bps_cnt == 4'd11)Tx_Done <= 1'b1;elseTx_Done <= 1'b0;end//--------<数据位输出模块-10选1多路器>-------- always@(posedge Clk or negedge Rst_n)beginif(!Rst_n)uart_tx <= 1'b1;else begincase(bps_cnt)0:uart_tx <= 1'b1;1:uart_tx <= START_BIT;2:uart_tx <= r_data_byte[0];3:uart_tx <= r_data_byte[1];4:uart_tx <= r_data_byte[2];5:uart_tx <= r_data_byte[3];6:uart_tx <= r_data_byte[4];7:uart_tx <= r_data_byte[5];8:uart_tx <= r_data_byte[6];9:uart_tx <= r_data_byte[7];10:uart_tx <= STOP_BIT;default:uart_tx <= 1'b1;endcaseendendendmodule串口接收模块:

//

//模块名称:串口接收模块(工业环境)

//

module uart_byte_rx(input Clk,//50Minput Rst_n,input [2:0] baud_set,input data_rx,output reg [7:0] data_byte,output reg Rx_Done

);reg s0_Rx,s1_Rx;//同步寄存器reg tmp0_Rx,tmp1_Rx;//数据寄存器reg [15:0]bps_DR;//分频计数器计数最大值reg [15:0]div_cnt;//分频计数器reg bps_clk;//波特率时钟reg [7:0]bps_cnt;reg uart_state;reg [2:0] r_data_byte [7:0];reg [2:0]START_BIT;reg [2:0]STOP_BIT;wire nedge;//--------<同步寄存器处理>--------

//用于消除亚稳态always@(posedge Clk or negedge Rst_n)beginif(!Rst_n)begins0_Rx <= 1'b0;s1_Rx <= 1'b0;endelse begins0_Rx <= data_rx;s1_Rx <= s0_Rx;endend//--------<数据寄存器处理>-------- always@(posedge Clk or negedge Rst_n)beginif(!Rst_n)begintmp0_Rx <= 1'b0;tmp1_Rx <= 1'b0;endelse begintmp0_Rx <= s1_Rx;tmp1_Rx <= tmp0_Rx;endend//--------<下降沿检测>-------- assign nedge = !tmp0_Rx & tmp1_Rx;//--------<div_cnt模块>--------

//得到不同计数周期的计数器always@(posedge Clk or negedge Rst_n)beginif(!Rst_n)div_cnt <= 16'd0;else if(uart_state)beginif(div_cnt == bps_DR)div_cnt <= 16'd0;elsediv_cnt <= div_cnt + 1'b1;endelsediv_cnt <= 16'd0;end

//--------<bps_clk信号的产生>-------- always@(posedge Clk or negedge Rst_n)beginif(!Rst_n)bps_clk <= 1'b0;else if(div_cnt == 16'd1)bps_clk <= 1'b1;elsebps_clk <= 1'b0;end//--------<bps_clk计数模块>-------- always@(posedge Clk or negedge Rst_n)beginif(!Rst_n)bps_cnt <= 8'd0;else if(bps_cnt == 8'd159 || (bps_cnt == 8'd12 && (START_BIT > 2)))bps_cnt <= 8'd0;else if(bps_clk)bps_cnt <= bps_cnt + 1'b1;elsebps_cnt <= bps_cnt;end//--------<Rx_Done模块>-------- always@(posedge Clk or negedge Rst_n)beginif(!Rst_n)Rx_Done <= 1'b0;else if(bps_cnt == 8'd159)Rx_Done <= 1'b1;elseRx_Done <= 1'b0;end //--------<波特率查找表>-------- always@(posedge Clk or negedge Rst_n)beginif(!Rst_n)bps_DR <= 16'd324;else begincase(baud_set)0:bps_DR <= 16'd324;1:bps_DR <= 16'd162;2:bps_DR <= 16'd80;3:bps_DR <= 16'd53;4:bps_DR <= 16'd26;default:bps_DR <= 16'd324;endcaseend end//--------<采样数据接收模块>-------- always@(posedge Clk or negedge Rst_n)beginif(!Rst_n)beginSTART_BIT <= 3'd0;r_data_byte[0] <= 3'd0; r_data_byte[1] <= 3'd0;r_data_byte[2] <= 3'd0; r_data_byte[3] <= 3'd0;r_data_byte[4] <= 3'd0; r_data_byte[5] <= 3'd0;r_data_byte[6] <= 3'd0; r_data_byte[7] <= 3'd0;STOP_BIT <= 3'd0;endelse if(bps_clk)begincase(bps_cnt)0:beginSTART_BIT <= 3'd0;r_data_byte[0] <= 3'd0;r_data_byte[1] <= 3'd0;r_data_byte[2] <= 3'd0;r_data_byte[3] <= 3'd0;r_data_byte[4] <= 3'd0;r_data_byte[5] <= 3'd0;r_data_byte[6] <= 3'd0;r_data_byte[7] <= 3'd0;STOP_BIT <= 3'd0; end6,7,8,9,10,11:START_BIT <= START_BIT + s1_Rx;22,23,24,25,26,27:r_data_byte[0] <= r_data_byte[0] + s1_Rx;38,39,40,41,42,43:r_data_byte[1] <= r_data_byte[1] + s1_Rx;54,55,56,57,58,59:r_data_byte[2] <= r_data_byte[2] + s1_Rx;70,71,72,73,74,75:r_data_byte[3] <= r_data_byte[3] + s1_Rx;86,87,88,89,90,91:r_data_byte[4] <= r_data_byte[4] + s1_Rx;102,103,104,105,106,107:r_data_byte[5] <= r_data_byte[5] + s1_Rx;118,119,120,121,122,123:r_data_byte[6] <= r_data_byte[6] + s1_Rx;134,135,136,137,138,139:r_data_byte[7] <= r_data_byte[7] + s1_Rx;150,151,152,153,154,155:STOP_BIT <= STOP_BIT + s1_Rx;default:beginSTART_BIT <= START_BIT;r_data_byte[0] <= r_data_byte[0];r_data_byte[1] <= r_data_byte[1];r_data_byte[2] <= r_data_byte[2];r_data_byte[3] <= r_data_byte[3];r_data_byte[4] <= r_data_byte[4];r_data_byte[5] <= r_data_byte[5];r_data_byte[6] <= r_data_byte[6];r_data_byte[7] <= r_data_byte[7];STOP_BIT <= STOP_BIT;endendcaseendend//--------<数据状态判定模块>-------- always@(posedge Clk or negedge Rst_n)beginif(!Rst_n)data_byte <= 8'd0;else if(bps_cnt == 8'd159)begindata_byte[0] <= r_data_byte[0][2];data_byte[1] <= r_data_byte[1][2];data_byte[2] <= r_data_byte[2][2];data_byte[3] <= r_data_byte[3][2];data_byte[4] <= r_data_byte[4][2];data_byte[5] <= r_data_byte[5][2];data_byte[6] <= r_data_byte[6][2];data_byte[7] <= r_data_byte[7][2];endelse;end//--------<uart_state模块>-------- always@(posedge Clk or negedge Rst_n)beginif(!Rst_n)uart_state <= 1'b0;else if(nedge)uart_state <= 1'b1;else if(Rx_Done || (bps_cnt == 8'd12 && (START_BIT > 2)))uart_state <= 1'b0;elseuart_state <= uart_state;endendmodule五、回环系统搭建

🍍系统功能描述

系统串口波特率设置为:115200;

功能描述: 为了避免使用按键等作为触发或者控制信号,本项目使用串口指令控制整个系统的运行,因此设置了十六进制的fe和ff指令。通过串口助手发送十六进制的fe指令使能ram的储存,再通过发送十六进制的ff指令让FPGA将ram中的数据通过串口发送出来。

🍍ram ip核设置

选择普通双端口类型:

由于串口接收到的数据位宽都是8位,将ram的输入端口设置为8位便于存储和控制,深度选择为2048,一直使能:

ram中的数据也是直接通过串口输出,因此输出端口的数据位宽也设置为8位便于控制和读取,选择使用使能引脚控制ram读取数据:

在Summary中可以看到每个端口访问数据的地址位宽:

🍍RTL视图

🍍系统完整代码

uart_top.v:

`timescale 1ns / 1psmodule uart_top(input sys_clk_p,input sys_clk_n,input rst_n,input uart_rx,output uart_tx

);localparam baud_set = 3'b100;wire locked;wire clk_r;wire clk;wire [7:0] data_byte;reg En;reg send_en;reg [11-1:0] data_in_cnt;wire Rx_Done;wire write_en;reg [10:0] addrb;wire read_en;wire [7:0] data_byte_tx;clk50MHz instance_name(// Clock out ports.clk_out1(clk_r), // output clk_out1// Status and control signals.reset(!rst_n), // input reset.locked(locked), // output locked// Clock in ports.clk_in1_p(sys_clk_p), // input clk_in1_p.clk_in1_n(sys_clk_n)); // input clk_in1_nassign clk = (locked)?clk_r:1'b0;uart_byte_rx inst_uart_byte_rx(.Clk (clk),.Rst_n (rst_n),.baud_set (baud_set),.data_rx (uart_rx),.data_byte (data_byte),.Rx_Done (Rx_Done));//--------------------<system_ctrl>--------------------------------always@(posedge clk or negedge rst_n)beginif(!rst_n)En <= 1'b0;else if(data_byte == 8'hfe)En <= 1'b1;elseEn <= En;endalways@(posedge clk or negedge rst_n)beginif(!rst_n)send_en <= 1'b0;else if(data_byte == 8'hff && addrb < 11'd2000)send_en <= 1'b1;else if(addrb == 11'd2000)send_en <= 1'b0;elsesend_en <= send_en;end

//-----------------------------------------------------------------//--------------------<data_in_cnt>--------------------------------always@(posedge clk or negedge rst_n)beginif(!rst_n)data_in_cnt <= 11'd0;else if((En) && (data_in_cnt < 11'd2047) && Rx_Done)data_in_cnt <= data_in_cnt + 1'b1;else if(data_in_cnt == 11'd2047)data_in_cnt <= 11'd0;elsedata_in_cnt <= data_in_cnt;end

//-----------------------------------------------------------------assign write_en = (En && !(send_en))?1'b1:1'b0;ram_ip ram_8_2048_8(.clka (clk), // input wire clka.wea (write_en), // input wire [0 : 0] wea.addra (data_in_cnt), // input wire [10 : 0] addra.dina (data_byte), // input wire [7 : 0] dina.clkb (clk), // input wire clkb.enb (read_en), // input wire enb.addrb (addrb), // input wire [10 : 0] addrb.doutb (data_byte_tx) // output wire [7 : 0] doutb);assign read_en = (send_en && Tx_Done)?1'b1:1'b0;always@(posedge clk or negedge rst_n)beginif(!rst_n)addrb <= 11'd0;else if(Tx_Done)addrb <= addrb + 1'b1;elseaddrb <= addrb;enduart_byte_tx inst_uart_byte_tx(.Clk (clk),.Rst_n (rst_n),.data_byte (data_byte_tx),.send_en (send_en),.baud_set (baud_set),.uart_tx (uart_tx),.Tx_Done (Tx_Done),.uart_state ());endmodule

🧸结尾

- ❤️ 感谢您的支持和鼓励! 😊🙏

- 📜您可能感兴趣的内容:

- 【FPGA零基础学习之旅#17】搭建串口收发与储存双口RAM系统

- 【Python】串口通信-与FPGA、蓝牙模块实现串口通信(Python+FPGA)

- 【Arduino TinyGo】【最新】使用Go语言编写Arduino-环境搭建和点亮LED灯

- 【全网首发开源教程】【Labview机器人仿真与控制】Labview与Solidworks多路支配关系-四足爬行机器人仿真与控制

相关文章:

【FPGA项目】bin文件ram存取回环测试

🎉欢迎来到FPGA专栏~bin文件ram存取回环测试 ☆* o(≧▽≦)o *☆嗨~我是小夏与酒🍹 ✨博客主页:小夏与酒的博客 🎈该系列文章专栏:FPGA学习之旅 文章作者技术和水平有限,如果文中出现错误,希望大…...

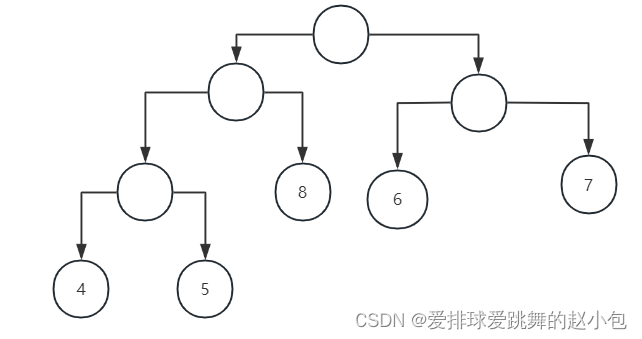

北航数据结构与程序设计第五次作业选填题复习

选填题考的很多都是基础概念,对于巩固复习一些仡佬拐角的知识点是很有用的。非北航学生也可以来看看这些题,这一节主要是树方面的习题: 一、 我们首先需要知道一个公式 这是证明: 知道了这个公式,我们把题目中的数据…...

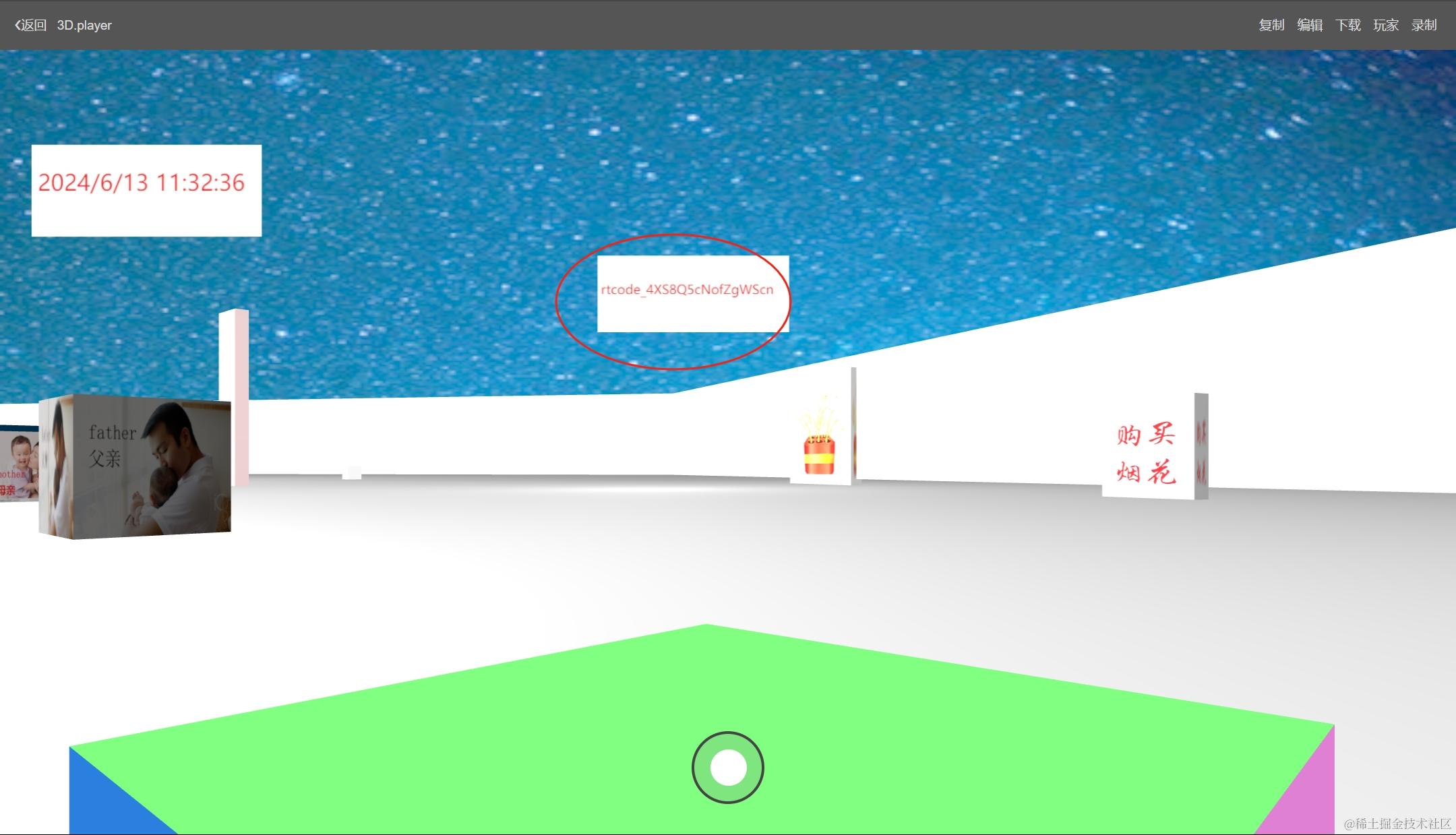

【WEB前端2024】3D智体编程:乔布斯3D纪念馆-第40课-实时订阅后端数据

【WEB前端2024】3D智体编程:乔布斯3D纪念馆-第40课-实时订阅后端数据 使用dtns.network德塔世界(开源的智体世界引擎),策划和设计《乔布斯超大型的开源3D纪念馆》的系列教程。dtns.network是一款主要由JavaScript编写的智体世界引…...

系统集成知识科普:核心原理与关键技术

目录 1.系统集成的核心原理 1.1 模块化原理 1.1.1 定义: 1.1.2 优势: 1.1.3 实现方式: 1.2 标准化原理 1.2.1 定义: 1.2.2 作用: 1.2.3 实践案例: 1.2.4 制定与遵循: 1.3 协同性原理…...

Coze+Discord:打造你的免费AI助手(教您如何免费使用GPT-4o/Gemini等最新最强的大模型/Discord如何正确连接Coze)

文章目录 📖 介绍 📖🏡 演示环境 🏡📒 文章内容 📒📝 准备Discord📝 准备Coze🔌 连接💡 测试效果⚓️ 相关链接 ⚓️📖 介绍 📖 你是否想免费使用GPT-4o/Gemini等最新最强的大模型,但又不想花费高昂的费用?本文将教你如何通过Coze搭建Bot,并将其转发…...

「OC」UI练习(二)——照片墙

「OC」UI练习——照片墙 文章目录 「OC」UI练习——照片墙UITapGestureRecognizer介绍照片墙实现 UITapGestureRecognizer介绍 UITapGestureRecognizer是UIKit框架中的一个手势识别器类,用于检测用户在视图上的轻击手势。它是UIGestureRecognizer的一个子类&#x…...

一手洞悉巴西slot游戏包投放本土网盟CPI广告优势

一手洞悉巴西slot游戏包投放本土网盟CPI广告优势 在巴西这片热土上,slot游戏包的投放本土网盟CPI广告是一项既充满挑战又富有机遇的任务。CPI(Cost Per Install)广告模式,即按安装付费,已经成为许多游戏开发商推广产品…...

中国环保网引领元宇宙新纪元 -探索绿色未来

在数字化浪潮的推动下,元宇宙这一概念正逐渐进入公众视野,成为科技与创新交汇的新前沿。作为环境保护的坚定倡导者,中国环保网秉承着推动绿色发展、构建生态文明的使命,正式踏入元宇宙领域,旨在通过高科技手段为环保事…...

2024最新流媒体在线音乐系统网站源码 音乐社区 多语言开心版

本文来自:2024最新流媒体在线音乐系统网站源码 音乐社区 多语言开心版 - 源码1688 应用介绍 简介: 2024最新流媒体在线音乐系统网站源码| 音乐社区 | 多语言 | 开心版 图片:...

【Java】解决Java报错:FileNotFoundException

文章目录 引言1. 错误详解2. 常见的出错场景2.1 文件路径错误2.2 文件名拼写错误2.3 文件权限问题2.4 文件路径未正确拼接 3. 解决方案3.1 检查文件路径3.2 使用相对路径和类路径3.3 检查文件权限3.4 使用文件选择器 4. 预防措施4.1 使用配置文件4.2 使用日志记录4.3 使用单元测…...

Seate分布式锁

XA模式 在第一阶段资源协调者(TC)会向资源管理者(RM)发出一个准备的请求,RM开始处理自身的业务,处理完成后不提交事务,而是向TC响应一个执行结果,表明自己成功还是失败,如…...

金融科技助力绿色金融:可持续发展新动力

随着全球气候变化和环境问题的日益严重,绿色金融作为推动环境保护和经济可持续发展的重要手段,已经受到越来越多的关注。而金融科技,作为科技与金融深度融合的产物,正以其独特的优势为绿色金融的发展注入新动力。本文将探讨金融科…...

灾备建设中虚拟机细粒度恢复的含义及技术使用

灾备建设中为了考虑虚拟机恢复的效率与实际的用途,在恢复上出了普通的恢复虚拟机,也有其余的恢复功能,比如瞬时恢复,细粒度恢复等。这里谈的就是细粒度恢复。 首先细粒度恢复是什么,这个恢复可以恢复单个备份下来的文…...

十种排序方法

目录 1.冒泡排序(Bubble Sort)代码实现 2.选择排序(Selection Sort)代码实现 3.插入排序(Insertion Sort) 4.希尔排序(Shell Sort)代码实现 5.快速排序(Quick Sort&…...

docker-compose启动oracle11、并使用navicat进行连接

一、docker-compose.yml version: 3.9 services:oracle:image: registry.cn-hangzhou.aliyuncs.com/helowin/oracle_11grestart: alwaysprivileged: truecontainer_name: oracle11gvolumes:- ./data:/u01/app/oracleports:- 1521:1521network_mode: "host"logging:d…...

使用ffmpeg进行音频处理

音频处理是数字媒体制作中不可或缺的一部分,而ffmpeg作为一款强大的多媒体处理工具,为我们提供了丰富的音频处理功能。 一、查看音频信息 在处理音频之前,了解音频的基本信息是非常重要的。FFmpeg的ffprobe工具可以帮助我们查看音频的详细信息,如采样率、位深等。 示例命…...

重装系统,以及设置 深度 学习环境

因为联想y7000在ubantu系统上连不到wifi,所以打算弄双系统 第一步:下载win10镜像,之后在系统用gparted新建个分区,格式化成ntfs,用来装win10系统 第二步,制作win10启动盘,这个需要先把u盘用disks格式化&a…...

深入理解渲染引擎:打造逼真图像的关键

在数字世界中,图像渲染是创造逼真视觉效果的核心技术。渲染引擎,作为这一过程中的关键组件,负责将二维或三维的模型、纹理、光照等数据转化为人们肉眼可见的二维图像。本文将深入探讨渲染引擎的工作原理及其在打造逼真图像中所起的关键作用。…...

【LeetCode最详尽解答】128_最长连续序列 Longest-Consecutive-Sequence

欢迎收藏Star我的Machine Learning Blog:https://github.com/purepisces/Wenqing-Machine_Learning_Blog。如果收藏star, 有问题可以随时与我交流, 谢谢大家! 链接: 128_最长连续序列 直觉 输入: nums [100, 4, 200, 1, 3, 2]输出: 4解释: 最长的连续元素序列是…...

盒马鲜生礼品卡如何使用?

盒马鲜生的礼品卡除了在门店用以外,还有什么用处啊 毕竟家附近的盒马距离都太远了,好多卡最后都闲置下来了,而且以前都不知道盒马卡还会过期,浪费了好多 还好最近发现了 盒马鲜生礼品卡现在也能在收卡云上兑现了,而且…...

ISO/SAE 21434:2021 逐条审核判定表

A 章节号|B 条款|C 要求内容|D 符合性|E 证据 / 说明|F:不符合整改项符合性选项:符合 / 部分符合 / 不符合 / 不适用章节号条款审核要求内容符合性证据 / 备注整改项44.1建立网络安全生命周…...

HunyuanVideo-Foley高算力适配:RTX4090D显存利用率优化至92%实测

HunyuanVideo-Foley高算力适配:RTX4090D显存利用率优化至92%实测 1. 镜像概述与核心优势 HunyuanVideo-Foley私有部署镜像专为视频与音效生成任务深度优化,基于RTX 4090D 24GB显存硬件平台打造。经过CUDA 12.4与驱动550.90.07的针对性调优,…...

C语言开发者视角:Kandinsky-5.0-I2V-Lite-5s高性能推理引擎调用

C语言开发者视角:Kandinsky-5.0-I2V-Lite-5s高性能推理引擎调用 1. 引言:当静态告警遇上动态生成 想象一下这样的场景:工业监控系统捕捉到设备异常,触发静态告警图片。传统方案中,这张图片需要人工介入分析ÿ…...

手把手教你用Cline插件零成本调用AI Ping的GLM-4.7,5分钟搞定一个React组件

5分钟实战:用Cline插件调用GLM-4.7生成React表单组件 最近在帮团队优化一个后台管理系统时,发现表单页面的重复开发消耗了大量时间。直到同事推荐了AI Ping的GLM-4.7模型配合VSCode的Cline插件,才真正体会到AI辅助编程的"开箱即用"…...

Phi-4-mini-reasoning真实案例:教育SaaS平台月均百万次推理调用的稳定性保障

Phi-4-mini-reasoning真实案例:教育SaaS平台月均百万次推理调用的稳定性保障 1. 项目背景与挑战 在教育科技行业,数学和逻辑推理类题目的自动解答一直是技术难点。某头部教育SaaS平台在2023年接入了Phi-4-mini-reasoning模型,用于其在线作业…...

利用MathType公式与GLM-OCR结合实现理科试卷自动批改

利用MathType公式与GLM-OCR结合实现理科试卷自动批改 1. 引言 批改理科试卷,尤其是数学、物理这类包含大量公式和符号的试卷,对老师来说一直是个耗时费力的活儿。一张试卷,既要看文字答案对不对,又要检查复杂的公式推导有没有写…...

智能视频PPT提取:从动态内容到静态文档的高效转化方案

智能视频PPT提取:从动态内容到静态文档的高效转化方案 【免费下载链接】extract-video-ppt extract the ppt in the video 项目地址: https://gitcode.com/gh_mirrors/ex/extract-video-ppt 场景痛点:视频内容提取的三大核心挑战 如何从90分钟的…...

窗口效率革命:WindowResizer重构数字空间管理新范式

窗口效率革命:WindowResizer重构数字空间管理新范式 【免费下载链接】WindowResizer 一个可以强制调整应用程序窗口大小的工具 项目地址: https://gitcode.com/gh_mirrors/wi/WindowResizer 问题诊断:被忽视的数字空间效率黑洞 现代办公的隐形枷…...

HsMod终极指南:5步打造你的专属炉石传说模改体验

HsMod终极指南:5步打造你的专属炉石传说模改体验 【免费下载链接】HsMod Hearthstone Modify Based on BepInEx 项目地址: https://gitcode.com/GitHub_Trending/hs/HsMod HsMod是一款基于BepInEx框架的炉石传说模改插件,为玩家提供全面的游戏体验…...

Qwen3.5-9B-AWQ-4bitWeb界面使用教程:上传/提问/防重复提交/结果解析全流程

Qwen3.5-9B-AWQ-4bit Web界面使用教程:上传/提问/防重复提交/结果解析全流程 1. 认识Qwen3.5-9B-AWQ-4bit模型 Qwen3.5-9B-AWQ-4bit是一个强大的多模态AI模型,它能够同时理解图片和文字。想象一下,你有一个既会看图片又会回答问题的智能助手…...