米联客-FPGA程序设计Verilog语法入门篇连载-15 Verilog语法_跨时钟域设计

软件版本:无

操作系统:WIN10 64bit

硬件平台:适用所有系列FPGA

板卡获取平台:https://milianke.tmall.com/

登录“米联客”FPGA社区 http://www.uisrc.com 视频课程、答疑解惑!

1概述

本小节主要讲解Verilog语法的跨时钟域设计,需要掌握跨时钟域时快慢时钟之间信号是如何同步的。

2跨时钟域慢速到快速时钟

由慢时钟到快时钟的信号传递,就传输的信号位宽一般分为两种,单比特信号和多比特信号。下面我们分开进行讨论。

2.1 单比特信号

上一节课同步异步设计有提到慢时钟到快时钟的设计方法,一般分析,快时钟域的信号总能采集到慢时钟域的信号,但是如果存在异步时钟域可能会导致采样数据出错,因此需要进行时钟同步处理。同步处理针对单比特信号采取打三拍进行同步。

异步时钟域的信号从一个时钟域进入另一个时钟域之前,将该信号用三级触发器缓存两次,可有效降低因为时序而导致的亚稳态问题。例:

module async_data(input clk_1, //输入时钟clk_1input data_1, //输入数据data_1input clk_2, //输入时钟clk_2 output data_2 //输出数据data_2);reg [2:0] data_ff ; //寄存器变量data_ffalways @(posedge clk_2) //clk_2敏感posedge,上升沿触发begin data_ff <= {data_ff[1:0], data_1}; //data_1数据采样End //data_ff[0]表示最新采样的数据,!data_ff[1]为上一个时钟周期采样的数据assign data_2 = !data_ff[2] && data_ff[1]; //最新的电平为1,之前的电平为0,判断为上升沿检测

clk_1为慢时钟,clk_2为快时钟,将data_1在快时钟域进行三拍缓存,检测信号的上升沿,此时将信号进行了同步化。

2.2多比特信号

对于多比特信号的传输,我们要考虑两种情况,即单时钟周期突发信号和多时钟周期连续信号的传输。

针对单时钟周期突发信号我们可以采用利用打拍法延迟采样。例:

module async_data_1(input clk_1, //输入时钟clk_1input [7:0] data_in, //输入数据data_1input din_en, //输入突发信号input clk_2, //输入时钟clk_2output reg[7:0] data_out, //输出数据dataoutput reg dout_en //输出突发数据有效信号);reg [2:0] din_en_ff ;wire din_en_pos;always @(posedge clk_2 )begindin_en_ff <= {din_en_ff[1:0], din_en} ; //输入突发信号打拍缓存2拍endassign din_en_pos = !din_en_ff[2] && din_en_ff[1] ; //din_en_ff[1]为新缓存的信号,为1时有效,din_en_ff[2]为上一拍缓存的信号//为0时有效,所以din_en_pos为捕捉 din_en信号上升沿always @(posedge clk_2)beginif (din_en_pos)data_out <= din ; //din_en_pos信号拉高,说明数据有效,将输入数据输出else;endalways @(posedge clk_2 )begindout_en <= din_en_pos ; //输出突发数据有效信号为din_en_pos信号endendmodule

针对多时钟周期连续信号我们可以采用检测慢时钟的边沿进行采样。如果两个时钟的频率相差较小,可能还需要对数据进行延迟缓存,以保证采集到的是当拍时钟的数据;如果两个时钟的频率相差较大,数据采样时刻可以通过计数的方法获得,而不用对数据进行缓存。例:

module async_data_2(input clk_1,input [7:0] data_in,input din_en,input clk_2,output reg[7:0] data_out,output reg dout_en);reg [3:0] din_en_ff ;wire din_edge_pos;reg [3:0] cnt ;always @(posedge clk_2 )begindin_en_ff <= {din_en_ff[2:0], clk_1} ;endassign din_edge_pos = !din_en_ff[2] && din_en_ff[1] ;always @(posedge clk_2) //clk_2为驱动时钟,进行计数if (din_edge_pos & din_en) //din_edge_pos信号为捕捉到上升沿,且din_en信号持续拉高cnt <= 4'h0 ;else if (cnt != 4'hf) //计数值为4'hfcnt <= cnt + 1'b1 ;endalways @(posedge clk_2) //clk_2为驱动时钟beginif (din_en && cnt == 7) //din_en信号持续拉高并且完成7次计数时,确认数据有效data_out <= din ; //数据完成赋值else;endalways @(posedge clk_2 )beginif(din_en && cnt == 8) //din_en信号持续拉高并且完成8次计数时,确认数据有效dout_en <= 1 ; //输出突发数据有效信号进行拉高elsedout_en <= 0;endendmodule

3跨时钟域快速到慢速时钟

由快时钟到慢时钟的信号传递,就传输的信号位宽一般分为两种,单比特信号和多比特信号。下面我们分开进行讨论。

3.1 单比特信号

由快时钟到慢时钟的单比特信号传递,我们需要考虑信号本身是单时钟周期的脉冲信号还是连续多个周期的电平信号。针对单时钟周期的脉冲信号,最好的传送方法是握手法,假设单时钟周期脉冲信号的高电平为有效信号,其基本原理如下。

(1) 快时钟域对脉冲信号进行检测,检测有高电平时输出一个高电平信号。快时钟域输出高电平信号时,保持输出信号为高电平状态。

(2) 慢时钟域对快时钟域的检测信号进行延迟打拍采样。因为此时的脉冲信号被快时钟域保持拉高状态,延迟打拍会采集到该信号。

(3) 慢时钟域确认采样得到高电平检测信号后,再反馈信号给快时钟域。

(4) 快时钟域对反馈信号进行延迟打拍采样。如果检测到反馈信号为高电平,证明慢时钟域已经接收到有效的高电平信号。如果此时快时钟域自身逻辑不再要求脉冲信号为高电平状态,拉低快时钟域的脉冲信号即可。

此方法是通过相互握手的方式对窄脉冲信号进行脉宽扩展。例:

module pulse_fast_2_slow(input rst_n, //复位信号input clk_fast, //快时钟input pulse_fast, //快时钟握手信号input clk_slow, //慢时钟output pulse_slow //慢时钟握手信号);wire clear_up ;reg pulse_fast_detect ;reg [1:0] pulse_fast_detect_ff ;reg [1:0] pulse_slow_2_fast ;always@(posedge clk_fast or negedge rst_n)beginif (!rst_n)pulse_fast_detect <= 1'b0 ; //pulse_fast_detect拉低复位else if (clear_up)pulse_fast_detect <= 1'b0 ; //pulse_fast_detect拉低复位else if (pulse_fast) //在快时钟域中对快时钟握手信号进行抓取pulse_fast_detect <= 1'b1 ; //信号抓取后,将 pulse_fast_detect持续拉高,可能为多个时钟周期,方便慢时钟域捕捉endalways@(posedge clk_slow or negedge rst_n)beginif (!rst_n)pulse_fast_detect_ff <= 3'b0 ; //缓存三拍清零elsepulse_fast_detect_ff <= {pulse_fast_detect_ff[0], pulse_fast_detect} ; //在慢时钟域中对pulse_fast_detect信号进行抓取End //不要求一翻转立刻捕捉到,只要求延时捕捉assign pulse_slow = pulse_fast_detect_ff[1] ; //取中间一拍进行输出给快时钟域always@(posedge clk_fast or negedge rst_n)beginif (!rst_n)pulse_slow_2_fast <= 1'b0 ;elsepulse_slow_2_fast <= {pulse_slow_2_fast[0], pulse_slow}; //快时钟域对慢时钟握手信号进行捕捉endassign clear_up = !pulse_fast && pulse_slow_2_fast[1]; //捕捉到回应,将 pulse_fast_detect拉低endmodule

3.2 多比特信号

当多位宽数据进行同步时,如果数据变化速率过快,就不能再使用延迟打拍采样的方法。因为此时数据各 bit 位变化的时间参差不齐,用异步时钟进行打拍采样,可能会采集到因路径延迟不同而导致的错误数据。解决此类异步问题的常用方法是采用异步 FIFO (First In First Out)进行数据的交换。异步FIFO在后面的一节课专门介绍。

相关文章:

米联客-FPGA程序设计Verilog语法入门篇连载-15 Verilog语法_跨时钟域设计

软件版本:无 操作系统:WIN10 64bit 硬件平台:适用所有系列FPGA 板卡获取平台:https://milianke.tmall.com/ 登录“米联客”FPGA社区 http://www.uisrc.com 视频课程、答疑解惑! 1概述 本小节主要讲解Verilog语法的…...

gradio 对话界面实现支持图片、视频正常显示

参考: https://www.gradio.app/docs/gradio/chatbot 问题: gradio网页输出视频nan;图片webp显示不出来 解决方法:需要通过gradio的Video、Image包装 代码: 这里下面启动个后端vlm模型(参考:https://blog.csdn.net/weixin_42357472/article/details/141126225),前端通…...

催收业务怎么提高接通率

提高催收呼叫业务的接通率是一个综合性的任务,需要从多个方面进行优化。以下是一些具体的策略和建议: 一、优化呼叫时间与频次 1. 选择合适的呼叫时间:通过分析目标客户的活跃时段,选择他们最可能接听电话的时间进行呼叫…...

动态生成sitemaps和robots.txt文件:提升SEO与网站可爬性

本文由 ChatMoney团队出品 在现代Web开发中,搜索引擎优化(SEO)是网站成功的关键因素之一。搜索引擎通过网络爬虫来索引网页,而sitemaps和robots.txt文件则是帮助这些爬虫更好地理解和索引网站内容的重要工具。 sitemaps简介 Sit…...

LeetCode 第二十五天 2024.8.12

1. :递增子序列 题目链接: 491. 非递减子序列 - 力扣(LeetCode) 应用条件:回溯 难点: 这道题的难点在于如何去重,肯定不能像我们在组合中去重那样对数组排序。而且我们是要对每一层进行去重,…...

Elasticsearch 全文查询详解

全文查询(Full-Text Query)是 Elasticsearch 中的核心功能之一,用于对非结构化文本数据进行高效检索。与结构化查询不同,全文查询不仅仅是简单的精确匹配,还包括对文本进行分析和处理,从而实现更复杂的搜索…...

20240810在荣品RK3588S-AHD开发板的预置Android13下挂载exFAT的256GB的TF卡

df -h mount fdisk无效 20240810在荣品RK3588S-AHD开发板的预置Android13下挂载exFAT的256GB的TF卡 2024/8/10 21:19 缘起:当时比较便宜96.9¥/想看看256GB的TF卡的高速卡的效果,就在京东入手了3张三星的高速TF卡。最近在弄RK3588S,…...

java基础进阶——log日志、类加载器、XML、单元测试、注解、枚举类

前言 这篇内容主要掌握的就是logback使用、理解类加载器、XML文件的编写,XML文档约束schema,用Dom4j解析XML文档,Xpath检索XML文档,完整使用Junit单元测试框架常用部分,注解的定义和使用,枚举类的定义和开发…...

《向量数据库指南》——控制Chatbot对话内容:Dopple AI的创新实践与用户体验优化

控制Chatbot对话内容:Dopple AI的创新实践与用户体验优化 在Chatbot技术日益成熟的今天,如何有效地控制对话内容,以满足用户多样化的需求,成为了开发者们关注的焦点。Dopple AI,作为一款先进的聊天机器人平台,通过其独特的交互设计和后端技术支持,为用户提供了前所未有…...

构建实时数据仓库:流式处理与实时计算技术解析

目录 一、流式处理 请求与响应 批处理 二、实时计算 三、Lambda架构 Lambda架构的缺点 四、Kappa架构 五、实时数据仓库解决方案 近年来随着业务领域的不断拓展,尤其像互联网、无线终端APP等行业应用的激增,产生的数据量呈指数级增长,对海量数…...

python算术表达式遗传算法

import random import operator import math# 定义可能的运算符和操作 ops {: ,-: -,*: *,/: /,sin: math.sin,cos: math.cos }# 随机生成一个表达式(个体) def generate_expression(depth0):if depth > 2: # 限制表达式的最大深度return str(rando…...

net.sf.jsqlparser.statement.select.SelectItem

今天一启动项目,出现了这个错误,仔细想了想,应该是昨天合并代码,导致的mybatis-plus版本冲突,以及分页PageHelper版本不兼容 可以看见这个我是最下边的 Caused by 报错信息,这个地方提示我 net .s…...

lua匹配MAC地址 正则表达式

LUA的正则表达式匹配很弱智,能不用lua就不要用lua。 %x表示十六进制数值 (%x%x):(%x%x):(%x%x):(%x%x):(%x%x):(%x%x)它不允许这样用: ((%x%x):){5}(%x%x)mac这还算好办,ipv4就难了,ipv6不可能,这样写下来那一串表达…...

Chainlit快速实现AI对话应用并将聊天数据的AWS S3 和 Azure Blob云服务中

自定义数据层 Literal AI 提供了最简单的方法来保存、分析和监控您的数据。 如果您正在考虑实现自定义数据层,请查看此处的示例以获取一些启发。 此外,我们非常希望看到社区主导的开源数据层实现并将其列在这里。如果您有兴趣做出贡献,请通过 Discord 与我们联系。 您需…...

浅谈性能优化(基于C++)

本文主要针对C的性能优化方法展开讨论。虽然这些方法也适用于一些其他语言,但由于C经常用于底层操作,提供了更多的优化空间;相比之下,诸如Python、Kotlin等高级语言由于其抽象程度更高,优化空间较少。 性能优化原理 …...

Python 报错:ModuleNotFoundError: No module named ‘Crypto‘

Crypto报错解决方案 Python 报错:ModuleNotFoundError: No module named Crypto前言问题解决方案 Python 报错:ModuleNotFoundError: No module named ‘Crypto’ 前言 Crypto是一个加密模块,它包含了多种加密算法,如 AES、DES、…...

和 UA(User Agent))

UE(User Equipment) 和 UA(User Agent)

UE(User Equipment) UE 是 用户设备,这是一个泛指的术语,涵盖了所有类型的终端设备,例如手机、电脑、平板、智能手表等。这些设备可以连接到网络并进行通信。UE可以包含多种功能,包括对话(语音…...

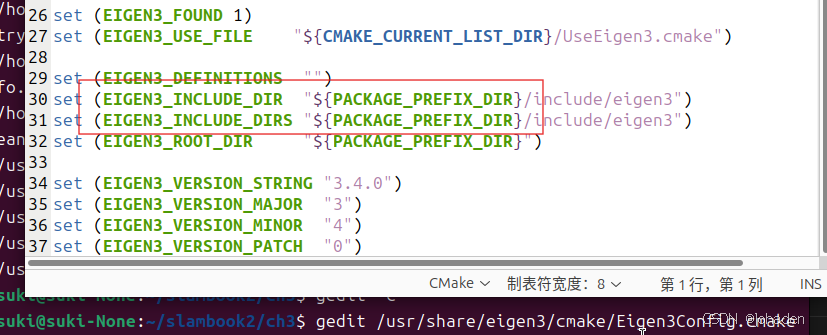

视觉SLAM ch3补充——在Linux中配置VScode以及CMakeLists如何添加Eigen库

ch3中的所有代码,除了在kdevelop中运行,还可以在VScode中运行。下面将简要演示配置过程,代码不再做解答,详细内容在下面的文章中。(这一节中的pangolin由于安装过程中会出现很多问题,且后续内容用不到该平台…...

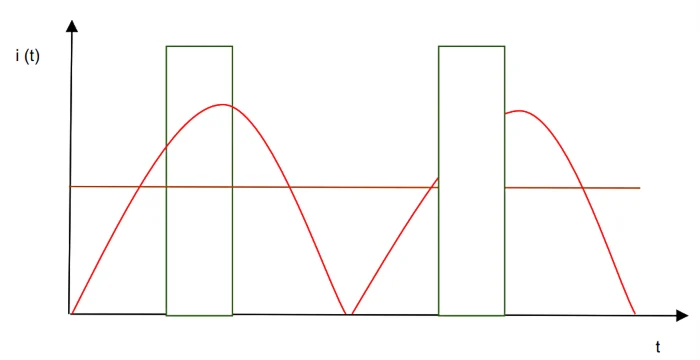

开关电源:优化电子产品中的能源使用

电压转换器是许多技术系统的支柱。根据应用的不同,所需的电源单元由变压器、整流器 AC/DC 转换器实现。当高性能开关电源尚未上市时,几乎只使用 50 Hz 变压器解决方案。 电源注意事项 电能几乎完全以三相电流的形式提供,系统电压为 10 ...3…...

Java语言程序设计——篇十三(2)

🌿🌿🌿跟随博主脚步,从这里开始→博主主页🌿🌿🌿 欢迎大家:这里是我的学习笔记、总结知识的地方,喜欢的话请三连,有问题可以私信🌳🌳&…...

企者不立,跨者不行,SAP UI5 开发里的克制、分寸与长久之道

老子这句话放到 SAP UI5 开发里看,并不是在劝开发者不进取,也不是叫我们少写功能、少做创新。它真正提醒的是,企业级前端开发最怕一种姿态,脚尖踮得很高,步子跨得很大,心里急着证明自己聪明,手上急着把每一个需求都做成个性化杰作。SAP UI5 最终运行在 SAP Fiori Launch…...

【数据结构】与排序算法鏖战5天,我终于搞懂了排序的思路和实现--排序算法大全的保姆级攻略

目录 一,排序的概念及分类 二,排序算法的实现 1,插入排序(intsert sort) _1,核心思路: _2,代码实现: _3,总结: 2,希尔排序(Shell sort) _…...

避开这些坑!用Verilog写2ASK/2FSK调制解调模块时的常见错误与调试技巧

避开这些坑!用Verilog写2ASK/2FSK调制解调模块时的常见错误与调试技巧 在数字通信系统的FPGA实现中,2ASK和2FSK作为基础调制方式常被用于教学和原型验证。但看似简单的调制解调模块,实际开发中却暗藏诸多"陷阱"。本文将从工程实践角…...

3步解锁电脑隐藏性能:UXTU硬件调优实战指南

3步解锁电脑隐藏性能:UXTU硬件调优实战指南 【免费下载链接】Universal-x86-Tuning-Utility Unlock the full potential of your Intel/AMD based device. 项目地址: https://gitcode.com/gh_mirrors/un/Universal-x86-Tuning-Utility 还在为游戏卡顿而烦恼吗…...

)

从零搭建AI-ready数据管道:2026奇点大会现场复刻的3小时极速部署流水线(含LLM元数据自动标注模块)

更多请点击: https://intelliparadigm.com 第一章:AI原生数据管道搭建:2026奇点智能技术大会数据工程实践 在2026奇点智能技术大会上,核心数据平台团队首次全栈落地了真正意义上的AI原生数据管道(AI-Native Data Pipe…...

Serverless函数优化:提升无服务器应用性能

Serverless函数优化:提升无服务器应用性能 一、Serverless函数优化概述 1.1 Serverless函数的定义 Serverless函数是一种事件驱动的计算服务,它允许开发者编写小块代码来响应事件,而无需管理服务器。Serverless函数优化是指通过各种技术手段提…...

云函数window hook分析

声明 本文章中所有内容仅供学习交流使用,不用于其他任何目的,抓包 内容、敏感网址、数据接口等均已做脱敏处理,严禁用于商业用途和非法用途,否则由此产生的一切后果均与作者无关!侵权通过头像私信或名字简介叫我删除博…...

BetterGI原神自动化助手:告别重复操作,解放双手的终极指南

BetterGI原神自动化助手:告别重复操作,解放双手的终极指南 【免费下载链接】better-genshin-impact 📦BetterGI 更好的原神 - 自动拾取 | 自动剧情 | 全自动钓鱼(AI) | 全自动七圣召唤 | 自动伐木 | 自动刷本 | 自动采集/挖矿/锄地 | 一条龙…...

LinkSwift:八大网盘直链解析与下载加速的现代解决方案

LinkSwift:八大网盘直链解析与下载加速的现代解决方案 【免费下载链接】Online-disk-direct-link-download-assistant 一个基于 JavaScript 的网盘文件下载地址获取工具。基于【网盘直链下载助手】修改 ,支持 百度网盘 / 阿里云盘 / 中国移动云盘 / 天翼…...

)

大厂CTO闭门分享实录(SITS 2026未发布AI工程化实践首次流出)

更多请点击: https://intelliparadigm.com 第一章:SITS 2026专题论坛揭秘:10核心议题覆盖AI全领域 SITS 2026(Smart Intelligence Technology Summit)专题论坛将于明年3月在上海张江科学会堂正式启幕,聚焦…...