【Verilog学习日常】—牛客网刷题—Verilog企业真题—VL69

脉冲同步器(快到慢)

描述

sig_a 是 clka(300M)时钟域的一个单时钟脉冲信号(高电平持续一个时钟clka周期),请设计脉冲同步电路,将sig_a信号同步到时钟域 clkb(100M)中,产生sig_b单时钟脉冲信号(高电平持续一个时钟clkb周期)输出。请用 Verilog 代码描述。

clka时钟域脉冲之间的间隔很大,无需考虑脉冲间隔太小的问题。

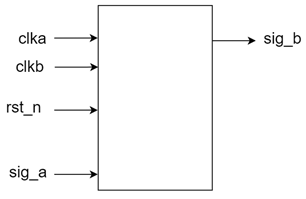

电路的接口如下图所示:

输入描述:

input clka ,

input clkb ,

input rst_n ,

input sig_a ,

输出描述:

output sig_b

解题思路

在了解脉冲同步器的工作原理之前,我们先来了解“单比特信号同步”的相关概念:

主要参考以下博文:

“单比特信号同步” 学习笔记

单比特信号同步

概述

- 信号同步的目的是防止新时钟域中第一级触发器的亚稳态信号对下一级逻辑造成影响。简单的同步器由两个触发器串联而成,中间没有其它组合电路。这种设计可以保证后面的触发器获得前一个触发器输出时,前一个触发器已退出了亚稳态,并且其输出已稳定。

信号同步的要求

- 为了使同步工作能正常进行,从某个时钟域传来的信号应先通过原时钟域上的一个触发器,然后不经过两个时钟域间的任何组合逻辑直接进入同步器的第一个触发器中。这一要求非常重要,因为同步器的第一级触发器对组合逻辑所产生的毛刺非常敏感。如果一个足够长的毛刺正好满足建立-保持时间的要求,则同步器的第一级触发器会将其放行,给新时钟域的后续逻辑送出一个虚假的信号。

同步造成的延时

- 一个经同步后的信号在两个时钟沿以后就成为新时钟域中的有效信号。信号的延迟是新时钟域的一到两个时钟周期。一种粗略的估算方法是同步器电路在新时钟域中造成两个时钟周期的延迟,设计者需要考虑同步延迟对跨时钟域的信号时序造成的影响。

三种常用的同步器(重点)

- 电平(level signal)同步器

在电平同步器中,跨时钟域的信号在新时钟域中要保持高电平或低电平两个时钟周期以上。同步之后的信号是电平的形式,而该电平所维持的时钟周期个数是其在跨时钟域期间被上升沿检测到的次数;

电平同步器设计电路如下:

- 边沿(edge detecting)检测同步器

边沿检测同步器在电平同步器的输出端增加了一个触发器。新增触发器的输出经反相后和电平同步器的输出进行与操作;

该电路会检测同步器输入的上升沿,产生一个与时钟周期等宽、高电平有效的脉冲。

如果将与门的两个输入端交换使用,就可以构成一个检测输入信号下降沿的同步器。

将与门改为非门可以构建一个产生低电平有效脉冲的电路。当一个脉冲进入更快的时钟域中时,边沿检测同步器可以工作的很好,该电路会产生一个脉冲,用来指示输入信号上升或下降沿。

该电路有一个限制,即输入脉冲的宽度必须大于同步时钟周期与第一个同步触发器所需保持时间之和。最保险的脉冲宽度是同步器时钟周期的两倍。如果输入是一个单时钟宽度脉冲进入一个较慢的时钟域,则这种同步器没有作用,在这种情况下就要采用脉冲同步器。

- 脉冲(Pulse)同步器

脉冲同步器工作原理

主要参考以下博文:

CDC(二) 单bit 脉冲跨时钟域处理

verilog设计-CDC:单bit脉冲快时钟域到慢时钟域

脉冲同步器就是带边沿检测的单bit同步器,基本原理就是把脉冲信号进行展宽。

脉冲同步器应用场景

- 适用于单bit脉冲信号跨时钟域。慢到快,快到慢均可,源脉冲间隔至少要为2个目的时钟周期,否则会被漏采。当然,在慢到快时钟比率大于2倍以上时也是可以实时采样的。

脉冲同步器原理

- 脉冲同步器的原理为将快时钟域的脉冲拓展为电平信号,使得该电平的宽度大于慢时钟域的时钟周期,从而可以使用两级同步器进行同步,然后在同步后的时钟域进行脉冲恢复,从而完成将信号(尤其是脉冲信号)从快时钟域传递到慢时钟域。

- 其电路设计图如下所示:

脉冲同步器电路特点

- 该电路只能传递脉冲信号(也还能传递一直是0的信号,只不过工程意义不大)。对于输入信号一直是1,或是只有0到1的阶跃信号,只有1到0的信号均无法正确传输;

- 该电路将输入端的脉冲传输给慢时钟域,无论输入端的脉冲有多宽,都只能在慢时钟域恢复成一个时钟周期宽度的脉冲;

- 输入信号的脉冲之间间隔要大于1倍的慢时钟周期,否则连着的两个脉冲问题会在慢时钟域合并成一个脉宽为2个满时钟周期的脉冲,导致丢失一个脉冲。

完整代码如下

`timescale 100ps/100psmodule pulse_detect(input clka , input clkb , input rst_n ,input sig_a ,output sig_b

);reg sig_a_r;reg q_buff0, q_buff1;//1.翻转电路部分(快时钟域)always @(posedge clka or negedge rst_n) beginif (!rst_n) sig_a_r = 1'b0;else beginif (sig_a) sig_a_r = ~sig_a_r;else sig_a_r = sig_a_r;endend//2.电平同步器部分always @(posedge clkb or negedge rst_n) beginif (!rst_n) begin q_buff0 <= 1'b0; q_buff1 <= 1'b0; endelse begin q_buff0 <= sig_a_r; q_buff1 <= q_buff0; endendreg q_slow;always @(posedge clkb or negedge rst_n) beginif (!rst_n) begin q_slow <= 1'b0; endelse begin q_slow <= q_buff1; endendassign sig_b = q_buff1 ^ q_slow;

endmodule

另一种写法:单独例化D触发器;

`timescale 100ps/100psmodule pulse_detect(input clka , input clkb , input rst_n ,input sig_a ,output sig_b

);reg sig_a_r;wire q_buff0, q_buff1, q_slow;always @(posedge clka or negedge rst_n) beginif (!rst_n) sig_a_r = 1'b0;else beginif (sig_a) sig_a_r = ~sig_a_r;else sig_a_r = sig_a_r;endendDFF_R D0 (.D(sig_a_r), .clk(clkb), .rst_n(rst_n), .Q(q_buff0));DFF_R D1 (.D(q_buff0), .clk(clkb), .rst_n(rst_n), .Q(q_buff1));DFF_R D2 (.D(q_buff1), .clk(clkb), .rst_n(rst_n), .Q(q_slow));assign sig_b = q_buff1 ^ q_slow;endmodule//带异步复位端的D触发器

module DFF_R(input D,input clk,input rst_n,output reg Q

);always @(posedge clk or negedge rst_n) beginif (!rst_n) Q <= 1'b0;else Q <= D;end

endmodule相关文章:

【Verilog学习日常】—牛客网刷题—Verilog企业真题—VL69

脉冲同步器(快到慢) 描述 sig_a 是 clka(300M)时钟域的一个单时钟脉冲信号(高电平持续一个时钟clka周期),请设计脉冲同步电路,将sig_a信号同步到时钟域 clkb(100M&…...

电商商品数据采集||高并发||多语言请求实例演示|京东|淘宝商品详情数据SKU价格

以京东商品数据采集为例 京东商品详情接口数据采集是指通过调用京东提供的商品详情API接口,获取商品的详细信息。以下是一个简单的步骤来实现这个功能: 1. 注册京东开发者账号 首先,你需要注册一个京东开发者账号,并创建一个应…...

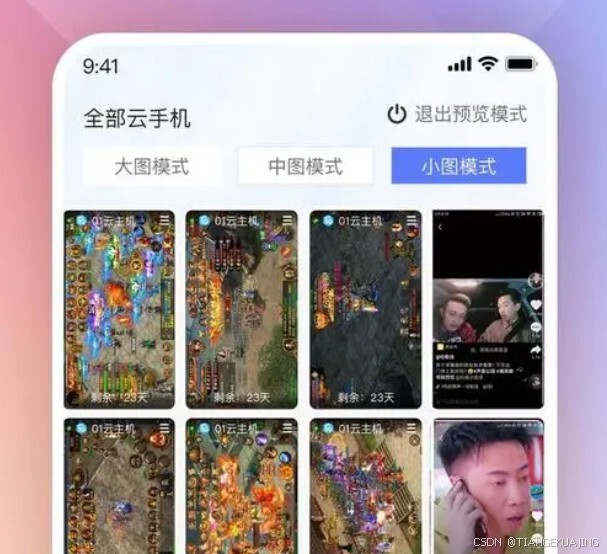

云手机哪款好用?2024年云手机推荐对比指南

随着云手机市场的快速扩展,消费者在选择云手机时面临着众多选择。为了帮助大家找到最适合自己的云手机,小编特意整理了一份当前市场上几款备受关注的云手机品牌对比,大家一起往下看吧。 1. Ogphone云手机 Ogphone云手机是近年来海外业务版块迅…...

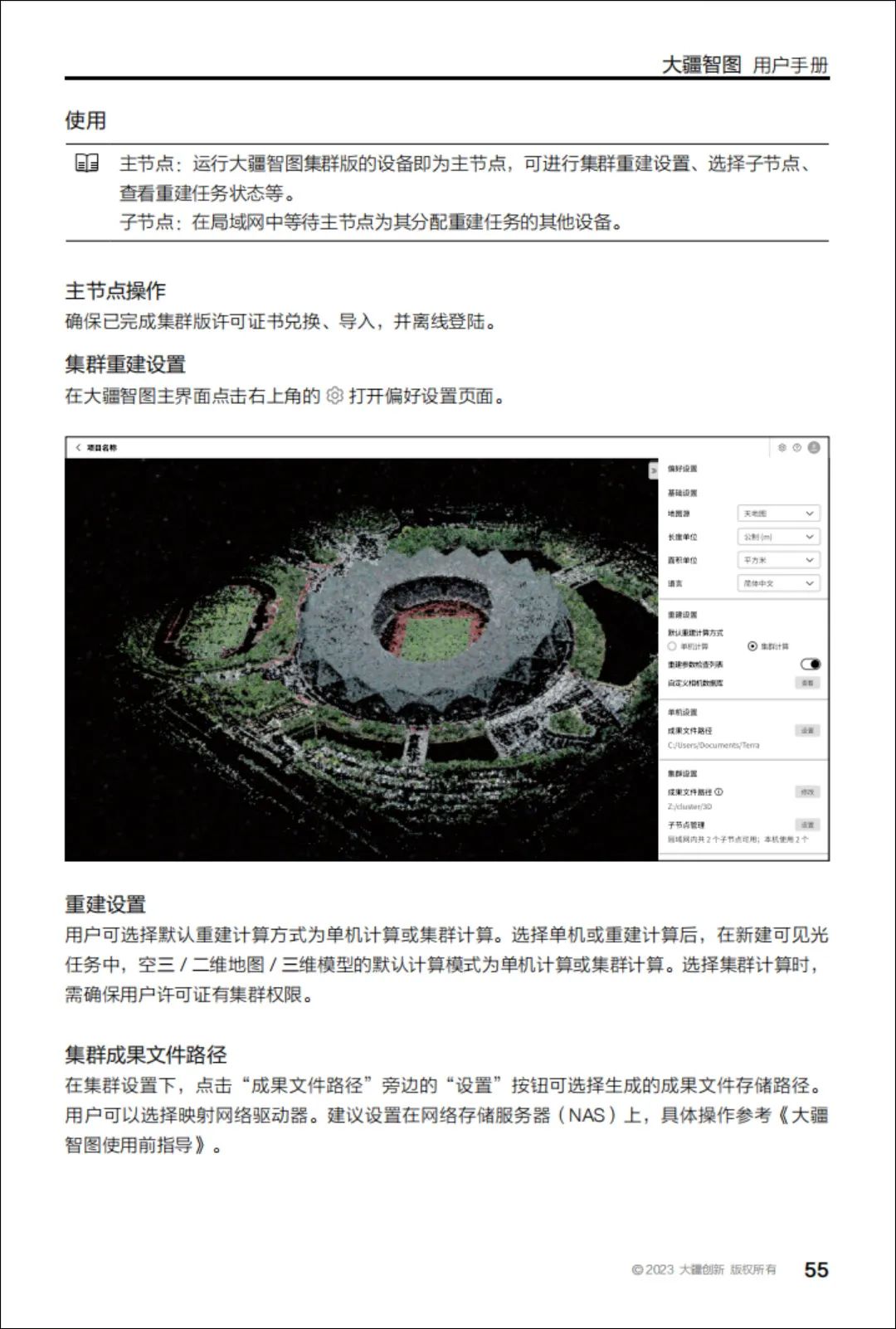

无人机航测内业常用建模软件手册下载(上)

航测项目外业离不开无人机,内业离不开制图软件。 无人机航测外业作业包括控点布设、航线规划、仿地飞行、航拍等流程,而内业数据处理则常涉及到CC、Pix4D、PhotoScan、大疆智图、重建大师、M3D、瞰景Smart3D、天工等软件。 我们整理了这些常用建模软件…...

Python Django ORM 的工作原理

在 Web 开发中,处理数据库是非常常见的需求,尤其是在构建动态应用程序时。Django 作为一个流行的 Python Web 框架,提供了一套强大的工具帮助开发者轻松管理数据库。Django 的 ORM(对象关系映射,Object-Relational Map…...

GoLang编程常用规范/工具

代码格式化工具 代码风格: go install github.com/fsgo/go_fmt/cmd/gorgeouslatest gorgeous # 仅格式化git有改动的文件。如需格式化所有文件,可以执行 gorgeous ./...标签格式:https://github.com/4meepo/tagalign go install github.c…...

数字王国里的虚拟人――技术、商业与法律解读

💂 个人网站:【 摸鱼游戏】【神级代码资源网站】【海拥导航】🤟 找工作,来万码优才:👉 #小程序://万码优才/HDQZJEQiCJb9cFi💅 想寻找共同学习交流,摸鱼划水的小伙伴,请点击【全栈技…...

Java后端基础练习|请求参数

请求参数,可以通过四种方式传递到后端 请求路径查询参数请求体请求头 controller代码 package com.urfread.breaknews.core.controller;import com.urfread.breaknews.core.common.model.ResultData; import lombok.Data; import org.springframework.web.bind.a…...

C# + SQLiteExpert 进行(cipher)加密数据库开发+Costura.Fody 清爽发布

一:让 SQLiteExpert 支持(cipher)加密数据库 SQLiteExpert 作为SQlite 的管理工具,默认不支持加密数据库的,使其成为支持(cipher)加密数据库的管理工具,需要添加e_sqlcipher.dll &…...

MySQL 8.0 新特性之自增变量持久化

MySQL 8.0 新特性之自增变量持久化 文章目录 MySQL 8.0 新特性之自增变量持久化MySQL 5.7 vs 8.0 测试对比MySQL 5.7MySQL 8.0 参考资料 MySQL 8.0 中支持自增变量持久化,实际也是解决之前版本中存在的自增主键重启重置的 BUG 问题( BUG #199࿱…...

网站建设公司哪家好?好的网站建设公司应该有哪些特别之处?

面对众多的网站建设公司,企业该如何选择呢?如何才能避坑呢?本文将探讨好的网站建设公司应该具备的特别之处 案例,这是最直观的表现,一个好的网站建设公司必然拥有为数众多的的案例展示,且这些案例质量高&a…...

香山南湖架构分析--FE

总体架构 分支预测和指令缓存,通过FTQ达到解耦的目的;FTQ将请求送给ICache,进行取指;取出的指令码通过预译码初步检查分支预测的错误并及时冲刷预测流水线;检查后的指令送入指令缓冲并传给译码模块,最终形成后端的指令…...

【Linux的那些事】shell命名及Linux权限的理解

目录 一、shell命令以及运行原理 二、Linux权限的概念 三、Linux权限管理 3.1.文件访问者的分类(人) 3.2.文件类型和访问权限(事物属性) 3.3.文件权限值的表示方法 3.4.文件访问权限的相关设置方法 a)chmod b)chown c)…...

Visual Studio 2022 配置 Boost 库

一、使用预编译版本 尽量不要使用预编译版本,因为可能构建的不完全,还得重新构建,不如一步到位 1. 下载预编译的 Boost 库 下载:Boost C Libraries - Browse /boost-binaries at SourceForge.net 2. 选择 msvc 版本࿰…...

逻辑回归(下): Sigmoid 函数的发展历史

背景 闲来无事翻了一下之前买的一个机器学习课程及之前记录的网络笔记,发现遇到公式都是截图,甚至是在纸上用笔推导的。重新整理一遍之前逻辑回归函数的学习笔记,主要是为了玩一下 LaTex 语法,写公式挺有意思的。 整理之前三篇笔…...

——RabbitMQ 各种交换机的区别与应用)

快速理解mQ(三)——RabbitMQ 各种交换机的区别与应用

RabbitMQ是一个开源的消息代理软件,它实现了高级消息队列协议(AMQP),允许应用程序或系统以异步的方式交换数据。RabbitMQ中的交换机(Exchange)是消息的分发中心,它接收来自生产者的消息…...

【五分钟学会】YOLO11 自定义数据集从训练到部署

数据集地址 数据集包含 360 张红血细胞图像及其注释文件,分为训练集与验证集。训练文件夹包含 300 张带有注释的图像。测试和验证文件夹都包含 60 张带有注释的图像。我们对原始数据集进行了一些修改以准备此 CBC 数据集,并将数据集分成三部分。在360张…...

Redis学习(十二)连接数不足报错及分析修复:ERR max number of clients reached.

目录 一、问题介绍二、问题分析2.1 redis-cli 登录2.2 info clients 查看连接数情况2.3 client list 查看具体连接情况2.4 分析连接空闲时长2.5 client list 根据客户端IP统计连接数 三、问题结论和解决3.1 问题结论:3.2 解决方案①:优化程序3.3 解决方案…...

)

八股文面试题总结(包含主流的面试经典题)

Java基础 1、JDK和JRE的区别是什么** JDK是Java开发工具包,JRE是Java运行时环境,二者的区别在于 JRE是Java程序运行所必须的,它包含jvm和一些Java的基础类库 JDK是Java程序开发所必须的,它包含JRE和一些开发工具 总结一下就是…...

一分钟掌握 Java22 新特性

1. 增强的模式匹配(Pattern Matching for Switch) Java 22 扩展了模式匹配的功能,允许在 switch 语句中使用模式匹配,从而使代码更加简洁和易读。 示例代码: public class PatternMatchingSwitchDemo {public stati…...

openLCA 2.6.2 完整安装与使用指南:免费开源的生命周期评估解决方案

openLCA 2.6.2 完整安装与使用指南:免费开源的生命周期评估解决方案 【免费下载链接】olca-app Source code of openLCA 项目地址: https://gitcode.com/gh_mirrors/ol/olca-app openLCA 是一款功能强大的开源生命周期评估软件,专门用于产品从原材…...

TrollInstallerX完整教程:3分钟搞定iOS越狱神器TrollStore一键安装

TrollInstallerX完整教程:3分钟搞定iOS越狱神器TrollStore一键安装 【免费下载链接】TrollInstallerX A TrollStore installer for iOS 14.0 - 16.6.1 项目地址: https://gitcode.com/gh_mirrors/tr/TrollInstallerX 还在为iOS设备上安装TrollStore而烦恼吗&…...

RISC-V开发板测评实战:从申请到深度评测的完整指南

1. 项目概述:一次深度参与RISC-V生态的绝佳机会最近在电子发烧友论坛上看到了一个挺有意思的活动——“第二届RISC-V开发板测评大赛”,主办方是昊芯。对于咱们这些搞嵌入式、玩单片机、或者对开源硬件和RISC-V架构感兴趣的朋友来说,这绝对是一…...

双足机器人EDF推进系统与高精度扭矩控制技术

1. 双足机器人EDF推进系统深度解析在双足机器人研发领域,姿态控制一直是核心挑战。传统方案依赖腿部关节的精细调节,但在高速运动或突发扰动情况下往往响应不足。我们团队创新性地引入了EDF(电动涵道风扇)推进系统,通过…...

新手避坑指南:你的FPGA按键消抖仿真为什么和板子对不上?

FPGA按键消抖实战:从仿真完美到真实失效的深度排查手册 刚接触FPGA开发的工程师常会遇到一个诡异现象:按键消抖模块在ModelSim里跑得风生水起,波形干净漂亮,可一旦下载到开发板就各种失灵——要么按键没反应,要么按一次…...

告别‘Requirement already satisfied’:精准定位Python环境,让pip install不再迷茫

1. 为什么pip总是说"已经安装好了"? 每次看到"Requirement already satisfied"这个提示,我都想对着屏幕大喊:"不!它根本没装在我想要的地方!"这种抓狂的感觉,相信很多Python…...

C166编译器内联展开机制与嵌入式性能优化

1. C166编译器运行时库函数的内联展开机制解析在嵌入式开发领域,C166架构因其高效的实时性能被广泛应用于工业控制领域。作为长期使用Keil C166工具链的开发者,我发现编译器对标准库函数的内联优化处理直接影响着代码的执行效率和内存占用。本文将深入剖…...

从STM32F103到GD32F303:如何用CubeMX和Keil5低成本‘平替’升级你的项目?

从STM32F103到GD32F303:低成本高性能迁移实战指南 在嵌入式开发领域,芯片选型往往需要在性能与成本之间寻找平衡点。对于已经熟悉STM32F103系列开发但面临成本压力或性能瓶颈的工程师来说,GD32F303系列提供了一个极具吸引力的替代方案。这款国…...

:解锁摄像头与雷达融合的3D感知新范式)

跨域空间匹配(CDSM):解锁摄像头与雷达融合的3D感知新范式

1. 为什么自动驾驶需要跨域空间匹配技术 当你坐在一辆自动驾驶汽车里,最不希望看到的就是系统把前方停着的卡车误判成广告牌。这种错误在单一传感器系统中其实很常见——摄像头可能因为逆光看不清物体轮廓,雷达又难以识别物体的具体形状。这就是为什么我…...

tensorrt_demos性能对比分析:FP16 vs INT8 vs DLA核心的优劣对比

tensorrt_demos性能对比分析:FP16 vs INT8 vs DLA核心的优劣对比 【免费下载链接】tensorrt_demos TensorRT MODNet, YOLOv4, YOLOv3, SSD, MTCNN, and GoogLeNet 项目地址: https://gitcode.com/gh_mirrors/te/tensorrt_demos tensorrt_demos是一个支持MODN…...