IC开发——数字电路设计简介

1. 前言

我们说的数字电路,一般是指逻辑数字电路,即通过逻辑门组合成的电路,也即我们常说的逻辑IC。IC除了逻辑IC之外,还有模拟IC,存储IC等。

IC设计,需要学习数字电路,需要学习Verilog/VHDL等设计语言,需要学习使用相关EDA,看起来非常难。IC设计是很难,但是简单的入门并没有那么难。

2. 数字电路

2.1. 基础

- 数字电路(Digital Circuit)

- 用数字信号完成对数字量进行算术运算和逻辑运算的电路称为数字电路。数字逻辑集成电路(IC)是数字电路在半导体晶圆上的物理实现。

- 模拟电路和数字电路

- 模拟电路信号更接近真实世界信号,但是抗干扰差。

- 数字电路信号一般使用2进制(0和1)编码,抗干扰佳,传输速度快。

- PAM4编码

数字信号一般使用2进制编码(NRZ编码),但是也可以使用其他编码方式,如PAM4编码, 可以传输更多的信号,如PCIe6即支持PAM4编码。

2.2. 门

- 数字电路构成

- 逻辑门是数字电路的基本构成,逻辑门主要用来执行布尔逻辑运算。

- 数字电路工艺

- TTL门

- 由电阻和三极管构成。

- 响应速度快。

- 三极管在导通时,基极需要保持一定的偏置电流,导致TTL工艺IC静态功耗高,难以大规模集成。

- CMOS门

- 由电阻和MOS管构成。

- MOS状态不变时(无论是导通或截止),其栅极没有电流,CMOS工艺的IC静态功耗低。(MOS管只在状态改变时产生电流)

- 当前逻辑IC的主流工艺是CMOS门工艺。

- TTL门

- 基本门

- 与门、或门、非门、同门

- 与门、或门、非门、同门

- 复合门

- 与非门、或非门、异或门、同或门

- 与非门、或非门、异或门、同或门

2.3. 组合逻辑电路

2.3.1. 加法器

- Full Adder(全加法器,带进位的加法器)

加法器,可以用与门、或门、异或门实现,也可以用或非门实现,还可以用其他门组合实现。

优先选择与门、或门、异或门的实现方式,这种方式消耗的门数最少,降低IC的功耗和面积。

2.3.2. 比较器

- 1-Bit Digital Comparator (1Bit比较器)

1Bit比较器是最简单的比较器。

以此为基础可以扩展为多Bit比较器。

2.3.3. ALU

-

算术逻辑单元(Arithmetic Logic Unit)。

-

CPU的每个核心至少有一个ALU。

-

负责算术运算、逻辑运算、位运算和比较运算等。

2.3.4. Mux

- 2×1 Multiplexer

多路选择器,根据输入选择输出。多路选择器可以扩展为支持更多输入控制。

2.3.5. 组合逻辑

- 组合逻辑电路:

- 由逻辑门构成。

- 电路通电时,电路立即执行完成,输出结果,可以认为是即时响应。

- Mux、Decoder、 Comparator等ALU单元都是组合逻辑电路。

- 组合逻辑电路时延

电信号的速度为30万公里/秒,在导线中的速度大概20万公里/秒。

1GHz的时钟的IC,其时钟周期为1ns,电运行距离20cm。

一个组合逻辑电路在IC中的总长度为10cm,电执行完的时间0.5ns,在1个周期内。

一个复杂的组合逻辑电路如果总长度为30cm,电执行完的时钟1.5ns,超过1个周期。

IC的执行以时钟周期为单位,在1个周期内,即可以认为立即执行完成。

IC的执行时间超过1个周期,即认为组合逻辑没有即时执行。

组合逻辑电路不要太过复杂,总执行时钟不能超过1个时钟周期。

(以上计算只是估算,实际组合电路中不同门、不同线宽等都影响电的实际速度)

2.4. 时序逻辑电路

2.4.1. 锁存器

- SR-Latch(SR锁存器)

- SR锁存器,能够锁存之前的状态。

- SR锁存器,有多种实现方式,下面以与非门来介绍。

- 当输入为1时,输出均为之前的状态。

- SR锁存器,能够保持之前的状态,有记忆功能。

2.4.2. D触发器

- D Flip Flop(D触发器)

- 基于SR锁存器,将R改为Clk时钟。

- 当Clk为0变到1时,查看SR锁存器真值表,输出锁存。

- 第1次采样Data电平1,Q输出1,并保持到下个上升沿。

- D触发器可以记忆输入信号的上个时钟采样的数据。

- 1个或多个D触发器组成寄存器,保存多位状态。

2.4.3. 分频电路

- 2分频电路

通过寄存器保持上一次状态来让实现2分频输出。

此电路可扩展为多分频输出。

2.4.4. 计数器

- 2Bit Up Counter

通过寄存器保存上个时钟的状态,达到更新状态。

2Bit 最多计数4种状态。

可扩展到多Bit计数器,计数更多状态。

2.4.5. 时序逻辑电路

- 时序逻辑电路(Sequential Logic Circuit)

- 时序逻辑电路与时钟序列有关的逻辑电路。

- 通过寄存器保存上个时钟周期的状态。

- 数据在时钟边沿(上升沿或下降沿)触发时更新。

- 大型计算,如果可以拆分为多个并行计算,那么可以使用组合电路在一个时钟周期内完成计算。

大型计算,如果不能在一个时钟内完成计算,则需要将计算分拆为多Step,每Step通过组合电路在一个时钟周期内完成计算,然后通过寄存器将结果传入下个时钟周期继续计算,完成所有Step之后,输出最终结果。

2.5. 状态机

State Machine(状态机),清晰的输入输出,更可靠的时序电路,可以实现更复杂的逻辑。

3. 数字电路硬件

3.1. ASIC

ASIC(特定应用集成电路)

- ASIC 是为特定应用或功能而专门设计的集成电路,可以高度优化以满足特定性能、功耗和面积要求。

- ASIC一般不集成CPU,不可编程。

- 常应用于放大器、滤波器、调制解调器、音频解码器、视频解码器等。 在IC发展早期,类型主要为ASIC。 实现相对简单。

- 灵活性不够,只能通过外部引脚完成一些简单的功能配置。

3.2. CPU

- 指令集发展

- 早期的IC都是特定应用的集成电路(ASIC),灵活性不够。

- 为了提升IC的灵活性,早期引入了助记符指令,IC可以执行自定义的助记符指令实现复杂逻辑操作。

- 随着IC逻辑进一步复杂,助记符指令也进一步发展变得复杂。

- 1970s,Intel推出微处理器,并在助记符指令的基础上专门的8080指令集,后来逐步发展为x86-64指令集。

- 1980s,RISC(精简指令集计算机)架构推出,相应衍生出MIPS、SPARC和ARM等架构和配套指令集。

- 2010年,RISC-V(Reduced Instruction Set Computer V)作为一种开放的指令集架构(ISA),由UC Berkeley提出。

- CPU发展

- CPU和ISA是同步发展的。

- ASIC引入控制单元模块来支持指令集,此时ASIC即变成了CPU。

- CPU控制单元负责读取指令集代码,解析执行相应的操作,并完成调用ALU,I/O输出等。

3.3. SoC

系统芯片,也称片上系统(SoC,System on Chip)是一种集成电路设计,它将计算机系统的许多组件集成到单一的芯片上。SoC 通常包括 CPU、总线(Bus)、其他Master模块(如Security Subsystem等)、DMA等其他Slave模块(如UART、IIC等) ,以提供完整的计算解决方案,降低用读电路开发难度。MCU可以认为是一种应用于嵌入式上的低功耗SoC。

IP(Intellectual Property,知识产权),类似软件开发中的库。IP的表现形式:

- 软IP,RTL代码(Verilog/VHDL),使用灵活,可扩展性强。

- 硬IP,完成物理布线的物理版图,使用简单,但可扩展性差。

3.4. FPGA

- FPGA(Field-Programmable Gate Array,现场可编程门阵列)是一种集成电路,它的最大特点是可以通过编程来配置其硬件逻辑。

- CPU可以通过编程增加灵活性,但是如果CPU对应的数字电路出现Bug,也是无法修改的。数字电路部署到- FPGA上,如果出现Bug,可以很方便地替换为新数字电路设计。

- 数字电路设计到IC生产,这一整个过程很长,也可以使用FPGA加速数字电路到生产部署。FPGA用于验证数字电路,提升数字电路设计的可靠性。

- FPGA适合需要灵活性和快速变化的应用场景。

4. 数字电路设计

4.1. 数字电路图

- Digital Circuit Diagram

- 早期的数字电路设计是直接手动绘制电路图,然后将晶体管和其他电子元件按照电路图附加在半导体材料上。

- 随着IC的技术发展,电路图可以使用基本模块,如加法器、D触发器、Mux等,可以提升手动绘制电路图的效率。

- 随着IC复杂度的进一步增加,手动绘制数字电路图的难度越来越大,急需要一种更便捷的方法。

- Advantage

简单,直观,可以快速设计小的数字电路。 - Disadvantage

针对大型/超大型数字电路,设计难度大,设计效率低。

4.2. 数字电路描述语言

4.2.1. 概念

- HDL

- 硬件描述语言(HDL)是一种专门用于描述数字电路的编程语言。

- 随着数字电路规模增加,手动绘制数字越来越难,效率越来越低。

- 使用一种编程语言来描述数字电路,然后用工具将编程代码综合成数字电路图。

- Traditional HDL

VHDL、Verilog/SystemVerilog。 - New HDL

- SystemC,基于C++的 的硬件描述和建模语言,主要用于IC开发前期的系统建模。

- Chisel,基于Scala的RTL级HDL,可以生成Verilog/SystemVerilog。

- SpinalHDL,基于Scala的RTL级HDL,可以生成Verilog,更好的可读性可维护性。

- MyHDL,基于Python的RTL级HDL,可以生成Verilog、VHDL。

- Synthesis Tools

- 商业综合工具,Synopsys Design Compiler, Cadence Genus等。

- 开源综合工具,Yosys, iverilog等。

4.2.2. 抽象层级

-

Level of Abstraction

- System Level:抽象高,关注功能,用于建模仿真,不关注时序细节,推荐SystemC。

- Algorithm Level:关注算法的实现,推荐语言C/C++,MATLAB。

- RTL Level:关注寄存器级传输行为,可以综合为实际数字电路,推荐语言VHDL,Verilog,Chisel。

- Gate Level:逻辑门级别,可以综合成实际数字电路,推荐语言VHDL,Verilog。

- Switch Level:基于三极管开关的实现,用于分析电路电气特性,推荐SPICE, Verilog-A。

-

Digital Circuit Design

- 系统级的HDL,虽然有一些高级综合技术可以综合为实际数字电路,但是实际使用较少。

- 门级HDL,抽象层级低,描述硬件效率低,一般不单独使用。

- RTL级抽象层中等,描述硬件效率高,并且可以综合成实际的数字电路,所以数字电路设计多用RTL级语言描述。

4.2.3. RTL

- RTL(Register Transfer Level)是一种用于描述数字电路设计的抽象级别,着重于在寄存器之间的数据传输和处理方式。

- RTL可以通过工具综合成实际数字电路。

- 实际数字电路设计多用RTL表示,因此一般用RTL来代指数字电路设计。

- RTL语言:Verilog/SystemVerilog、VHDL、Chisel等。

相关文章:

IC开发——数字电路设计简介

1. 前言 我们说的数字电路,一般是指逻辑数字电路,即通过逻辑门组合成的电路,也即我们常说的逻辑IC。IC除了逻辑IC之外,还有模拟IC,存储IC等。 IC设计,需要学习数字电路,需要学习Verilog/VHDL等…...

openmmlab实现图像超分辨率重构

文章目录 前言一、图像超分辨率重构简介二、mmmagic实现图像超分 前言 超分辨率重构技术,作为计算机视觉领域的一项重要研究课题,近年来受到了广泛关注。随着科技的飞速发展,人们对图像质量的要求越来越高,尤其是在智能手机、监控…...

四、远程登录到Linux服务器

说明 linux 服务器是开发小组共享,正式上线的项目是运行在公网,因此需要远程登录到 Linux 进行项目管理或者开发 Xshell 1、特点 Xshell 是目前最好的远程登录到 Linux 操作的软件,流畅的速度并且完美解决了中文乱码的问题, 是目…...

Qt开发全指南:从基础到高级

1. Qt快速入门 • 什么是Qt框架? • 如何安装和配置Qt? • 使用Qt Creator:快速上手 • 项目结构与构建系统:qmake 和 CMake 2. 核心模块解析 • 信号与槽机制详解 • QtCore、QtGui 和 QtWidgets 模块介绍 • 并行编程&a…...

【算法】——双指针算法合集(力扣)

阿华代码,不是逆风,就是我疯 你们的点赞收藏是我前进最大的动力!! 希望本文内容能够帮助到你!! 目录 第一题:移动零 第二题:复写零 第三题:快乐数 第四题:…...

小猿口算自动PK脚本

大家好,我是小黄。 近期,众多大学生炸鱼小猿口算APP,把一众小学生都快虐哭了,小黄听闻后,也跃跃欲试。对此小黄也参考网上的资料写了一个自动Pk的脚步。 首先大家需要安装一个pytorch环境过程中,如果小伙伴对此不熟悉的…...

)

蓝桥杯备赛(c/c++)

排序 9. 实现选择排序 10. 实现插入排序 11. 实现快速排序 12. 实现归并排序 13. 实现基数排序 14. 合并排序数组...

LLM大模型预测耗时的粗略估计以及sft和continue pre-train的区别

目录 预训练(Pretraining)与微调(SFT, Supervised Fine-Tuning)的区别 训练方式 数据组成 特殊标记(Special Tokens) Prompt处理 Session数据处理 训练目的 小结 LLM大模型预测耗时的粗略估计 1. …...

go和python打包项目对比

go源码 package mainimport ("fmt" )func main() {fmt.Println(" _____ _____ _____ _____")fmt.Println(" |2 ||2 ||2 ||2 |")fmt.Println(" | ^ || & || v || o |")fmt.Println(" | …...

EmEditor传奇脚本编辑器

主程序:EmEditor.exe 目前已有功能 可以自己指定一个快捷键 实现以下功能(默认快捷键为:F1) 以下全功能 都是鼠标所在行 按快捷键 (默认快捷键:F1) 1.在Merchant.txt中 一键打开NPC 没有…...

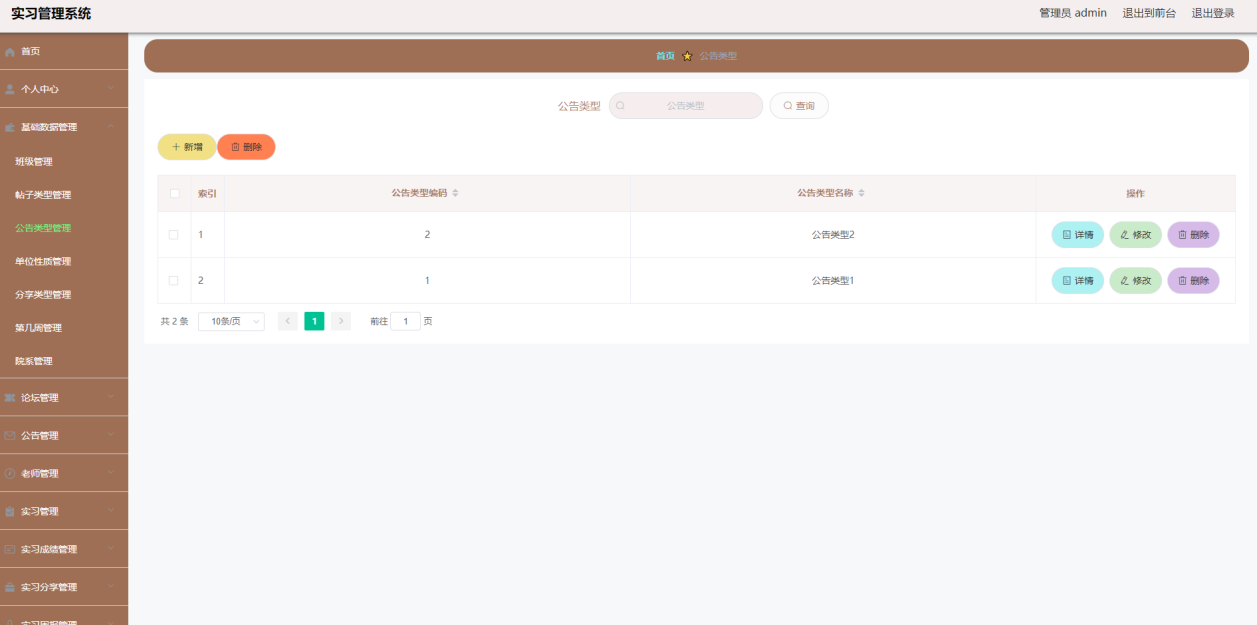

基于JAVA+SpringBoot+Vue的实习管理系统

基于JAVASpringBootVue的实习管理系统 前言 ✌全网粉丝20W,csdn特邀作者、博客专家、CSDN[新星计划]导师、java领域优质创作者,博客之星、掘金/华为云/阿里云/InfoQ等平台优质作者、专注于Java技术领域和毕业项目实战✌ 🍅文末附源码下载链接🍅 哈喽兄…...

Python自定义异常类:实际应用示例之最佳实践

Python自定义异常类:实际应用示例之最佳实践 前言 在软件开发中,合理处理异常是保证程序稳定性的重要环节。虽然 Python 内置了丰富的异常类型,但在处理复杂业务逻辑时,自定义异常类能够使代码更加清晰且具备可扩展性。 本文将…...

创新设计大师项骅:用卓越才华打造医疗科技新未来

项骅,这位在设计界声名鹊起的才俊,正准备在其璀璨的职业生涯中开启一个激动人心的新篇章。近日,他宣布即将进军医疗科技领域,这一决定在设计圈和医疗界引起了广泛关注。项骅计划以UX设计师的身份,致力于改善医疗服务的用户体验。谈到这个新挑战,他显得兴致勃勃:"我期待将我…...

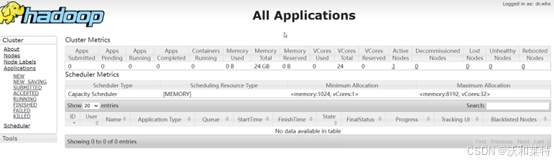

云计算第四阶段 CLOUD2周目 01-03

国庆假期前,给小伙伴们更行完了云计算CLOUD第一周目的内容,现在为大家更行云计算CLOUD二周目内容,内容涉及K8S组件的添加与使用,K8S集群的搭建。最重要的主体还是资源文件的编写。 (*^▽^*) 环境准备: 主机清单 主机…...

Linux搭建Hadoop集群(详细步骤)

前言 Hadoop是一个由Apache基金会所开发的分布式系统基础架构。用户可以在不了解分布式底层细节的情况下,开发分布式程序。充分利用集群的威力进行高速运算和存储。 说白了就是实现一个任务可以在多个电脑上计算的过程。 一:准备工具 1.1 VMware 1.2L…...

MongoDB中如何实现相似度查询

在 MongoDB 中,进行相似度查询通常涉及文本搜索或基于特定字段的相似度计算。以下是几种常见的方法: 1. 使用文本索引和文本搜索 MongoDB 提供了文本索引功能,可以对字符串字段进行全文搜索。你可以使用 $text 操作符来执行文本搜索查询。 …...

F开头的词根词缀:ful

60.-ful (1)表形容词,“有…的” grateful a 感激的(grate感激) rueful a 后悔的(rue悔恨) willful a 任性的(will意志…任意办事) tactful a 圆滑的(tact手腕…...

【python开发笔记】-- python装饰器

装饰器: 不修改被装饰对象的源代码,也不修改调用方式的前提下,给被装饰对象添加新的功能 原则:开放封闭原则 开放:对扩展功能(增加功能开放),扩展功能的意思是在源代码不做任何改变…...

WEB攻防-python考点CTF与CMS-SSTI模板注入PYC反编译

知识点: 1、PYC(python编译后的文件)文件反编译; 2、Python-Web-SSTI; 3、SSTI模板注入利用分析; (Server-Side Template Injection) SSTI 就是服务器端模板注入 当前使用的一…...

Open3D实现点云数据的序列化与网络传输

转载自个人博客:Open3D实现点云数据的序列化与网络传输 在处理点云数据的时候,有时候需要实现点云数据的远程传输。当然可以利用传输文件的方法直接把点云数据序列化成数据流进行传输,但Open3D源码在实现RPC功能时就提供了一套序列化及传输的…...

3大策略掌握Avidemux视频编辑:从源码编译到专业级处理

3大策略掌握Avidemux视频编辑:从源码编译到专业级处理 【免费下载链接】avidemux2 Avidemux2, simple video editor 项目地址: https://gitcode.com/gh_mirrors/avi/avidemux2 Avidemux是一款开源跨平台视频编辑工具,专注于快速剪辑、编码转换和批…...

开发智能客服系统时利用 Taotoken 实现模型降级与容灾路由的策略

🚀 告别海外账号与网络限制!稳定直连全球优质大模型,限时半价接入中。 👉 点击领取海量免费额度 开发智能客服系统时利用 Taotoken 实现模型降级与容灾路由的策略 在构建面向真实用户的智能客服系统时,服务的连续性与…...

Midjourney年度订阅避坑手册:92%用户不知的3大失效风险——自动续费陷阱、区域定价欺诈、账户绑定漏洞

更多请点击: https://intelliparadigm.com 第一章:Midjourney年度订阅优惠全景透视 Midjourney 作为当前主流的 AI 图像生成服务,其年度订阅计划长期受到创作者与团队用户的高度关注。相比月度订阅,年度方案不仅显著降低单月成本…...

Prettier配置踩坑实录:我的‘singleQuote: true’为什么不生效?深度解析VSCode格式化优先级与冲突解决

Prettier配置失效深度解析:VSCode格式化优先级与冲突解决实战 当你满怀期待地在.prettierrc中写下"singleQuote": true,保存文件后按下格式化快捷键——却发现引号依然顽固地保持双引号。这不是个例,而是前端开发者每天都会遇到的配…...

)

ATmega328P烧录Bootloader报错?别急着换芯片,可能是签名搞的鬼(附avrdude.conf修改教程)

ATmega328P烧录Bootloader报错?别急着换芯片,可能是签名搞的鬼(附avrdude.conf修改教程) 当你兴致勃勃地准备给新买的ATmega328P芯片烧录Bootloader时,突然弹出一串红色报错信息,那种心情就像煮熟的鸭子飞走…...

终极指南:如何在Windows 11上轻松安装Android应用?APK Installer完整教程

终极指南:如何在Windows 11上轻松安装Android应用?APK Installer完整教程 【免费下载链接】APK-Installer An Android Application Installer for Windows 项目地址: https://gitcode.com/GitHub_Trending/ap/APK-Installer 你是否曾经想在Window…...

CTF新手必看:一张图里藏了啥?手把手教你用010 Editor秒解BUUCTF图片隐写题

CTF新手入门:从图片隐写题中快速提取Flag的实战指南 当你第一次接触CTF比赛中的图片隐写题时,可能会感到无从下手。那些看似普通的图片背后,往往藏着关键的Flag信息。本文将带你一步步破解BUUCTF平台上的典型图片隐写题,使用010 E…...

从MySQL到Neo4j:用你熟悉的SQL思维,快速上手CQL创建第一个知识图谱

从MySQL到Neo4j:用SQL思维快速构建知识图谱的实战指南 当你在MySQL中熟练编写JOIN查询时,是否想过这些表关系本质上就是一张网?图数据库将这种网状关系作为一等公民,而Neo4j正是这个领域的佼佼者。本文会带你用熟悉的SQL视角&…...

LeetCode 合并K个排序链表题解

LeetCode 合并K个排序链表题解 题目描述 合并 k 个排序链表,返回合并后的排序链表。 示例: 输入:lists [[1,4,5],[1,3,4],[2,6]]输出:[1,1,2,3,4,4,5,6] 解题思路 方法:堆 思路: 使用最小堆存储每个链表的…...

云端开发新体验:code-server部署与多场景应用指南

1. 为什么你需要一个云端开发环境? 记得去年我同时参与三个项目时,每天要在办公室台式机、家里笔记本和平板电脑之间来回切换。每次换设备最头疼的就是开发环境不一致——Node.js版本不同、Python包缺失、配置文件没同步...有次紧急修复线上bug时&#x…...