FPGA实现PCIE采集电脑端视频缩放后转千兆UDP网络输出,基于XDMA+PHY芯片架构,提供3套工程源码和技术支持

目录

- 1、前言

- 工程概述

- 免责声明

- 2、相关方案推荐

- 我已有的PCIE方案

- 我这里已有的以太网方案

- 本博已有的FPGA图像缩放方案

- 3、PCIE基础知识扫描

- 4、工程详细设计方案

- 工程设计原理框图

- 电脑端视频

- PCIE视频采集QT上位机

- XDMA配置及使用

- XDMA中断模块

- FDMA图像缓存

- 纯Verilog图像缩放模块详解

- 纯Verilog图像缩放模块使用

- UDP视频组包发送

- UDP协议栈

- MAC数据缓冲FIFO组

- Tri Mode Ethernet MAC IP核

- PHY芯片

- IP地址、端口号的修改

- UDP视频接收显示QT上位机

- Windows版本XDMA驱动安装

- Linux版本XDMA驱动安装

- 工程源码架构

- Vivado工程注意事项

- PCIE上板调试注意事项

- 5、vivado工程源码1详解-->Artix7-100T,PCIE-->FPGA-->B50610版本

- 6、vivado工程源码2详解-->Kintex7-35T,PCIE-->FPGA-->B50610版本

- 7、vivado工程源码3详解-->Kintex7-35T,PCIE-->FPGA-->RTL8211F版本

- 8、工程移植说明

- vivado版本不一致处理

- FPGA型号不一致处理

- 其他注意事项

- 9、上板调试验证

- 准备工作

- 电脑端视频通过PCIE到FPGA端图像缩放转UDP网络视频输出效果演示

- 10、福利:工程代码的获取

FPGA实现PCIE采集电脑端视频缩放后转千兆UDP网络输出,基于XDMA+PHY芯片架构,提供3套工程源码和技术支持

1、前言

FPGA实现PCIE数据传输现状;

目前基于Xilinx系列FPGA的PCIE通信架构主要有以下2种,一种是简单的、傻瓜式的、易于开发的、对新手友好的XDMA架构,该架构对PCIE协议底层做了封装,并加上了DMA引擎,使得使用的难度大大降低,加之Xilinx提供了配套的Windows和Linux系统驱动和上位机参考源代码,使得XDMA一经推出就让工程师们欲罢不能;另一种是更为底层的、需要设计者有一定PCIE协议知识的、更易于定制化开发的7 Series Integrated Block for PCI Express架构,该IP实现的是PCIe 的物理层、链路层和事务层,提供给用户的是以 AXI4-stream 接口定义的TLP 包,使用该IP 核,需要对PCIe 协议有清楚的理解,特别是对事务包TLP报文格式;本设计采用第一种方案,使用XDMA的中断模式实现PCIE通信;本架构既有简单的测速实验,也有视频采集应用;

FPGA实现UDP网络通信现状;

Xilinx系列FPGA实现UDP网络通信主要有两种方案,其一是使用PHY芯片实现物理层功能,比如常见的RTL8211、B50610等芯片,UDP协议栈部分很简单,可使用verilog代码直接实现;其二是使用Xilinx官方的IP核实现物理层功能,比如常见的1G/2.5G Ethernet PCS/PMA or SGMII、AXI 1G/2.5G Ethernet Subsystem、10G/25G Ethernet Subsystem、10G Ethernet Subsystem等,UDP协议栈部分很简单,可使用verilog代码直接实现;本设计使用PHY芯片方案实现物理层功能;

工程概述

本设计使用Xilinx系列FPGA为平台,实现电脑端视频通过PCIE到FPGA端转UDP网络视频输出;输入源为电脑端实时视频,也就是电脑桌面的实时图像,分辨率为1280x720@60Hz;打开QT上位机,QT上位机会实时采集电脑端视频,通过PCIE总线发送到FPGA板卡;FPGA内部的XDMA IP核接收到电脑端发来的视频后,将视频写入板载DDR3中缓存;同时使用本博主常用的FDMA图像缓存架构将视频从板载DDR3中读出;然后视频送入纯verilog实现的图像缩放模块对视频进行缩放操作;然后视频再经过FDMA图像缓存架构进行图像缓存操作;视频从板载DDR3中读出后送入UDP视频组包发送模块,将视频加上包头和其他控制信息;然后组包的视频送入UDP协议栈进行以太网帧组帧;UDP协议栈输出的MAC数据经过FIFO组进行数据缓冲;MAC数据再送入Xilinx官方的Tri Mode Ethernet MAC IP核实现AXIS数据到RGMII数据转换;再经过板载的PHY网络芯片实现物理层功能,将RGMII数据转换为差分数据;再经过板载的RJ45网口,用网线传输到电脑端;电脑端使用QT上位机接收UDP网络视频并显示出来;本博客提供3套工程源码,具体如下:

现对上述3套工程源码做如下解释,方便读者理解:

工程源码1

开发板FPGA型号为Xilinx–>Artix7-100T–xc7a100tfgg484-2;输入源为电脑端实时视频,也就是电脑桌面的实时图像,分辨率为1280x720@60Hz;打开QT上位机,QT上位机会实时采集电脑端视频,通过PCIE总线发送到FPGA板卡;FPGA内部的XDMA IP核接收到电脑端发来的视频后,将视频写入板载DDR3中缓存;同时使用本博主常用的FDMA图像缓存架构将视频从板载DDR3中读出;然后视频送入纯verilog实现的图像缩放模块对视频进行缩放操作;将原视频分辨率从1920x1080缩放为1280x720;然后视频再经过FDMA图像缓存架构进行图像缓存操作;视频从板载DDR3中读出后送入UDP视频组包发送模块,将视频加上包头和其他控制信息;然后组包的视频送入UDP协议栈进行以太网帧组帧;UDP协议栈输出的MAC数据经过FIFO组进行数据缓冲;MAC数据再送入Xilinx官方的Tri Mode Ethernet MAC IP核实现AXIS数据到RGMII数据转换;再经过板载的B50610网络芯片实现物理层功能,将RGMII数据转换为差分数据;再经过板载的RJ45网口,用网线传输到电脑端;电脑端使用QT上位机接收UDP网络视频并显示出来;板载的PCIE为1 Lane的PCIE2.0;单Lane线速率配置为5GT/s;板载的PHY芯片为B50610,工作于延时模式,输出RGMII接口数据;由此形成QT上位机+PCIE+XDMA+UDP的高端架构;该工程适用于PCIE接口的视频采集卡或者网卡应用;

工程源码2

开发板FPGA型号为Xilinx–>Kintex7–35T–xc7k325tffg676-2;输入源为电脑端实时视频,也就是电脑桌面的实时图像,分辨率为1280x720@60Hz;打开QT上位机,QT上位机会实时采集电脑端视频,通过PCIE总线发送到FPGA板卡;FPGA内部的XDMA IP核接收到电脑端发来的视频后,将视频写入板载DDR3中缓存;同时使用本博主常用的FDMA图像缓存架构将视频从板载DDR3中读出;然后视频送入纯verilog实现的图像缩放模块对视频进行缩放操作;将原视频分辨率从1920x1080缩放为1280x720;然后视频再经过FDMA图像缓存架构进行图像缓存操作;视频从板载DDR3中读出后送入UDP视频组包发送模块,将视频加上包头和其他控制信息;然后组包的视频送入UDP协议栈进行以太网帧组帧;UDP协议栈输出的MAC数据经过FIFO组进行数据缓冲;MAC数据再送入Xilinx官方的Tri Mode Ethernet MAC IP核实现AXIS数据到RGMII数据转换;再经过板载的B50610网络芯片实现物理层功能,将RGMII数据转换为差分数据;再经过板载的RJ45网口,用网线传输到电脑端;电脑端使用QT上位机接收UDP网络视频并显示出来;板载的PCIE为4 Lane的PCIE2.0;单Lane线速率配置为5GT/s;板载的PHY芯片为B50610,工作于延时模式,输出RGMII接口数据;由此形成QT上位机+PCIE+XDMA+UDP的高端架构;该工程适用于PCIE接口的视频采集卡或者网卡应用;

工程源码3

开发板FPGA型号为Xilinx–>Zynq7100–xc7z100ffg900-2;输入源为电脑端实时视频,也就是电脑桌面的实时图像,分辨率为1280x720@60Hz;打开QT上位机,QT上位机会实时采集电脑端视频,通过PCIE总线发送到FPGA板卡;FPGA内部的XDMA IP核接收到电脑端发来的视频后,将视频写入板载DDR3中缓存;同时使用本博主常用的FDMA图像缓存架构将视频从板载DDR3中读出;然后视频送入纯verilog实现的图像缩放模块对视频进行缩放操作;将原视频分辨率从1920x1080缩放为1280x720;然后视频再经过FDMA图像缓存架构进行图像缓存操作;视频从板载DDR3中读出后送入UDP视频组包发送模块,将视频加上包头和其他控制信息;然后组包的视频送入UDP协议栈进行以太网帧组帧;UDP协议栈输出的MAC数据经过FIFO组进行数据缓冲;MAC数据再送入Xilinx官方的Tri Mode Ethernet MAC IP核实现AXIS数据到RGMII数据转换;再经过板载的RTL8211F网络芯片实现物理层功能,将RGMII数据转换为差分数据;再经过板载的RJ45网口,用网线传输到电脑端;电脑端使用QT上位机接收UDP网络视频并显示出来;板载的PCIE为8 Lane的PCIE2.0;单Lane线速率配置为5GT/s;板载的PHY芯片为RTL8211F,工作于延时模式,输出RGMII接口数据;由此形成QT上位机+PCIE+XDMA+UDP的高端架构;该工程适用于PCIE接口的视频采集卡或者网卡应用;

电脑端视频通过PCIE到FPGA端图像缩放转UDP网络视频输出的设计方案,工程代码可综合编译上板调试,可直接项目移植,适用于在校学生、研究生项目开发,也适用于在职工程师做项目开发,可应用于医疗、军工等行业的高速接口领域;

提供完整的、跑通的工程源码和技术支持;

工程源码和技术支持的获取方式放在了文章末尾,请耐心看到最后;

免责声明

本工程及其源码即有自己写的一部分,也有网络公开渠道获取的一部分(包括CSDN、Xilinx官网、Altera官网等等),若大佬们觉得有所冒犯,请私信批评教育;基于此,本工程及其源码仅限于读者或粉丝个人学习和研究,禁止用于商业用途,若由于读者或粉丝自身原因用于商业用途所导致的法律问题,与本博客及博主无关,请谨慎使用。。。

2、相关方案推荐

我已有的PCIE方案

我的主页有PCIE通信专栏,该专栏基于XDMA的轮询模式实现与QT上位机的数据交互,既有基于RIFFA实现的PCIE方案,也有基于XDMA实现的PCIE方案;既有简单的数据交互、测速,也有应用级别的图像采集传输,以下是专栏地址:

点击直接前往

此外,我的主页有中断模式的PCIE通信专栏,该专栏基于XDMA的中断模式实现与QT上位机的数据交互,以下是专栏地址:

点击直接前往

此外,还有基于RIFFA架构的PCIE通信专栏,以下是专栏地址:

点击直接前往

我这里已有的以太网方案

目前我这里有大量UDP协议的工程源码,包括UDP数据回环,视频传输,AD采集传输等,也有TCP协议的工程,还有RDMA的NIC 10G 25G 100G网卡工程源码,对网络通信有需求的兄弟可以去看看:

直接点击前往

其中千兆TCP协议的工程博客如下:

直接点击前往

本博已有的FPGA图像缩放方案

我的主页目前有FPGA图像缩放专栏,改专栏收录了我目前手里已有的FPGA图像缩放方案,从实现方式分类有基于HSL实现的图像缩放、基于纯verilog代码实现的图像缩放;从应用上分为单路视频图像缩放、多路视频图像缩放、多路视频图像缩放拼接;从输入视频分类可分为OV5640摄像头视频缩放、SDI视频缩放、MIPI视频缩放等等;以下是专栏地址:

点击直接前往

3、PCIE基础知识扫描

PCIe 总线架构与以太网的 OSI 模型类似,是一种分层协议架构,分为事务层(Transaction Layer)、数据链路层(Data Link Layer) 和物理层(Physical Layer)。这些层中的每一层都分为两部分:一部分处理出站(要发送的)信息,另一部分处理入站(接收的)信息,如下图:

事务层

事务层的主要责任是事务层包 TLP(Transaction Layer Packet)的组装和拆卸。事务层接收来自 PCIe 设备核心层的数据,并将其封装为 TLP。TLP 用于传达事务,例如读取和写入,以及确定事件的类型。事务层还负责管理 TLP 的基于信用的流控制。每个需要响应数据包的请求数据包都作为拆分事务实现。每个数据包都有一个唯一标识符,该标识符使响应数据包可以定向到正确的始发者。数据包格式支持不同形式的寻址,具体取决于事务的类型(内存、I/O、配置和消息)。数据包可能还具有诸如 No Snoop、Relaxed Ordering 和基于 ID 的排序(IDO)之类的属性。事务层支持四个地址空间:包括三个 PCI 地址空间(内存、I/O 和配置)并添加消息空间。该规范使用消息空间来支持所有先前 PCI 的边带信号,例如中断、电源管理请求等,作为带内消息事务。

数据链路层

数据链路层充当事务层和物理层之间的中间阶段。数据链路层的主要职责包括链路管理和数据完整性,包括错误检测和错误纠正。数据链路层的发送方接受事务层组装的 TLP,计算并应用数据保护代码和 TLP序列号,以及将它们提交给物理层以在链路上传输。接收数据链路层负责检查接收到的 TLP 的完整性,并将它们提交给事务层以进行进一步处理。在检测到 TLP 错误时,此层负责请求重发 TLP,直到正确接收信息或确定链路失败为止。数据链路层还生成并使用用于链路管理功能的数据包。为了将这些数据包与事务层(TLP)使用的数据包区分开,当指代在数据链路层生成和使用的数据包时,将使用术语“数据链路层数据包(DLLP)”。

物理层

PCIe 总线的物理层为 PCIe 设备间的数据通信提供传送介质,为数据传送提供可靠的物理环境。物理层包括用于接口操作的所有电路,包括驱动器和输入缓冲器、并行至串行和串行至并行转换、PLL 和阻抗匹配电路。它还包括与接口初始化和维护有关的逻辑功能。物理层以实现特定的格式与数据链路层交换信息。该层负责将从数据链路层接收的信息转换为适当的序列化格式,并以与连接到链路另一端的设备兼容的频率和通道宽度在 PCI Express 链路上传输该信息。物理层是 PCIe 体系结构最重要,也是最难以实现的组成部分(该层对用户透明,开发 PCIe 程序时无需关心)。PCIe 总线的物理层定义了 LTSSM (Link Training and Status State Machine)状态机,PCIe 链路使用该状态机管理链路状态,并进行链路训练、链路恢复和电源管理。PCIe 总线使用端到端的连接方式,在一条PCIe 链路的两端只能各连接一个设备,这两个设备互为数据发送端和数据接收端。由于 PCIe 是支持全双工通信的,所以发送端和接收端中都含有TX (发送逻辑) 和RX (接收逻辑)。在PCIe 总线的物理链路的一个数据通路(Lane) 中,有两组差分信号,共4 根信号线组成。其中发送端的TX 与接收端的RX 使用一组差分信号连接,该链路也被称为发送端的发送链路,也是接收端的接收链路;而发送端的RX 与接收端的TX 使用另一组差分信号连接,该链路也被称为发送端的接收链路,也是接收端的发送链路。一个PCIe 链路可以由多个Lane 组成。目前PCIe 链路可以支持1、2、4、8、12、16 和32 个Lane,即×1、×2、×4、×8、×12、×16 和×32 宽度的PCIe 链路。每一个Lane 上使用的总线频率与PCIe 总线使用的版本相关。

4、工程详细设计方案

工程设计原理框图

工程设计原理框图如下:

电脑端视频

输入源为电脑端实时视频,也就是电脑桌面的实时图像,分辨率为1920x1080@60Hz;电脑端的分辨率需要设置为1920x1080@60Hz,如下:

PCIE视频采集QT上位机

仅提供Win10版本的QT上位机,位置如下:

以Win10版本为例,源码位置如下:

以Win10版本下,可以点击已经编译好的QT软件直接运行,位置如下:

QT上位机运行效果如下:

XDMA配置及使用

根据Xilinx官方手册,XDMA框图如下:

由图可知,XDMA封装了Integrated Block for PCI Express IP,不仅完成了事务层的组包解包,还添加了完整的 DMA 引擎;

XDMA 一般情况下使用AXI4 接口,AXI4 接口可以加入到系统总线互联,适用于大数据量异步传输,而且通常情况下使用 XDMA 都会使用到 BRAM 或 DDR 内存;AXI4-Stream 接口适用于低延迟数据流传输。XDMA 允许在主机内存和 DMA 子系统之间移动数据。它通过对包含有关要传输的数据的源、目标和数量的信息的“描述符”进行操作来实现此目的。这些直接内存传输既可以用于主机到卡(Host to Card,H2C)的传输,也可以用与卡到主机(Card to Host,C2H)的传输。可以将 DMA 配置为由所有通道共享一个 AXI4 Master 接口,或者为每个启用的通道提供一个 AXI4-Stream 接口。内存传输是基于每个通道的描述符链接列表指定的,DMA 从主机内存和进程中获取这些链接列表。诸如描述符完成和错误之类的事件通过中断来发出信号。XDMA 还提供多达 16 条用户中断线,这些中断线会向主机生成中断。本设计需要配置为中断模式;如下图:

XDMA详情参考《AXI Bridge for PCI Express Gen3 Subsystem Product Guide(PG194)》;XDMA在Block Design中如下:

XDMA中断模块

XDMA中断模块和XDMA IP配合使用,XDMA中断模块主要执行两个任务,一是获取XDMA的状态,输出用户中断使能信号,以指示用户此时可以发起中断,该任务通过AXI_Lite接口与XDMA连接,其从机地址受PC端软件控制;二是转发用户中断给XDMA,当用户侧检测到XDMA处于可接受中断状态时,用户逻辑可以发起中断,XDMA中断模块将此中断转发给XDMA IP;将模块直接拖入Block Design中,显示如下:

FDMA图像缓存

FDMA图像缓存架构实现的功能是将输入视频缓存到板载DDR3中,由于调用了Xilinx官方的MIG作为DDR控制器,所以FDMA图像缓存架构就是实现用户数据到MIG的桥接作用;架构如下:

FDMA图像缓存架构由FDMA控制器+FDMA组成;FDMA实际上就是一个AXI4-FULL总线主设备,与MIG对接,MIG配置为AXI4-FULL接口;FDMA控制器实际上就是一个视频读写逻辑,以写视频为例,假设一帧图像的大小为M×N,其中M代表图像宽度,N代表图像高度;FDMA控制器每次写入一行视频数据,即每次向DDR3中写入M个像素,写N次即可完成1帧图像的缓存,本设计只用到了2路FDMA控制器,其中一路只用到了读数据功能,用作将PCIE传来的视频从DDR3中读出,另一路FDMA用到了读写功能,作用是将图像缩放后的视频缓存一下,以优化视频时序;第一路FDMA控制器IP配置如下:

FDMA图像缓存架构在Block Design中如下:

纯Verilog图像缩放模块详解

本设计图像缩放模块使用纯Verilog方案,功能框图如下,由跨时钟FIFO、插值+RAM阵列构成,跨时钟FIFO的目的是解决跨时钟域的问题,比如从低分辨率视频放大到高分辨率视频时,像素时钟必然需要变大,这是就需要异步FIFO了,插值算法和RAM阵列具体负责图像缩放算法层面的实现;

插值算法和RAM阵列以ram和fifo为核心进行数据缓存和插值实现,设计架构如下:

图像缩放模块代码架构如下:模块的例化请参考工程源码的顶层代码;

图像缩放模块FIFO的选择可以调用工程对应的vivado工具自带的FIFO IP核,也可以使用纯verilog实现的FIFO,可通过接口参数选择,图像缩放模块顶层接口如下:

module helai_video_scale #(//---------------------------Parameters----------------------------------------parameter FIFO_TYPE = "xilinx", // "xilinx" for xilinx-fifo ; "verilog" for verilog-fifoparameter DATA_WIDTH = 8 , //Width of input/output dataparameter CHANNELS = 1 , //Number of channels of DATA_WIDTH, for color imagesparameter INPUT_X_RES_WIDTH = 11 //Widths of input/output resolution control signals

)(input i_reset_n , // 输入--低电平复位信号input [INPUT_X_RES_WIDTH-1:0] i_src_video_width , // 输入视频--即缩放前视频的宽度input [INPUT_X_RES_WIDTH-1:0] i_src_video_height, // 输入视频--即缩放前视频的高度input [INPUT_X_RES_WIDTH-1:0] i_des_video_width , // 输出视频--即缩后前视频的宽度input [INPUT_X_RES_WIDTH-1:0] i_des_video_height, // 输出视频--即缩后前视频的高度input i_src_video_pclk , // 输入视频--即缩前视频的像素时钟input i_src_video_vs , // 输入视频--即缩前视频的场同步信号,必须为高电平有效input i_src_video_de , // 输入视频--即缩前视频的数据有效信号,必须为高电平有效input [DATA_WIDTH*CHANNELS-1:0] i_src_video_pixel , // 输入视频--即缩前视频的像素数据input i_des_video_pclk , // 输出视频--即缩后视频的像素时钟,一般为写入DDR缓存的时钟output o_des_video_vs , // 输出视频--即缩后视频的场同步信号,高电平有效output o_des_video_de , // 输出视频--即缩后视频的数据有效信号,高电平有效output [DATA_WIDTH*CHANNELS-1:0] o_des_video_pixel // 输出视频--即缩后视频的像素数据

);

FIFO_TYPE选择原则如下:

1:总体原则,选择"xilinx"好处大于选择"verilog";

2:当你的FPGA逻辑资源不足时,请选"xilinx";

3:当你图像缩放的视频分辨率较大时,请选"xilinx";

4:当你的FPGA没有FIFO IP或者FIFO IP快用完了,请选"verilog";

5:当你向自学一下异步FIFO时,,请选"verilog";

6:不同FPGA型号对应的工程FIFO_TYPE参数不一样,但选择原则一样,具体参考代码;

2种插值算法的整合与选择

本设计将常用的双线性插值和邻域插值算法融合为一个代码中,通过输入参数选择某一种算法;

具体选择参数如下:

input wire i_scaler_type //0-->bilinear;1-->neighbor

通过输入i_scaler_type 的值即可选择;

输入0选择双线性插值算法;

输入1选择邻域插值算法;

代码里的配置如下:

纯Verilog图像缩放模块使用

图像缩放模块使用非常简单,顶层代码里设置了四个参数,举例如下:

当然,需要修改的不仅仅这一个地方,FDMA的配置也需要相应修改,详情请参考代码,但我想要证明的是,图像缩放模块使用非常简单,你都不需要知道它内部具体怎么实现的,上手就能用;

UDP视频组包发送

UDP视频组包发送实现视频数据的组包并通过UDP协议栈发送出去,视频数据发送必须与QT上位机的接受程序一致,上位机定义的UDP帧格式包括帧头个UDP数据,QT上位机接收代码数据帧头定义如下:

FPGA端的UDP数据组包代码必须与上图的数据帧格式对应,否则QT无法解析,代码中定义了数据组包状态机以及数据帧,如下:

另外,由于UDP发送是64位数据位宽,而图像像素数据是24bit位宽,所以必须将UDP数据重新组合,以保证像素数据的对齐,这部分是整个工程的难点,也是所有FPGA做UDP数据传输的难点;UDP视频组包发送代码架构如下:

UDP协议栈

本UDP协议栈使用UDP协议栈网表文件,该协议栈目前并不开源,只提供网表文件,虽看不见源码但可正常实现UDP通信,但不影响使用,该协议栈带有用户接口,使得用户无需关心复杂的UDP协议而只需关心简单的用户接口时序即可操作UDP收发,非常简单;协议栈架构如下:

协议栈性能表现如下:

1:支持 UDP 接收校验和检验功能,暂不支持 UDP 发送校验和生成;

2:支持 IP 首部校验和的生成和校验,同时支持 ICMP 协议中的 PING 功能,可接收并响应同一个子网内部设备的 PING 请求;

3:可自动发起或响应同一个子网内设备的 ARP 请求,ARP 收发完全自适应。ARP 表可保存同一个子网内部256 个 IP 和 MAC 地址对;

4:支持 ARP 超时机制,可检测所需发送数据包的目的 IP 地址是否可达;

5:协议栈发送带宽利用率可达 93%,高发送带宽下,内部仲裁机制保证 PING 和 ARP 功能不受任何影响;

6:发送过程不会造成丢包;

7:提供64bit位宽AXI4-Stream形式的MAC接口,可与Xilinx官方的千兆以太网IP核Tri Mode Ethernet MAC,以及万兆以太网 IP 核 10 Gigabit Ethernet Subsystem、10 Gigabit Ethernet MAC 配合使用;

有了此协议栈,我们无需关心复杂的UDP协议的实现了,直接调用接口即可使用。。。

本UDP协议栈用户接口发送时序如下:

本UDP协议栈用户接口接收时序如下:

MAC数据缓冲FIFO组

这里对代码中用到的数据缓冲FIFO组做如下解释:

由于 UDP IP 协议栈的 AXI-Stream 数据接口位宽为 64bit,而 Tri Mode Ethernet MAC 的 AXI-Stream数据接口位宽为 8bit。因此,要将 UDP IP 协议栈与 Tri Mode Ethernet MAC 之间通过 AXI-Stream 接口互联,需要进行时钟域和数据位宽的转换。实现方案如下图所示:

收发路径(本设计只用到了发送)都使用了2个AXI-Stream DATA FIFO,通过其中1个FIFO实现异步时钟域的转换,1个FIFO实

现数据缓冲和同步Packet mode功能;由于千兆速率下Tri Mode Ethernet MAC的AXI-Stream数据接口同步时钟信号为125MHz,此时,UDP协议栈64bit的AXI-Stream数据接口同步时钟信号应该为125MHz/(64/8)=15.625MHz,因此,异步

AXI-Stream DATA FIFO两端的时钟分别为125MHz(8bit),15.625MHz(64bit);UDP IP协议栈的AXI-Stream接口经过FIFO时钟域转换后,还需要进行数据数据位宽转换,数据位宽的转换通过AXI4-Stream Data Width Converter完成,在接收路径中,进行 8bit 到 64bit 的转换;在发送路径中,进行 64bit 到 8bit 的转换;MAC数据缓冲FIFO组代码架构如下:

Tri Mode Ethernet MAC IP核

Tri Mode Ethernet MAC主要是为了适配PHY芯片,因为后者的输入接口是GMII,而Tri Mode Ethernet MAC的输入接口是AXIS,输出接口是GMII,Tri Mode Ethernet MAC配置如下:

Tri Mode Ethernet MAC IP核还需要复位和配置逻辑才能工作,整体代码架构如下:

此外,Tri Mode Ethernet MAC IP核在配合不同型号的PHY芯片使用时用法也不一样,给开发者带来了很大麻烦,基于此本博主提供Tri Mode Ethernet MAC针对B50610和RTL8211F的使用教程和移植教程,这两款PHY芯片在延时模式下的RGMII时序具有代表性,所以看了本博主提供的Tri Mode Ethernet MAC IP核移植修改教程,再去做其他PHY芯片的工程时,应该是可以得心应手的;

PHY芯片

本工程的PHY芯片使用了B50610和RTL8211F,为什么选择这两款芯片呢?一是因为这两款芯片成熟稳定,市场占有率较高,二是因为这两款芯片在延时模式下的RGMII时序具有代表性,做过本博主提供的工程项目,再去做其他PHY芯片的工程时,应该是可以得心应手的;为了照顾到做硬件的开发者,本博主还提供了B50610和RTL8211F的参考原理图;

IP地址、端口号的修改

UDP协议栈留出了IP地址、端口号的修改端口供用户自由修改,位置在顶层模块如下:

UDP视频接收显示QT上位机

仅提供Win10版本的QT上位机,位置如下:

以Win10版本为例,源码位置如下:

以Win10版本下,可以点击已经编译好的QT软件直接运行,位置如下:

QT上位机运行效果如下:

我们的QT目前仅支持1280x720分辨率的视频抓图显示,但同时预留了1080P接口,对QT开发感兴趣的朋友可以尝试修改代码以适应1080P,因为QT在这里只是验证工具,不是本工程的重点,所以不再过多赘述;

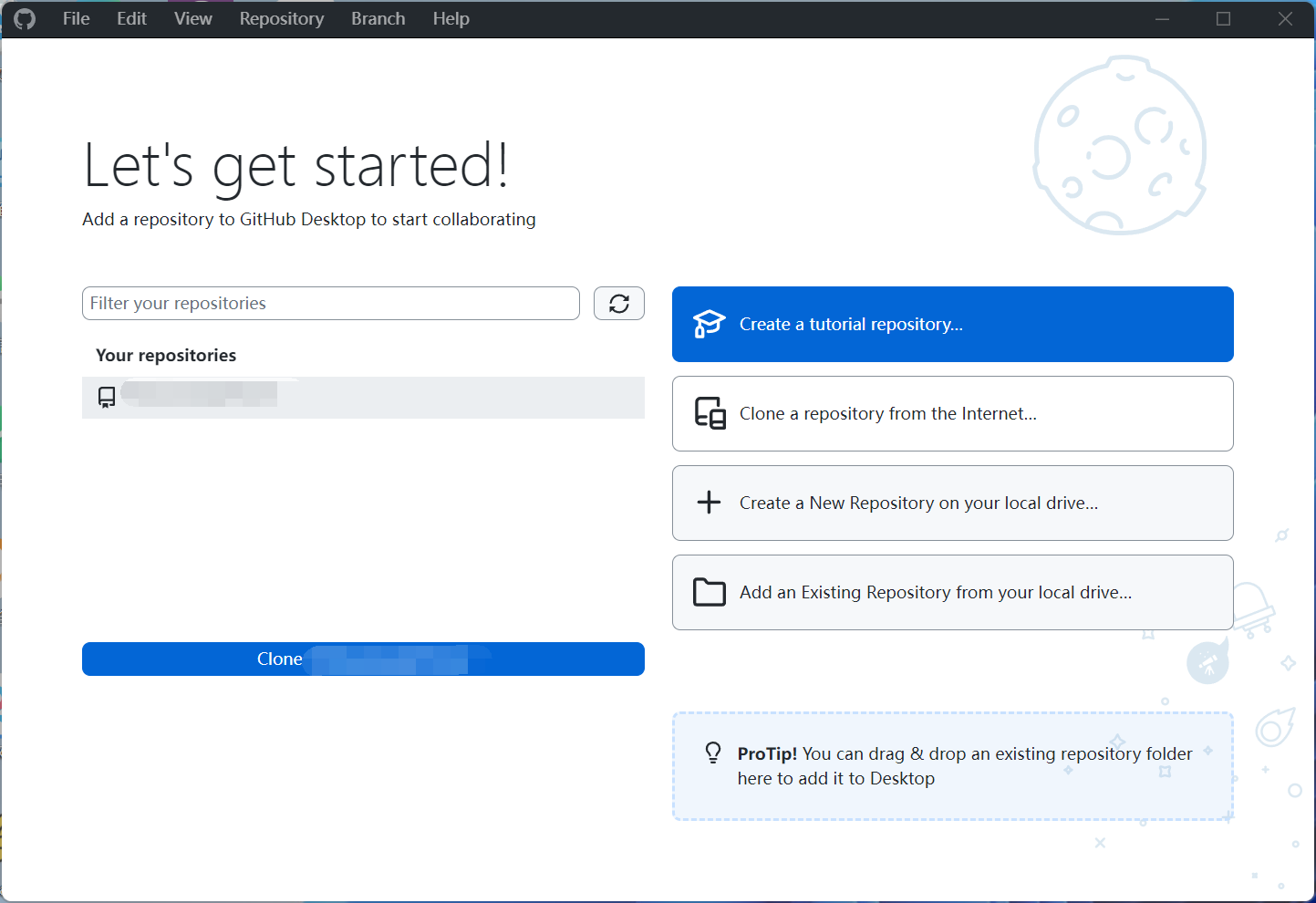

Windows版本XDMA驱动安装

提供Windows和Linux系统驱动,本章节介绍Windows下XDMA驱动安装;

Windows下驱动安装步骤如下:友情提示,Windows下驱动秩序安装一次即可;

第一步:使系统禁用签名并进入测试模式,方法如下:

也可百度其他方法实现上述目的,完成后电脑屏幕右下角应有如下显示:

第二步:定位到驱动目录下,提供Windows7和Windows10两个版本驱动,由于我的电脑选择Windows10,如下:

单击鼠标右键安装即可,如下:

第三步:下载FPGA工程bit到FPGA开发板,然后重启电脑,打开我的电脑–>管理–>设备管理器,应看到如下设备:

Linux版本XDMA驱动安装

提供Windows和Linux系统驱动,本章节介绍Linux下XDMA驱动安装;

Linux下驱动安装步骤如下:友情提示,Linux下,每次下载FPGA bit后都需要重启电脑才能安装驱动;

进入到Linux驱动目录下,一次执行以下两条指令即可安装,如下:

• 驱动编译终端指令:make -j8

•驱动安装终端指令:sudo insmod xdma.ko

工程源码架构

提供3套工程源码,以工程源码1为例,工程Block Design设计如下:

提供3套工程源码,以工程源码1为例,综合后的工程源码架构如下:

Vivado工程注意事项

Vivado工程需要配合修改过的Xilinx官方XDMA驱动和QT上位机一起使用,所以Vivado工程必须做到以下几点:

1:XDMA中的AXI4_Lite基地址必须设为0x44A00000,这是XDMA驱动修改的规定,感兴趣的可以去看驱动源码,配置如下;

2:MIG的DDR基地址必须从0x00000000开始,这是QT上位机代码的规定,感兴趣的可以去看QT源码,配置如下;

PCIE上板调试注意事项

1:必须先安装本博提供的XDMA驱动,详情请参考第4章节的《XDMA驱动及其安装》,Windows版本驱动只需安装一次;

2:Windows版本下载FPGA工程bit后需要重启电脑,电脑才能识别到XDMA驱动;程序固化后也需要重启电脑;Linux版本每次载FPGA工程bit后都需要重启电脑,都需要安装XDMA驱动;

3:FPGA板卡插在主机上后一般不需要额外供电,如果你的板子元器件较多功耗较大,则需要额外供电,详情咨询开发板厂家,当然,找我买板子的客户可以直接问我;

4:PCIE调试需要电脑主机,但笔记本电脑理论上也可以外接出来PCIE,详情百度自行搜索一下,电脑主机PCIE插槽不方便操作时可以使用延长线接出来,某宝有卖;

5、vivado工程源码1详解–>Artix7-100T,PCIE–>FPGA–>B50610版本

开发板FPGA型号:Xilinx–Artix7–xc7a100tfgg484-2;

FPGA开发环境:Vivado2019.1;

QT开发环境:VS2015 + Qt 5.12.10;

输入:电脑主机实时视频,分辨率1920x1080@60Hz;

输出:UDP网络视频,分辨率1280x720@60Hz;

PC端到FDMA传输方案:PCIE传输;

图像缩放方案:自研纯Verilog图像缩放;

图像缩放实例:1920x1080缩放到1280x720;

图像缓存方案:FDMA图像缓存+DDR3颗粒;

PCIE底层方案:Xilinx XDMA;

PCIE详情:PCIE2.0版本,X1,5GT/s单lane线速率;

UDP协议栈:千兆UDP协议栈;

MAC层方案:Xilinx官方Tri Mode Ethernet MAC IP核方案;

以太网物理层方案:PHY芯片–B50610方案;延时模式;RGMII接口;

实现功能:电脑端视频通过PCIE到FPGA端图像缩放转转UDP网络视频输出;

工程作用:此工程目的是让读者掌握电脑端视频通过PCIE到FPGA端图像缩放转转UDP网络视频输出的设计能力,以便能够移植和设计自己的项目;

工程Block Design和工程代码架构请参考第4章节的《工程源码架构》小节内容;

工程的资源消耗和功耗如下:

6、vivado工程源码2详解–>Kintex7-35T,PCIE–>FPGA–>B50610版本

开发板FPGA型号:Xilinx–>Kintex7–35T–xc7k325tffg676-2;

FPGA开发环境:Vivado2019.1;

QT开发环境:VS2015 + Qt 5.12.10;

输入:电脑主机实时视频,分辨率1920x1080@60Hz;

输出:UDP网络视频,分辨率1280x720@60Hz;

PC端到FDMA传输方案:PCIE传输;

图像缩放方案:自研纯Verilog图像缩放;

图像缩放实例:1920x1080缩放到1280x720;

图像缓存方案:FDMA图像缓存+DDR3颗粒;

PCIE底层方案:Xilinx XDMA;

PCIE详情:PCIE2.0版本,X4,5GT/s单lane线速率;

UDP协议栈:千兆UDP协议栈;

MAC层方案:Xilinx官方Tri Mode Ethernet MAC IP核方案;

以太网物理层方案:PHY芯片–B50610方案;延时模式;RGMII接口;

实现功能:电脑端视频通过PCIE到FPGA端图像缩放转转UDP网络视频输出;

工程作用:此工程目的是让读者掌握电脑端视频通过PCIE到FPGA端图像缩放转转UDP网络视频输出的设计能力,以便能够移植和设计自己的项目;

工程Block Design和工程代码架构请参考第4章节的《工程源码架构》小节内容;

工程的资源消耗和功耗如下:

7、vivado工程源码3详解–>Kintex7-35T,PCIE–>FPGA–>RTL8211F版本

开发板FPGA型号:Xilinx–>Kintex7–35T–xc7k325tffg900-2;

FPGA开发环境:Vivado2019.1;

QT开发环境:VS2015 + Qt 5.12.10;

输入:电脑主机实时视频,分辨率1920x1080@60Hz;

输出:UDP网络视频,分辨率1280x720@60Hz;

PC端到FDMA传输方案:PCIE传输;

图像缩放方案:自研纯Verilog图像缩放;

图像缩放实例:1920x1080缩放到1280x720;

图像缓存方案:FDMA图像缓存+DDR3颗粒;

PCIE底层方案:Xilinx XDMA;

PCIE详情:PCIE2.0版本,X8,5GT/s单lane线速率;

UDP协议栈:千兆UDP协议栈;

MAC层方案:Xilinx官方Tri Mode Ethernet MAC IP核方案;

以太网物理层方案:PHY芯片–RTL8211F方案;延时模式;RGMII接口;

实现功能:电脑端视频通过PCIE到FPGA端图像缩放转转UDP网络视频输出;

工程作用:此工程目的是让读者掌握电脑端视频通过PCIE到FPGA端图像缩放转转UDP网络视频输出的设计能力,以便能够移植和设计自己的项目;

工程Block Design和工程代码架构请参考第4章节的《工程源码架构》小节内容;

工程的资源消耗和功耗如下:

8、工程移植说明

vivado版本不一致处理

1:如果你的vivado版本与本工程vivado版本一致,则直接打开工程;

2:如果你的vivado版本低于本工程vivado版本,则需要打开工程后,点击文件–>另存为;但此方法并不保险,最保险的方法是将你的vivado版本升级到本工程vivado的版本或者更高版本;

3:如果你的vivado版本高于本工程vivado版本,解决如下:

打开工程后会发现IP都被锁住了,如下:

此时需要升级IP,操作如下:

FPGA型号不一致处理

如果你的FPGA型号与我的不一致,则需要更改FPGA型号,操作如下:

更改FPGA型号后还需要升级IP,升级IP的方法前面已经讲述了;

其他注意事项

1:由于每个板子的DDR不一定完全一样,所以MIG IP需要根据你自己的原理图进行配置,甚至可以直接删掉我这里原工程的MIG并重新添加IP,重新配置;

2:根据你自己的原理图修改引脚约束,在xdc文件中修改即可;

3:纯FPGA移植到Zynq需要在工程中添加zynq软核;

9、上板调试验证

准备工作

需要准备的器材如下:

FPGA开发板,没有开发板可以找本博提供;

带PCIE卡槽的电脑主机;

网线;

我的开发板了连接如下:

电脑端视频通过PCIE到FPGA端图像缩放转UDP网络视频输出效果演示

电脑端视频通过PCIE到FPGA端图像缩放转UDP网络视频输出效果如下:

XDMA-FPGA-UDP-PHY

10、福利:工程代码的获取

福利:工程代码的获取

代码太大,无法邮箱发送,以某度网盘链接方式发送,

资料获取方式:私,或者文章末尾的V名片。

网盘资料如下:

此外,有很多朋友给本博主提了很多意见和建议,希望能丰富服务内容和选项,因为不同朋友的需求不一样,所以本博主还提供以下服务:

相关文章:

FPGA实现PCIE采集电脑端视频缩放后转千兆UDP网络输出,基于XDMA+PHY芯片架构,提供3套工程源码和技术支持

目录 1、前言工程概述免责声明 2、相关方案推荐我已有的PCIE方案我这里已有的以太网方案本博已有的FPGA图像缩放方案 3、PCIE基础知识扫描4、工程详细设计方案工程设计原理框图电脑端视频PCIE视频采集QT上位机XDMA配置及使用XDMA中断模块FDMA图像缓存纯Verilog图像缩放模块详解…...

Hi3061M开发板——系统时钟频率

这里写目录标题 前言MCU时钟介绍PLLCRG_ConfigPLL时钟配置另附完整系统时钟结构图 前言 Hi3061M使用过程中,AD和APT输出,都需要考虑到时钟频率,特别是APT,关系到PWM的输出频率。于是就研究了下相关的时钟。 MCU时钟介绍 MCU共有…...

C++入门基础知识110—【关于C++ if...else 语句】

成长路上不孤单😊😊😊😊😊😊 【14后😊///C爱好者😊///持续分享所学😊///如有需要欢迎收藏转发///😊】 今日分享关于C if...else 语句的相关内容!…...

基于YOLO11深度学习的非机动车驾驶员头盔检测系统【python源码+Pyqt5界面+数据集+训练代码】深度学习实战、目标检测、卷积神经网络

《博主简介》 小伙伴们好,我是阿旭。专注于人工智能、AIGC、python、计算机视觉相关分享研究。 ✌更多学习资源,可关注公-仲-hao:【阿旭算法与机器学习】,共同学习交流~ 👍感谢小伙伴们点赞、关注! 《------往期经典推…...

图像分类-demo(Lenet),tensorflow和Alexnet

目录 demo(Lenet) 代码实现基本步骤: TensorFlow 一、核心概念 二、主要特点 三、简单实现 参数: 模型编译 模型训练 模型评估 Alexnet model.py train.py predict.py demo(Lenet) PyTorch提供了一个名为“torchvision”的附加库,其中包含…...

excel 单元格嵌入图片

1.图片右键,设置图片格式 2.属性 随单元格改为位置和大小 这样的话,图片就会嵌入到单元格,也会跟着单元格的大小而改变...

GitHub简介与安装使用入门教程

1、Git与GitHub的简介 Git是目前世界上最先进的分布式控制系统,它允许开发者跟踪和管理源代码的改动历史记录等,可以将你的代码恢复到某一个版本,支持多人协作开发。它的核心功能包括版本控制、分支管理、合并和冲突解决等,其操作…...

HTML(五)列表详解

在HTML中,列表可以分为两种,一种为有序列表。另一种为无序列表 今天就来详细讲解一下这两种列表如何实现,效果如何 1.有序列表 有序列表的标准格式如下: <ol><li>列表项一</li><li>列表项二</li>…...

SparkSQL介绍及使用

SparkSQL介绍及使用 一、什么是SparkSQL(了解) spark开发时可以使用rdd进行开发,spark还提供saprksql工具,将数据转为结构化数据进行操作 1-1 介绍 官网:https://spark.apache.org/sql/ Spark SQL是 Apache Spark 用于…...

【聚星文社】3.2版一键推文工具更新啦

【聚星文社】3.2版一键推文工具更新啦。调试了好几个通宵就是为了效果和质量。 旧版尽早更新新版,从此告别手搓! 工具入口https://iimenvrieak.feishu.cn/docx/ZhRNdEWT6oGdCwxdhOPcdds7nof...

C++基础补充(03)C++20 的 std::format 函数

文章目录 1. 使用C20 std::format2. 基本用法3. 格式说明 1. 使用C20 std::format 需要将VisualStudio默认的标准修改为C20 菜单“项目”-“项目属性”,打开如下对话框 代码中加入头文件 2. 基本用法 通过占位符{}制定格式化的位置,后面传入变量 #…...

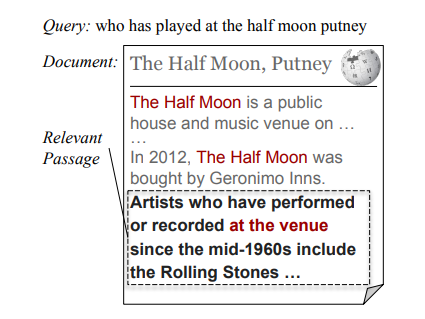

[论文笔记]DAPR: A Benchmark on Document-Aware Passage Retrieval

引言 今天带来论文DAPR: A Benchmark on Document-Aware Passage Retrieval的笔记。 本文提出了一个基准:文档感知段落检索(Document-Aware Passage Retrieval,DAPR)以及介绍了一些上下文段落表示的方法。 为了简单,下文中以翻译的口吻记录,…...

Spring Boot知识管理:智能搜索与分析

3系统分析 3.1可行性分析 通过对本知识管理系统实行的目的初步调查和分析,提出可行性方案并对其一一进行论证。我们在这里主要从技术可行性、经济可行性、操作可行性等方面进行分析。 3.1.1技术可行性 本知识管理系统采用JAVA作为开发语言,Spring Boot框…...

(进程调度/进程调度器类型/三种进程调度/调度算法))

操作系统(2) (进程调度/进程调度器类型/三种进程调度/调度算法)

目录 1. 介绍进程调度(Introduction to Process Scheduling) 2. 优先级调度(Priority Scheduling) 3. CPU 利用率(CPU Utilization) 4. 吞吐量(Throughput) 5. 周转时间…...

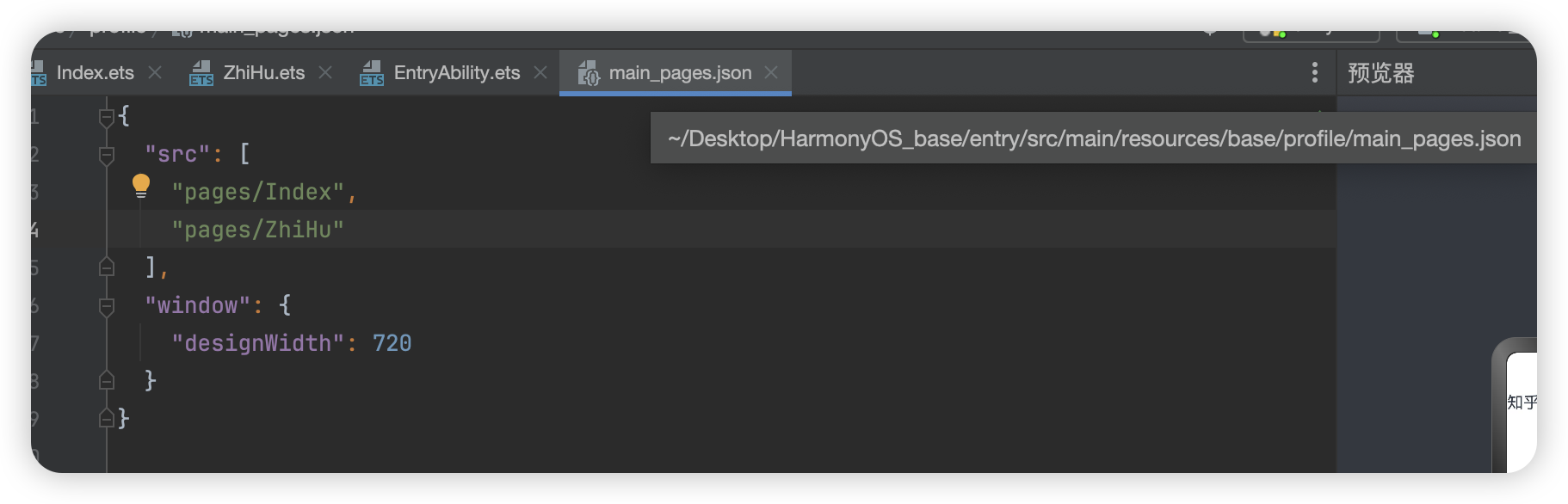

鸿蒙--知乎评论

这里我们将采用组件化的思想进行开发 在开发中默认展示的是首页也就是 pages/Index.ets页面 这里存放的是所有页面的配置文件,类似与uniapp中的pages.json 如果我们此时要更改默认显示Zh...

之间实现UDP通信(C语言版本))

2024 - 两台CentOS服务器上的1000个Docker容器(每台500个)之间实现UDP通信(C语言版本)

两台CentOS服务器上的1000个Docker容器(每台500个)之间实现UDP通信(C语言版本) 给女朋友对象写得,她不会,我就写了一个 为了帮助您在两台CentOS服务器上的1000个Docker容器(每台500个)之间实现UDP通信&…...

小程序该如何上架

小程序的上架流程通常包括准备工作、代码审核、人工审核以及上线发布等关键步骤。以下是一个详细的小程序上架指南: 一、准备工作 注册开发者账号: 在微信小程序平台或支付宝开放平台等相应的小程序发布平台上注册开发者账号。 开发小程序: …...

XMOJ3065 旅游线路

10分钟没啥思路就去看题解了,结果发现很蠢。 题目大意 有一条河,河的东侧和西侧分别有 n , m n,m n,m 个景点,每个景点有个权值。有 k k k 条船,每条船连接东侧和西侧的一个景点。定义一个旅游线路是通过船连接起来的景点序列…...

量化之一:均值回归策略

文章目录 均值回归策略理论基础数学公式 关键指标简单移动平均线(SMA)标准差Z-Score 交易信号实际应用优缺点分析优点缺点 结论 实践backtrader参数:正常情况:异常情况: 均值回归策略 均值回归(Mean Rever…...

NVIDIA Bluefield DPU上的启动流程4个阶段分别是什么?作用是什么?

文章目录 Bluefield上的硬件介绍启动流程启动流程:eMMC中的两个存储分区:ATF介绍ATF启动的四个阶段:四个主要步骤:各个阶段依赖的启动文件一次烧录fw失败后的信息看启动流程综述Bluefield上的硬件介绍 本文以Bluefield2为例,可以看到RSHIM实际上是Boot相关的集合。也能看…...

Qdrant客户端库实战:从向量数据库连接到生产级应用开发

1. 项目概述:从向量数据库到应用落地的桥梁如果你最近在折腾大模型应用,或者想给自己的产品加上一个“智能大脑”,那你大概率绕不开一个词:向量数据库。简单来说,它就像一个能理解“意思”的超级搜索引擎,不…...

ElevenLabs匈牙利语音API响应延迟飙升300%?内网穿透+CDN缓存+匈牙利语音素预加载三阶优化方案

更多请点击: https://intelliparadigm.com 第一章:ElevenLabs匈牙利文语音API响应延迟飙升300%的现象复现与根因定位 近期多位开发者反馈,ElevenLabs API 在处理匈牙利语(hu-HU)文本转语音请求时,平均端到…...

Cursor编辑器状态快照插件开发:一键保存与恢复工作区

1. 项目概述:一个专为开发者设计的“后悔药”如果你是一名重度使用 Cursor 编辑器的开发者,那么你一定经历过这样的场景:在沉浸式编码时,为了快速定位或修改,你可能会频繁地使用CtrlClick跳转到函数定义,或…...

5分钟快速上手:Windows虚拟显示器终极指南,轻松实现多屏扩展

5分钟快速上手:Windows虚拟显示器终极指南,轻松实现多屏扩展 【免费下载链接】parsec-vdd ✨ Perfect virtual display for game streaming 项目地址: https://gitcode.com/gh_mirrors/pa/parsec-vdd 还在为单显示器工作效率低下而烦恼吗…...

AI与人类共创:从替代焦虑到协作闭环

GPT-Image 2 与人类创造力的共生:从“替代焦虑”到“协作闭环”(2026 研究视角与可落地实践)当 GPT-Image 2 这样的多模态生成/理解模型进入创作流程后,“竞争还是协作”立刻变成一个绕不开的讨论。直觉上,大家会把它理…...

)

仅0.3%用户掌握的胶片叙事技巧:用Midjourney实现“过期胶卷”时间衰减效果(含Exif元数据欺骗指令集)

更多请点击: https://intelliparadigm.com 第一章:胶片叙事与数字时代的时间诗学 胶片影像的物理性——帧率、显影时长、机械快门延时——曾将时间锚定为可触摸的物质存在;而数字媒介则以纳秒级采样、无损复制与非线性剪辑,将时间…...

数字电路跨时钟域信号传输:从亚稳态到同步器设计实践

1. 跨时钟域信号传输:从亚稳态到可靠同步在数字芯片和FPGA设计中,只要系统里存在多个时钟,就绕不开跨时钟域(CDC)信号传输这个经典问题。这可不是什么高深莫测的理论,而是每个硬件工程师在画第一块板子、写…...

Midjourney概念艺术风格≠调参!20年CG总监拆解:风格生成本质是跨模态语义压缩,3个关键损失函数阈值决定成败

更多请点击: https://intelliparadigm.com 第一章:Midjourney概念艺术风格≠调参!20年CG总监的范式颠覆 风格不是参数堆砌,而是语义锚点重构 传统AI绘画工作流常将“风格”等同于反复调整 --s、--style raw 或后缀词如 trending…...

坐到马斯克和库克中间的湖南女人

梦瑶 发自 凹非寺量子位 | 公众号 QbitAI谁能在国宴现场坐在马斯克和库克中间?她——你可能不认识她的脸。△图源:《新闻联播》但你手上这块iPhone的玻璃屏,是她家公司做的。你开的特斯拉的车体配件,大概率也是。三星、Meta、摩托…...

多智能体 执行-辩论-校验 闭环架构

文章目录一、核心本质二、三大智能体权责划分1. 执行Agent(A/B/C)2. 辩论Agent3. 校验Agent(终审裁判)三、闭环流转逻辑四、关键设计规则五、TaskList 任务标准字段一、核心本质 整体架构本质:执行 → 辩论 → 校验 三…...