数字IC实践项目(10)—基于System Verilog的DDR4 Model/Tb 及基础Verification IP的设计与验证(付费项目)

数字IC实践项目(10)—基于System Verilog的DDR4 Model/Tb 及基础Verification IP的设计与验证(付费项目)

- 前言

- 项目框图

- 1)DDR4 Verification IP

- 2)DDR4 JEDEC Model & Tb

- 项目文件

- 1)DDR4 Verification IP

- 2)DDR4 JEDEC Model & Tb

- Wave&Coverage

- 1)DDR4 Verification IP

- 2)DDR4 JEDEC Model & Tb

- 3)DDR4 IBIS model sim

- 自动化脚本

- 1)Makefile脚本

- 2)Python自动化脚本

- 项目简介和资料

- 1)项目简介

- 2)拓展资料

- 软件环境要求

- 总结

前言

在之前的博客中,推出的CNN硬件加速器的设计与实现,获得了积极的反馈。这次,我希望可以继续拓展项目,避免项目同质化,帮助更多同学在秋招中提前锁定Offer,借此推出关于DDR4接口协议、仿真模型及验证IP(Verification IP)的全新项目。

对于找工作的帮助:

-

技术能力提升

掌握DDR4协议和相关仿真技术,可以增强在嵌入式系统、数字IC设计和验证领域的专业能力。 -

市场需求匹配

内存接口在市场上有很高的需求,尤其是在AI、视频处理、高速计算和数据中心领域。 -

项目经历展示

该项目可以作为简历中的重要经历,展示个人技术能力和项目管理能力,帮助你在众多求职者中脱颖而出。

项目框图

1)DDR4 Verification IP

DDR4 Verification IP项目框图的结构如下:

-

DIMM_Model:该模块用于模拟DDR4内存模块的行为,主要负责对DIMM(Dual Inline Memory Module)结构及其接口进行建模。它实现了对从DDR_TOP发送的命令的处理,包括读、写和其他控制信号,并返回相应的数据。

-

Random_Stimulus:此模块的主要功能是生成随机的激励信号,以测试DDR4接口的响应能力和稳定性。通过设计多种读写模式和边界条件,Random_Stimulus能够确保全面覆盖随机读写地址及数据操作场景。

-

DDR_TOP:作为项目的核心模块,DDR_TOP负责管理DDR4的状态机,处理各类命令的执行,包括激活(ACT)、写入(WR)、读取(RD)和预充电(PRE)等操作。它依据生成的随机激励,协调命令和数据的发送与接收。同时,DDR_TOP还会严格遵循DDR4规范,避免如空读、单个bank重复激活等违规操作,确保数据传输的准确性和可靠性。

-

MEMORY_CHECK:这一模块负责对内存操作的正确性进行检查,涵盖数据完整性、时序分析及一致性验证等功能。MEMORY_CHECK会监控DDR_TOP的操作结果,确保所有读写操作符合预期,并能够及时捕捉到潜在的错误或不一致之处,为设计提供反馈。

-

DDR_CLOCK:该模块提供DDR4所需的时钟信号,确保数据传输的同步性和稳定性。DDR_CLOCK不仅负责生成基本的时钟信号,还包括时钟延迟和相位调整,从而支持不同工作频率下的性能测试。

-

DDR_VECTOR:DDR_VECTOR模块用于产生Hspice格式激励,可用于实际电路的输入和输出比较,确保电路设计的准确性。

-

DDR Interface:此模块作为DDR4内存与外部系统之间的连接桥梁,负责数据的输入和输出。它确保了数据传输的可靠性,并处理信号转换、时序匹配等问题。

-

TB (Testbench):测试平台将所有模块集成在一起,进行全面的功能验证和性能测试。TB通过Random_Stimulus生成激励信号,监控DDR_TOP的行为,并利用MEMORY_CHECK进行结果的验证。测试平台还可以配置不同的测试场景和参数,以适应各种验证需求,确保DDR4 IP在各种条件下均能正常工作。

2)DDR4 JEDEC Model & Tb

项目额外提供一个标准JEDEC的DDR4 仿真Model及相关Tb,顶层设计如下:

- Timing Setting table:提供1066~4000Mbps,覆盖完整JEDEC Spec速度挡位的相关Timing设定;

- Golden behavior model: 提供JEDEC 标准DDR4的行为模型,支持Act/Write/Read/Pre/MRW/MRR等操作;

- DDR4 interface:提供全局DDR4接口信号,例如CK/DQS/DQ/CA等;

- testbench: 提供顶层测试模块,涵盖Power Up/Power Down/MRW/Refresh/Precharge/Activate/Write/Read等基础操作task;

- Other:提供包含容量、位宽定义等相关项目参数定义。

项目文件

项目文件列表如下:

1)DDR4 Verification IP

2)DDR4 JEDEC Model & Tb

Wave&Coverage

1)DDR4 Verification IP

2KB Random Wr/Rd Stimulus

Memory check report & final rpt

Code Coverage

2)DDR4 JEDEC Model & Tb

tccds seamless wr/rd

Code Coverage

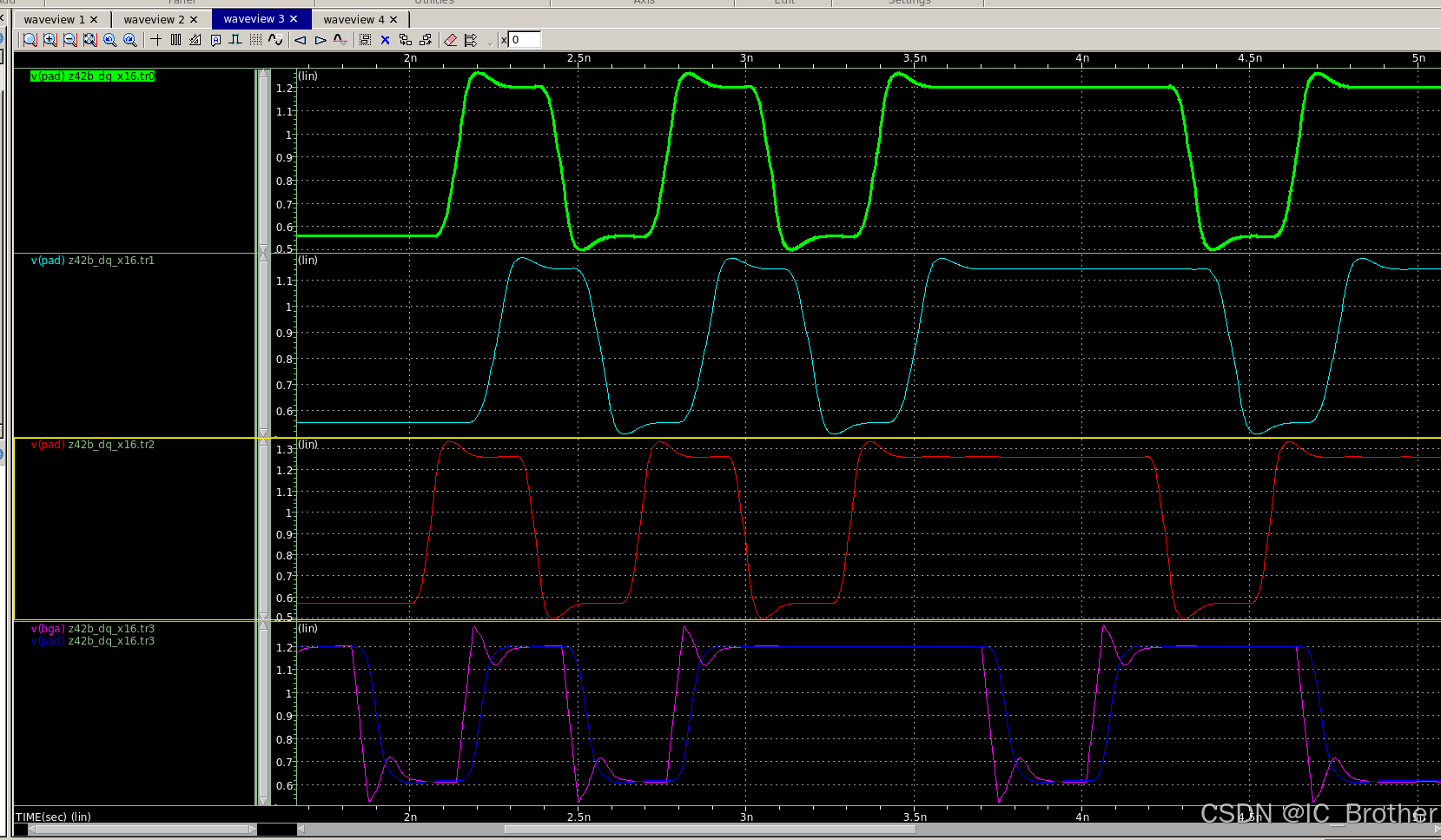

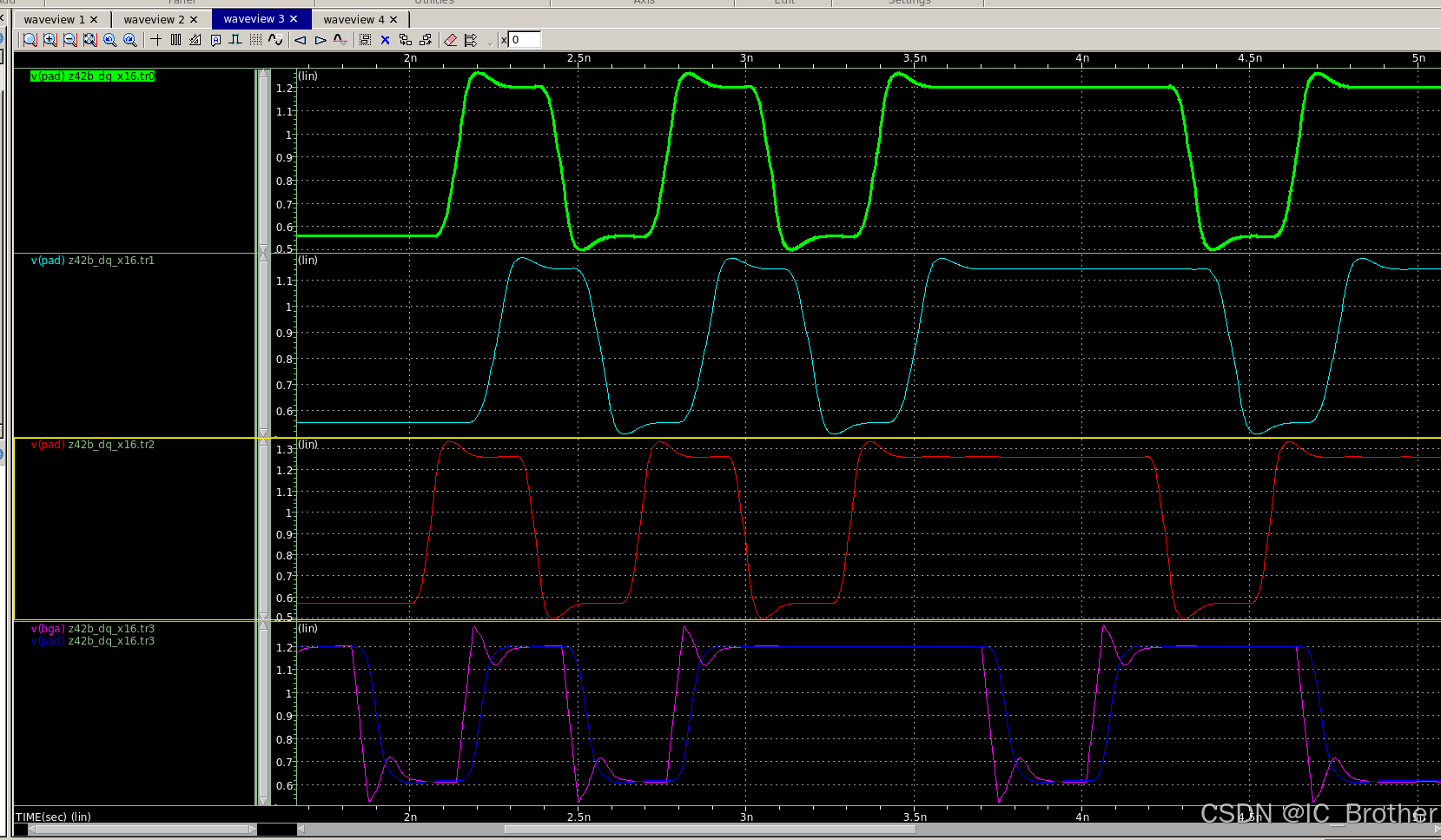

3)DDR4 IBIS model sim

input

dqs

dq

自动化脚本

1)Makefile脚本

all: run_vcs cleanTIME_SCALE = -timescale=1ps/1ps## -cm line+cond+tgl+fsm+branch+assertrun_vcs:vcs -f ddr4_tb.f \${TIME_SCALE} -sverilog -full64 -debug_access +all -ignore all -R -fsdb +define+FSDB -l rpt/ddr4_tb.log \-lca -kdb -ntb_opts \+npspecify \-reportstats -l rpt/ddr4_tb.rpt \-cm line+cond+fsm+branch+assertrun:vcs -f ddr4_tb.f \${TIME_SCALE} -sverilog -v2005 -full64 -ignore all -R -gui -l rpt/ddr4_tb.log \-reportstats -l rpt/ddr4_tb.rpt \run_verdi:verdi -ssf ddr4_tb.fsdb -f ddr4_tb.f -sv &cov:verdi -cov -covdir simv.vdb/ &clean:rm -rf csrc DVEfiles simv* *.vpd simv *.key novas* verdi* *.log vc_hdrs.h vdCovLog *.fsdb *.vector2)Python自动化脚本

通过python3获取pattern list,并行仿真后,收集仿真结果,部分示例如下。

pattern.list(部分)

依次为pattern name,DDR4 cfg,Speed

basic001_act_wr_rd_pre,DDR4_2G_X4,TS_1250

basic001_act_wr_rd_pre,DDR4_2G_X4,TS_1072

basic001_act_wr_rd_pre,DDR4_2G_X4,TS_938

basic001_act_wr_rd_pre,DDR4_2G_X4,TS_833

basic001_act_wr_rd_pre,DDR4_2G_X4,TS_750

basic001_act_wr_rd_pre,DDR4_2G_X4,TS_682

basic001_act_wr_rd_pre,DDR4_2G_X4,TS_625

sim.log(部分)

Log Timestamp: 2024-10-07 21:51:59

Total Count: 588

Total Pass: 588

Total Fail: 0

=================================================================

basic001_act_wr_rd_pre_DDR4_2G_X4_TS_1250 : Pass

basic001_act_wr_rd_pre_DDR4_2G_X4_TS_1072 : Pass

basic001_act_wr_rd_pre_DDR4_2G_X4_TS_938 : Pass

basic001_act_wr_rd_pre_DDR4_2G_X4_TS_833 : Pass

basic001_act_wr_rd_pre_DDR4_2G_X4_TS_750 : Pass

basic001_act_wr_rd_pre_DDR4_2G_X4_TS_682 : Pass

basic001_act_wr_rd_pre_DDR4_2G_X4_TS_625 : Pass

basic001_act_wr_rd_pre_DDR4_2G_X8_TS_1250 : Pass

basic001_act_wr_rd_pre_DDR4_2G_X8_TS_1072 : Pass

项目难度:⭐⭐⭐⭐⭐

项目推荐度:⭐⭐⭐⭐

项目推荐天数:28~35天

项目简介和资料

1)项目简介

本项目基于JEDEC JESD79-4 标准,完成了DDR4控制器接口的架构规划、RTL设计以及基础功能验证。整个项目分为两个主要部分:

1)基于Micron DDR4 仿真模型搭建基本DDR4协议初始化、Act、Write、Read等基础操作,帮助学习DDR4关键时序参数,快速了解DDR4 Spec,覆盖1600~3200Mbps、2 ~16G、X4/X8/X16全Spec应用场景。

2)使用System Verilog设计和测试DDR4控制器及高速接口。提供将命令、数据转换为DDR控制器和内存DDR4 DIMM使用的引脚信号电平,并在Testbench提供2Kb随机读写测试案例中用于验证DDR接口。

3)项目包含源文件、技术文档、Makefile脚本、Python脚本以及答疑,其中Python脚本支持一键搭建环境、VCS仿真、收集Report并汇总到日志文件。

4)项目还会额外提供丰富的DRAM基础资料,包含DDR4 Spec、DRAM电路设计教材、论文、专利等资料,对于有意向选择全定制存储的同学将会有一定帮助。

2)拓展资料

项目还额外提供DRAM设计相关资料,包含:

1)DRAM设计教材

2)DRAM设计论文及相关专利

3)16Gb DDR4 Hspice IBIS仿真模型及质量报告

软件环境要求

软件和EDA环境:

(1)操作系统:Centos

(2)EDA 软件:VCS-MX O-2018.09-1、Verdi_O-2018.09-SP2、HSPICE Version N-2017.12-SP2

(3)Python版本:Python 3.6.8

项目学习目的:

(1)熟练掌握复杂项目的工程管理;

(2)熟悉 Verilog HDL仿真以及Python自动化脚本工具;

(3)学习DRAM基本结构和基础原理;

(4)学习DDR4 Spec和基本时序参数;

(5)熟练掌握System Verilog语法和验证方法;

总结

整个项目涵盖了完整的DDR4控制器以及testbench设计,项目旨在设计和验证一个基于 SystemVerilog 的 DDR4 存储器模型和测试平台。项目核心包括:设计 DDR4 接口,构建模拟存储器的控制逻辑,创建测试平台(Testbench)进行功能、时序和性能验证。通过使用状态机来模拟命令和数据传输,利用 VIP 模块生成各种操作并进行协议检查,确保模型符合 DDR4 标准。在验证过程中,涵盖了读写操作、时序约束、性能测试等,确保最终验证环境全面、可靠。相对先前列出的开源和初级项目来说,整体难度偏高,适合缺少验证及高速接口相关项目经验的求职者。

特地注明:整个项目耗费较长的周期和个人精力,项目收费并且保证独一无二(性价比肯定是重要因素,毕竟都有过学生时代)。感兴趣的同学可以通过私信联系,我始终相信好的知识和项目肯定是收费的,网上也有很多类似的课程和项目,但大多数没有从完整的项目需求出发,代码和工程重复率高,不少同学往往是花了很多钱,却没有学到真正的东西。

相关文章:

数字IC实践项目(10)—基于System Verilog的DDR4 Model/Tb 及基础Verification IP的设计与验证(付费项目)

数字IC实践项目(10)—基于System Verilog的DDR4 Model/Tb 及基础Verification IP的设计与验证(付费项目) 前言项目框图1)DDR4 Verification IP2)DDR4 JEDEC Model & Tb 项目文件1)DDR4 Veri…...

MATLAB保存多帧图形为视频格式

基本思路 在Matlab中,要将drawnow绘制的多帧数据保存为视频格式,首先需要创建一个视频写入对象。这个对象用于将每一帧图像数据按照视频格式的要求进行组合和编码。然后,在每次drawnow更新绘图后,将当前的图形窗口内容捕获为一帧图…...

dict字典)

redis7.x源码分析:(3) dict字典

dict字典采用经典hash表数据结构实现,由键值对组成,类似于C中的unordered_map。两者在代码实现层面存在一些差异,比如gnustl的unordered_map分配的桶数组个数是(质数n),而dict分配的桶数组个数是࿰…...

连续九届EI稳定|江苏科技大学主办

【九届EI检索稳定|江苏科技大学主办 | IEEE出版 】 🎈【截稿倒计时】!!! ✨徐秘书:gsra_huang ✨往届均已检索,已上线IEEE官网 🎊第九届清洁能源与发电技术国际学术会议(CEPGT 2…...

HarmonyOS NEXT应用开发实战 ( 应用的签名、打包上架,各种证书详解)

前言 没经历过的童鞋,首次对HarmonyOS的应用签名打包上架可能感觉繁琐。需要各种秘钥证书生成和申请,混在一起也分不清。其实搞清楚后也就那会事,各个文件都有它存在的作用。 HarmonyOS通过数字证书与Profile文件等签名信息来保证鸿蒙应用/…...

【CICD】CICD 持续集成与持续交付在测试中的应用

一、什么是CICD? CI/CD 是指持续集成(Continuous Integration)和持续部署(Continuous Deployment)或持续交付(Continuous Delivery) 1.1 持续集成(Continuous Integration…...

Dolby TrueHD和Dolby Digital Plus (E-AC-3)编码介绍

文章目录 1. Dolby TrueHD特点总结 2. Dolby Digital Plus (E-AC-3)特点总结 Dolby TrueHD 与 Dolby Digital Plus (E-AC-3) 的对比 Dolby TrueHD和Dolby Digital Plus (E-AC-3) 是两种高级的杜比音频编码格式,常用于蓝光影碟、流媒体、影院等高品质音频传输场景。它…...

数字频率计的设计-- 基于 HDL 方法

目录 数字频率计的设计 1.计数、锁存与显示译码电路设计 2.主控电路设计 3.分频电路设计 4.顶层电路设计 伪随机序列发生器 的设计 数字频率计的设计 基于HDL设计数字系统时,可以根据需要应用Verilog HDL描述所需要的功能电路,既有利于节约资源&am…...

[程序员] 没有产生core文件的原因

最近和同事一块看一个core文件没有产生的问题,总结了一些在CSDN的专栏里。分析的过程,参考使用了ftrace的功能,感觉非常实用。 如果有需要可以参考。大体上就这么几种情况:信号的特殊处理,coredump相关的配置没有设置正确,文件系统访问权限问题,setuid相关的不匹配问题。…...

【数字图像处理+MATLAB】基于 Sobel 算子计算图像梯度并进行边缘增强:使用 imgradientxy 函数

引言 在图像处理中,边缘通常是图像中像素强度变化最大的地方,这种变化可以通过计算图像的梯度来量化。梯度是一个向量,它的方向指向像素强度增加最快的方向,它的大小(或者说幅度)表示像素强度增加的速度。…...

P10901 [蓝桥杯 2024 省 C] 封闭图形个数

铁子们好呀,今天博主给大家更新一道编程题!!! 题目链接如下: P10901 [蓝桥杯 2024 省 C] 封闭图形个数 好,接下来,我将从三个方面讲解这道例题。分别是 题目解析算法原理代码实现 文章目录 1.题…...

ubuntu-desktop-24.04上手指南(更新阿里源、安装ssh、安装chrome、设置固定IP、安装搜狗输入法)

ubuntu-desktop-24.04上手指南(更新阿里源、安装ssh、安装chrome、设置固定IP、安装搜狗输入法) 一、更新并安装基础软件 #切换root用户 sudo su -#更新 apt update #升级 apt upgrade#install vim apt install vim#install net-tools apt install net-tools二、安装ssh并设置…...

手机直连卫星NTN通信初步研究

目录 1、手机直连卫星之序幕 2、卫星NTN及其网络架构 2.1 NTN 2.2 NTN网络架构 3、NTN的3GPP标准化进程 3.1 NTN需要适应的特性 3.2 NTN频段 3.3 NTN的3GPP标准化进程概况 3.4 NTN的3GPP标准化进程的详情 3.4.1 NR-NTN 3.4.1.1 NTN 的无线相关 SI/WI 3.4.1.2…...

蓝桥杯c++算法学习【2】之搜索与查找(九宫格、穿越雷区、迷宫与陷阱、扫地机器人:::非常典型的必刷例题!!!)

别忘了请点个赞收藏关注支持一下博主喵!!! 关注博主,更多蓝桥杯nice题目静待更新:) 搜索与查找 一、九宫格 【问题描述】 小明最近在教邻居家的小朋友小学奥数,而最近正好讲述到了三阶幻方这个部分,三 …...

Android加载pdf

依赖 implementation com.squareup.okhttp3:okhttp:4.9.1 implementation com.github.barteksc:android-pdf-viewer:3.2.0-beta.1在project.build中添加该源 maven { url "https://repository.liferay.com/nexus/content/repositories/public/" }XML <LinearLa…...

IOT物联网低代码可视化大屏解决方案汇总

目录 参考来源云服务商阿里云物联网平台产品主页产品文档 开源项目DGIOT | 轻量级工业物联网开源平台项目特点项目地址开源许可 IoTGateway | 基于.NET6的跨平台工业物联网网关项目特点项目地址开源许可 IoTSharp | 基于.Net Core开源的物联网基础平台项目特点项目地址开源许可…...

Python的面向对象day7

1、什么是面向对象 面向对象称为OO,他通过将数据和功能封装在一个被称为‘对象’的实体中,来组织和管理代码。面向对象变成(OOP)具有四个特性,封装、继承、多态、抽象 优点:模块化、安全性高、代码重用性…...

计算机网络(11)和流量控制补充

这一篇对数据链路层中的和流量控制进行详细学习 流量控制(Flow Control)是计算机网络中确保数据流平稳传输的技术,旨在防止数据发送方发送过多数据,导致接收方的缓冲区溢出,进而造成数据丢失或传输失败。流量控制通常…...

Rust 所有权机制

Rust 所有权机制 本文示例代码地址 所有权是Rust中最独特的特性,它让Rust无需GC就可以保证内存安全。 什么是所有权? 所有权(ownership)是 Rust 用于如何管理内存的一组规则。所有程序都必须管理其运行时使用计算机内存的方式…...

Pwn VM writeup

国赛期间,做了一个很有意思的pwn题,顺便学了一下现在常见的pwn的板子题是什么样子的,这里做一下记录 Magic VM 题目逻辑 题目本身其实非常的有趣,它实现了一个简易流水线的功能,程序中包含四个结构体,其中三…...

PG数据库空间查询添加空间索引后提速10倍

以下语句直接在Navicat软件中链接PG数据库后实现 添加空间索引之前查询第一次要10几秒,添加空间索引之后不到1秒 -- 创建支持 UTM 32650 投影查询的空间索引 CREATE INDEX idx_fjdmdz_geom_32650 ON tablename USING GIST (ST_Transform(geom, 32650));SELECT * FROM tabl…...

树莓派4B内存分配翻车实录:给GPU 512MB导致libcamera拍照报错‘内存不足’?

树莓派4B内存分配陷阱:GPU设置如何影响libcamera性能 树莓派4B作为一款功能强大的单板计算机,其8GB内存版本尤其受到开发者和创客的青睐。然而,许多用户在尝试使用libcamera进行高性能图像捕获时,会遇到一个令人困惑的问题&#x…...

的设计思路复用)

从游戏UI到工业HMI:聊聊Qt自定义控件(仪表盘、雷达、摇杆)的设计思路复用

从游戏UI到工业HMI:Qt自定义控件的跨领域设计思维 在数字界面设计领域,游戏UI与工业HMI看似分属两个极端——前者追求炫酷动效与沉浸体验,后者强调信息清晰与操作可靠。但当我们拆解那些优秀的仪表盘、雷达扫描和交互摇杆控件时,会…...

)

Cadence ADE保姆级教程:手把手教你用S参数文件提取变压器QLk指标(附完整公式)

Cadence ADE实战指南:从S参数文件到变压器QLk指标的全流程解析 在射频集成电路设计中,变压器作为关键无源器件,其性能直接影响整个系统的效率与稳定性。QLk指标(品质因数Q、电感值L和耦合系数k)的准确提取,…...

)

别急着加内存!PyTorch报错‘DefaultCPUAllocator: not enough memory’的另类解法(附一键修复脚本)

别急着加内存!PyTorch报错‘DefaultCPUAllocator: not enough memory’的另类解法 当你看到PyTorch抛出RuntimeError: DefaultCPUAllocator: not enough memory时,第一反应可能是检查任务管理器——然后发现物理内存明明还剩大半,这个报错就显…...

【数据库】PostgreSQL实战:从基础到高级特性

【数据库】PostgreSQL实战:从基础到高级特性 引言 PostgreSQL是一个功能强大的开源关系型数据库,以其可靠性、扩展性和丰富的特性而闻名。本文将详细介绍PostgreSQL的核心特性、SQL操作和高级功能。 一、基础概念 1.1 数据库对象 -- 创建数据库 CREATE D…...

量化感知训练中的权重震荡:成因、影响与抑制策略

1. 量化感知训练中的“震荡”现象:一个被忽视的优化陷阱在将神经网络模型部署到手机、摄像头、嵌入式芯片这类资源受限的边缘设备时,量化几乎是必经之路。简单说,量化就是把模型里那些动辄32位的浮点数权重和激活值,压缩成8位、4位…...

2026年六大主流AI变声器软件排名推荐!

随着AI语音技术持续迭代升级,AI变声器不再是单一的娱乐工具,广泛应用于游戏开黑、直播互动、短视频配音、音频创作、隐私语音沟通等多个场景。目前市面上变声软件品类繁杂,涵盖移动端、PC端、免费开源、专业付费等不同类型,普通用…...

车标识别平台

车标识别平台选题背景分析随着全球汽车产业的蓬勃发展以及智能交通系统(ITS)的加速建设,车标识别技术作为计算机视觉与人工智能领域的重要应用分支,其市场需求与技术价值日益凸显。开发一个高效、精准的车标识别平台,其…...

YOLOv11厨房食材目标检测数据集-2499张-Meat-1_5

YOLOv11厨房食材目标检测数据集 📊 数据集基本信息 目标类别: [‘ayam’, ‘beef’, ‘pork’]中文类别:[‘鸡肉’, ‘牛肉’, ‘猪肉’]训练集:2256 张验证集:164 张测试集:79 张总计:2499 张 …...