Xilinx 7 系列 FPGA的各引脚外围电路接法

Xilinx 7系列FPGA的外围电路接法涉及到多个方面,包括电源引脚、时钟输入引脚、FPGA配置引脚、JTAG调试引脚,以及其他辅助引脚。

本文参考资料:

ds180 - 7 Series FPGAs Data Sheet - Overview

ds181 - Artix 7 FPGAs Data Sheet - DC and AC Switching Characteristics

ug470 - User Guide - 7 Series FPGAs Configuration

ug472 - User Guide - 7 Series FPGAs Clocking Resources

ug480 - User Guide - 7 Series FPGAs XADC Dual 12-Bit 1 MSPS Analog-to-Digital Converter

ug475 - Product Specification - 7 Series FPGAs Packaging and Pinout

xapp1084 - Developing Tamper Resistant Designs with Xilinx Virtex-6 and 7 Series FPGAs

xapp586 - Using SPI Flash with 7 Series FPGAs

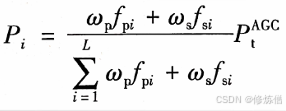

专用配置Bank(Bank0)包含如下引脚:

当使用SPIx4模式时,参考的连接图如下:

M0_0, M1_0, M2_0

Configuration mode selection

M[2:0] determine the configuration mode. Connect each mode pin either directly, or via a ≤ 1kΩ resistor, to VCCO_0 or GND.

配置模式选择脚。根据设计的配置模式,可通过小电阻或直接接至VCCO_0或GND。内部有上拉电阻,因此默认设置为Slave Serial模式(M[2:0]=111)

通常的FPGA开发板均使用了Master SPI模式,外挂一颗SPI接口的NOR Flash芯片。

具体选项如下:

(其他模式的用法可参阅ug470,本文仅介绍Master SPI模式,即外挂SPI NOR Flash的用法)

M[2:0]=000

Master Serial模式

M[2:0]=001

Master SPI模式(具体的x1, x2, x4由存储在SPI Flash内的详细配置信息决定)

M[2:0]=010

Master BPI模式

M[2:0]=011

未定义

M[2:0]=100

Master SelectMAP模式

M[2:0]=101

仅JTAG模式

M[2:0]=110

Slave SelectMAP模式

M[2:0]=111

Slave Serial模式

TDO_0, TCK_0, TMS_0, TDI_0

JTAG引脚。可以外接JTAG调试器,可以通过JTAG接口进行FPGA配置或进行SPI间接烧录。

这四个引脚可以直接引出,输入端口已经内置上拉。

例如最常用的是基于FTDI的FT232HL芯片的jtag-smt2-nc兼容版方案。

常见的两种JTAG插座的线序分别如下

(有凸起的是插座,有缺口的是插座,均为正视图)

2x5简牛JTAG座(2.0mm或2.54mm间距的都常见,Altera的CPLD/FPGA板子也常用这个线序)

2x7简牛JTAG座(常见2.0mm间距的)

注:这里的VREF脚需要连接至VCCO_0。该脚将会连接到JTAG调试器上的电平转换芯片上,为电平转换芯片提供FPGA端的IO电平参考

CFGBVS_0

The configuration banks voltage select pin (CFGBVS) must be set to a High (VCCO_0) or Low (GND) to set the configuration and JTAG I/O in banks 0, 14, and 15 for 3.3V/2.5V or 1.8V/1.5V operation, respectively. When CFGBVS is set to Low for 1.8V/1.5V I/O operation, the VCCO_0 supply and I/O signals to bank 0 must be 1.8V (or lower) to avoid device damage. If CFGBVS is Low, then any I/O pins used for configuration in banks 14 and 15 must also be powered and operated at 1.8V or 1.5V.

Bank0、14、15上的专用/复用配置I/O工作在3.3V/2.5V时,CFGBVS_0需要拉高,接VCCO_0。

Bank0、14、15上的专用/复用配置I/O工作在1.8V/1.5V时,CFGBVS_0需要拉低,接GND。

D00_MOSI, D01_DIN, D02, D03, FCS_B, CCLK_0

FCS_B: Active-Low chip select output that enables SPI or BPI flash devices for configuration. For SPI and BPI modes: Connect the FPGAFCS_B to the flash device chip-select input and connect to an external ≤ 4.7kΩ pull-up resistor to VCCO_14.

配置模式为Master SPI x4模式时,用于外接SPI Flash的引脚。

以winbond的SPI NOR Flash(型号如W25Q32, W25Q128, W25Q256等)为例,则将这六个引脚依次连接至IO0, IO1, IO2, IO3, CS, CLK。

其中D00_MOSI, D01_DIN, D02, D03, FCS_B属于FPGA的Bank 14,而CCLK_0属于Bank 0,因此Master SPI模式下应确保Bank14与Bank0采用相同的IO供电电压。

推荐设计要求在IO2, IO3, CS这三个脚加了上拉电阻。不确定是否必须要加。

为了避免CLK引脚走线的寄生电感引起CLK线的振铃,导致时钟错乱,建议在CLK走线上串联一个小电阻(10~30Ω)。

注意:Bank14有一个名为DOUT的引脚,该脚并不是用于连接SPI Flash的引脚,应当与MOSI区别开,切勿混淆!

关于SPI Flash容量的选取,ug470文档中给出了表格“Bitstream Length”,列出了全部7系列FPGA的SPI Flash最大容量需求。芯片规模越大,可能生成的最大Bitstram越大,需要的Flash容量也会越大。

常见FPGA型号的Flash容量要求如下(选用的Flash芯片可大于该容量,但如果小于该容量,则会有容量不足的风险)

7S15,8Mb

7A35T,32Mb

7A100T,32Mb

7A200T,128Mb

7K70T,32Mb

7K325T,128Mb

7K410T,128Mb

PUDC_B

Active-Low PUDC_B input enables internal pull-up resistors on the SelectIO pins after power-up and during configuration.

When PUDC_B is Low, internal pull-up resistors are enabled on each SelectIO pin.

When PUDC_B is High, internal pull-up resistors are disabled on each SelectIO pin.

PUDC_B must be tied either directly or via a 1 kΩ or less resistor to VCCO_14 or GND. When PUDC_B is tied to GND, the activation of internal pull-ups during power-on depends on the power sequence because the PUDC_B control signal is forwarded through an input buffer in bank 14 and internal paths to the enables of internal pull-ups at applicable pins in their respective I/O banks. An external pull-up resistor is recommended between a pin and the pin’s VCCO power supply when it is critical for the pin to be pulled High immediately as the pin’s VCCO power ramps up.

控制全部普通FPGA IO(与配置无关的IO?)在上电配置阶段的状态。(配置完成后,IO状态由bitstream里的设定控制)

如果拉低,芯片在上电配置阶段,所有IO将处于内部弱上拉状态。

如果拉低,芯片在上电配置阶段,所有IO将处于高阻状态。

该引脚位于Bank14,要求不能悬空,但是大多数开发板均未将该脚合理连接。

EMCCLK

当bitstream被配置为使用外部时钟时(BITSTREAM.CONFIG.EXTMASTERCCLK_EN),该引脚用于输入一个不高于100MHz的外部时钟。外部时钟可以提供更加准确的时钟频率,从而允许使用更快地SPI配置时钟。内部时钟的误差标称值为±50%,因此SPI频率最高可能达到设定值的150%,有可能超出SPI Flash的最大频率。为确保可靠地完成配置,需要计算确定较低的SPI配置频率(在bitstram中设定)。SPI初始化阶段的配置时钟频率为3MHz,较为保守。

如未设置BITSTREAM.CONFIG.EXTMASTERCCLK_EN,则该引脚在配置阶段不会被使用

该引脚位于Bank14。

PROGRAM_B_0

Active-Low reset to configuration logic. When PROGRAM_B is pulsed Low, the FPGA configuration is cleared and a new configuration sequence is initiated. Configuration reset initiated upon falling edge, and configuration (i.e. programming) sequence begins upon the following rising edge.

Connect PROGRAM_B to an external ≤ 4.7kΩ pull-up resistor to VCCO_0 to ensure a stable High input, and recommend push-button to GND to enable manual configuration reset.

Holding PROGRAM_B Low from power-on does not keep the FPGA configuration in reset. Instead, use INIT_B to delay the power-on configuration sequence.

FPGA配置逻辑的异步复位引脚,低电平有效。常用做FPGA开发板的复位按键,下降沿将会清除FPGA内的现有配置,上升沿将开始新的配置。外部配置器件重新载入配置信息。如不使用,可接高至VCCO_0。如使用,可接一个上拉电阻到VCCO_0,并接一个按钮到GND。

一个例外是,上电保持该引脚低电平,并不会使FPGA保持复位状态,而是仍会完成配置。上电后再操作该引脚才有用。如需在上电时保持FPGA未配置,需通过INIT_B引脚实现。

DONE_0

DONE indicates successful completion of configuration (active High)

FPGA成功完成配置后,将输出高电平。如有任何错误,将会保持低电平。常用于外接一个指示灯,指示FPGA已完成配置。

这是一个内置10k上拉电阻的开漏输出口,因此如需外接的LED指示灯产生足够的亮度,需要外加强上拉电阻。

INIT_B_0

Active-Low FPGA initialization pin or configuration error signal. The FPGA drives this pin Low when the FPGA is in a configuration reset state, when the FPGA is initializing (clearing) its configuration memory, or when the FPGA has detected a configuration error. Upon completing the FPGA initialization process, INIT_B is released to high-Z at which time an external resistor is expected to pull INIT_B High. INIT_B can externally be held Low during power-up to stall the power-on configuration sequence at the end of the initialization process. When a High is detected at the INIT_B input after the initialization process, the FPGA proceeds with the remainder of the configuration sequence dictated by the M[2:0] pin settings.

Connect INIT_B to a ≤ 4.7 kΩ pull-up resistor to VCCO_0 to ensure clean Low-to-High transitions.

配置错误信号(上电初始化阶段用做开漏输出),初始化控制脚(上电初始化完成后用做高阻输入)

当FPGA处于配置复位状态、FPGA初始化(清除)其配置内存或FPGA检测到配置错误时,FPGA将驱动该引脚为低电平。

如外部将该引脚拉低,则会在在上电初始化完成后,暂停FPGA配置,直至检测到高电平。

需要外接一个上拉电阻到VCCO_0,以确保初始化后可以自动开始配置。也可外接RC延时网络或按钮、拨码开关等器件,延迟或暂停FPGA配置流程。

DXP_0, DXN_0

Temperature-sensing diode pins (Anode: DXP; Cathode: DXN). The thermal diode is accessed by using the DXP and DXN pins in bank 0. When not used, tie to GND. To use the thermal diode an appropriate external thermal monitoring IC must be added. Consult the external thermal monitoring IC data sheet for usage guidelines. The recommended temperature monitoring solution for 7series FPGAs uses the temperature sensor in the XADC block.

这些引脚用于访问FPGA内部的热二极管,以便进行温度监测。可以搭配MAX6628等芯片,从FPGA外部监控其温度。如不使用,可接地。

VCCBATT_0

VCCBATT is the battery backup supply for the FPGA’s internal volatile memory that stores the key for the AES decryptor. For encrypted bitstreams that require the decryptor key from the volatile key memory area, connect this pin to a battery to preserve the key when the FPGA is unpowered. If there is no requirement to use the decryptor key from the volatile key storage area, connect this pin to GND or VCCAUX. The pin name includes the “_0” bank designation but it is not an I/O and not affected by VCCO_0.

当使用加密bitstream时,可将bitstream的AES密钥存储在Decryptor key memory区域中(另一种方法是永久存储密钥至FPGA片内的eFuse,该方法无需电池,更多信息可参阅应用笔记xapp1084)。该引脚可接一个1.89V以下电压的电池(也就是1.5V或1.55V纽扣电池),确保AES密钥数据完整。一旦VCCBATT_0掉电,外部SPI Flash里的加密bitstream将再也无法被FPGA芯片加载,有效地确保了FPGA设计资料不被窃取。

该引脚最大电流仅为150nA,一颗160mAh的LR44氧化银纽扣电池可供其使用长达125年(电池的使用寿命通常没这么久)。

如不使用该特性,可接至VCCAUX(1.8V)或GND。

GNDADC_0, VCCADC_0

XADC analog supply voltage

XADC模块的电源。要求接至1.8V电源,建议通过滤波网络连接至VCCAUX电源,以取得更好的ADC性能。

超过2.0V将会损坏芯片。

VREFN_0, VREFP_0

1.25V reference input

XADC模块的1.25基准电压输入。如有高精度测量需求(精度±0.2%),可外接高精度1.25V电压基准芯片。否则可全部接GND,此时XADC模块将会启用内部基准源(精度±1%)。关于XADC模块的详情可参阅ug480。

VN_0, VP_0

片内XADC的一对差分输入通道。这两个引脚是专用的XADC输入通道,在Bank15和Bank35还有很多与IO共享的XADC输入通道。

每个XADC输入通道在差分模式下使用要求0V<=Vn<=1.0V且0V<=Vp<=1.0V,Vp-Vn=1.0V对应最大测量值,Vn-Vp=1.0V对应最小测量值;

如果按单端模式使用,则Vn=0V,0V<=Vp<=1.0V,Vp=1.0V对应最大测量值,Vp=0V对应最小测量值。

VCCINT, VCCBRAM

对于无特殊注明的标准电压芯片,这两组引脚要接1.0V电源,推荐范围0.95V~1.05V,即浮动±5%

VCCAUX

对于无特殊注明的标准电压芯片,这组引脚要接1.8V电源,推荐范围1.71V~1.89V,即浮动±5%

VCCO_0, VCCO_14, VCCO_15, VCCO_16, VCCO_34, VCCO_35等

首先需要确定每个Bank是HR还是HP的Bank

HR即为High range,高电压,最低支持1.2V电平标准,最高支持3.3V电平标准,耐压3.6V

HP即为High Performance,高性能,最低支持1.2V电平标准,最高支持1.8V电平标准,耐压2.0V

即IO耐压最高可超过标准电压的10%

注:

Spartan-7或者Artix-7这两个系列,全部IO Bank都是HR Bank

Kintex-7和Virtex-7这两个较为高端的FPGA系列,同时有HR和HP两种Bank

MGTAVCC, MGTAVTT, MGTVCCAUX

GTX收发器的三路电源,如不使用,可以全部接地。

MRCC, SRCC

MRCC即Multi-region clock-capable I/O,适合与片外时钟信号(如有源晶振)连接。因为MRCC可以直接通过片内资源连接至BUFG,从而提供片内全局时钟。性能最好。

SRCC即Single-region clock-capable I/O。

VREF

每个Bank均有一个IO复用为VREF脚。

当IO设定为使用HSTL, HSUL, SSTL等电平标准时,VREF脚的输入电压将会用作输入高低电平的翻转点。

IO

其他所有IO均可在FPGA设计中作为普通IO使用。

相关文章:

Xilinx 7 系列 FPGA的各引脚外围电路接法

Xilinx 7系列FPGA的外围电路接法涉及到多个方面,包括电源引脚、时钟输入引脚、FPGA配置引脚、JTAG调试引脚,以及其他辅助引脚。 本文参考资料: ds180 - 7 Series FPGAs Data Sheet - Overview ds181 - Artix 7 FPGAs Data Sheet - DC and AC…...

基础 | 目标网站)

Python 爬虫 (1)基础 | 目标网站

一、目标网站 1、加密网站 1.1、关键字比较明确 企名片:https://wx.qmpsee.com/articleDetail?idfeef62bfdac45a94b9cd89aed5c235be 1.2、关键字比较泛 烯牛数据:https://www.xiniudata.com/project/event/lib/invest...

数字后端零基础入门系列 | Innovus零基础LAB学习Day11(Function ECO流程)

###LAB 20 Engineering Change Orders (ECO) 这个章节的学习目标是学习数字IC后端实现innovus中的一种做function eco的flow。对于初学者,如果前面的lab还没掌握好的,可以直接跳过这节内容。有时间的同学,可以熟悉掌握下这个flow。 数字后端…...

量子卷积神经网络

量子神经网络由量子卷积层、量子池化层和量子全连接层组成 量子卷积层和量子池化层交替放置,分别实现特征提取和特征降维,之后通过量子全连接层进行特征综合 量子卷积层、量子池化层和量子全连接层分别由量子卷积单元、量子池化单元和量子全连接单元组…...

储能电站构成及控制原理

系列文章目录 能量管理系统(EMS)储能充放电策略 文章目录 系列文章目录一、储能电站构成二、储能系统关键部件及作用1.电池储能系统2.功率变换系统(Power Conversion System,PCS)3.变配电系统4.后台监控系统5.继电保护及安全自动装置 三、储能电站的功能四、储能电站控制策略 …...

Rocky Linux 系统安装/部署 Docker

1、下载docker-ce的repo文件 [rootlocalhost ~]# curl https://download.docker.com/linux/centos/docker-ce.repo -o /etc/yum.repos.d/docker.repo % Total % Received % Xferd Average Speed Time Time Time Current Dloa…...

12 —— Webpack中向前端注入环境变量

需求:开发模式下打印语句生效,生产模式下打印语句失效 使用Webpack内置的DefinePlugin插件 const webpack require(webpack) module.exports { plugins: [ new webpack.DefinePlugin({ process.env.NODE_ENV:JSON.stringify(process.env.NODE_ENV) }…...

uniapp接入BMapGL百度地图

下面代码兼容安卓APP和H5 百度地图官网:控制台 | 百度地图开放平台 应用类别选择《浏览器端》 /utils/map.js 需要设置你自己的key export function myBMapGL1() {return new Promise(function(resolve, reject) {if (typeof window.initMyBMapGL1 function) {r…...

外卖系统开发实战:从架构设计到代码实现

开发一套外卖系统,需要在架构设计、技术选型以及核心功能开发等方面下功夫。这篇文章将通过代码实例,展示如何构建一个基础的外卖系统,从需求梳理到核心模块的实现,帮助你快速掌握开发要点。 一、系统架构设计 一个完整的外卖系…...

神经网络反向传播算法公式推导

要推导反向传播算法,并了解每一层的参数梯度如何计算,以及每一层的梯度受到哪些值的影响,我们使用一个简单的神经网络结构: 输入层有2个节点一个有2个节点的隐藏层,激活函数是ReLU一个输出节点,激活函数是…...

Spark SQL 之 QueryStage

ExchangeQueryStageExec ExchangeQueryStageExec 分为两种...

【shodan】(三)vnc漏洞利用

shodan基础(三) 声明:该笔记为up主 泷羽的课程笔记,本节链接指路。 警告:本教程仅作学习用途,若有用于非法行为的,概不负责。 count count命令起到一个统计计数的作用。 用上节的漏洞指纹来试…...

每日OJ_牛客_游游的字母串_枚举_C++_Java

目录 牛客_游游的字母串_枚举 题目解析 C代码 Java代码 牛客_游游的字母串_枚举 游游的字母串 描述: 对于一个小写字母而言,游游可以通过一次操作把这个字母变成相邻的字母。a和b相邻,b和c相邻,以此类推。特殊的࿰…...

51c深度学习~合集8

我自己的原文哦~ https://blog.51cto.com/whaosoft/12491632 #patchmix 近期中南大学的几位研究者做了一项对比学习方面的工作——「Inter-Instance Similarity Modeling for Contrastive Learning」,主要用于解决现有对比学习方法在训练过程中忽略样本间相似关系…...

嵌入式:Flash的分类以及Jlink/J-flash的编程支持

相关阅读 嵌入式https://blog.csdn.net/weixin_45791458/category_12768532.html?spm1001.2014.3001.5482 常见的Flash大致可以分为以下大类: Serial Nor FlashSerial Nand FlashParallel Nor FlashParallel Nand FlashSerial EEPROM Serial Nor Flash 介绍 Se…...

【爬虫】Firecrawl对京东热卖网信息爬取(仅供学习)

项目地址 GitHub - mendableai/firecrawl: 🔥 Turn entire websites into LLM-ready markdown or structured data. Scrape, crawl and extract with a single API. Firecrawl更多是使用在LLM大模型知识库的构建,是大模型数据准备中的一环(在…...

遗传算法(Genetic Algorithm, GA)

简介 遗传算法(Genetic Algorithm, GA)是一种基于自然选择和遗传机制的优化算法,由 John Holland 于20世纪70年代提出。它是一种模拟生物进化过程的启发式搜索算法,被广泛应用于函数优化、机器学习、调度问题等领域。 代码说明 …...

【二分答案+倍增快速幂】课堂练习

P1678 烦恼的高考志愿 #include<bits/stdc.h> using namespace std; const int N1e55; int n,m,a[N];long long bs(int x){int l1,rn;while(l<r){int midlr>>1;if(a[mid]x) return 0;if(a[mid]>x) rmid-1;else lmid1;}//根据前驱后继返回最小差值//printf(&…...

LeetCode 力扣 热题 100道(九)反转链表(C++)

给你单链表的头节点 head ,请你反转链表,并返回反转后的链表。 方法一:迭代法 /*** Definition for singly-linked list.* struct ListNode {* int val;* ListNode *next;* ListNode() : val(0), next(nullptr) {}* ListNod…...

Linux之网络基础

网络发展 网络的发展可以从人与人之间的工作模式开始谈起, 人与人的工作模式反应了机器与机器的工作模式: 1. 独立模式: 在网络发展的早期计算机间处于独立模式, 计算机之间相互独立 最开始计算机之间是独立运行的, 数据之间的交互需要人用软盘等存储介质拷贝过去, 一般涉及…...

【Python】安装 Python 环境

需要安装的环境主要是两个部分: 运行环境:Python开发环境:PyCharm 一、安装 Python 1、找到官方网站 Welcome to Python.org 2、找到下载页面 选择 "Download for Windows": 现在主流使用的 Python 版本是 Python…...

AntimicroX完全指南:游戏手柄映射的艺术与科学

AntimicroX完全指南:游戏手柄映射的艺术与科学 【免费下载链接】antimicrox Graphical program used to map keyboard buttons and mouse controls to a gamepad. Useful for playing games with no gamepad support. 项目地址: https://gitcode.com/GitHub_Trend…...

信创协同办公价格与成本:这样选,性价比直接拉满!

“一套信创协同办公到底多少钱?”“是按人头收费,还是按项目打包算?”“前期买着便宜,后期维护会不会无底洞?”不管是政企单位采购,还是企业选型,这三个问题几乎是所有人的核心顾虑。毕竟信创办…...

基于鲸鱼优化算法改进XGBoost在MATLAB中的时间序列预测性能(迭代次数、最大深度和学习...

基于鲸鱼优化算法优化XGBoost(WOA-XGBoost)的时间序列预测 WOA-XGBoost时间序列 采用交叉验证抑制过拟合问题 优化参数为迭代次数、最大深度和学习率 matlab代码,注:暂无Matlab版本要求 -- 推荐 2016B 版本及以上 注:采用 XGBoost 工具箱&…...

Cursor Composer 2 技术报告拆解:MoE 预训练、RL 环境设计与 CursorBench 基准的工程实践

在生产级代码仓库里,一个 AI Agent 面对的往往不是“实现某个功能”这样清晰的任务,而是“新特性上线后出现诡异 bug,日志里只有 954 个 JSON 响应,栈踪迹完全不可靠”。它必须自己跨文件定位、写启发式检测器、调参避免误报&…...

)

保姆级避坑指南:在CentOS 7上手动部署MySQL 8.0二进制包(附systemd服务配置)

CentOS 7手动部署MySQL 8.0二进制包的深度避坑指南 在Linux服务器上手动部署MySQL数据库是每个运维工程师的必修课。不同于常见的yum或apt安装方式,二进制包部署能让你更深入地理解MySQL的运行机制,同时获得更灵活的控制权。但这条路并不平坦,…...

【深度解析】用 Superpowers 改造 AI 编码代理:从“快手实习生”到“有流程的工程师”

摘要 本文从 Superpowers 开源项目出发,拆解它背后的「AI 软件开发方法论」:如何通过技能(Skills)、子代理(Sub-agents)、规则(Rules)和 Git 工作流,让 AI 编码代理不再只…...

如何快速掌握MelonLoader:从零基础到精通Unity游戏模组加载的完整教程

如何快速掌握MelonLoader:从零基础到精通Unity游戏模组加载的完整教程 【免费下载链接】MelonLoader The Worlds First Universal Mod Loader for Unity Games compatible with both Il2Cpp and Mono 项目地址: https://gitcode.com/gh_mirrors/me/MelonLoader …...

如何通过WeChatMsg实现微信聊天记录永久保存:从数据安全到情感记忆的完整解决方案

如何通过WeChatMsg实现微信聊天记录永久保存:从数据安全到情感记忆的完整解决方案 【免费下载链接】WeChatMsg 提取微信聊天记录,将其导出成HTML、Word、CSV文档永久保存,对聊天记录进行分析生成年度聊天报告 项目地址: https://gitcode.co…...

5分钟快速上手LosslessCut:零编码视频剪辑的终极指南

5分钟快速上手LosslessCut:零编码视频剪辑的终极指南 【免费下载链接】lossless-cut The swiss army knife of lossless video/audio editing 项目地址: https://gitcode.com/gh_mirrors/lo/lossless-cut 你是否曾因视频剪辑导致画质下降而烦恼?是…...