FPGA Xilinx维特比译码器实现卷积码译码

FPGA Xilinx维特比译码器实现卷积码译码

文章目录

- FPGA Xilinx维特比译码器实现卷积码译码

- 1 Xilinx维特比译码器实现

- 2 完整代码

- 3 仿真结果

MATLAB (n,k,m)卷积码原理及仿真代码(你值得拥有)_matlab仿真后代码-CSDN博客

MATLAB 仿真实现任意(n,k,m)卷积码译码_维特比译码matlab-CSDN博客

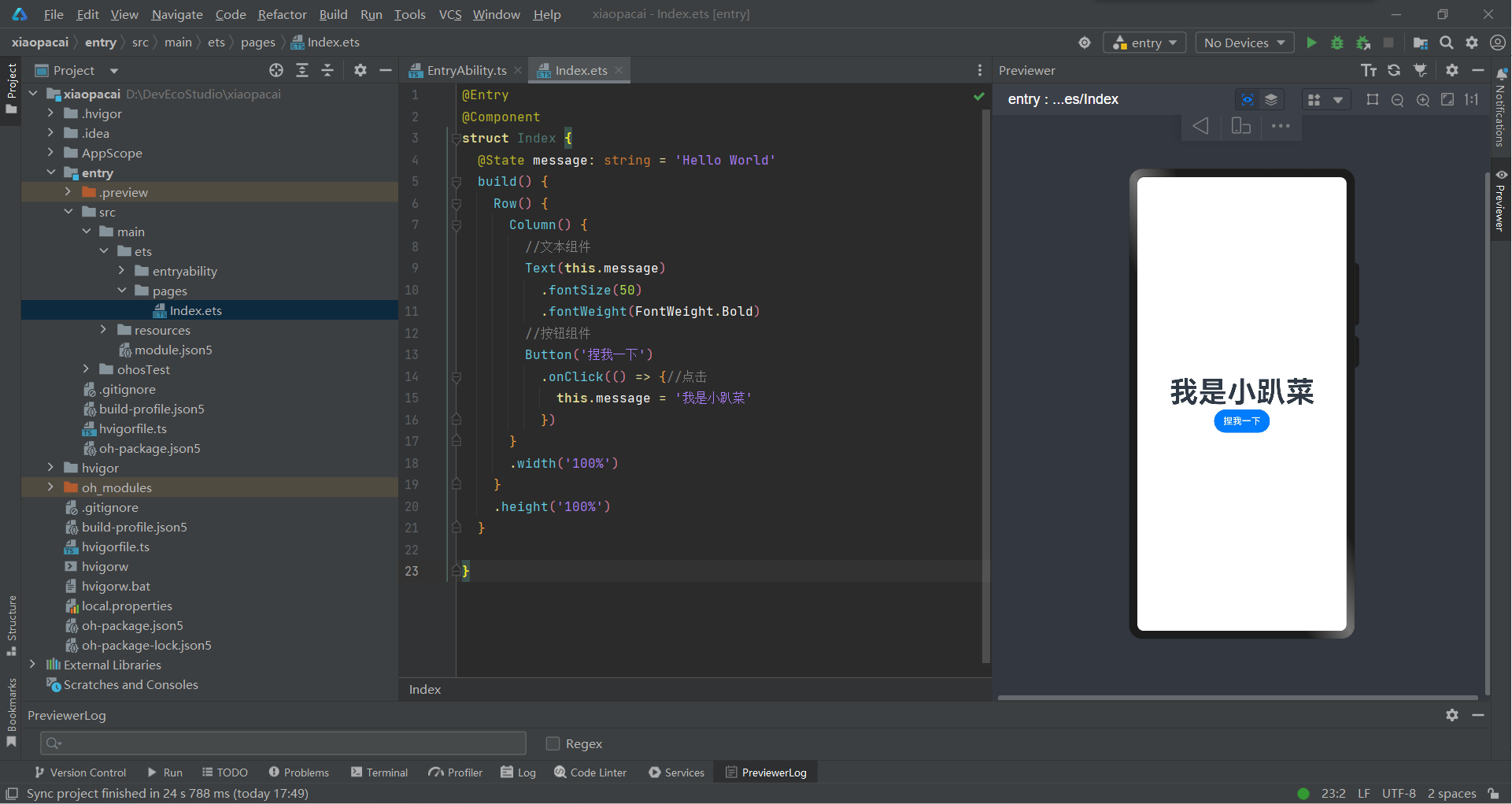

前面已经使用MATLAB实现了卷积码和译码,前段时间也在项目中实现了Xilinx中维特比译码器,这次就简单介绍一下这个译码器,从项目中把关于卷积码编译码的部分抽取出来 修改了一下,匆促实现了一下,还行。

1 Xilinx维特比译码器实现

首先找到Viterbi译码器 随便选一个

第一页 别管兄弟们 我也很多不懂什么意思,反正第一个就标准 Standard,第二个就回溯长度 ,兄弟们自己设置。

第二页 的第一个Best State 也不懂,用了之后会多几个看不懂的引脚 第二个Puncturing 好像那个是打孔的意思,我也没用到。第三个Coding是软硬编码的,我选择最简单的硬编码,直接输入0 1 就行了

第三页就是CC编码时的选项了,我编码使用的是1/2CC 然后对应的表达式分别为7 5,所以这里第一个就是2 代表两个输出码元,然后下面的代表的是表达式7 5

第四页第一个BER Options也没用到,用到了也会多几个引脚,没敢用

最后一页就是总结,大家注意上图中 左侧信息 “Implementation Details”

其中第一个DATA_IN_1(8:8) DATA_IN_1(0:0)意思是输入的比特第8位和第0位有效,到时候你只需要把输入的两比特放进这个变量里的第0位和第8位就行了。

DATA(0:0) 就代表每一次输出只有第0位是有效的,也就是一次输入一位 这一位就是第0位

2 完整代码

仿真文件

///

`timescale 1ns/1ps

module testbench_top();//参数定义`define CLK_PERIORD 10 //时钟周期设置为10ns(100MHz) //接口申明reg clk;

reg rst_n;

reg input_bit;

reg input_valid;wire [1:0] output_bits;

wire output_valid;reg enable;wire out_data;

wire outdata_valid;

wire over;reg o_data_end;// 对被测试的设计进行例化// 实例化待测试的卷积编码模块CC2 u_CC2( //二分之一码率 多项式 = 7,5.clk (clk), .rst (rst_n),.enable (enable), //使能信号 .sink_data (input_bit), //输入数据.sink_valid (input_valid), //数据有效信号.out_valid (output_valid), //输出数据有效信号.out_data (output_bits) //输出数据

);CC2_Decoding u_CC2_Decoding(.clk (clk),.rst (rst_n),.in_data_valid (output_valid), //进来的全是有效数据 直接全部放进译码器中.in_data (output_bits),.o_data_end (o_data_end),.over (over), //结束解码.out_data (out_data),.outdata_valid (outdata_valid)

);//复位和时钟产生//时钟和复位初始化、复位产生

initial beginclk <= 0;rst_n <= 0;#1000;rst_n <= 1;

end//时钟产生

always #(`CLK_PERIORD/2) clk = ~clk; integer file; // 文件句柄//测试激励产生

initial begin// 打开文件,写入模式file = $fopen("D:\\out_data.txt", "w");// 确保文件成功打开if (file == 0) begin$display("Error opening file!");$finish;endendalways @(posedge clk) beginif (outdata_valid) begin // 仅在数据有效时写入$fdisplay(file, "%d", out_data); // 将Ik写入文件end

endinitial begin@(posedge rst_n); //等待复位完成enable <= 1'b0;@(posedge clk);input_bit <= 1'b0;enable <= 1'b1;o_data_end <= 1'b0;@(posedge clk);repeat(8*16) begin //连续输入8 * 16 *4个bit@(posedge clk); input_bit <= 1'b1;input_valid <= 1'b1; //输入数据有效信号@(posedge clk); input_bit <= 1'b1;@(posedge clk); input_bit <= 1'b0;@(posedge clk); input_bit <= 1'b0;endinput_valid <= 1'b0; //输入数据有效信号repeat(3) begin@(posedge clk);endo_data_end <= 1'b1; enable <= 1'b0;@(posedge clk);o_data_end <= 1'b0;#1000000;$fclose(file); // 关闭文件$stop;

endendmodule1/2CC卷积码编码

module CC2 ( //二分之一码率 多项弿 = 7,5input clk, input rst,input enable, //使能信号 input sink_data, //输入数据input sink_valid, //数据有效信号output reg out_valid, //输出数据有效信号output reg [1:0] out_data //输出数据

);// sink_data shift_reg[1] shift_reg[0]

// out_data[1] out_data[0] 7 5

reg [1:0] shift_reg; //移位寄存噿always @(posedge clk) beginif(!rst) beginshift_reg <= 2'b0; //初始化为0out_valid <= 1'b0; //数据输出无效out_data <= 2'b0;end else if(enable) beginif(sink_valid) begin //检测到数据有效信号拉高out_data[0] <= sink_data + shift_reg[0];out_data[1] <= sink_data + shift_reg[1] + shift_reg[0];out_valid <= 1'b1; //拉高数据输出有效信号shift_reg <= {sink_data,shift_reg[1]}; //移位end else beginout_data <= out_data;out_valid <= 1'b0;shift_reg <= shift_reg;endend else beginshift_reg <= 2'b0; //将所有寄存器清零out_valid <= 1'b0; //数据输出无效out_data <= 2'b0; endendendmodule

1/2CC卷积码译码

module CC2_Decoding

(input clk,input rst,input in_data_valid, //进来的全是有效数据 直接全部放进译码器中input [ 1:0] in_data,input o_data_end,output reg over, //结束解码output out_data,output outdata_valid

);parameter out_data_hop_amount = 8 * 16 * 4; // 输出所有的有效比特数wire [ 7:0] decoded_data;reg [15:0] binary_data;

reg data_valid;reg [ 10:0] out_data_hop_count; //一跳的输出码元计数器reg flag;wire s_axis_data_tready;

wire decoded_valid;assign out_data = decoded_data[0];Viterbi2CC_Ip u_Viterbi2CC_Ip(.aclk (clk),.aresetn (rst), //低电平就是复位.binary_data (binary_data), // 输入的硬判决编码数据流(16比特宽度).data_valid (data_valid), // 输入数据有效信号.s_axis_data_tready (s_axis_data_tready),.decoded_data (decoded_data), // 解码后的输出数据.decoded_valid (decoded_valid) // 解码输出有效信号

);assign outdata_valid = (out_data_hop_count < out_data_hop_amount) ? decoded_valid : 0;always @(posedge clk) beginif(!rst) begindata_valid <= 'b0;binary_data <= 'b0;end else if(in_data_valid && !flag) begindata_valid <= 1'b1; //调高数据有效信号binary_data[8] <= in_data[0];binary_data[0] <= in_data[1];end else if(flag && s_axis_data_tready && out_data_hop_count <= out_data_hop_amount)begindata_valid <= 1'b1;binary_data <= 'b0;end else begindata_valid <= 1'b0;binary_data <= binary_data;end

end//对输出的一跳卷积译码码元计数

always @(posedge clk) beginif(!rst) beginover <= 1'b0;out_data_hop_count <= 'b0;end else if(decoded_valid && out_data_hop_count <= out_data_hop_amount) begin//此时还在接收64个输出的有效比特数据over <= 1'b0;out_data_hop_count <= out_data_hop_count + 2'd1;end else if(out_data_hop_count <= out_data_hop_amount) beginover <= 1'b0;out_data_hop_count <= out_data_hop_count;end else beginover <= 1'b1;out_data_hop_count <= out_data_hop_count;end

endalways @(posedge clk) beginif(!rst) beginflag <= 'b0;end else if(o_data_end) begin //数据送完了flag <= 1'b1;end else beginflag <= flag;end

endendmodule

维特比译码器

module Viterbi2CC_Ip (input aclk,input aresetn,input [15:0] binary_data, // 输入的硬判决编码数据流(16比特宽度)input data_valid, // 输入数据有效信号output s_axis_data_tready,output reg [7:0] decoded_data, // 解码后的输出数据output reg decoded_valid // 解码输出有效信号

);reg [15:0] s_axis_data_tdata;

reg s_axis_data_tvalid;wire [7:0] m_axis_data_tdata;

wire m_axis_data_tvalid;

reg m_axis_data_tready;viterbi2CC your_instance_name (.aclk(aclk), // input wire aclk.aresetn(aresetn), // input wire aresetn.s_axis_data_tdata(s_axis_data_tdata), // input wire [15 : 0] s_axis_data_tdata.s_axis_data_tvalid(s_axis_data_tvalid), // input wire s_axis_data_tvalid.s_axis_data_tready(s_axis_data_tready), // output wire s_axis_data_tready.m_axis_data_tdata(m_axis_data_tdata), // output wire [7 : 0] m_axis_data_tdata.m_axis_data_tvalid(m_axis_data_tvalid), // output wire m_axis_data_tvalid.m_axis_data_tready(m_axis_data_tready) // input wire m_axis_data_tready

);always @(posedge aclk) beginif (!aresetn) begin// 复位信号处理s_axis_data_tvalid <= 'b0;m_axis_data_tready <= 'b0;decoded_valid <= 'b0;decoded_data <= 'b0;end else beginif (data_valid && s_axis_data_tready) begin// 输入有效时,将二进制编码数据发送给解码器s_axis_data_tdata <= binary_data; // 输入16比特的编码数据s_axis_data_tvalid <= 1'd1; // 表示输入数据有效end else begins_axis_data_tvalid <= 1'd0;end// 解码器输出处理if (m_axis_data_tvalid) begindecoded_data <= m_axis_data_tdata; // 获取解码后的数据decoded_valid <= 1'd1; // 标记解码输出有效end else begindecoded_valid <= 1'd0;endm_axis_data_tready <= 1'd1; // 准备接收更多解码数据end

endendmodule

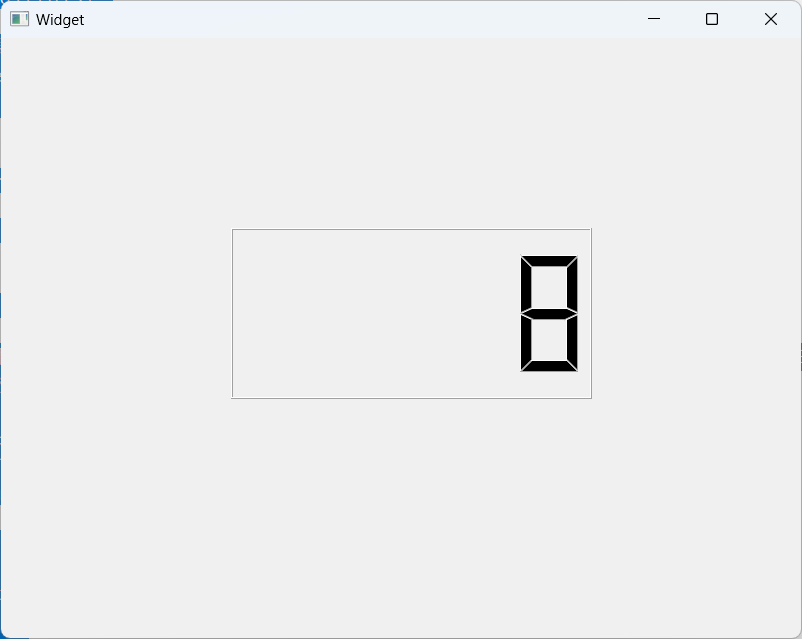

3 仿真结果

这是multisim中的仿真结果,不好看,直接在MATTAB中看解调出来的数据

最后MATLAB中的数据和仿真输入的数据几乎一模一样,只有后四位不一样,这主要是因为卷积码译码回溯的问题,导致最后几位译码会出现问题。不过问题不大

相关文章:

FPGA Xilinx维特比译码器实现卷积码译码

FPGA Xilinx维特比译码器实现卷积码译码 文章目录 FPGA Xilinx维特比译码器实现卷积码译码1 Xilinx维特比译码器实现2 完整代码3 仿真结果 MATLAB (n,k,m)卷积码原理及仿真代码(你值得拥有)_matlab仿真后代码-CSDN博客 MATLAB 仿真…...

hive 行转列

行转列的常规做法是,group bysum(if())【或count(if())】 建表: CREATE TABLE table2 (year INT,month INT,amount DOUBLE );INSERT INTO table2 (year, month, amount) VALUES(1991, 2, 1.2),(1991, 3, 1.3),(1991, 4, 1.4),(1992, 1, 2.1),(1992, 2, 2.2),(1992…...

Vue中使用ECharts图表中的阈值标记(附源码)

在数据处理和可视化领域,我们经常需要对一系列数据点进行分析。本文将介绍如何在给定的数据点中找到对应于特定Y值的X值,并设置标线起始点标记在ECharts图表中,效果图如下: 实现步骤 1、数据准备 let seriesData [// 提供日期…...

【特征融合】融合空间域和频率域提升边缘检测能力

基于深度学习的边缘检测方法已显示出巨大的优势,并获得了可喜的性能。然而,目前大多数方法只能从空间(RGB)域提取特征进行边缘检测,可挖掘的信息有限。因此,这些方法无法很好地应用于物体与背景颜色相似的场景。为了应对这一挑战,提出了一种融合空间域和频率域特征的新型…...

深入理解AVL树:结构、旋转及C++实现

1. AVL树的概念 什么是AVL树? AVL树是一种自平衡的二叉搜索树,其发明者是Adelson-Velsky和Landis,因此得名“AVL”。AVL树是首个自平衡二叉搜索树,通过对树的平衡因子进行控制,确保任何节点的左右子树高度差最多为1&…...

R24-11)

AUTOSAR AP 汽车API知识点总结(Automotive API )R24-11

汽车API知识点总结 一、背景与目标 背景:智能互联汽车正逐步依赖远程诊断、软件更新等功能以确保行驶安全,并且用户已习惯于通过智能设备中的应用程序控制连接设备。虽然AUTOSAR标准支持车辆软件的可更新性,但尚未提供将AUTOSAR应用产生的数据和功能安全可靠地暴露给非AUTO…...

【HarmonyOS开发】超详细的ArkTS入门

安装DevEco Studio和新建项目就不多说了,可以移步官网 就可以把他们拆成这几个部分了,如果看不懂可以暂时忽略下面冒号后面的内容 装饰器:用于装饰类、结构、方法以及变量,并赋予其特殊的含义。如上述示例中Entry、Component和St…...

SpringBoot3整合Sentinel-nacos持久化策略)

Springboot(五十一)SpringBoot3整合Sentinel-nacos持久化策略

上文中我记录了在Springboot项目中链接sentinel-dashboard使用限流规则的全过程。 但是呢,有一个小小的问题,我重启了一下我本地的sentinel-dashboard服务,然后,我之前创建的所有的流控规则都没了…… 这……好像有点不合理啊,咱就不能找地儿存储一下?你这一重启就没了,…...

[go-redis]客户端的创建与配置说明

创建redis client 使用go-redis库进行创建redis客户端比较简单,只需要调用redis.NewClient接口创建一个客户端 redis.NewClient(&redis.Options{Addr: "127.0.0.1:6379",Password: "",DB: 0, })NewClient接口只接收一个参数red…...

Qt入门7——Qt事件

目录 1. Qt事件介绍: 2. 事件的处理 示例1:鼠标进入(enterEvent)与离开事件(leaveEvent) 示例2:鼠标点击事件(mousePressEvent) 示例3:鼠标移动事件(mouseMoveEvent) 3. 按键事件 4. 定时器 5. 窗口事件 1. Qt事件介绍&a…...

)

CTF之密码学(仓颉编码)

一、仓颉码(用于建立中文索引) 定义与目标: 仓颉码是为了建立中文的索引观念而设计的一种编码方式。其主要目标是方便对中文资料或程式进行索引功能的处理。 工作原理: 仓颉码的索引以ASCII的字符码为基准,但在内部会转…...

面向人工智能安全的多维应对策略

• 制定并实施人工智能伦理框架 国家和行业层面需建立AI伦理原则,将其融入研发与应用中,强化科研人员的伦理培训,推动全球AI伦理框架的制定。 • 加强可信数字内容体系建设 构建可信的互联网内容体系以应对深度伪造带来的安全威胁ÿ…...

考研英语翻译与大小作文

名词动化词 1 持有 harbor2 2 反映 mirror 3 缩短 bridge 4 使用 harness 5 掩饰 mask/veil 6 修改 tailor 7 汇集 pool 8 控制 curb 9 想象 picture 10 激发 trigger 拉丁…...

视频监控汇聚平台Liveweb视频安防监控实时视频监控系统操作方案

Liveweb国标GB28181视频平台是一种基于国标GB/T28181协议的安防视频流媒体能力平台。它支持多种视频功能,包括实时监控直播、录像、检索与回看、语音对讲、云存储、告警以及平台级联等功能。该平台部署简单、可扩展性强,支持全终端、全平台分发接入的视频…...

算法第一弹-----双指针

目录 1.移动零 2.复写零 3.快乐数 4.盛水最多的容器 5.有效三角形的个数 6.查找总价值为目标值的两个商品 7.三数之和 8.四数之和 双指针通常是指在解决问题时,同时使用两个指针(变量,常用来指向数组、链表等数据结构中的元素位置&am…...

linux环境GitLab服务部署安装及使用

一、GitLab介绍 GitLab是利用Ruby onRails一个开源的版本管理系统,实现一个自托管的Git项目仓库,可通过Web界面进行访问公开的或者私人项目。 二、GitLab安装 1、先安装相关依赖 yum -y install policycoreutils openssh-server openssh-clients postf…...

MotorCAD:定子绕组中的趋肤效应和邻近效应损耗

MotorCAD 有助于减少定子绕组中的集肤效应和邻近效应损失,优化电动机性能。 了解集肤和邻近效应损失 集肤效应:交流电场在导体中感应出电流回路,增加了中心的磁通链路,导致该位置的电抗更高,结果是电流在表面附近流动…...

R语言机器学习论文(二):数据准备

禁止商业或二改转载,仅供自学使用,侵权必究,如需截取部分内容请后台联系作者! 文章目录 介绍加载R包数据下载导入数据一、数据描述二、数据预处理(一)修改元素名称(二)剔除无关变量(三)缺失值检查(四)重复值检查(五)异常值检查三、描述性统计(一)连续变量数据情…...

FFmpeg:强大的音视频处理工具指南

FFmpeg:强大的音视频处理工具指南 1. FFmpeg简介2. 核心特性2.1 基础功能2.2 支持的格式和编解码器 3. 主要组件3.1 命令行工具3.2 开发库 4. 最新发展5. 安装指南5.1 Windows系统安装5.1.1 直接下载可执行文件5.1.2 使用包管理器安装 5.2 Linux系统安装5.2.1 Ubunt…...

NiFi-从部署到开发(图文详解)

NiFi简介 Apache NiFi 是一款强大的开源数据集成工具,旨在简化数据流的管理、传输和自动化。它提供了直观的用户界面和可视化工具,使用户能够轻松设计、控制和监控复杂的数据流程,NiFi 具备强大的扩展性和可靠性,可用于处理海量数…...

LFM2.5-1.2B-Thinking-GGUF在软件测试中的应用:自动化生成测试用例与代码审查

LFM2.5-1.2B-Thinking-GGUF在软件测试中的应用:自动化生成测试用例与代码审查 1. 引言:当AI遇上软件测试 "测试工程师80%的时间都在写重复的测试用例"——这个行业痛点正在被AI改变。想象一下,当你拿到一份需求文档,A…...

5分钟搞定!cv_unet_image-matting图像抠图WebUI快速抠图技巧

5分钟搞定!cv_unet_image-matting图像抠图WebUI快速抠图技巧 1. 为什么选择这款AI抠图工具 在电商设计、社交媒体运营、证件照处理等场景中,高质量图像抠图是刚需。传统手动抠图不仅耗时耗力,对技术要求也高。而这款基于U-Net架构的AI抠图工…...

实测科哥版HeyGem稳定性:文件校验、中断恢复、显存保护全解析

实测科哥版HeyGem稳定性:文件校验、中断恢复、显存保护全解析 1. 引言:为什么稳定性对数字人视频生成如此重要 在数字人视频生成领域,我们常常关注生成效果和速度,却容易忽视一个更基础的问题——稳定性。想象一下,当…...

2026年4月OpenClaw部署方法:本地服务器部署OpenClaw、配置百炼APIKey、集成Skill详细教程

2026年4月OpenClaw部署方法:本地服务器部署OpenClaw、配置百炼APIKey、集成Skill详细教程。OpenClaw(原Clawdbot)作为2026年主流的AI自动化助理平台,可通过阿里云轻量服务器实现724小时稳定运行,并快速接入钉钉&#x…...

探索R语言中的数据处理:序列统计

在数据分析中,我们经常需要处理复杂的顺序数据,例如测试的时间序列。在本篇博客中,我们将探讨如何使用R语言来处理一个特定的问题:统计四种测试(Test 1到Test 4)在不同顺序下的执行频率。 问题描述 假设我们有一个研究数据框,其中包含四种测试的日期,这些测试可以以任…...

Redis中有事务吗?有何不同?

在技术领域,我们常常被那些闪耀的、可见的成果所吸引。今天,这个焦点无疑是大语言模型技术。它们的流畅对话、惊人的创造力,让我们得以一窥未来的轮廓。然而,作为在企业一线构建、部署和维护复杂系统的实践者,我们深知…...

24小时稳定运行方案:OpenClaw+Qwen3-32B进程守护配置

24小时稳定运行方案:OpenClawQwen3-32B进程守护配置 1. 为什么需要进程守护? 去年12月,我尝试用OpenClaw自动化处理每日技术简报时,遭遇了一个尴尬场景——凌晨3点任务突然中断,导致次日早晨的会议材料缺失关键数据。…...

EMDB:面向MCU的嵌入式键值数据库设计与实践

1. 项目概述EMDB(Embedded Micro Database)是一个专为资源受限嵌入式系统设计的极简型键值数据库,其核心目标是在微控制器级别提供可查询、可持久化、内存友好的数据管理能力。与传统嵌入式KV存储(如简单的哈希表或链表缓存&#…...

微信小程序助力老年智能评估,Pillow高级实战案例:图像处理的进阶应用。

基于微信小程序的关爱老年人在线能力评估系统设计 系统背景与意义 随着老龄化社会进程加速,老年人能力评估成为养老服务的重要环节。传统纸质评估方式效率低、数据难留存。基于微信小程序的在线评估系统可实现便捷化、标准化评估,提升养老服务智能化水平…...

【数据结构与算法】第24篇:哈夫曼树与哈夫曼编码

一、基本概念1.1 带权路径长度在二叉树中:路径长度:从一个节点到另一个节点经过的边数带权路径长度(WPL):所有叶子节点的权重 路径长度 之和示例:text叶子节点:A(7), B(5), C(2), D(4)普通树:15/ \7 8/…...