verilog笔记

Verilog学习笔记(一)入门和基础语法BY电棍233

由于某些不可抗拒的因素和各种的特殊原因,主要是因为我是微电子专业的,我需要去学习一门名为verilog的硬件解释语言,由于我是在某西部地区的神秘大学上学,这所大学的数字系统设计基础课程的考试居然是手写代码,十分的令人好笑,教育资源的匮乏可见一斑。这种编程课靠听课记笔记显然是没有办法学好的,怎么办,只有敲代码。下面的笔记是我借助AI+网上帖子+自己实践手敲代码验证写出来的。这部分笔记是从verilog入门到基础知识部分。

引入与描述性解释

verilog是硬件描述语言,诞生于1988年,现在所用的verilog标准是2005年的。

Verilog 主要用于以下领域:

- 数字电路设计:描述数字系统的行为和结构。

- 仿真:验证设计是否按预期工作。

- 综合:将 Verilog 代码转换成门级网表,进而可以用于制造芯片。

- 测试和验证:编写测试平台来验证设计的正确性。

语言特点

- 模块化:Verilog 设计是基于模块的,每个模块代表设计中的一个功能单元。

- 并行性:Verilog 代码模拟硬件的并行行为,模块内的语句并行执行。

- 时序:可以描述信号的时序关系,如延迟和时序控制。

- 数据流:通过连续赋值语句(assign)和过程块(always)来描述数据流。

基本语法

以下是一些 Verilog 的基本语法元素:

- 模块定义:使用

module关键字定义模块,endmodule结束模块定义。 - 端口声明:模块的输入和输出通过端口声明来定义。

- 变量类型:包括 wire(用于连接逻辑门),reg(用于存储值),integer 等。

- 逻辑操作:使用

&&(逻辑与),||(逻辑或),!(逻辑非)等。 - 算术操作:加(+),减(-),乘(*),除(/)等。

- 条件语句:if-else,case,casex,casez 等。

- 循环语句:for,while,repeat 等。

模块

模块是verilog语法中的基础,module可以视为verilog中的基础,是一个具备输入和输出的黑盒子。verilog中的每一个模块必须是以.v为后缀的,且文件名即为模块名称。

module top_module(input in1,input in2,output out)***

end module

但是在实际过程中往往不可能只用到一个模块,通常是会用到多个模块,类似于c语言中的头文件,在verilog中也可以相互去引入。在 Verilog 中,模块实例化是将一个模块(module)的实例(instance)放入另一个模块中的过程。这是构建复杂硬件设计的基础,允许设计者重用和组合较小的设计单元来创建更大的系统。举个例子,在主模块中调用与门模块。

module and_gate (input wire A, input wire B, output wire Y);assign Y = A & B;//输出Y=A&B

endmodule把上面的模块保存为and_gate.v

然后再定义一个top_module.v文件,在其中实例化应用and_gate 模块。

module top_module;// 声明内部信号wire A, B, Y;// 实例化 and_gate 模块and_gate instance_name (.A(A), // 将 and_gate 的 A 端口连接到 top_module 的 A 信号.B(B), // 将 and_gate 的 B 端口连接到 top_module 的 B 信号.Y(Y) // 将 and_gate 的 Y 端口连接到 top_module 的 Y 信号);// 其他模块逻辑...

endmodule逻辑块

在verilog中,逻辑块被用来描述硬件的行为和结构,主要有两种类型的逻辑块,分别是initial块和always块。

always逻辑块可以用来构建组合逻辑和时序逻辑,复杂的逻辑操作都需要出于此该逻辑块中。当然了,always逻辑块需要被写在模块module中。

下面是一些简单的always逻辑块的示例代码:

首先是组合逻辑的always逻辑块,其次是时许逻辑的always逻辑块。

always @(*) beginout = a & b; // 输出是输入 a 和 b 的逻辑与

endreg data_reg;//reg是一种数据存储类型

always @(posedge clk or negedge rstn) beginif (!rstn) begindata_reg <= 1'b0; // 当复位信号为低时,将寄存器清零end else begindata_reg <= data_in; // 在时钟上升沿,将输入数据赋值给寄存器end

end其中posedge是上升沿,negedge是下降沿。

完整的示例代码如下,在模块中嵌套逻辑块:

module top_module();always @(posedge clk) begin....endendmodule

generate逻辑块通常是结合for循环使用的,在 Verilog 中,generate 逻辑块是一个非常有用的结构,它允许你根据参数或循环来生成硬件结构。这可以用来创建可参数化的模块,或者生成大量的相同或相似的硬件结构,而不需要手动编写重复的代码。主要的用途有:

1.操作向量

2.模块重复多次实例化。

Verilog 中有三种类型的 generate 逻辑块:

-

generate-for:用于基于循环生成多个相同的硬件实例。 -

generate-if:用于基于条件判断生成或不生成硬件。 -

generate-case:用于基于多个条件生成不同的硬件结构。

下面是一个generate-for的实例:

module register_array(input wire clk,input wire reset,input wire [3:0] data_in,output wire [3:0] data_out

);parameter NUM_REGISTERS = 4;generate//generate-for逻辑块genvar i;for (i = 0; i < NUM_REGISTERS; i = i + 1) begin : gen_registersreg [3:0] reg_i;always @(posedge clk or posedge reset) beginif (reset) beginreg_i <= 4'b0000;end else beginreg_i <= data_in;endendassign data_out[i] = reg_i;end

endgenerateendmodule//结束module的定义initial逻辑块

在 Verilog 中,initial 逻辑块用于在仿真开始时执行一次性的初始化操作。它与 always 块不同,always 块在仿真过程中会无限循环执行,而 initial 块只在仿真开始时执行一次,之后就不会再执行。

initial 块通常用于以下几种情况:

-

初始化寄存器的值。

-

定义测试平台的激励(stimulus)。

-

配置仿真环境,如设置初始时间分辨率。

-

打印仿真开始时的消息。

initial逻辑块的示例代码如下:

module testbench;reg my_reg;initial begin// 在仿真时间0时初始化my_reg为0my_reg = 0;#10; // 等待10个时间单位my_reg = 1; // 在仿真时间10时将my_reg设置为1#20; // 再等待20个时间单位my_reg = 0; // 在仿真时间30时将my_reg重新设置为0$display("Simulation ended at time %t",$time);end

endmodule赋值方式

在verilog中有三种赋值方式,分别是连续赋值,阻塞赋值与非阻塞赋值,如下:

在Verilog硬件描述语言中,赋值语句用于定义信号的行为。根据赋值的类型,Verilog中的赋值可以分为以下几种:阻塞赋值(Blocking Assignment)、非阻塞赋值(Non-Blocking Assignment)和连续赋值(Continuous Assignment)。阻塞赋值使用等号(=)表示。在执行过程中,当前语句必须等待赋值完成之后,才会执行下一条语句。这意味着在同一个always块中,阻塞赋值的执行是顺序的。非阻塞赋值使用小于等于号(<=)表示。在执行过程中,当前语句不会阻塞后续语句的执行。在同一个always块中,非阻塞赋值的操作是并行的,即它们同时开始但完成时间不一定相同。连续赋值使用等号(=)表示,但它不同于阻塞赋值,因为它没有放在always块中。连续赋值描述的是组合逻辑,只要右侧的表达式发生变化,赋值就会立即更新左侧的信号。

示例代码如下:

assign x=y//此为连续赋值,用assign关键词

// 组合块

always @(*) begin//此为阻塞赋值out1 = a ;a = b ;out2 = a ;

end

// 时序块

always @(posedge clk) begin//此为非阻塞赋值out1 <= a ;a <= b ;out2 <= a ;

end

基础语法

逻辑值与逻辑运算

逻辑值

在Verilog中,主要有以下四种逻辑值:

- 0:表示逻辑低电平,通常对应于电压的0V或GND。

- 1:表示逻辑高电平,通常对应于电源电压(如5V或3.3V)。

- x:表示未知逻辑值,可以是0或1。

- z:表示高阻态,通常用于三态门或双向端口,表示输出既不是高电平也不是低电平,而是处于不驱动状态。

逻辑运算

Verilog支持以下逻辑运算,下面这些是按位运算,假如要做逻辑运算,则用&&,||这些

- 逻辑与(&):

- 运算规则:只有当两个操作数都为1时,结果才为1;否则结果为0。

- 示例:

4'b1010 & 4'b1100的结果为4'b1000。

- 逻辑或(|):

- 运算规则:只要有一个操作数为1,结果就为1;只有当两个操作数都为0时,结果才为0。

- 示例:

4'b1010 | 4'b1100的结果为4'b1110。

- 逻辑异或(^):

- 运算规则:当两个操作数不相同时,结果为1;当两个操作数相同时,结果为0。

- 示例:

4'b1010 ^ 4'b1100的结果为4'b0110。

- 逻辑同或(~^ 或 ^~):

- 运算规则:当两个操作数相同时,结果为1;当两个操作数不相同时,结果为0。

- 示例:

4'b1010 ~^ 4'b1100的结果为4'b1000。

- 逻辑非(! 或 ~):

- 运算规则:将操作数的逻辑值取反。

- 示例:

!4'b1010的结果为4'b0101,~4'b1010的结果也是4'b0101。

这里补充一下在verilog中的数字表示形式:'b在verilog中是二进制的意思,4’b1100是4位二进制数1100,这种表示方法我没学习的时候是一头雾水的。'b是二进制,'h是八进制,'d是十进制。

变量(wire,reg)

在Verilog中,wire和reg是两种不同的变量类型,它们用于表示硬件电路中的不同信号和功能。

wire

wire类型用于表示硬件电路中的物理连线。它通常用于表示模块间的连接、组合逻辑的输出以及芯片上的实际电线。以下是关于wire的一些特点:

-

wire用于表示线网(net),即它是一个无状态的变量,它的值由驱动它的逻辑门或模块的输出决定。 -

wire不能存储值,它的值是连续分配的,即它的值在任何时刻都是由连接到它的驱动器所决定的。 -

wire主要用于表示组合逻辑的输出。 -

wire可以在连续赋值语句(assign statement)中使用,用于连续赋值。

reg

reg类型用于表示寄存器类型的变量,它通常用于表示时序逻辑中的存储元素。以下是关于reg的一些特点:

reg用于表示变量,它可以存储值,通常用于在always块中赋值。reg并不总是代表硬件寄存器,它也可以用于表示用于仿真的内部变量。reg可以在过程赋值语句(procedural assignment)中使用,如always块、initial块等。reg通常用于表示触发器(flip-flop)的输出。

wire a, b, sum;assign sum = a & b; // 使用assign语句将a和b的逻辑与结果赋值给sum,wire用在assign 语句中reg a, b, q;always @(posedge clk) beginq <= a & b; // 在时钟上升沿将a和b的逻辑与结果赋值给q,reg用在always逻辑块中

end区别如下

wire用于组合逻辑,而reg用于时序逻辑。wire通过连续赋值语句赋值,而reg通过过程赋值语句赋值。wire不能在always块中直接赋值,而reg可以在always块中赋值。

值得注意的是即使register(reg)暗示了其是一个寄存器,但实际上这还要和其在电路中是如何使用的对应上。

向量与参数(常量)

parameter 参数:

parameter是一种常量,通常出现在module内部,常被用于定义状态、数据位宽等

vector(向量):

在Verilog中,向量变量是一种表示多位宽信号的方式,它允许我们以单个变量的形式处理一组位。向量可以是线网(wire)或变量(reg)类型,并且可以用于表示组合逻辑或时序逻辑的输出。以下是关于Verilog中向量变量形式的详细介绍:

向量通过在变量名后面加上方括号[]来定义,方括号内指定了向量的位宽。位宽可以是确定的数字,也可以是参数化的表达式。向量的位宽定义了向量包含的位数。

wire [3:0] w; // 定义一个4位的wire类型向量,位宽从3到0

reg [7:0] r; // 定义一个8位的reg类型向量,位宽从7到0向量索引:

Verilog允许通过索引来访问向量中的单个位或连续的位段。索引可以是常数或计算得到的表达式。

reg [7:0] r;// 访问单个位

r[0] = 1'b1; // 设置r的第0位为1

r[7] = 1'b0; // 设置r的最高位为0// 访问连续的位段

r[3:1] = 3'b101; // 设置r的第3位到第1位为101向量拼接:

允许将向量进行相连,如此看来向量和c语言中的字符串更加相似。

wire [3:0] a = 4'b1010;

wire [3:0] b = 4'b1100;

wire [7:0] c;// 向量拼接

c = {a, b}; // c将会是8'b10101100向量赋值:

向量赋值允许整体赋值和部分赋值。

reg [7:0] r;//八位向量,[7:0]// 整体赋值

r = 8'b10101010;// 部分选择赋值

r[7:4] = 4'b1111; // r现在为8'b11111010向量的操作:

向量间允许进行逻辑运算,算术运算和比较运算。向量间运算的时候,需要保持其长度一样。

reg [3:0] a = 4'b1010;

reg [3:0] b = 4'b1100;

reg [3:0] result;// 逻辑运算

result = a & b; // 结果为4'b1000在verilog中的向量一般来说是从最高位到最低位这样设定的,比如reg [4:0] a中就是从第四位到第0位如此设定的。

三元表达式

在Verilog中,三元表达式是一种简洁的书写方式,用于在单个表达式中实现条件赋值。它类似于C语言中的条件运算符 ? :。三元表达式的语法如下:

condition ? expression1 : expression2部分使用示例如下:

reg a, b, c;

wire d;// 如果a为1,则d赋值为b,否则赋值为c

d = a ? b : c;

reg [3:0] a, b, result;// 如果a的最高位为1,则result的最高4位赋值为b,否则赋值为a

result[3:0] = a[3] ? b[3:0] : a[3:0];分支语句

在Verilog中,分支语句用于根据条件的真假来执行不同的代码块。Verilog提供了两种主要的分支语句:if语句和case语句。下面将详细介绍这两种分支语句的用法。

if语句:

if语句是最基本的分支结构,它根据条件的真假来决定是否执行某个代码块。

reg [1:0] a;

reg b;always @(posedge clk) beginif (a == 2'b01) beginb <= 1'b1; // 如果a等于01,则b赋值为1endelse beginb <= 1'b0; // 否则,b赋值为0end

endcase语句:

case语句是一种多路分支结构,它允许根据表达式的值选择多个代码块中的一个来执行。case语句中假如不满足所有的值就执行default条件。示例代码如下,类似于c语言中的case语句:

reg [1:0] a;

reg [2:0] b;always @(posedge clk) begincase (a)2'b00: b <= 3'b000; // 如果a等于00,则b赋值为0002'b01: b <= 3'b001; // 如果a等于01,则b赋值为0012'b10: b <= 3'b010; // 如果a等于10,则b赋值为010default: b <= 3'b111; // 如果a不匹配上述任何值,则b赋值为111endcase

endfor循环语句

在Verilog中,for循环语句是一种重复执行代码块的构造,它允许你根据给定的条件重复执行一系列操作。这在初始化寄存器数组或执行重复计算时非常有用。以下是for循环的基本语法和用法。在verilog中的for循环语句和c语言中的for循环语句相似。

reg [7:0] my_array [0:99]; // 声明一个包含100个8位寄存器的数组initial beginfor (int i = 0; i < 100; i = i + 1) beginmy_array[i] = 8'h00; // 将数组中的每个元素初始化为0end

end- 循环变量通常声明为整数类型(

int),这是Verilog中的一个4态变量,可以表示正值、负值、0和x(未知)。 - 在Verilog中,

for循环通常用于initial和always块中。 - 在可综合的Verilog代码中,

for循环必须保证在有限的时间内完成。这意味着循环的迭代次数必须是可预测的,通常基于常数或参数。 - 在仿真中,

for循环可以无限运行,但在实际硬件中,循环必须在一个时钟周期内完成,或者分解为多个时钟周期内的操作。 - 在可综合的代码中,

for循环的索引变量不应在循环体内被赋值,除非是按照循环迭代的固定模式更新。

拼接运算符

在Verilog中,拼接运算符(Concatenation Operator)用于将多个位宽不同的信号或变量组合成一个连续的位宽更大的信号。拼接运算符有两种形式:连续拼接运算符 {} 和重复拼接运算符 {n{}}。连续拼接运算符允许你将多个信号或值按顺序拼接起来,形成一个更大的向量。重复拼接运算符允许你将一个信号或值重复多次,形成一个更大的向量。示例代码如下:

wire [3:0] a = 4'b1010;

wire [1:0] b = 2'b11;

wire [5:0] c;assign c = {a, b}; // c 将被赋值为 6'b101011

wire [1:0] a = 2'b11;

wire [7:0] b;assign b = {4{a}}; // b 将被赋值为 8'b11111111while循环

在Verilog中,while循环是一种过程性语句,它允许在initial块或always块中根据给定的条件重复执行一段代码。while循环的行为类似于C语言中的while循环,它在每次迭代之前检查条件,如果条件为真(即非零),则执行循环体内的代码;如果条件为假(即零),则退出循环。示例代码如下:

reg [7:0] accumulator; // 8位累加器

reg [7:0] counter; // 8位计数器initial beginaccumulator = 0; // 初始化累加器counter = 0; // 初始化计数器while (counter < 100) beginaccumulator = accumulator + counter; // 累加计数器的值counter = counter + 1; // 计数器递增end$display("Accumulator value: %d", accumulator); // 显示累加器的最终值

end在下面的示例中编写了test_bench文件并编译和查看结果:

repeat循环

在Verilog中,repeat 循环是一个用于重复执行一段代码的循环结构。它类似于 C 语言中的 for 循环,但是 repeat 循环的语法更简单,因为它只指定了循环次数,而不需要初始化表达式和递增表达式。示例代码如下:

module repeat_test;

reg [3:0] count; // 4位计数器

initial begin//initial逻辑块count = 0; // 初始化计数器repeat (10) begin#5; // 等待5个时间单位count = count + 1; // 计数器递增$display("Count is %d", count); // 打印计数器的值end

end

endmodule

实际上说明在verilog编译的时候不需要test_bench也是可行的,仅仅编写一个module文件也是可以编译并查看结果的,具体如下所示:

函数与任务

在Verilog中,函数(function)和任务(task)是两种用于封装和重用代码块的重要机制。它们在模块内部定义,可以用来执行特定的操作或计算。函数是一种返回单个值的操作,它不能包含任何时间延迟(#)或非阻塞赋值(<=)。函数通常用于计算和返回一个结果。

函数的特点:

- 函数必须有一个返回类型,可以是线网(wire)或寄存器(reg)类型,并且可以指定宽度。

- 函数可以接受输入参数,但不能有输出参数。

- 函数不能包含任何时间延迟(#)或非阻塞赋值(<=)。

- 函数在调用时必须有一个返回值。

function [7:0] add_bytes(input [7:0] a, input [7:0] b);//定义函数,输出是[7:0]的向量,输入是[7:0]a和[7:0]b,这是system verilog的语法,传统的verilog实际上不支持参数的声明在括号中add_bytes = a + b;

endfunction任务是一种可以执行多个操作的块,它可以包含时间延迟和非阻塞赋值。任务可以没有返回值,但可以有输入和输出参数。

任务的特点:

- 任务可以没有返回值,因此不需要指定返回类型。

- 任务可以接受输入参数和输出参数。

- 任务可以包含时间延迟(#)和非阻塞赋值(<=)。

- 任务可以调用其他任务或函数。

值得注意的是,任务的特点在于其可以包含时间延迟和非阻塞赋值,且其不一定得有一个返回值。

task delay_and_print(input [7:0] data, output reg done);#10; // 延迟10个时间单位$display("Data is %h", data);done = 1'b1; // 设置完成标志

endtask下面的代码示例展示了如何在verilog中编写并调用函数。

module task_test;// 函数定义(传统Verilog语法)function [7:0] myfunction;input [7:0] a; // 在函数体内声明输入参数input [7:0] b;beginmyfunction = a + b; // 通过赋值给函数名返回结果endendfunctionreg [7:0] out;initial beginout = myfunction(8'b11000011, 8'b10101010);$display("out is %b", out); end

endmodule

相关文章:

verilog笔记

Verilog学习笔记(一)入门和基础语法BY电棍233 由于某些不可抗拒的因素和各种的特殊原因,主要是因为我是微电子专业的,我需要去学习一门名为verilog的硬件解释语言,由于我是在某西部地区的神秘大学上学,这所…...

c++中sleep是什么意思(不是Sleep() )

sleep 函数在 C 语言中用于暂停程序执行指定的秒数,语法为 sleep(unsigned int seconds)。当 seconds 为 0 时,函数立即返回,否则函数将使进程暂停指定的秒数,并返回实际暂停的时间。 sleep 函数在 C 中的含义 sleep 函数是 C 标…...

Uniapp 开发中遇到的坑与注意事项:全面指南

文章目录 1. 引言Uniapp 简介开发中的常见问题本文的目标与结构 2. 环境配置与项目初始化环境配置问题解决方案 项目初始化注意事项解决方案 常见错误与解决方案 3. 页面与组件开发页面生命周期注意事项示例代码 组件通信与复用注意事项示例代码 样式与布局问题注意事项示例代码…...

Dify安装教程:Linux系统本地化安装部署Dify详细教程

1. 本地部署 Dify 应用开发平台 环境:Ubuntu(24.10) docker-ce docker compose 安装 克隆 Dify 源代码至本地环境: git clone https://github.com/langgenius/dify.git 启动 Dify: cd dify/docker cp .env.example...

rtsp rtmp 跟 http 区别

SDP 一SDP介绍 1. SDP的核心功能 会话描述:定义会话的名称、创建者、时间范围、连接地址等全局信息。媒体协商:明确媒体流的类型(如音频、视频)、传输协议(如RTP/UDP)、编码格式(如H.264、Op…...

基于YOLO11深度学习的运动鞋品牌检测与识别系统【python源码+Pyqt5界面+数据集+训练代码】

《------往期经典推荐------》 一、AI应用软件开发实战专栏【链接】 项目名称项目名称1.【人脸识别与管理系统开发】2.【车牌识别与自动收费管理系统开发】3.【手势识别系统开发】4.【人脸面部活体检测系统开发】5.【图片风格快速迁移软件开发】6.【人脸表表情识别系统】7.【…...

物体识别系统(识别图片中的物体)

这是一个基于 PyTorch 和 PyQt5 的物体识别程序,使用 Faster R-CNN 模型来识别图片中的物体,并通过图形界面展示识别结果。 1.用户界面 主窗口:包含加载图片、识别、清除按钮,以及图片显示区域和结果展示区域。 图片显示&#…...

数据表的存储过程和函数介绍

文章目录 一、概述二、创建存储过程三、在创建过程中使用变量四、光标的使用五、流程控制的使用六、查看和删除存储过程 一、概述 存储过程和函数是在数据库中定义的一些SQL语句的集合,然后直接调用这些存储过程和函数来执行已经定义好的SQL语句。存储过程和函数可…...

【DeepSeek-R1背后的技术】系列九:MLA(Multi-Head Latent Attention,多头潜在注意力)

【DeepSeek背后的技术】系列博文: 第1篇:混合专家模型(MoE) 第2篇:大模型知识蒸馏(Knowledge Distillation) 第3篇:强化学习(Reinforcement Learning, RL) 第…...

【JavaWeb12】数据交换与异步请求:JSON与Ajax的绝妙搭配是否塑造了Web的交互革命?

文章目录 🌍一. 数据交换--JSON❄️1. JSON介绍❄️2. JSON 快速入门❄️3. JSON 对象和字符串对象转换❄️4. JSON 在 java 中使用❄️5. 代码演示 🌍二. 异步请求--Ajax❄️1. 基本介绍❄️2. JavaScript 原生 Ajax 请求❄️3. JQuery 的 Ajax 请求 &a…...

)

[特殊字符] 蓝桥杯 Java B 组 之位运算(异或性质、二进制操作)

Day 6:位运算(异或性质、二进制操作) 📖 一、位运算简介 位运算是计算机底层优化的重要手段,利用二进制操作可以大大提高运算速度。常见的位运算包括: 与(&):a &am…...

[MDM 2024]Spatial-Temporal Large Language Model for Traffic Prediction

论文网址:[2401.10134] Spatial-Temporal Large Language Model for Traffic Prediction 论文代码:GitHub - ChenxiLiu-HNU/ST-LLM: Official implementation of the paper "Spatial-Temporal Large Language Model for Traffic Prediction" …...

LTO优化详解

嵌入式开发过程中的LTO优化是什么意思?能够用来解决什么问题?它都优化了哪些?仅开启LTO真的可以优化SIZE的问题吗? 请分别回答我刚才提到的问题? 嗯,用户问关于嵌入式开发中的LTO优化,我需要详细解释这个概…...

分布式事务三阶段协议

分布式事务的三阶段分别是准备阶段、预提交阶段和提交 / 回滚阶段,以下是详细介绍: 三阶段提交协议可以理解为两阶段提交协议的改良版,是在协调者和参与者中都引入超时机制,并且把两阶段提交协议的第一个阶段分成了两步: 询问&am…...

LLaMA-Factory|微调大语言模型初探索(4),64G显存微调13b模型

上篇文章记录了使用lora微调deepseek-7b,微调成功,但是微调llama3-8b显存爆炸,这次尝试使用qlora微调HQQ方式量化,微调更大参数体量的大语言模型,记录下来微调过程,仅供参考。 对过程不感兴趣的兄弟们可以直…...

常用高压缩率的视频容器格式,并进行大比例压缩

常用的高压缩率视频容器格式,包括*.mp4 、*.mkv、*.webM等。 容器格式本身并不直接决定压缩率,而是取决于容器中所使用的视频编码格式等因素。不过,在常见的视频容器格式中,一些容器在搭配特定编码格式时,通常能表现出较高的压缩效率,以下是相关介绍: 1 MKV格式 …...

)

代码编译(词法义)

1.预处理 (Preprocessing): 在这个阶段,编译器会处理所有以 # 开头的指令,如 #include、#define 等。它会把头文件的内容插入到源代码中,进行宏替换等预处理操作,生成一个纯净的代码文件。 3.词法分析 (Lexical Analy…...

android,flutter 混合开发,pigeon通信,传参

文章目录 app效果native和flutter通信的基础知识1. 编解码器 一致性和完整性,安全性,性能优化2. android代码3. dart代码 1. 创建flutter_module2.修改 Android 项目的 settings.gradle,添加 Flutter module3. 在 Android app 的 build.gradl…...

at32f403a rt thread led基础bsp工程测试

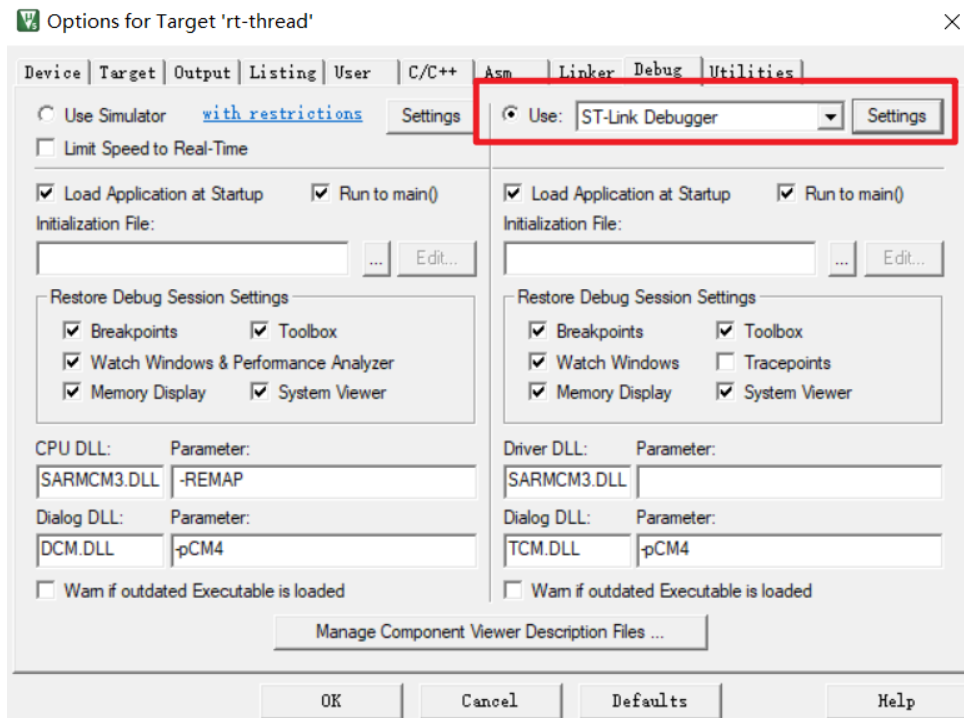

1.led工程官方bsp使用 导出一个独立的AT32F403A的BSP工程 下载RTT源代码 gitee更新较慢 https://gitee.com/rtthread/rt-thread github版本更新最新 https://github.com/RT-Thread/rt-thread. 切换到V5.1.0分支(使用一个发布版本可以避免不必要的bug) 导出一个独立的AT32BSP…...

DeepSeek写贪吃蛇手机小游戏

DeepSeek写贪吃蛇手机小游戏 提问 根据提的要求,让DeepSeek整理的需求,进行提问,内容如下: 请生成一个包含以下功能的可运行移动端贪吃蛇H5文件: 要求 蛇和食物红点要清晰,不超过屏幕外 下方有暂停和重新…...

NVIDIA NIM微服务在Kubernetes中的自动扩缩容实践

1. 项目概述在2025年3月18日之后,NVIDIA Triton推理服务器已正式成为NVIDIA Dynamo平台的一部分,并更名为NVIDIA Dynamo Triton。NVIDIA NIM微服务作为模型推理容器,可以在Kubernetes集群中部署运行。在生产环境中,理解这些微服务…...

)

关键词排名上去了,为什么还是没询盘?深度拆解+实操解决(谷歌SEO新手必看)

排名≠询盘|真正致命的4个转化卡点,花3分钟逐个击破做英文独立站,最开心的莫过于看着关键词一步步冲上谷歌首页,以为询盘会源源不断涌来。可现实往往很扎心:排名有了、流量来了,邮箱和表单却安安静静&#…...

有哪些好用的技巧?)

大模型检索增强生成(RAG)有哪些好用的技巧?

RAG算是大模型时代的hello world项目了,但是开源方案基本都是文章切块向量召回llm生成 3步,实际业务落地过程中有哪些好用的技巧呢? 说实话,RAG 这东西我一开始觉得挺简单——文档切片、向量化、检索、生成,四步完事。…...

JimuReport:企业级开源报表工具的技术架构与实施路径分析

JimuReport:企业级开源报表工具的技术架构与实施路径分析 【免费下载链接】JimuReport 开源的报表工具与BI大屏,完美替代帆软和Tableau,提供强大的报表能力。一款类似Excel的报表设计器和大屏设计!完全在线傻瓜式拖拽设计…...

机器人声学验证技术:非侵入式行为监测方案

1. 机器人工作流的声学验证技术解析 在工业自动化、医疗手术和仓储物流等关键领域,机器人系统的行为可靠性直接关系到生产安全和运营效率。传统验证方法通常依赖机器人内置的传感器数据,但这些数据可能被恶意篡改或受到系统故障的影响。我们团队开发的Wa…...

Postman新手必看:一个隐藏的Host勾选框,如何让你的接口测试总报400 Bad Request?

Postman接口测试避坑指南:揭秘Host头缺失引发的400错误 第一次用Postman测试接口就遇到400 Bad Request?别急着怀疑人生,这可能是工具本身的一个隐藏机制在作祟。作为API测试领域的瑞士军刀,Postman在易用性背后藏着不少新手容易踩…...

手把手教你用MogFace人脸检测模型-large:从部署到检测全流程指南

手把手教你用MogFace人脸检测模型-large:从部署到检测全流程指南 1. 快速上手:MogFace是什么,为什么值得一试? 如果你正在寻找一个“靠谱”的人脸检测工具,那么MogFace-large绝对是一个绕不开的名字。简单来说&#…...

Linux proc sysfs与devfs 虚拟文件系统解析

Linux_proc_sysfs与devfs_虚拟文件系统解析 本文说明 Linux 中三类常见伪文件系统(内存中由内核呈现、不占用块设备上常规文件空间)的定位与差异:proc、sysfs,以及已基本退出主流的 devfs 及其替代路径。读者具备基础 Shell 与系…...

基于LLM与RAG技术的智能销售助手开发实战

1. 从零构建AI销售助手的实战经验分享在科技行业,销售团队每天需要处理海量产品信息、客户数据和市场动态。传统的信息检索方式效率低下,销售人员往往需要翻阅数十份文档才能找到所需内容。我们团队基于大语言模型(LLM)和检索增强…...

acbDecrypter技术解析:如何解密游戏音频文件的完整指南

acbDecrypter技术解析:如何解密游戏音频文件的完整指南 【免费下载链接】acbDecrypter 项目地址: https://gitcode.com/gh_mirrors/ac/acbDecrypter acbDecrypter是一款基于Python开发的专业游戏音频解密工具,专门用于处理ACB/AWB容器格式中的加…...