PCIE接口

PCIE接口

- PIC接口

- 介绍

- PIC总线结构

- PCI总线特点

- PCI总线的主要性能

- PIC的历程

- PCIE接口

- 介绍

- PCIe接口总线位宽

- PCIE速率

- GT/s和Gbps区别

- PCIE带宽计算

- PCIE架构

- PCIe体系结构

- 端到端的差分数据传递

- PCIe总线的层次结构

- 事务层

- 数据链路层

- 物理层

- PCIe层级结构及功能框图

- PCIe链路初始化

- PCIe链路的扩展

- PCIe链路均衡

- PCIe的接口形态

- PCIe Add-in-Card(AIC)

- PCIe的信号连接

- +3.3V和AUX3.3V电源分开设计原因

- M.2接口

- OAM 卡

PIC接口

介绍

PCI即Peripheral Component Interconnect,中文意思是“外围器件互联”,是由PCISIG (PCI Special Interest Group)推出的一种局部并行总线标准。PCI总线是由ISA(Industy Standard Architecture)总线发展而来的,ISA并行总线有8位和16位两种模式,时钟频率为8MHz,工作频率为33MHz/66MHz。是一种同步的独立于处理器的32位或64位局部总线。从结构上看,PCI是在CPU的供应商和原来的系统总线之间插入的一级总线,具体由一个桥接电路实现对这一层的管理,并实现上下之间的接口以协调数据的传送。从1992年创立规范到如今,PCI总线已成为了计算机的一种标准总线。已成为局部总线的新标准,广泛用于当前高档微机、工作站,以及便携式微机。主要用于连接显示卡、网卡、声卡。PCI总线是32位同步复用总线。其地址和数据线引脚是AD31~AD0。PCI的工作频率为33MHz。

PIC总线结构

PCI总线是一种树型结构,并且独立于CPU总线,可以和CPU总线并行操作。PCI总线上可以挂接PCI设备和PCI桥片,PCI总线上只允许有一个PCI主设备,其他的均为PCI 从设备,而且读写操作只能在主从设备之间进行,从设备之间的数据交换需要通过主设备中转。 [1] PCI总线结构如下图所示。

在处理器系统中,含有PCI总线和PCI总线树这两个概念。这两个概念并不相同,在一颗PCI总线树中可能具有多条PCI总线,而具有血缘关系的PCI总线组成一颗PCI总线树。PCI总线由HOST主桥或者PCI桥管理,用来连接各类设备,如声卡、网卡和IDE接口卡等。在一个处理器系统中,可以通过PCI桥扩展PCI总线,并形成具有血缘关系的多级PCI总线,从而形成PCI总线树型结构。在处理器系统中有几个HOST主桥,就有几颗这样的PCI总线树,而每一颗PCI总线树都与一个PCI总线域对应。

与HOST主桥直接连接的PCI总线通常被命名为PCI总线0。考虑到在一个处理器系统中可能有多个主桥。

PCI总线取代了早先的ISA总线。当然与在PCI总线后面出现专门用于显卡的AGP总线,与现在的PCI Express总线相比,功能没有那么强大,但是PCI能从1992用到现在,说明他有许多优点,比如即插即用(Plug and Play)、中断共享等。在这里我们对PCI总线做一个深入的介绍。

从数据宽度上看,PCI总线有32bit、64bit之分,从总线速度上分,有33MHz、66MHz两种。目前流行的是32bit @ 33MHz,而64bit系统正在普及中。改良的PCI系统,PCI-X,最高可以达到64bit @ 133MHz,这样就可以得到超过1GB/s的数据传输速率。如果没有特殊说明,以下的讨论以32bit @ 33MHz为例。

不同于ISA总线,PCI总线的地址总线与数据总线是分时复用的。这样做的好处是,一方面可以节省接插件的管脚数,另一方面便于实现突发数据传输。在做数据传输时,由一个PCI设备做发起者(主控,Initiator或Master),而另一个PCI设备做目标(从设备,Target或Slave)。总线上的所有时序的产生与控制,都由Master来发起。PCI总线在同一时刻只能供一对设备完成传输,这就要求有一个仲裁机构(Arbiter),来决定在谁有权力拿到总线的主控权。

当PCI总线进行操作时,发起者(Master)先置REQ#,当得到仲裁器(Arbiter)的许可时(GNT#),会将FRAME#置低,并在AD总线上放置Slave地址,同时C/BE#放置命令信号,说明接下来的传输类型。所有PCI总线上设备都需对此地址译码,被选中的设备要置DEVSEL#以声明自己被选中。然后当IRDY#与TRDY#都置低时,可以传输数据。当Master数据传输结束前,将FRAME#置高以标明只剩最后一组数据要传输,并在传完数据后放开IRDY#以释放总线控制权。

这里我们可以看出,PCI总线的传输是很高效的,发出一组地址后,理想状态下可以连续发数据,峰值速率为132MB/s。实际上,目前流行的33M@32bit北桥芯片一般可以做到100MB/s的连续传输。

PCI总线特点

- 传输速率高最大数据传输率为132MB/s,当数据宽度升级到64位,数据传输率可达264MB/s。这是其他总线难以比拟的。它大大缓解了数据I/O瓶颈,使高性能CPU的功能得以充分发挥,适应高速设备数据传输的需要。

- 多总线共存采用PCI总线可在一个系统中让多种总线共存,容纳不同速度的设备一起工作。通过HOST-PCI桥接组件芯片,使CPU总线和PCI总线桥接;通过PCI-ISA/EISA桥接组件芯片,将PCI总线与ISA/EISA总线桥接,构成一个分层次的多总线系统。高速设备从ISA/EISA总线卸下来,移到PCI总线上,低速设备仍可挂在ISA/EISA总线上,继承原有资源,扩大了系统的兼容性。

- 独立于CPU PCI总线不依附于某一具体处理器,即PCI总线支持多种处理器及将来发展的新处理器,在更改处理器品种时,更换相应的桥接组件即可。

- 自动识别与配置外设 用户使用方便。

- 并行操作能力。

PCI总线的主要性能

- 总线时钟频率33.3MHz/66.6MHz。

- 总线宽度32位/64位。

- 最大数据传输率132MB/s(264MB/s)。

- 支持64位寻址。

- 适应5V和3.3V电源环境。

PIC的历程

话说上世纪80年代处理器的速度是越来越快,早期的ISA并行总线有8位和16位两种模式,时钟频率为8MHz,总线带宽可以达到8MB/s和16MB/s;到88年推出了EISA在兼容ISA的基础上将位宽增加到32位,带宽因此也能达到32MB/s,当时这速率连接386/486之类的处理器已足够;但随着处理器速度越来越快,EISA总线的带宽已经满足不了CPU的需求,CPU外网总线带宽已经成为制约计算机处理能力继续提高的瓶颈。于是在1991年,Intel、IBM、HP、Compaq、DEC等100多家计算机公司成立了PCISIG,联合推出PCI(Peripheral Component Interconnect),92年PCI1.0便Release。

随着PCI总线的发展,PCI总线又发展到PCI-X(Peripheral Component Interconnect eXtended)。与PCI总线相比,PCI-X总线的位宽未改变,而是将时钟频率进行了提高。PCI-X 1.0的时钟频率有66MHz/100MHz/133MHz,总线带宽分别为:264MB/s,400MB/s和532MB/s(32位),528MB/s,800MB/s和1064MB/s;PCI-X2.0的时钟频率有266MHZ/533MHz/1066MHz,总线带宽分别为1064MB/s、2132MB/s和4264MB/s(32位),3128MB/s,4264MB/s和8512MB/s(64位)。PCI-X与PCI在结构上完全兼容。不过PCI-X出现不就便出现了PCIe,因此在工业界,PCI-X应用远没有PCI和PCIe广泛。

90年代处理器按照摩尔定律发展,PCI碰到了和ISA一样的问题–赶不上处理器发展速度。想要提高速度,还是并行总线的PCI,要么提升频率要么提升位宽;如果提升频率的话并行信号间的串扰让时序难以收敛,提高位宽的话,信号线数量又大大增加。于是高速的串行总线开始替代并行总线,差分线替代并行线,在2003年的时候PCIe诞生了。

PCIE接口

介绍

PCI Express是新一代的总线接口。早在2001年的春季,英特尔公司就提出了要用新一代的技术取代PCI总线和多种芯片的内部连接,并称之为第三代I/O总线技术。随后在2001年底,包括Intel、AMD、DELL、IBM在内的20多家业界主导公司开始起草新技术的规范,并在2002年完成,对其正式命名为PCI Express,它原来的名称为“3GIO”。

从概念上来说,PCIe总线架构实际上是旧的PCI总线的高速串行替代产品,其最大的差别在于总线的拓扑结构:PCI总线使用的是共享并行总线架构,所有的PCI主机和所有的设备共享一组通用的地址、数据和控制线,由于其共享式总线拓扑结构,因此采用的是仲裁方式访问,单个方向上一次只允许一个主设备存在。PCIe采用了目前业内流行的点对点串行连接,以及交换式架构。单独的串行链路将每个设备连接到host(root complex),每个设备都有自己的专用连接,不需要向整个总线请求带宽,而且可以把数据传输率提高到一个很高的频率。

在数据传输方面,旧的PCI时钟方案采用的是总线上最慢的设备频率作为基准数据传输频率(不管有多少设备,也不管其他设备的情况如何),因此整体传输效率会被较慢的设备拉低。鉴于此,在传统的PCI-AGP系统中,AGP总线需要单独的控制器才能访问和控制,并和通用的PCI链路彻底隔离。这样显然增加了系统的复杂程度。

相比之下,PCIe改用了全新的任意两个端点的全双工通信,同时对多个端点的并发访问没有限制,系统只需要保留一个或者数个多通路的PCIe控制器,就可以实现对不同带宽需求的设备进行控制。比如显卡需要PCIe x16,SSD需要PCIe x4,声卡需要PCIe x1,这些设备都可以挂接在一个PCIe控制器上,互相之间也不会受到影响。

在总线协议方面,PCIe的通信数据使用了特殊的数据包封装,打包和解包数据以及状态消息流的工作由PCIe的端口事物层处理,不需要CPU的干涉。此外,PCIe总线在链接配对方面存在极高的灵活性。两个设备之间的PCIe链路可以在x1和x32之间自由变动,此时吞吐量将随着链路变动而变动。

在实际工作中,链路之间的通道数量可以在设备初始化期间自动协商连接,可以采用最低链路的设备规格,也可以采用其他规格。举例来说,可以将只支持PCIe x1的设备插入PCIe x4或者x16的插槽中,初始化时将自动设置为最高可相互支持的物理链接通道数。反之,也可以自行配置较少的通道数,这样能够在设备出现坏道或者不可靠通道时提供容错性。

信号方面,PCIe规定了每一个通道中包含两组差分信号对,其中一对差分信号用于接收数据,另外一对差分信号用于发送数据。因此每个PCIe通道都需要4条线缆或者信号迹线。一般来说,人们对这种同时可以收发的信息通道称作“全双工”信息传输通道。每次传输、链路端点之间的两个方向上都会传递8位字节格式的数据包。采用串行信息的优势在于,每个通道的每个方向只有一个差分信号,并且嵌入了时钟信息,这使得整个系统的抗干扰能力大大增强,并且频率极限被提升至千兆赫兹。

PCIe的初始标准定义了七种链路宽度,对应七种不同的物理插槽规格。这七种链路规格的通道数量分别为1组、2组、4组、8组、12组、16组和32组,对应的标识分别采用x1、x2、x4、x8、x12、x16和x32,不同规格的链路也和相应长度的物理插槽规格相匹配。一般来说,x16插槽是最常见的插槽规格,它用于接驳显卡或者万兆网络、超高速SSD等高性能高带宽设备。x32的插槽不太多见,往往用于服务器或者特殊场合。

值得一提的是,由于PCIe规范的灵活性,人们往往设计智能切换方案来进行插槽链路配置,而不再需要和物理链路规格绑定。举例来说,一个x16的PCIe链路,可以同时面向一个x16规格的物理插槽和一个x4规格的物理插槽。

当x4物理接口没有插入任何设备时,在优先级配置规范的指引下,PCIe链路将全部分配给x16的物理插槽;当x4规格接口插入设备后,PCIe链路可以根据配置需要,分配x12或者x8的链路给原本为x16的物理插槽,新的x4接口可以在不启用和获得x4带宽之间自由选择。

除了上述传输方面的设计外,PCIe在电源方面也作出了加强。根据PCIe规范,PCIe设计了数个专用的+12V和+3.3V引脚,最大可供电能力为75W,这个供电能力已经完全可以满足大部分普通设备的需求了。不过在实际使用中,受制于主板设计、PCB设计以及系统供电等原因,PCIe插槽的供电能力有可能达不到75W,各家厂商也会在相应的产品中予以说明。

显卡所使用的6pin、8pin供电标准也是PCIe规范所定义的。

PCIe接口总线位宽

PCI Express的接口根据总线位宽不同而有所差异,包括X1、X4、X8以及X16(X2模式将用于内部接口而非插槽模式)。较短的PCI Express卡可以插入较长的PCI Express插槽中使用(自动识别并兼容)。PCI Express接口能够支持热拔插,这也是个不小的飞跃。PCI Express卡支持的三种电压分别为+3.3V、3.3Vaux以及+12V。用于取代AGP接口的PCI Express接口位宽为X16,将能够提供5GB/s的带宽,即便有编码上的损耗但仍能够提供4GB/s左右的实际带宽,远远超过AGP 8X的2.1GB/s的带宽。

PCI Express规格从1条通道连接到32条通道连接,有非常强的伸缩性,以满足不同系统设备对数据传输带宽不同的需求。例如,PCI Express X1规格支持双向数据传输,每向数据传输带宽250MB/s,PCI Express X1已经可以满足主流声效芯片、网卡芯片和存储设备对数据传输带宽的需求,但是远远无法满足图形芯片对数据传输带宽的需求。 因此,必须采用PCI Express X16,即16条点对点数据传输通道连接来取代传统的AGP总线。PCI Express X16也支持双向数据传输,每向数据传输带宽高达4GB/s,双向数据传输带宽有8GB/s之多,相比之下,目前广泛采用的AGP 8X数据传输只提供2.1GB/s的数据传输带宽。

PCIE速率

2021年,PCIe 6.0 规范发布。每通道数据传输速率从PCIe 5.0的32 GT/s翻番至64 GT/s,PCIe 6.0*16通道的带宽高达256 GB/s,除了带宽和效率的提升外,PCIe 6.0还具有更低的延迟,是PCIe技术的又一大飞跃。

GT/s和Gbps区别

在数据传输中,GT/s和Gbps的数值是否相等,取决于每个传输(Transfer)包含多少比特(bit)。

- GT/s —— Giga transation per second(千兆传输/秒),即每一秒内传输的次数。重点在于描述物理层通信协议的速率属性,可以不和链路宽度等关联。

- Gbps —— Giga Bits Per Second(千兆位/秒)。GT/s 与Gbps 之间不存在成比例的换算关系。

1、双倍数据速率(DDR)场景:

若总线时钟频率为F GHz,在双倍速率(DDR)下,每秒传输次数为2F GT/s。若每次传输对应 1 个比特(例如串行通信,每个传输周期发送 1 bit),则:数据传输速率=2F Gbps。此时2F GT/s 在数值上等于2F Gbps,即GT/s = Gbps。

2、复杂情况的影响:

并行传输:若每次传输通过多根数据线发送多个比特(如 64 位总线),则Gbps=GT/s×总线宽度。

编码开销:若使用编码(如 8b/10b),有效数据速率会降低(例如10GT/s的实际有效速率为8Gbps)。

3、总结:

在理想情况下(单比特传输、无编码开销),当数据传输速率为总线时钟的两倍时,数值上1GT/s = 1Gbps。若存在并行传输或编码,则两者不等。

PCIE带宽计算

PCIe 吞吐量(可用带宽)计算方法:

吞吐量 = 传输速率 * 编码方案

例如:PCI-e2.0协议支持5.0GT/s,即每一条Lane 上支持每秒钟内传输5G个Bit;但这并不意味着 PCIe 2.0协议的每一条Lane支持5Gbps的速率。因为PCIe 2.0的物理层协议中使用的是8b/10b的编码方案。 即每传输8个Bit,需要发送10个Bit;这多出的2个Bit并不是对上层有意义的信息。那么, PCIe 2.0协议的每一条Lane支持 5x8/10 = 4Gbps = 500MB/s的速率。以一个PCIe 2.0 x8的通道为例,x8的可用带宽为 4x8 = 32Gbps = 4GB/s。

同理,PCI-e3.0协议支持8.0GT/s, 即每一条Lane 上支持每秒钟内传输 8G个Bit。而PCIe 3.0的物理层协议中使用的是128b/130b的编码方案。 即每传输128个Bit,需要发送130个Bit。那么,PCIe 3.0协议的每一条Lane支持 8x128/130 = 7.877Gbps = 984.6MB/s 的速率。一个PCIe 3.0 x16的通道,x16 的可用带宽为7.877x16 = 126.031Gbps = 15.754GB/s。

PCIE架构

PCIe采用的是树型拓扑结构, 一般由根复合体(Root Complex),中继器(Repeater),终端设备(Endpoint)等类型的PCIe设备组成。接下来将讲述PCIe如何通过下图突出显示的典型链路进行初始化和传输。

Root Complex: 根复合体是CPU和PCIe总线连接的接口。主要负责存储器域到PCIe总线域的地址转换,随着虚拟化技术的引入,根复合体的功能也越来越复杂。根复合体把来自CPU的request转化成PCIe的4类request(configuration、memory、I/O、message)并发送给下面的设备。

Repeater:中继器是一种信号调节装置,可分为两类:Retimers和Redriver,两者都是常用的PCIe组件,Retimer通过内部时钟重构信号,再恢复后发送出去;Redriver则是通过信号均衡化和预加强等技术,重新加强再发送出去。在图示中,我们将使用PCIe 4.0兼容的Retimers举例。

PCIe Endponit: PCIe终端设备,是PCIe树型结构的末端节点。比如SSD,网卡、GFX卡等等。

PCIe体系结构

PCIe总线作为处理器系统的局部总线,其作用与PCI总线类似,主要目的是为了连接处理器系统中的外部设备,当然PCIe总线也可以连接其他处理器系统。在不同的处理器系统中,PCIe体系结构的实现方法略有不同。但是在大多数处理器系统中,都使用了RC、Switch和PCIe-to-PCI桥这些基本模块连接PCIe和PCI设备。在PCIe总线中,基于PCIe总线的设备,也被称为EP。

在下图的结构中,处理器系统首先使用一个虚拟的PCI桥分离处理器系统的存储器域与PCI总线域。FSB总线下的所有外部设备都属于PCI总线域。与这个虚拟PCI桥直接相连的总线为PCI总线0。这种架构与Intel的x86处理器系统较为类似。

端到端的差分数据传递

“端到端的数据传送方式”是PCIe和PCI最大的差别,PCI是物理层为并行总线传输。PCIe链路使用“端到端的数据传送方式”,发送端和接收端中都含有TX(发送逻辑)和RX(接收逻辑)。

在PCIe总线的物理链路的一个数据通路(Lane)中,由两组差分信号,共4根信号线组成。其中发送端的TX部件与接收端的RX部件使用一组差分信号连接,该链路也被称为发送端的发送链路,也是接收端的接收链路;而发送端的RX部件与接收端的TX部件使用另一组差分信号连接,该链路也被称为发送端的接收链路,也是接收端的发送链路。一个PCIe链路可以由多个Lane组成。

高速差分信号电气规范要求其发送端串接一个电容,以进行AC耦合。该电容也被称为AC耦合电容。PCIe链路使用差分信号进行数据传送,一个差分信号由D+和D-两根信号组成,信号接收端通过比较这两个信号的差值,判断发送端发送的是逻辑“1”还是逻辑“0”。

与单端信号相比,差分信号抗干扰的能力更强,因为差分信号在布线时要求“等长”、“等宽”、“贴近”,而且在同层。因此外部干扰噪声将被“同值”而且“同时”加载到D+和D-两根信号上,其差值在理想情况下为0,对信号的逻辑值产生的影响较小。因此差分信号可以使用更高的总线频率。

此外使用差分信号能有效抑制电磁干扰EMI(Electro Magnetic Interference)。由于差分信号D+与D-距离很近而且信号幅值相等、极性相反。这两根线与地线间耦合电磁场的幅值相等,将相互抵消,因此差分信号对外界的电磁干扰较小。当然差分信号的缺点也是显而易见的,一是差分信号使用两根信号传送一位数据;二是差分信号的布线相对严格一些。

PCIe总线的层次结构

PCIe总线采用了串行连接方式,并使用数据包(Packet)进行数据传输,采用这种结构有效去除了在PCI总线中存在的一些边带信号,如INTx和PME#等信号。在PCIe总线中,数据报文在接收和发送过程中,需要通过多个层次,包括事务层、数据链路层和物理层。PCIe总线的层次结构如图所示。具体每一层的硬件逻辑后续章节会详细介绍。

PCIe总线的层次组成结构与网络中的层次结构有类似之处,但是PCIe总线的各个层次都是使用硬件逻辑实现的。在PCIe体系结构中,数据报文首先在设备的核心层(Device Core)中产生,然后再经过该设备的事务层(Transaction Layer)、数据链路层(Data Link Layer)和物理层(Physical Layer),最终发送出去。而接收端的数据也需要通过物理层、数据链路和事务层,并最终到达Device Core。

数据包在各个层的处理如下所示:

事务层

事务层定义了PCIe总线使用总线事务,其中多数总线事务与PCI总线兼容。这些总线事务可以通过Switch等设备传送到其他PCIe设备或者RC。RC也可以使用这些总线事务访问PCIe设备。

事务层接收来自PCIe设备核心层的数据,并将其封装为TLP(Transaction Layer Packet)后,发向数据链路层。此外事务层还可以从数据链路层中接收数据报文,然后转发至PCIe设备的核心层。

数据链路层

数据链路层保证来自发送端事务层的报文可以可靠、完整地发送到接收端的数据链路层。来自事务层的报文在通过数据链路层时,将被添加Sequence Number前缀和CRC后缀。数据链路层使用ACK/NAK协议保证报文的可靠传递。

PCIe总线的数据链路层还定义了多种DLLP(Data Link Layer Packet),DLLP产生于数据链路层,终止于数据链路层。值得注意的是,TLP与DLLP并不相同,DLLP并不是由TLP加上Sequence Number前缀和CRC后缀组成的。

物理层

物理层是PCIe总线的最底层,将PCIe设备连接在一起。PCIe总线的物理电气特性决定了PCIe链路只能使用端到端的连接方式。PCIe总线的物理层为PCIe设备间的数据通信提供传送介质,为数据传送提供可靠的物理环境。

物理层是PCIe体系结构最重要,也是最难以实现的组成部分。PCIe总线的物理层定义了LTSSM(Link Training and Status State Machine)状态机,PCIe链路使用该状态机管理链路状态,并进行链路训练、链路恢复和电源管理。

PCIe层级结构及功能框图

下图为PCIe设备核心层、事务层、数据链路层、物理层的结构及功能框图。

PCIe链路初始化

在了解PCIe链路是如何建立以及数据如何通过PCIe协议传输之前,我们先了解一下常见PCIe控制信号的功能。

PERST#信号为全局复位信号,由处理器系统提供。处理器系统需要为PCIe插槽和PCIe设备提供该复位信号。PCIe设备使用该信号复位内部逻辑,当该信号有效时,PCIe设备将进行复位操作。

WAKE#和CLKREQ#信号都用于在本文讨论范围之外的低功率状态之间转换。

REFCLK#是PCIe设备开始数据传输的先决条件,PCIe设备通过使用REFCLK#提供的100MHz外部参考时钟(Refclk),用于协调在两个PCIe设备间的数据传输。

PCIe链路在初始状态时,需要检测对端设备是否存在,然后才能进行链路训练。所有PCIe设备通电并提供参考时钟信号后在每个通道上将拥有接收器检测电路(Receiver Detection circuit),该电路将允许PCIe设备确定是否有要配对的链路伙伴。假设PCIe Rx检测电路检测到另一个设备,则每个通道将开始以2.5 GT/s的速度进行传输串行数据。

2.5 GT/s是第一代PCIe 1.0采用的数据速率,另外由于PCIe 1.0与任何PCIe设备兼容,因此每个PCIe链路都以相同的链路初始化过程开始。以下图为例,Root Complex、Retimer和Endpoint都以PCIe 1.0的速度开始传输。

在经过PCIe链路初始化后,每个器件将能接收到数据并做出相应的响应。PCIe连接开始链路训练过程并进入配置阶段,在该阶段中,由于通道长度变化而导致数据中的任何偏差都能得到校准,PCIe链路的宽度、链路速率、链路翻转和链路极性也在此阶段确定。

如果存在多条链路,则PCIe连接称为PCIe分叉。在示例中,有一个非分叉连接,即所有通道都分配给编号为0的链路。由于Retimer链路分为两部分,其两侧的链路分别进行链路初始化。在确定链路和通道号后,PCIe链路可以进入多种状态。

以进入L0状态举例,这是发送和接收数据与数据包的正常操作状态。到达L0后Root Complex和Enpoint可相互通信,PCIe链路也可转换为多种低功耗状态或另一种链路训练状态。在此不做过多阐述。

PCIe链路的扩展

PCIe链路使用端到端的数据传送方式。在一条PCIe链路中,这两个端口是完全对等的,分别连接发送与接收设备,而且一个PCIe链路的一端只能连接一个发送设备或者接收设备。因此PCIe链路必须使用Switch扩展PCIe链路后,才能连接多个设备。使用Switch进行链路扩展的实例如图所示。

PCIe链路均衡

PCIe设备都支持PCIe Gen2,则链路速度也会随之提高。如果数据速率为PCIe Gen3或以上,PCIe链路将需要经历额外链路优化过程(称为链路均衡)。

链路均衡以建立设备间稳定的连接为目的。通过调节Tx (传输端)和Rx (接收端)的设置,提高信号质量,使PCIe链路以最稳定且更快的速率传输。由于PCIe在Gen3及以上的每一代均需优化连接,因此链路均衡过程可能发生多次。

例如:若所有PCIe设备为Gen5,则有3次链路均衡过程(第1次:Gen1-Gen3;第2次:Gen3-Gen4;第3次:Gen4-Gen5)。链路均衡通过PCIe 规范中定义的preset值来实现,preset指不同的预过冲(Preshoot)和去加重(De-emphasis)的组合。对于Gen3和Gen4,有11个preset值,即preset0-preset10。对于不同的链路情况,系统要求Rx端发送Tx EQ preset设置请求给Tx端,让其做对应的preset均衡设置;Tx端发送Rx EQ均衡设置,要求Rx端做相应的设置,最终获得一个最优的均衡组合和Rx端的眼图。

Phase0:第1阶段链路均衡涉及上游端口(Upstream port)和下游端口(Downstream port)之间的精确动态协商,下游端口通过向上游设备发送每个通道所需的发送器preset值来开始链路均衡,被称为第0阶段链接均衡。在接收到下游端口的请求后不久,上游端口增加到第3代(Gen3)链路数据速率,并开始使用所需preset将训练序列发送回下游端口。链路速度增加至Gen3(8 GT/s)后,链路均衡过程通过来回发送preset值来协商每个端口的preset配置,从而继续优化链路。

Phase1:为了充分优化链路,以便能够交换训练序列(Training Sequences)并且完成用于精调目的的剩余链路均衡阶段,尽管有出现链路质量差的可能性,但相同的训练序列会被重复发送,来确保下游端口接收到正确的preset值。

Phase2:在第1阶段链路的误码率实现BER≤10e-4后,进入到Phase 2,随后进一步优化上游端口的preset值,直至获得最优设置,链路的误码率应满足BER ≤ 1E-12。

Phase3:到第3阶段对下游端口执行相同的协商。上游端口通过训练序列发送均衡请求去调整下游端口的preset值,直至获得最优设置,链路的误码率应满足BER ≤ 1E-12。

当Phase3完成后,链路均衡也已完成,此时链路以Gen3的速率进入L0状态,并在该速率进行稳定通信。对于更高的传输速率,PCIe设备必须进行多次链路均衡过程。

然而在某些主板设计中,尤其是那些具有长通道链路的主板,这种信号质量无法实现,可能需要另外的信号调节。在这种情况下,中继器(如ReDriver,ReTimer)则被用来做信号调节,并在PCIe设备和根复合体(在CPU,存储设备和PCIe设备之间的重要连接部分)之间提供高质量信号。

PCIe的接口形态

目前已有的接口规范有下面几种

- PCIe Add-in-Card(AIC)

- PCIe M.2

- OAM等异形插槽

PCIe Add-in-Card(AIC)

PCIe AIC 是最常见的PCIe接口形态,组装过电脑的可能比较清楚,电脑上的主板上都会有下面的几排插槽,这就是典型的PCIe AIC的插槽,比较常见的插槽位宽为x16和x1

插在上面的卡就是PCIe AIC。PCIe AIC常见的有显卡,无线网卡,存储设备等等。这个AIC上的插头有个闪亮的名字,叫“金手指”。金手指来源于PCB制作工艺中的沉金工艺,为了导电性良好,这上面可是有真金哦。这个金手指有两面,两面都有信号连接。

PCIe的信号连接

- 电源和地,包括必备的12V电源和可选的3.3V电源

- SerDes的差分信号,支持多少条Lane就有多少组差分信号,例如16Lane的PCIe AIC就有16x4=64个信号

- 附属信号(Auxlilary Signal),必选的包括

参考时钟(REFCLK-/REFCLK+),给PCIe AIC提供时钟。复位信号(PERST#),用于复位PCIe AIC。插入检测信号(PRSNT1# ,PRSNT2#)。这个信号在金手指上会短一点,所以如果这个信号已经连上了说明整个插口已经插进去了。WAKE#:唤醒信号,用于唤醒设备。

详细的金手指两面的信号如下:

具体的Spec可以参考PCI Express® Card Electromechanical Specification

+3.3V和AUX3.3V电源分开设计原因

在PCI Express(PCIe)规范中,+3.3V和AUX3.3V电源分开设计有其特定的原因和优势。以下是这两个电源分开的主要原因:

1、独立供电

- +3.3V:主要用于设备的正常工作供电,提供稳定的3.3V电源。

- AUX3.3V:主要用于设备的初始化、低功耗模式和热插拔支持,提供独立的3.3V辅助电源。

2、热插拔支持

- AUX3.3V:在设备热插拔时,AUX3.3V电源可以提供持续的电力,确保设备在插入或拔出过程中不会因为断电而损坏。这有助于系统检测设备的插入和拔出状态,确保正确的热插拔操作。

- +3.3V:在设备正常工作时提供电力,但在热插拔过程中可能无法提供持续的电力。

3、低功耗模式

- AUX3.3V:在设备处于低功耗模式或待机模式时,AUX3.3V电源可以继续为设备的关键部件供电,以维持基本功能。这有助于设备快速响应和恢复到正常工作状态。

- +3.3V:在设备正常工作时提供电力,但在低功耗模式下可能被关闭以节省能源。

4、信号完整性

- AUX3.3V:通过提供独立的辅助电源,可以减少主电源线路的干扰,提高系统的稳定性和性能,特别是在高速数据传输时。

- +3.3V:主要用于设备的正常工作,确保信号的完整性和可靠性。

5、设备初始化

- AUX3.3V:在设备启动和初始化阶段,AUX3.3V电源可以为设备提供必要的电力,确保设备能够顺利启动。

- +3.3V:在设备正常工作时提供电力,但在启动和初始化阶段可能无法提供足够的电力。

总结:

+3.3V和AUX3.3V电源分开设计的主要目的是确保设备在各种工作状态下的稳定性和可靠性。AUX3.3V电源在设备初始化、低功耗模式、热插拔支持和信号完整性方面起着关键作用,而+3.3V电源则主要用于设备的正常工作。这种设计使得PCIe设备在各种场景下都能表现出良好的性能和可靠性。

M.2接口

M.2接口主要用于小型SSD的连接,我们熟悉的M.2 SSD是这样的,M.2接口胜在小巧。

M.2接口分为:

- B Key,支持PCIe x2 Lane

- M Key,支持PCIe x4 Lane

- B+M Key,支持PCIe x2 Lane,同时兼容插在M Key上

OAM 卡

OAM 是OCP(Open Compute) 定义的指导AI硬件加速模块和系统设计的标准,可以在服务器上实现更优的AI硬件加速模块的互联。外形长成这个样子:

详细的信息可以参考Open Compute Project

更多:

PCIE接口介绍

相关文章:

PCIE接口

PCIE接口 PIC接口介绍PIC总线结构PCI总线特点PCI总线的主要性能PIC的历程 PCIE接口介绍PCIe接口总线位宽PCIE速率GT/s和Gbps区别PCIE带宽计算 PCIE架构PCIe体系结构端到端的差分数据传递PCIe总线的层次结构事务层数据链路层物理层PCIe层级结构及功能框图 PCIe链路初始化PCIe链路…...

Leetcode 3479. Fruits Into Baskets III

Leetcode 3479. Fruits Into Baskets III 1. 解题思路2. 代码实现 题目链接:3479. Fruits Into Baskets III 1. 解题思路 这一题思路本质上就是考察每一个水果被考察时找到第一个满足条件且未被使用的basket。 因此,我们只需要将basket按照其capacit…...

小程序 -- uni-app开发微信小程序环境搭建(HBuilder X+微信开发者工具)

目录 前言 一 软件部分 1. 微信开发者工具 2. HBuilder X 开发工具 二 配置部分 1. 关于 HBuilder X 配置 2. 关于 微信开发工具 配置 三 运行项目 1. 新建项目 2. 代码编写 3. 内置浏览器 编译 4. 配置小程序 AppID获取 注意 四 实现效果 前言 uni-app开发小程…...

深度学习PyTorch之13种模型精度评估公式及调用方法

深度学习pytorch之22种损失函数数学公式和代码定义 深度学习pytorch之19种优化算法(optimizer)解析 深度学习pytorch之4种归一化方法(Normalization)原理公式解析和参数使用 深度学习pytorch之简单方法自定义9类卷积即插即用 实时…...

《云原生监控体系构建实录:从Prometheus到Grafana的观测革命》

PrometheusGrafana部署配置 Prometheus安装 下载Prometheus服务端 Download | PrometheusAn open-source monitoring system with a dimensional data model, flexible query language, efficient time series database and modern alerting approach.https://prometheus.io/…...

GHCTF2025--Web

upload?SSTI! import os import refrom flask import Flask, request, jsonify,render_template_string,send_from_directory, abort,redirect from werkzeug.utils import secure_filename import os from werkzeug.utils import secure_filenameapp Flask(__name__)# 配置…...

NO.32十六届蓝桥杯备战|函数|库函数|自定义函数|实参|形参|传参(C++)

函数是什么 数学中我们其实就⻅过函数的概念,⽐如:⼀次函数 y kx b ,k和b都是常数,给⼀个任意的x ,就得到⼀个 y 值。其实在C/C语⾔中就引⼊了函数(function)的概念,有些翻译为&a…...

计算机视觉算法实战——老虎个体识别(主页有源码)

✨个人主页欢迎您的访问 ✨期待您的三连 ✨ ✨个人主页欢迎您的访问 ✨期待您的三连 ✨ ✨个人主页欢迎您的访问 ✨期待您的三连✨ 1. 领域介绍 老虎个体识别是计算机视觉中的一个重要应用领域,旨在通过分析老虎的独特条纹图案,自动识别和区…...

【移动WEB开发】rem适配布局

目录 1. rem基础 2.媒体查询 2.1 语法规范 2.2 媒体查询rem 2.3 引入资源(理解) 3. less基础 3.1 维护css的弊端 3.2 less介绍 3.3 less变量 3.4 less编译 3.5 less嵌套 3.6 less运算 4. rem适配方案 4.1 rem实际开发 4.2 技术使用 4.3 …...

25年携程校招社招求职能力北森测评材料计算部分:备考要点与误区解析

在求职过程中,能力测评是筛选候选人的重要环节之一。对于携程这样的知名企业,其能力测评中的材料计算部分尤为关键。许多求职者在备考时容易陷入误区,导致在考试中表现不佳。本文将深入解析材料计算部分的实际考察方向,并提供针对…...

【Elasticsearch入门到落地】9、hotel数据结构分析

接上篇《8、RestClient操作索引库-基础介绍及导入demo》 上一篇我们介绍了RestClient的基础,并导入了使用Java语言编写的RestClient程序Demo以及将要分析的数据库。本篇我们就要分析导入的宾馆数据库tb_hotel表结构的具体含义,并分析如何建立其索引库。 …...

现代互联网网络安全与操作系统安全防御概要

现阶段国与国之间不用对方路由器,其实是有道理的,路由器破了,内网非常好攻击,内网共享开放端口也非常多,更容易攻击。还有些内存系统与pe系统自带浏览器都没有javascript脚本功能,也是有道理的,…...

轻量级TCC框架的实现

现有seata、tcc-transaction等tcc框架实现都较为重量级,今天主要带来一种轻量级的实现,大概只用了1200行代码实现。不依赖具体框架grpc、http、dubbo等,只需要业务系统按照标准化实现Try、Commit、Cancel实现接口即可。 已解决悬挂、幂等、空…...

共绘智慧升级,看永洪科技助力由由集团起航智慧征途

在数字化洪流汹涌澎湃的当下,企业如何乘风破浪,把握转型升级的黄金机遇,已成为所有企业必须直面的时代命题。由由集团,作为房地产的领航者,始终以前瞻视野引领变革,坚决拥抱数字化浪潮,携手数字…...

小程序开发总结

今年第一次帮别人做小程序。 从开始动手到完成上线,一共耗时两天。AI 让写代码变得简单、高效。 不过,小程序和 Flutter 等大厂开发框架差距实在太大,导致我一开始根本找不到感觉。 第一,IDE 不好用,各种功能杂糅在…...

元脑服务器:浪潮信息引领AI基础设施的创新与发展

根据国际著名研究机构GlobalData于2月19日发布的最新报告,浪潮信息在全球数据中心领域的竞争力评估中表现出色,凭借其在算力算法、开放加速计算和液冷技术等方面的创新,获得了“Leader”评级。在创新、增长力与稳健性两个主要维度上ÿ…...

uniapp+node+mysql接入deepseek实现流式输出

node import express from express; import mysql from mysql2; import cors from cors; import bodyParser from body-parser; import axios from axios; import { WebSocketServer } from ws; // 正确导入 WebSocketServerconst app express();// Middlewares app.use(cors…...

PHP MySQL 创建数据库

PHP MySQL 创建数据库 引言 在网站开发中,数据库是存储和管理数据的核心部分。PHP 和 MySQL 是最常用的网页开发语言和数据库管理系统之一。本文将详细介绍如何在 PHP 中使用 MySQL 创建数据库,并对其操作进行详细讲解。 前提条件 在开始创建数据库之…...

UE4 World, Level, LevelStreaming从入门到深入

前言 在《塞尔达传说:旷野之息》中,玩家攀上初始高塔的瞬间,目光所及的山川湖泊皆可抵达;在《艾尔登法环》中,黄金树的辉光始终悬于地平线之上,指引玩家穿越无缝衔接的史诗战场。这些现代游戏杰作背后的核…...

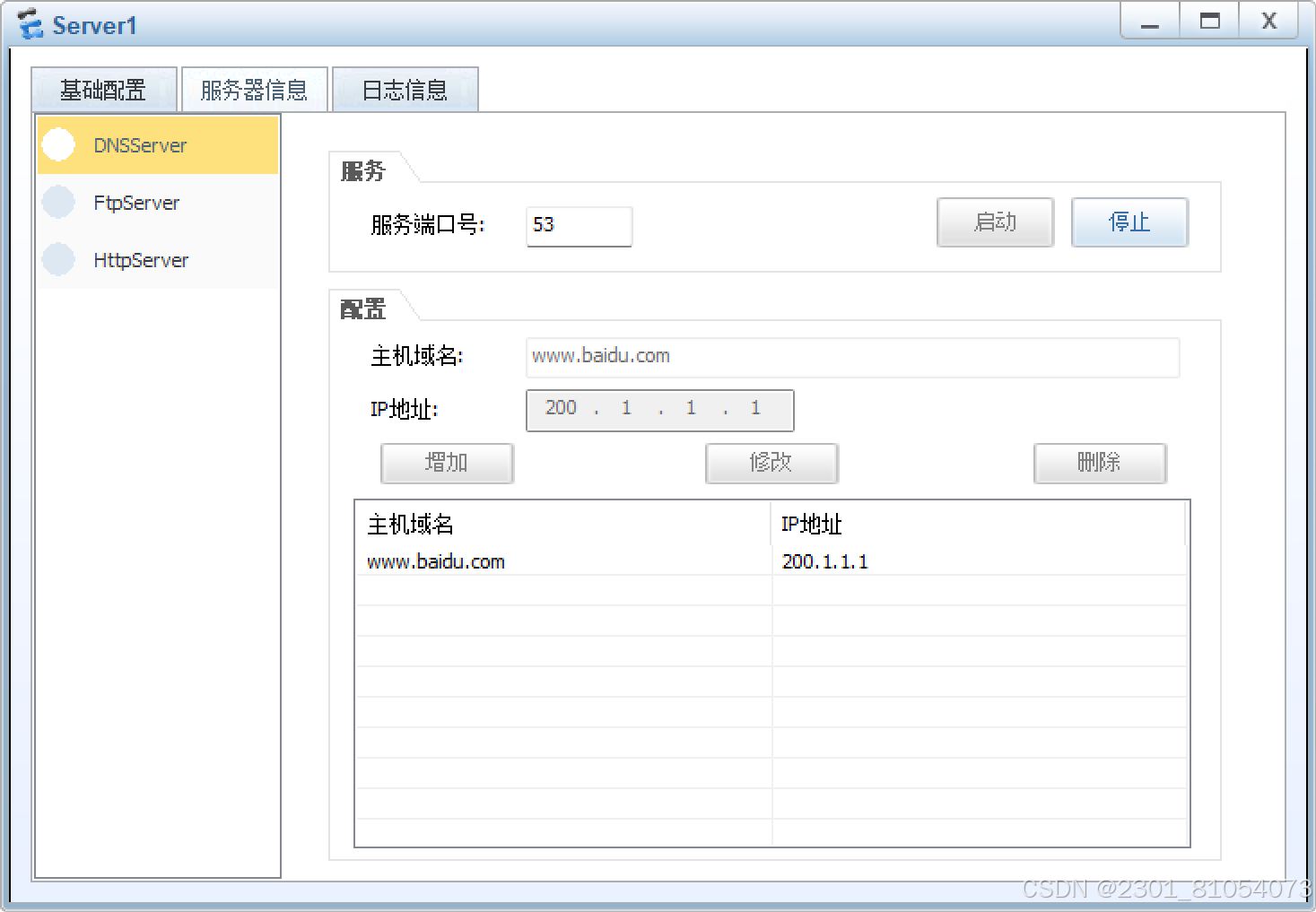

3月8日实验

拓扑: 需求: 1.学校内部的HTTP客户端可以正常通过域名www.baidu.com访问到白度网络中的HTTP服务器 2.学校网络内部网段基于192.168.1.0/24划分,PC1可以正常访问3.3.3.0/24网段,但是PC2不允许 3.学校内部路由使用静态路由&#…...

)

新手也能懂的RAIM算法:用Python复现GNSS完好性监测(附代码与数据)

新手也能懂的RAIM算法:用Python复现GNSS完好性监测(附代码与数据) 当你用手机导航时,是否想过这些定位信号有多可靠?RAIM(Receiver Autonomous Integrity Monitoring)算法就像GNSS系统的"质…...

异步AI流式响应总出错?FastAPI 2.0架构设计图首次公开:EventSource vs Server-Sent Events vs WebSockets选型决策树

第一章:FastAPI 2.0异步AI流式响应架构设计图全景概览FastAPI 2.0 引入了原生增强的异步流式响应支持,为大语言模型(LLM)推理、实时语音转写、多模态生成等AI场景提供了低延迟、高吞吐的基础设施能力。其核心在于将 ASGI 生命周期…...

EdB Prepare Carefully:定制你的RimWorld完美开局体验

EdB Prepare Carefully:定制你的RimWorld完美开局体验 【免费下载链接】EdBPrepareCarefully EdB Prepare Carefully, a RimWorld mod 项目地址: https://gitcode.com/gh_mirrors/ed/EdBPrepareCarefully 是否厌倦了RimWorld随机生成的殖民者团队带来的不确定…...

)

Mojo+Python混合项目部署失败全记录(含完整错误日志溯源与跨运行时调试手册)

第一章:MojoPython混合项目部署失败全记录(含完整错误日志溯源与跨运行时调试手册)在将 Mojo 模块嵌入 Python 3.11 环境的 CI/CD 流水线中,首次构建即触发运行时崩溃。核心现象为 mojo_runtime_init() 在 Python 进程内调用后立即…...

一个都不能少)

银河麒麟V4.0.2-sp4服务器到手后,这三步网络配置(IP/DNS/源)一个都不能少

银河麒麟V4.0.2-sp4服务器网络配置实战指南:从零搭建稳定运行环境 刚拿到一台预装银河麒麟V4.0.2-sp4操作系统的服务器时,许多运维工程师常会陷入"有设备却用不起来"的困境——无法远程连接、软件包安装失败、系统更新卡壳,这些问题…...

Umi-OCR插件技术方案:5款引擎深度对比与实战配置指南

Umi-OCR插件技术方案:5款引擎深度对比与实战配置指南 【免费下载链接】Umi-OCR_plugins Umi-OCR 插件库 项目地址: https://gitcode.com/gh_mirrors/um/Umi-OCR_plugins Umi-OCR插件库为开源OCR工具提供了丰富的引擎选择,从本地CPU加速到云端AI识…...

直接解决了特定业务场景下的性)

在 Java 并发编程和高性能数据处理中,HashMap 和 ConcurrentHashMap 是两大核心容器。它们在 JDK 8+ 中的演进(链表转红黑树、锁机制优化)直接解决了特定业务场景下的性

在 Java 并发编程和高性能数据处理中,HashMap 和 ConcurrentHashMap 是两大核心容器。它们在 JDK 8 中的演进(链表转红黑树、锁机制优化)直接解决了特定业务场景下的性能瓶颈。 以下结合具体业务场景,深度解析它们的内部机制及设计…...

2026年专业金属链板输送带服务哪家强?TOP排名为你揭晓!

家人们,在工业生产领域,金属链板输送带那可是相当重要的设备,它的质量和服务直接影响着生产效率。今天咱就来聊聊 2026 年专业金属链板输送带服务的那些事儿,给大家揭晓一下排名情况,顺便看看哪家更值得咱们选择。冲突…...

OpenClaw技能调试:GLM-4.7-Flash功能开发排错指南

OpenClaw技能调试:GLM-4.7-Flash功能开发排错指南 1. 为什么需要关注技能调试 上周我在为团队开发一个基于GLM-4.7-Flash的自动化周报生成技能时,遇到了一个棘手的问题:技能在本地测试时运行完美,但部署到OpenClaw后却频繁超时。…...

基于Arduino与Mixly的心知天气实时监测系统开发指南

1. 项目概述与准备 最近在工作室捣鼓了一个特别实用的小项目——用Arduino和Mixly搭建的天气监测系统。这个系统能实时获取温度、湿度、空气质量等数据,特别适合放在阳台或者窗台。我最初做这个是因为家里老人总抱怨手机天气App看不懂,现在有了这个实体设…...