ASIC-WORLD Verilog(2)FPGA的设计流程

写在前面

在自己准备写一些简单的verilog教程之前,参考了许多资料----asic-world网站的这套verilog教程即是其一。这套教程写得极好,奈何没有中文,在下只好斗胆翻译过来(加了自己的理解)分享给大家。

这是网站原文:http://asic-world.com/verilog/veritut.html

这是系列导航:Verilog教程系列文章导航

简介

作为 Verilog初学者,您可能想尝试一些例子和新的东西。我列出了可用于实现此目的的工具流程。这个流程我亲自尝试过,它对我来说效果很好。在这里,我只采用了工具流程的前端设计部分和部分 FPGA 设计,这套流程无需在工具上花费大量资金即可完成。

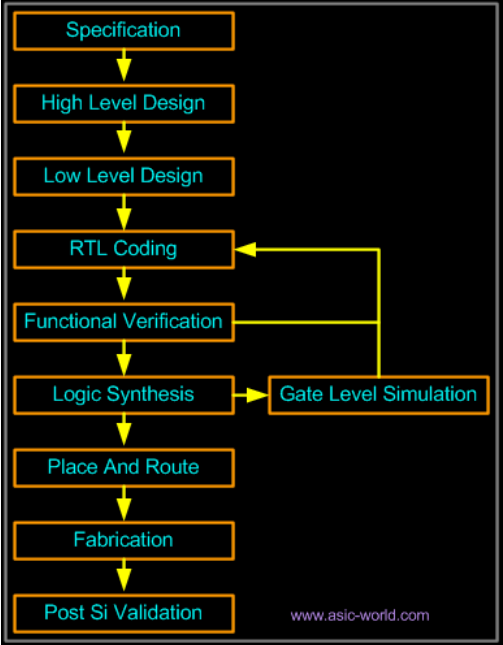

ASIC/FPGA设计的各个阶段

这是各个设计阶段可以使用的工具。

- 规格书(Specification ):文字处理器,如 Word、Kwriter、AbiWord、Open Office。

- 高层级设计(High Level Design):文字处理器,如 Word、Kwriter、AbiWord,用于绘制波形使用工具,如 waveformer 或 testbencher 或 Word,Open Office。

- 低层级设计(Micro Design/Low level design): Word、Kwriter、AbiWord 等字处理器,用于绘制波形使用工具,如 waveformer 或 testbencher 或 Word。

- RTL 编码(RTL Coding): Vim、Emacs、conTEXT、HDL TurboWriter

- 仿真(Simulation ): Modelsim、VCS、Verilog-XL、Veriwell、Finsim、Icarus。

- 综合(Synthesis):设计编译器、FPGA 编译器、Synplify、Leonardo Spectrum。您可以从 Altera 和 Xilinx 等 FPGA 供应商处免费下载。

- 布局布线(Place & Route):对于 FPGA,使用 FPGA 供应商的 P&R 工具。ASIC 工具需要像 Apollo 这样昂贵的 P&R 工具。学生可以使用LASI、Magic。

- 后仿真(Post Si Validation):对于ASIC和FPGA,芯片需要在真实环境中进行测试。电路板设计,设备驱动需要到位。

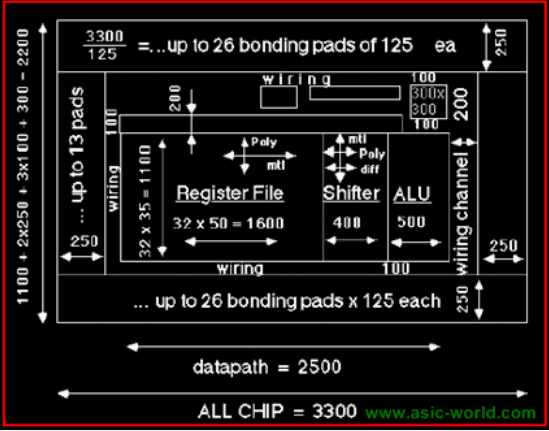

这是一张典型的设计流程图:

规格书

这是定义您预期设计的系统/设计的重要参数的阶段。一个简单的例子是:我想设计一个计数器----它应该是 4 位宽,应该有同步复位,高电平有效使能;当复位激活时,计数器输出应变为“0”。

高层级设计

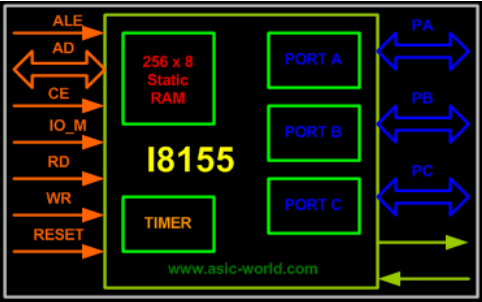

这是您在设计中定义各种子模块以及它们如何通信的阶段。假设我们需要设计一个微处理器:高层级设计意味着根据功能将设计分成多个子模块---寄存器、ALU、指令解码、内存接口等。

低层级设计

低层级设计是设计人员描述如何实现每个子模块的阶段。它包含状态机、计数器、多路复用器、解码器、内部寄存器的详细信息。在各种界面绘制波形是一个好主意。这是个人花费大量时间的阶段。

RTL编码

在 RTL 编码中,使用设计语言的可综合结构将低层级设计转换为 Verilog/VHDL 代码。我们通常喜欢在开始验证或综合之前检查代码。

module addbit (

a , // first input

b , // Second input

ci , // Carry input

sum , // sum output

co // carry output

);

//Input declaration

input a;

input b;

input ci;

//Ouput declaration

output sum;

output co;

//Port Data types

wire a;

wire b;

wire ci;

wire sum;

wire co;

//Code starts here

assign {co,sum} = a + b + ci;endmodule // End of Module addbit仿真

仿真是在任何抽象级别验证模型功能特性的过程。我们使用仿真工具来仿真硬件模型。要测试 RTL 代码是否满足规范的功能要求,我们必须查看所有 RTL 模块是否功能正确。为了实现这一点,我们需要编写一个testbench,它生成时钟、复位和所需的测试向量。计数器的示例testbench如下所示。通常我们将 60-70% 的时间花在设计验证上。

我们使用仿真工具的波形输出来查看 DUT(Device Under Test,被测设备)在功能上是否正确。大多数仿真工具都带有波形查看器。随着设计变得复杂,我们可以编写自检式testbench,自动将 DUT 的输出与预期值进行比较。

还有一种仿真叫做时序仿真,是在综合之后或者布局布线之后进行的。此处包括门延迟和线延迟,以查看 DUT 是否能以额定时钟工作。这也称为SDF(Standard Delay Format,标准延迟格式) 仿真或门级仿真。

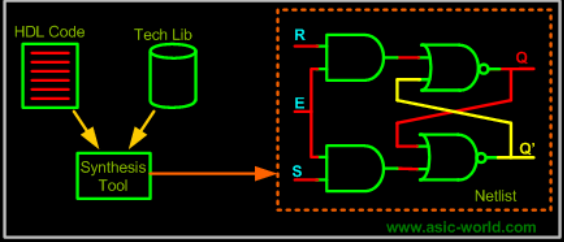

综合

综合是综合工具将 Verilog 或 VHDL 中的 RTL、目标技术和作为输入的约束并将 RTL 映射到目标技术原语的过程。综合工具在将 RTL 映射到门之后,还会进行最少量的时序分析,以查看映射的设计是否满足时序要求。(需要注意的重要一点是,综合工具不知道线延迟,它们只知道门延迟)。

综合之后,在将网表传递到后端(放置和布线)之前通常需要做几件事:

- 形式验证(Formal Verification):检查 RTL 到门的映射是否正确

- 扫描插入(Scan insertion):在ASIC的情况下插入扫描链

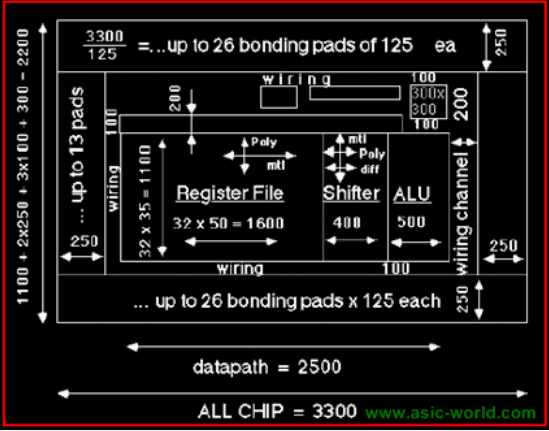

布局布线

来自综合工具的门级网表被提取并以 Verilog 网表格式导入到布局布线工具中。所有的门和触发器会被放置(布局);时钟树被综合和复位被布线。在此之后,每个子模块都被布线。P&R 工具输出是一个 GDS 文件,代工厂使用它来制造 ASIC。后端团队通常将 SPEF(标准寄生交换格式)/RSPF(减少寄生交换格式)/DSPF(详细寄生交换格式)从 ASTRO 等布局工具转储给前端团队,然后前端团队使用 Prime Time 等工具中的 read_parasitic 命令来写出 SDF(标准延迟格式)用于门级仿真目的。

后仿真

芯片(硅)从晶圆厂返回后,需要将其置于真实环境中并进行测试,然后才能投放市场。由于 RTL 的仿真速度(每秒时钟数)非常慢,因此总是有可能在后仿真过程中发现错误。

- 📣您有任何问题,都可以在评论区和我交流📃!

- 📣本文由 孤独的单刀 原创,首发于CSDN平台🐵,博客主页:wuzhikai.blog.csdn.net

- 📣您的支持是我持续创作的最大动力!如果本文对您有帮助,还请多多点赞👍、评论💬和收藏⭐!

相关文章:

ASIC-WORLD Verilog(2)FPGA的设计流程

写在前面 在自己准备写一些简单的verilog教程之前,参考了许多资料----asic-world网站的这套verilog教程即是其一。这套教程写得极好,奈何没有中文,在下只好斗胆翻译过来(加了自己的理解)分享给大家。 这是网站原文&…...

数字化体验时代,企业如何做好内部知识数字化管理

随着数字化时代的到来,企业内部的知识管理也面临着新的挑战和机遇。数字化技术的应用,可以极大地提高企业内部知识的数字化管理效率和质量,从而提升企业内部的工作效率、员工满意度和企业竞争力。本文将从数字化时代的背景出发,探…...

Qt5.12實戰之Linux靜態庫與動態庫多文件生成a與so文件並調用

1.編輯並輸入內容到test.cpp與test2.cpp test.cpp #include <stdio.h> int func() {return 888; } test2.cpp #include <stdio.h> int func2() {return 999; } 將test.cpp與test2.cpp編譯成目標文件: g -c test.cpp test2.cpp 一次性生成目標文件…...

Spring 之初始化前中后详解

Spring 框架是一个非常流行的 Java 框架,它提供了一种轻量级的、可扩展的方式来构建企业级应用程序。在 Spring 的生命周期中,有三个重要的阶段,即初始化前、初始化、初始化后。这篇文章将详细介绍这些阶段,并提供相应的源代码示例…...

企业数字化转型路上的陷阱有哪些

近年来,随着科技的快速发展,越来越多的企业开始了数字化转型的征程,希望通过数字化技术来提高企业的效率、降低成本、提升竞争力。然而,数字化转型也存在许多陷阱,如果不注意,可能会导致企业陷入困境。下面…...

Baumer工业相机堡盟工业相机如何联合BGAPISDK和OpenCV实现图像的直方图算法增强(C++)

Baumer工业相机堡盟工业相机如何联合BGAPISDK和OpenCV实现图像的直方图算法增强(C) Baumer工业相机Baumer工业相机使用图像算法增加图像的技术背景Baumer工业相机通过BGAPI SDK联合OpenCV使用图像增强算法1.引用合适的类文件2.BGAPI SDK在图像回调中引用…...

面试官:“你会组件化开发操作吗?它的优势在哪?”

随着 Android 版本的不断更新升级和用户对 APP 产品需求技术越来越高,相对的各大公司对 Android 开发者们设置的招聘门槛也越来越高。 至于如何去看一个开发者水平的高低,一般看面试官会怎么问,会问哪些部分的技术内容? 一般公司…...

腾讯新增长,AI扛大旗?

经历了疫情期间的低谷与波折,腾讯正在恢复它的活力。 3月22日,腾讯发布了2022年第四季度及全年财报。财报显示,2022全年营收为5546亿元人民币,归母净利润(Non-IFRS)为1156亿元人民币;2022年腾讯第四季度的营收为1450亿…...

项目6:实现数据字典的展示与缓存

项目6:实现数据字典的展示与缓存 1.数据字典如何展示? 2.前后端如何设计? 3.前端设计代码? 4.后端设计代码? 5.实现数据字典缓存到redis 项目6:实现数据字典的展示与缓存 1.数据字典如何展示? ①数据字典展示 树形结构②...

JsNode算法题acm模式输入

js分为jsNode和JsV8两种输入输出方式,一般的执行代码还是一样的 牛客是两种都支持 华为的题目大多只支持jsNode 本文主要介绍jsNode的输入 JsNode 首先他是逐行输入的,就和py差不多,一定是每行每行地输入,用字符串line&#x…...

Javaweb小练习---在JSP中使用Javabean访问数据库完成用户信息的简单添加

Javaweb小练习---在JSP中使用Javabean访问数据库完成用户信息的简单添加 目录 Javaweb小练习---在JSP中使用Javabean访问数据库完成用户信息的简单添加 0.创建数据库 1. 在resources目录下创建db.properties文件 2. /** * 获取链接与释放资源的工具类--JdbcUtil类 */ 3…...

(十七)排序算法-基数排序

1 基本介绍 1.1 概述 (1)基数排序(radix sort)属于“分配式排序”,顾名思义,它是通过键值的各个位的值,将要排序的元素分配至某些“桶”中,达到排序的作用。 (2&#x…...

详解)

JMM之先行发生原则(happens-before)详解

1、概述 在JMM规范下,如果一个操作执行的结果需要对另一个操作可见,那么这两个操作之间必须存在happers-before(先行发生)原则。 例如 int x 10 ; int y x; 这两行代码中第二个操作 yx ,因为需要将x值赋值给y,所以第一行代码的…...

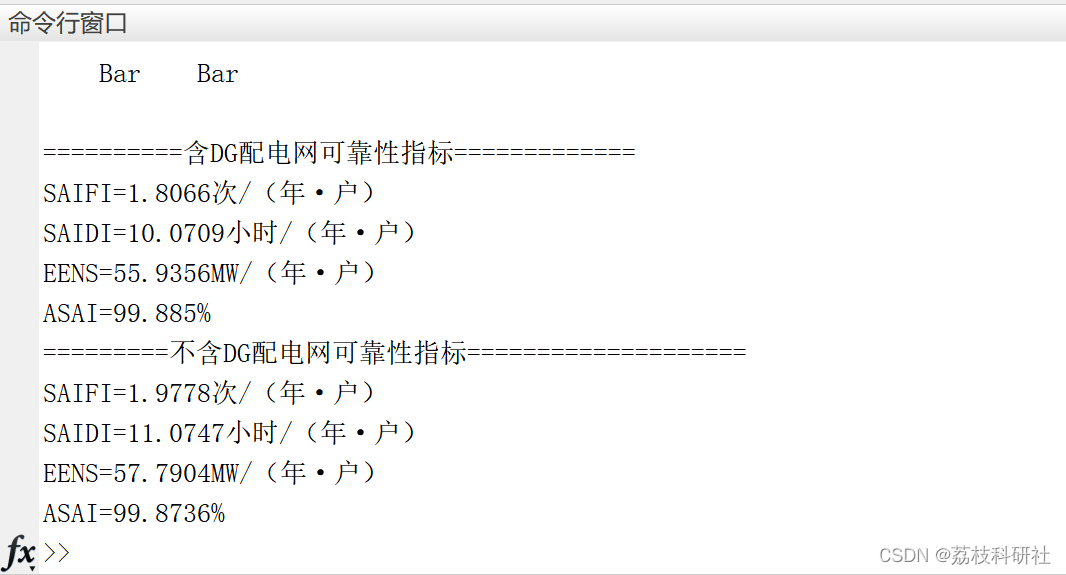

含分布式电源的配电网可靠性评估研究(Matlab代码实现)

💥💥💞💞欢迎来到本博客❤️❤️💥💥 🏆博主优势:🌞🌞🌞博客内容尽量做到思维缜密,逻辑清晰,为了方便读者。 ⛳️座右铭&a…...

安全加固服务是什么?哪些行业需要做?

安全加固服务是什么?安全加固服务是一种针对企业信息系统、网络设备、应用程序等进行安全加固和优化的服务。安全加固服务的主要目的是保障企业信息系统的安全性和稳定性,有效防范各类网络攻击和安全威胁。 安全加固服务是什么?通常包括以下…...

好程序员:Java书籍推荐,程序员必看的5本Java书籍,赶紧收藏!

今天好程序员给大家推荐5本Java书籍,各大高校都在使用(具体名单如下),所有学习Java的程序员都不应该错过! 第一本Java书籍《Java EE(SSM框架)企业应用实战》 本书全面介绍了JavaEE中MyBatis、Sp…...

maven将jar包添加到本地仓库

第一步:下载需要添加的jar包 可以在maven库中查找下载,也可以在对应官网下载 maven库网址:https://mvnrepository.com/ 找到对应版本的jar包下载 第二步:将下载的jar包放到指定位置(位置自己指定)…...

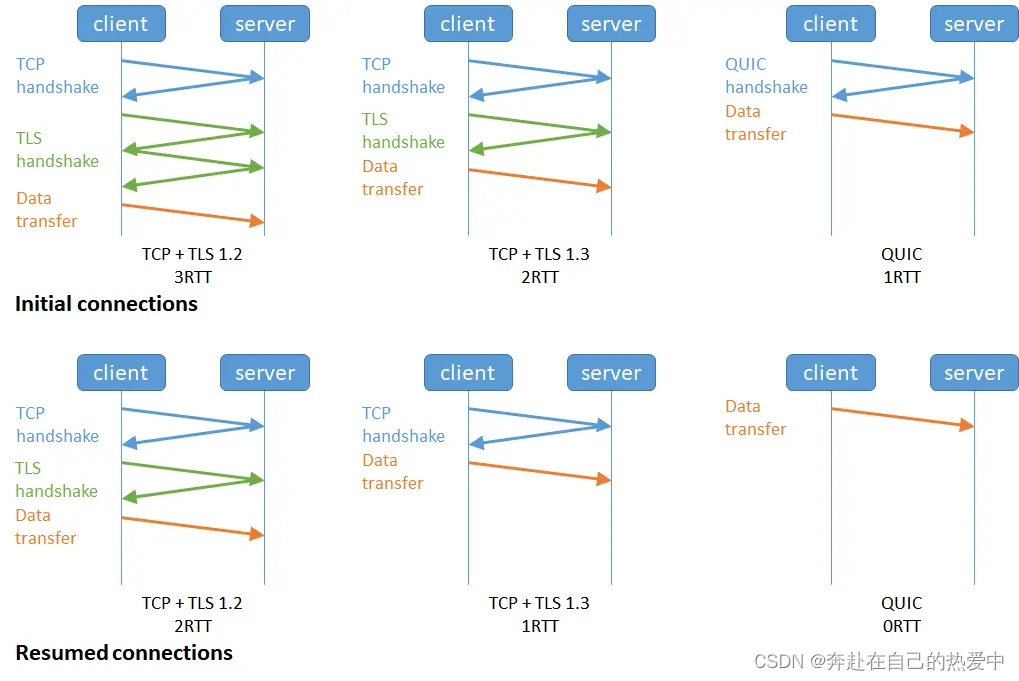

4.12--计算机网络之TCP篇之TCP 协议的缺陷+如何基于 UDP 协议实现可靠传输?--(复习+大总结)---沉下心来(加油呀)

TCP 协议四个方面的缺陷: 1.升级 TCP 的工作很困难; TCP 协议是在内核中实现的,应用程序只能使用不能修改,如果要想升级 TCP 协议,那么只能升级内核。 而升级内核这个工作是很麻烦的事情 2.TCP 建立连接的延迟&#x…...

数据库网络编程

数据库网络编程是一个重要的领域,它涉及到如何使用编程语言与数据库进行交互,以及如何设计和实现网络应用程序。在这篇文章中,我将探讨数据库网络编程的基础知识、常用技术和实践经验,以及一些应用案例和未来发展趋势。 一、基础…...

为什么现代企业都在使用ERP系统 它有哪些优势

随着科技的不断发展,企业管理方式也在不断地发生改变。在这个信息化的时代,企业要想取得成功,必须要善于利用先进的信息化技术工具。其中,ERP系统是企业管理中不可或缺的重要工具。本文将探讨现代企业为什么会使用ERP系统…...

终极指南:3分钟快速安装Windows官方包管理器Winget

终极指南:3分钟快速安装Windows官方包管理器Winget 【免费下载链接】winget-install Install WinGet using PowerShell! Prerequisites automatically installed. Works on Windows 10/11 and Server 2019/2022. 项目地址: https://gitcode.com/gh_mirrors/wi/win…...

GitGitHub实操图文详解教程(06)—git status命令)

(最新版)GitGitHub实操图文详解教程(06)—git status命令

版权声明 本文原创作者:谷哥的小弟 作者博客地址:http://blog.csdn.net/lfdfhl 1. 应用场景 git status 是 Git 中最常用的命令之一,用于查看当前仓库的状态。它能够告诉你: 当前所在分支 哪些文件被修改但未暂存 哪些文件已暂存但尚未提交 哪些文件未被 Git 跟踪 对于初学…...

目标检测Neck进化史:从FPN到BiFPN,为什么PAN是承上启下的关键?

目标检测Neck进化史:从FPN到BiFPN,为什么PAN是承上启下的关键? 在计算机视觉领域,目标检测一直是核心任务之一。随着深度学习的发展,目标检测器的架构逐渐形成了Backbone-Neck-Head的标准范式。其中,Neck作…...

ROS2进阶实践 -- 从零构建模块化差速机器人模型 -- 掌握xacro宏定义与参数化设计

1. 为什么需要xacro宏定义与参数化设计 当你第一次用URDF给机器人建模时,可能会觉得这种XML格式的描述方式很直观。但随着模型复杂度提升,问题就来了——我最近给一个差速机器人添加传感器时,发现URDF文件膨胀到了500多行,其中光是…...

别再只调API了!深入XXL-Job时间轮源码,手把手带你搞懂任务触发与调度过期的那些坑

深入XXL-Job时间轮:从源码解析任务调度与过期处理的实战指南 在分布式任务调度领域,XXL-Job以其轻量级、易扩展的特性成为众多Java项目的首选方案。但当我们从简单的API调用者转变为架构设计者时,仅满足于配置层面的理解显然不够。本文将带您…...

TPS5430玩点不一样的:15V输入如何生成一个干净的-12V电源?电路设计与极性电容防炸指南

TPS5430负压生成实战:从15V到-12V的电路设计精要 在模拟电路设计中,双电源供电系统(如12V)是音频设备、运算放大器和高精度ADC的常见需求。然而,当系统仅提供单路正电压输入时,如何高效生成稳定的负电压轨成…...

技术演进:从PDH到SDH的WAN接口变迁与POS/CPOS应用解析

1. 从铜缆到光纤:PDH与SDH的技术演进之路 记得我第一次接触E1接口是在2008年,当时在一家电信机房看到一排闪着绿色指示灯的设备,老师傅告诉我这就是承载着电话业务的"2M线"。那时候我还不知道,这个看似简单的接口背后&a…...

为开发者工具注入情感分析能力:开源库ai-devtools-sentiment实战指南

1. 项目概述:一个为开发者工具注入情感分析能力的开源库最近在折腾一些开发者工具,比如代码审查机器人、文档生成器或者IDE插件,我总感觉它们冷冰冰的。它们能告诉你代码有语法错误,能提示你某个API已废弃,但它们无法感…...

AnyLogic新手避坑指南:搞懂‘空间逻辑’和‘层’,你的第一个行人仿真模型就成功了一半

AnyLogic行人仿真空间逻辑完全解析:从概念混淆到精准建模 第一次打开AnyLogic的行人仿真模块时,那个充满蓝色网格的3D空间和密密麻麻的参数面板,很容易让人产生一种错觉——这不过是个"高级版流程图工具"。直到亲眼目睹自己精心设计…...

WorkshopDL:打破平台壁垒,免费获取Steam创意工坊模组的终极方案

WorkshopDL:打破平台壁垒,免费获取Steam创意工坊模组的终极方案 【免费下载链接】WorkshopDL WorkshopDL - The Best Steam Workshop Downloader 项目地址: https://gitcode.com/gh_mirrors/wo/WorkshopDL 还在为Epic、GOG等平台购买的游戏无法使…...