Vivado 下 IP核 之ROM 读写

目录

Vivado 下 IP核 之ROM 读写

1、实验简介

2、ROM IP 核简介

3、ROM IP 核配置

3.1、创建 ROM 初始化文件

3.2、单端口 ROM 的配置

3.3、双端口 ROM 的配置

3.4、ROM IP 核的调用

(1)ROM 顶层模块代码

(2)ROM IP 核仿真

(3)仿真结果

Vivado 下 IP核 之ROM 读写

1、实验简介

本实验基于 Xinlinx 黑金 AX7A035 FPGA 开发板在Vivado平台下,介绍如何使用 FPGA 内部的 ROM 以及程序对该 ROM 的数据读操作。

2、ROM IP 核简介

本小节为大家介绍一种较为常用的存储类 IP 核——ROM 的使用方法。ROM 是只读存储器(Read-Only Memory)的简称,是一种只能读出事先所存数据的固态半导体存储器。其特性是一旦储存资料就无法再将之改变或删除,且资料不会因为电源关闭而消失。而事实上在 FPGA 中通过 IP 核生成的 ROM 或 RAM 调用的都是 FPGA 内部的 RAM 资源,掉电内容都会丢失(这也很容易解释,FPGA 芯片内部本来就没有掉电非易失存储器单元)。用 IP 核生成的 ROM 模块只是提前添加了数据文件(.coe 格式),在 FPGA 运行时通过数据文件给 ROM 模块初始化,才使得 ROM 模块像个“真正”的掉电非易失存储器;也正是这个原因,ROM 模块的内容必须提前在数据文件中写死,无法在电路中修改。

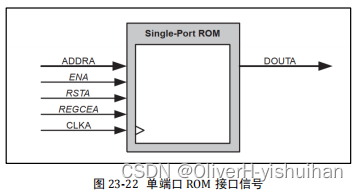

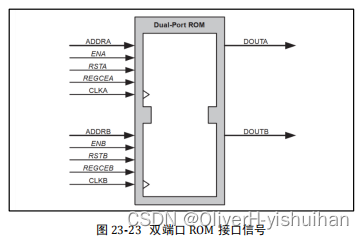

Xilinx 推出的 ROM IP 核分为两种类型:单端口 ROM(Single-Port Rom)和双端口ROM(Dual-Port ROM)。对于单端口 ROM 提供一个读地址端口和一个读数据端口,只能进行读操作;双端口 ROM 与单端口 ROM 类似,区别是其提供两个读地址端口和两个读数据端口,基本上可以看做两个单口 RAM 拼接而成。下面是 ROM 不同配置模式存储器的接口信号图,如图 23-22、图 23-23 所示。

上图中的接口信号我们并不是全部需要用到,因为我们配置时,有些信号是可以不创建的。所以很多接口信号我们可以不用管,只需管我们需要用的信号即可,而什么信号是我们需要用到的呢?这在我们调用完 IP 核后,是可以生成其例化模块的,到时候就可以看到我们需要控制的信号了。

3、ROM IP 核配置

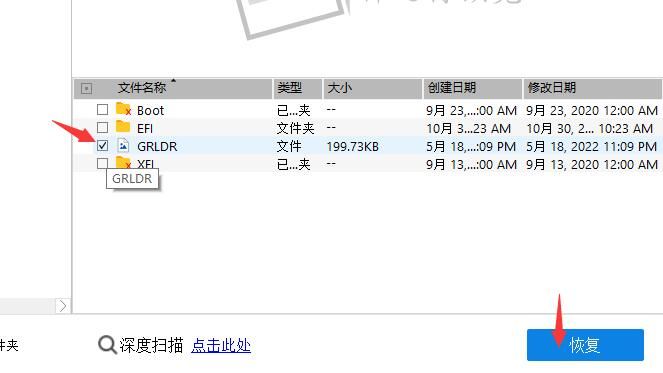

3.1、创建 ROM 初始化文件

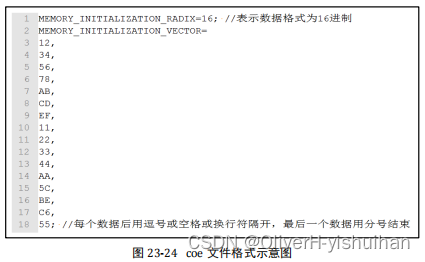

ROM 作为只读存储器,在进行 IP 核设置时需要指定初始化文件,即写入存储器中的 数据,数据要以规定的格式才能正确写入 ROM,这种格式就是 coe 文件。coe 是Vivado 规定的一种文件格式,文件格式示意图,具体见图 23-24。

如上图 23-24 所示,该文件的格式较为简单,第一行是定义数据的格式,其中 16 表示数据格式为 16 进制,也可将数据格式定义为二进制和八进制,只需将 16 改为 2 或 8 即可。其中第 3 到第 18 行是 16*8bit 大小 ROM 的初始化数据。

3.2、单端口 ROM 的配置

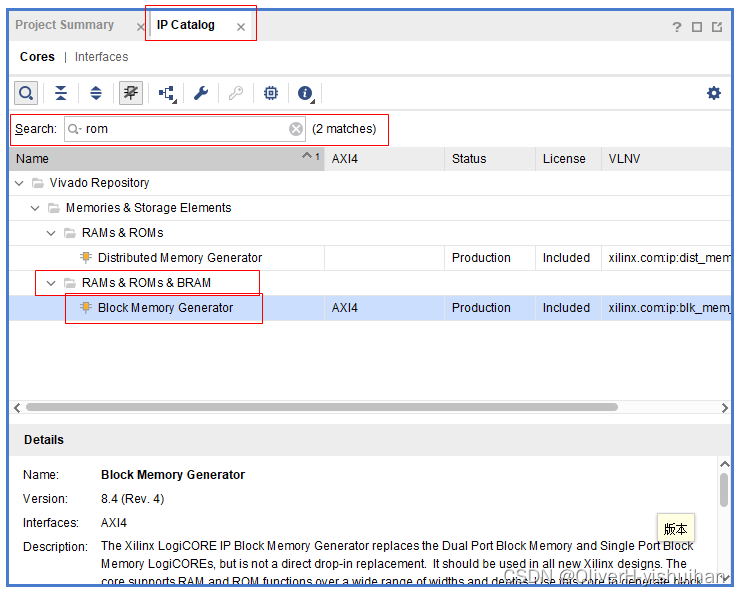

(1)新建一个 ip_rom 工程后,首先点击 “IP Catalog”,点击后会出现 IP Catalog 页面;我们在 IP 核的搜索框中搜索 “rom”,双击 RAM & ROM & BRAM 核下的 “Block Memory Generator”。

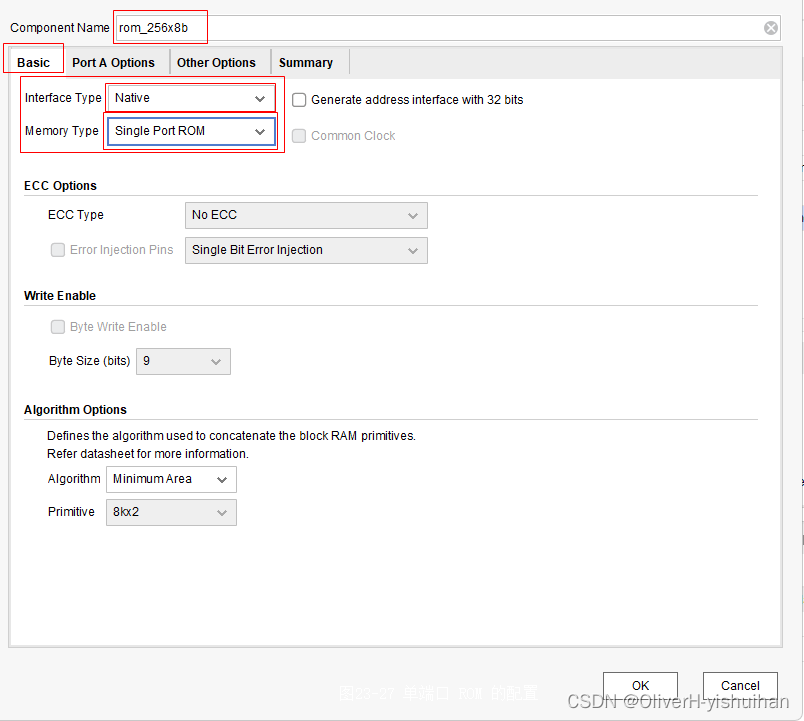

(2)双击之后会出现如下图所示的配置界面。在 "Basic" 栏目下,将 “Component Name” 改为 "rom_256x8b"(rom 是我们调用的 IP 核,256 是调用的 IP 核容量,8 是调用的 IP 核数据位宽。这里这样命名是为了方便识别我们创建的 IP 核类型及资源量)。“Interface Type” 保持默认 "Native "。

在“Memory Type” 框中选择存储器类型,可供选择的类型有:Single Port RAM(单端口 RAM)、 Simple Dual Port RAM(简单双口 RAM)、True Dual Port RAM(真双口 RAM)、Singl Port ROM(单端口 ROM)、Doul Port ROM(双端口 ROM)。这里我们选择“Single Port Rom”单端口 ROM。 在 Algorithm 一栏中可选择用于实现内存的算法,其中 Minimum Area 为最小面积 算法;Low Power 为低功耗算法;Fixed Primitives 为固定单元算法。这里我们按默认选择 Minimum Area 即可。

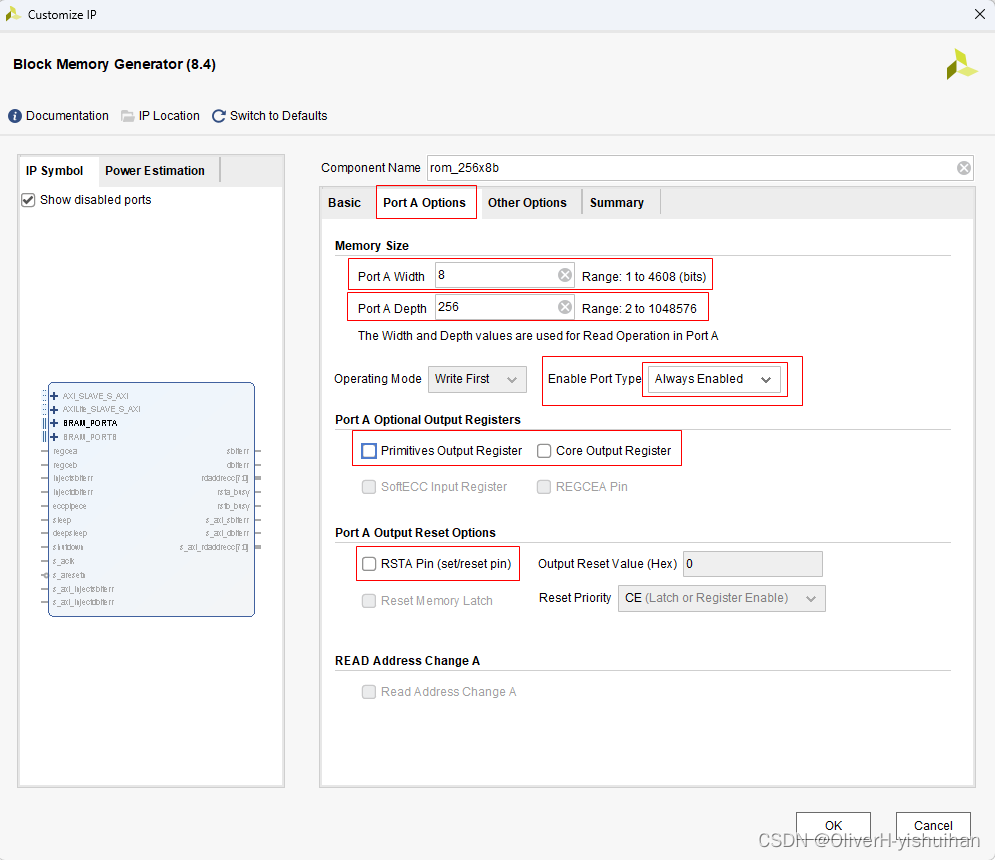

(3)切换到 “Port A Options ”栏目下,设置存储数据的位宽,将 ROM 位宽 "Port A Width" 改为 8;设置数据深度,将 ROM 深度 "Port A Depth" 改为 256,这样我们设置的 ROM 和最大能存储的数据即为 256 x 8bit。(注意:设置的容量需大于我们需要写入的数据文件的数据量);使能管脚 "Enable Port Type" 选择是否创建端口使能信号,这里我们不创建,选择“Always Enabled”始终 使能。如下图:

-

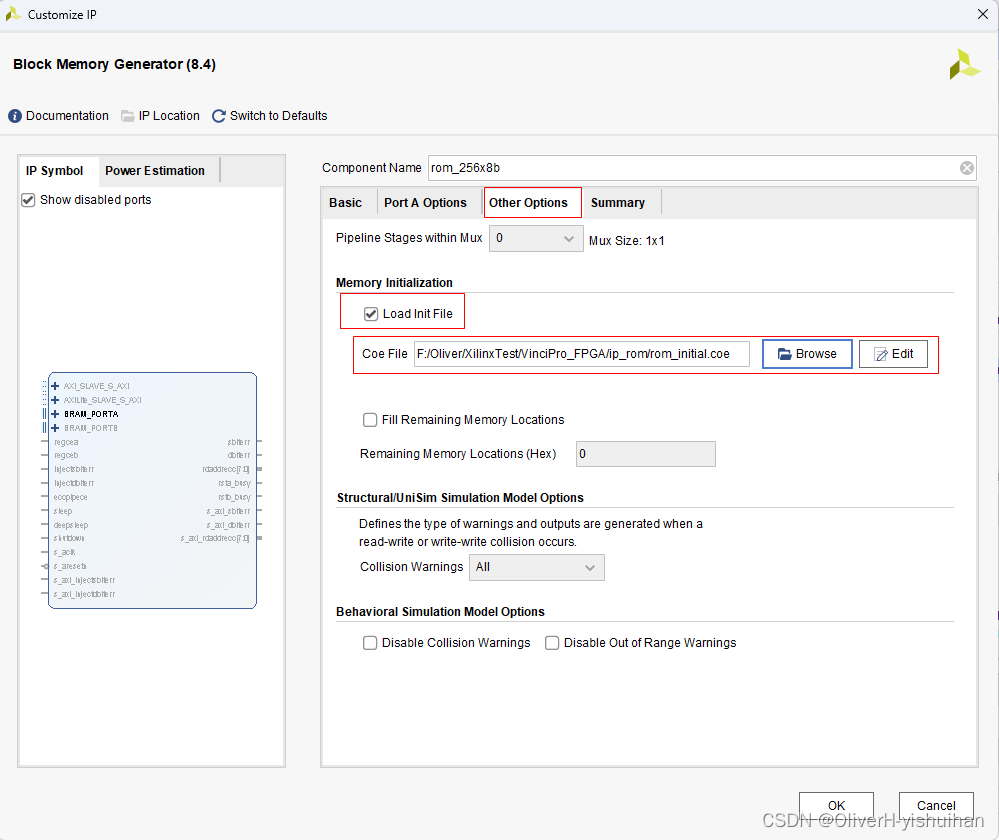

加载数据文件,将 .coe 文件保存到生成的 Rom IP 核中

(4)切换到“Other Options”栏目,加载数据文件,将 .coe 文件保存到生成的 Rom IP 核中,即我们前面讲到的 ROM 初始化文件, 由于 ROM 是只读存储器,所以我们必须添加 ROM 初始化文件才行。勾选上“Load Init File”点击Browse 进行添加.coe 初始化文件,文件格式我们之前已经讲解,大家可根据自己想存入的数据进行生成该文件。该页面其余按默认设置即可。

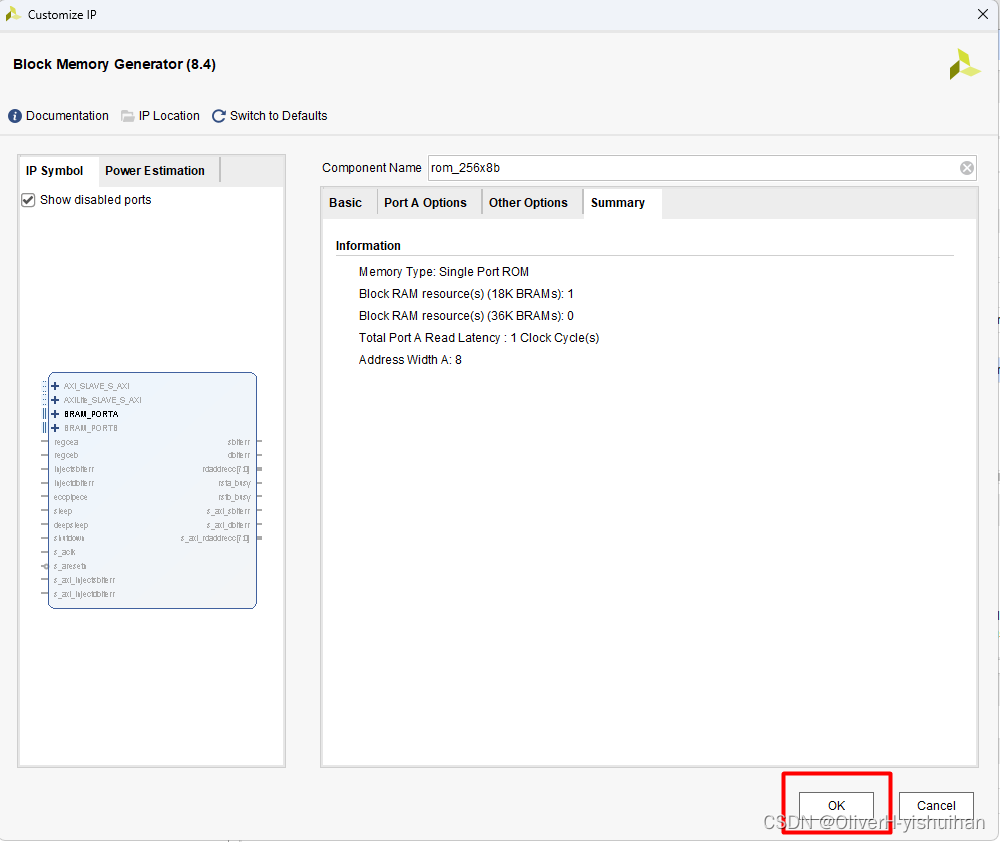

(5)切换到“Summary”页面,在 “Summary” 页面,从“IP Symbol”窗口可以看到我们最终创建的 ROM 核的端口信号。点击 “OK” 完成 ROM 的创建设置。

(6)创建之后接下来跳出如下图所示界面,我们点击“Generate” 生成 ip 核。

(7)接下来出现如下图所示界面,我们点击“OK”完成生成。

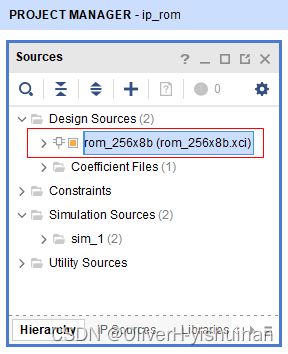

(8)生成之后可以在工程中看到我们正常的 IP 核,双击 IP 核可进入配置界面,对 IP 核的相关参数进行更改。

3.3、双端口 ROM 的配置

单端口 ROM 的配置步骤讲解完之后,下面介绍一下双端口 ROM 的配置步骤。

(1)该步骤前面的步骤与单端口 ROM 的配置是一样的,到该页面我们在 Memory Type 选择 “Dual Port ROM” 双端口 ROM,其余设置不变。如图 23-34 所示

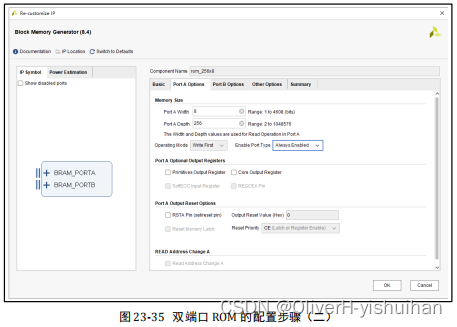

(2)切换到 “Potr A Options” 页面,如图 23-35 所示,该窗口是对端口 A 的设置,该页面的设置我们跟单端口 ROM 的设置一样即可。

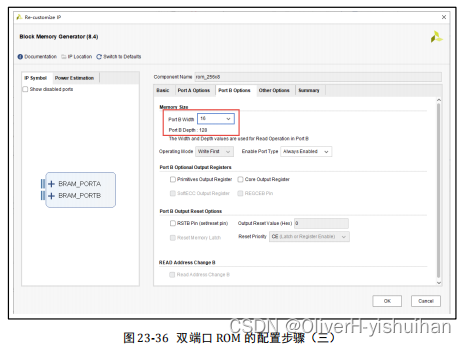

(3)切换到 “Potr B Options” 页面,如图 23-36 所示,该窗口是对端口 B 的设置,这也是双端口 ROM 与单端口 ROM 最大的区别,多了一组端口。这里我们只需对 B 端口的数据位宽设置即可,数据深度会根据端 口 A 的设置自动设置。例如我们端口 A 设置的数据位宽为 8bit,深度为 256;而我们 B 端口设置的数据位宽为 16bit,则其深度即为 128,其数据总量是一样的。其余设置与端口 A 设置一样即可。

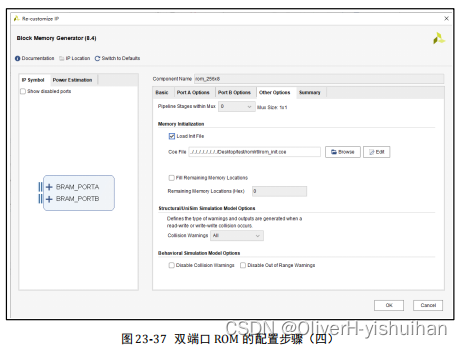

(4)切换到“Other Options”页面,如图 23-37 所示,该页面与单端口 ROM 配置一样。

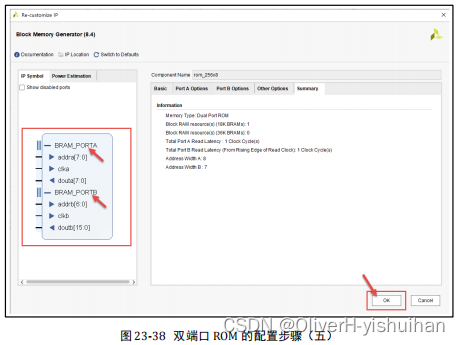

(5)切换到“Summary”页面,如图 23-38 所示,在“Summary”页面,从“IP Symbol”窗口可以看到我们最终创建的 ROM 核的端口信号。可以看到其相比单端口 ROM 来说多了一组端口 B 信号。点击“OK”完成 ROM 的创建设置。接下来步骤与单端口 ROM 一样,就不再重复介绍。

3.4、ROM IP 核的调用

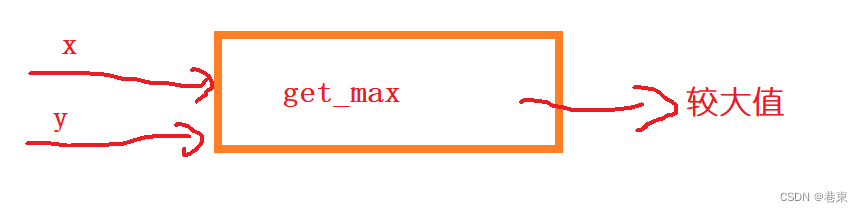

在配置 ROM 核之前,我们先生成一个 ROM 的初始化文件(生成数据是十进制数 0~255,256 × 8bit),即我们往地址 0~255 存入十进制数据 0~255。初始化文件生成之后我们按单端口 ROM 的配置步骤配置一个单端口 ROM。

ROM IP 核配置完成后我们对它进行调用,通过仿真来观察输出信号的变化。验证的方法和例子有很多,后面我们还会在实战项目中使用到这个 IP 核。为了让大家能够清晰的看到 ROM IP 核信号的变化,RTL 代码的顶层只有端口列表和 ROM IP 核的实例化,其中:

- RTL 代码顶层的输入信号有:50MHz 的系统时钟 sys_clk、输入 ROM 的读地址。这些输入信号需要在 Testbench 中产生激励。

- RTL 代码顶层的输出信号有:ROM 的输出数据。

(1)ROM 顶层模块代码

ROM 顶层模块参考代码,如下所示:

`timescale 1ns / 1ps

//

// Company:

// Engineer:

//

// Create Date: 2023/05/19 21:35:56

// Design Name:

// Module Name: ip_rom

// Project Name:

// Target Devices:

// Tool Versions:

// Description:

//

// Dependencies:

//

// Revision:

// Revision 0.01 - File Created

// Additional Comments:

//

//module ip_rom(

// input sys_clk, //50MHz系统时钟(一个周期是20ns:1/50MHz=0.02us=20ns)//differential system clocks //200MHz系统时钟(一个周期是5ns:1/200MHz=0.005us=5ns)input sys_clk_p, // Differential input clock 200Mhzinput sys_clk_n, // Differential input clock 200Mhzinput wire [7:0] addra , //输入 rom 地址output wire [7:0] douta //输出 rom 数据);//*********差分时钟这么处理***START******************

wire sys_clk;

//差分输入时钟缓冲器-黑金FPGA

IBUFDS sys_clk_ibufgds //generate single end clock

(.O (sys_clk ), //Differential clock converted to single terminal clock.I (sys_clk_p ),.IB (sys_clk_n )

);

//*********差分时钟这么处理*****END*******************//********************************************************************//

//*************************** Instantiation **************************//

//********************************************************************//

//rom_256x8b_inst

rom_256x8b u_rom_256x8b

(

// .clka (sys_clk ), // input clka.clka (sys_clk_p ), // input clka.addra (addra ), // input [7 : 0] addraendmodule.douta (douta ) // output [7 : 0] douta

);endmodule

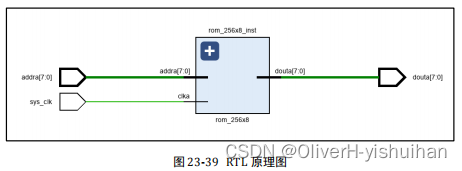

根据上面 RTL 代码综合出的 RTL 原理图如图 23-39 所示。

(2)ROM IP 核仿真

仿真参考代码如下所示:

`timescale 1ns / 1ps

//

// Company:

// Engineer:

//

// Create Date: 2023/05/19 21:45:01

// Design Name:

// Module Name: tb_ip_rom

// Project Name:

// Target Devices:

// Tool Versions:

// Description:

//

// Dependencies:

//

// Revision:

// Revision 0.01 - File Created

// Additional Comments:

//

//module tb_ip_rom();//********************************************************************//

//****************** Parameter and Internal Signal *******************//

//********************************************************************////parameter T = 20; //50Mhz系统时钟,一个周期为20ns

parameter T = 5; //200Mhz系统时钟,一个周期为5ns//reg define

//reg sys_clk; //时钟信号

reg sys_clk_p; //时钟信号

wire sys_clk_n;

reg sys_rst_n ; //复位信号

reg [7:0] addra ;//wire define

wire [7:0] douta ;//********************************************************************//

//***************************** Main Code ****************************//

//********************************************************************////对 sys_clk, sys_rst 赋初值,并模拟按键抖动

initial begin

// sys_clk <= 1'b1; //初始时钟为低电平sys_clk_p <= 1'b1; //初始时钟为低电平sys_rst_n <= 1'b0 ; //复位信号初始为低电平#200 //等待200ns后sys_rst_n <= 1'b1 ; //复位信号拉高

end//sys_clk:模拟系统时钟,每 10ns 电平取反一次,周期为 20ns,频率为 50Mhz

//always #10 sys_clk = ~sys_clk;

//always #(T/2) sys_clk <= ~sys_clk; //每半个周期后,电平取反一次。

always #(T/2) sys_clk_p <= ~sys_clk_p; //每半个周期后,电平取反一次。

assign sys_clk_n = ~sys_clk_p;//让地址从 0~255 循环

always @(posedge sys_clk_p or negedge sys_rst_n)if(sys_rst_n == 1'b0)addra <= 8'd0;else if(addra == 8'd255)addra <= 8'd0;elseaddra <= addra + 1'b1;//********************************************************************//

//*************************** Instantiation **************************//

//********************************************************************////rom_inst

ip_rom u_ip_rom

(

// .sys_clk (sys_clk ), //50Mhz系统时钟,一个周期为20ns.sys_clk_p (sys_clk_p ), //200Mhz系统时钟(差分时钟),一个周期为5ns.addra (addra ), //输入 rom 地址.douta (douta ) //输出 rom 数据

);endmodule

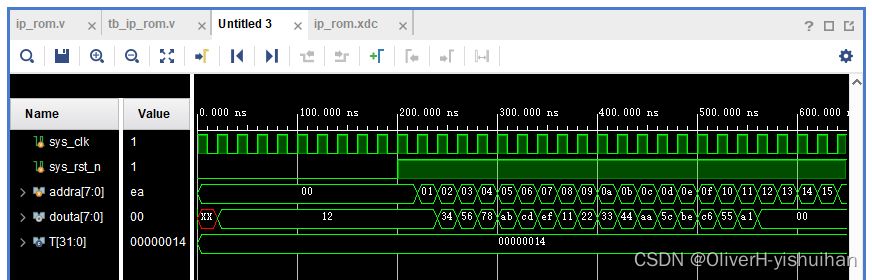

(3)仿真结果

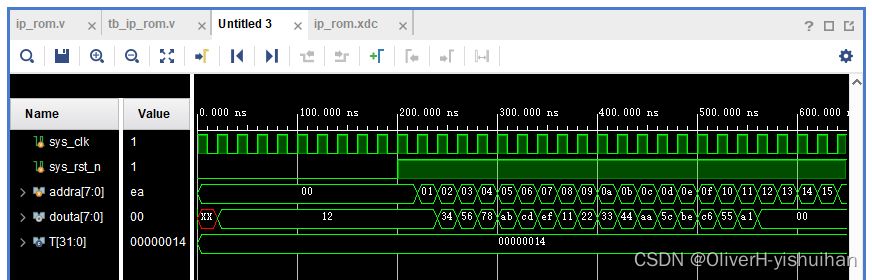

对代码进行仿真,仿真波形如下所示。

从图中可以很清楚的看到 ROM IP 核地址与数据的关系。在前面我们知道我们往地址 0~255 存入的数据是 0~255,从波形图中可以看到当读时钟的上升沿采到地址时,在下一刻就会输出该地址存储的数据。

4、添加约束文件 .xdc

添加约束文件 ip_rom.xdc,添加约束文件.xdc,详细步骤见:Vivado 下 LED 流水灯实验_OliverH-yishuihan的博客-CSDN博客中的 “4.3、添加 XDC管脚约束文件”

约束文件 ip_rom.xdc 的具体内容如下:

############## NET - IOSTANDARD #######黑金-FPGA##############

set_property CFGBVS VCCO [current_design]

set_property CONFIG_VOLTAGE 3.3 [current_design]

#############SPI Configurate Setting#################

set_property BITSTREAM.CONFIG.SPI_BUSWIDTH 4 [current_design]

set_property CONFIG_MODE SPIx4 [current_design]

set_property BITSTREAM.CONFIG.CONFIGRATE 50 [current_design]

############## clock define 时钟引脚、电平信号约束 #######黑金-FPGA##############

create_clock -period 5 [get_ports sys_clk_p]

set_property PACKAGE_PIN R4 [get_ports sys_clk_p]

set_property IOSTANDARD DIFF_SSTL15 [get_ports sys_clk_p]

##############reset key define#######################

set_property PACKAGE_PIN F15 [get_ports rst_n]

set_property IOSTANDARD LVCMOS33 [get_ports rst_n]相关文章:

Vivado 下 IP核 之ROM 读写

目录 Vivado 下 IP核 之ROM 读写 1、实验简介 2、ROM IP 核简介 3、ROM IP 核配置 3.1、创建 ROM 初始化文件 3.2、单端口 ROM 的配置 3.3、双端口 ROM 的配置 3.4、ROM IP 核的调用 (1)ROM 顶层模块代码 (2)ROM IP 核仿…...

朗诵素材-《诵四季诗韵,咏师恩师德》

女:中华五千年的悠久历史,孕育了底蕴深厚的民族文化。 男:华夏源远流长的经典诗文, 女:是文化艺苑中经久不衰的瑰宝。 男:在那些脍炙人口的诗句里,凝聚着华光熠熠的民族精魂。 女࿱…...

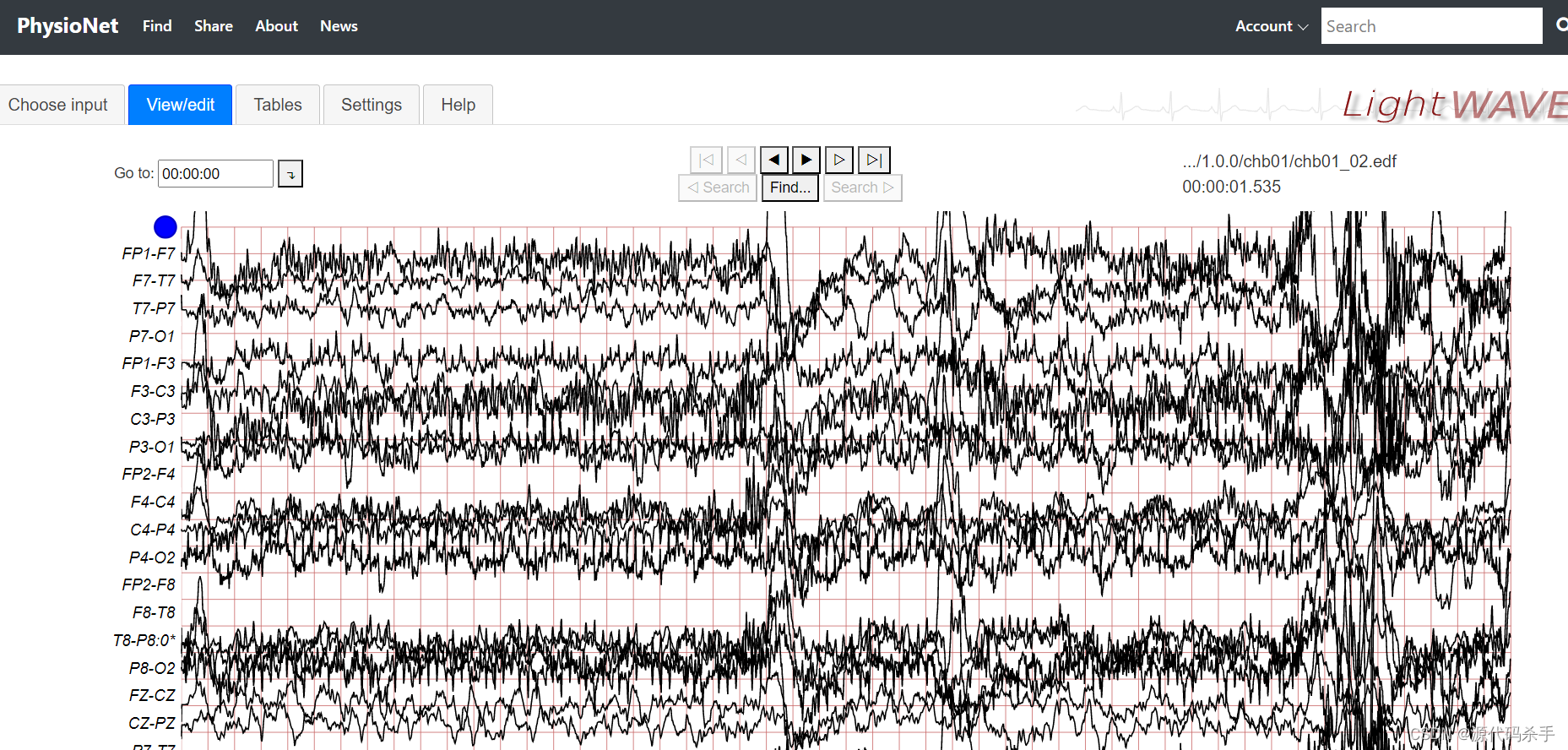

CHB-麻省理工学院头皮脑电图数据库

数据库介绍 该数据库在波士顿儿童医院收集,包括患有顽固性癫痫发作的儿科受试者的脑电图记录。受试者在停用抗癫痫药物后被监测长达几天,以表征他们的癫痫发作并评估他们手术干预的候选资格。 数据库链接:https://physionet.org/content/chb…...

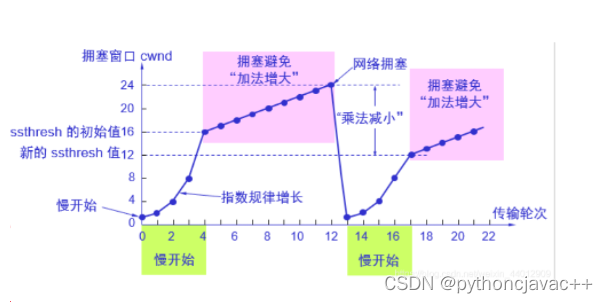

传输层协议

目录 传输层 端口号 端口号范围划分 认识知名端口号(Well-Know Port Number) netstat pidof UDP协议UDP协议端格式编辑 UDP的特点 面向数据报 UDP的缓冲区 UDP使用注意事项 基于UDP的应用层协议 TCP协议 TCP协议段格式 确认应答(ACK)机制 超时重传机制 连…...

公司新招了个字节拿36K的人,让我见识到了什么才是测试扛把子......

5年测试,应该是能达到资深测试的水准,即不仅能熟练地开发业务,而且还能熟悉项目开发,测试,调试和发布的流程,而且还应该能全面掌握数据库等方面的技能,如果技能再高些的话,甚至熟悉分…...

pytorch rpc如何实现分物理机器的model parallel

因为业务需要,最近接到一项任务,是如何利用pytorch实现model parallel以及distributed training。搜罗了网上很多资料,以及阅读了pytorch官方的教程,都没有可参考的案例。讲的比较多的是data parallel,关于model paral…...

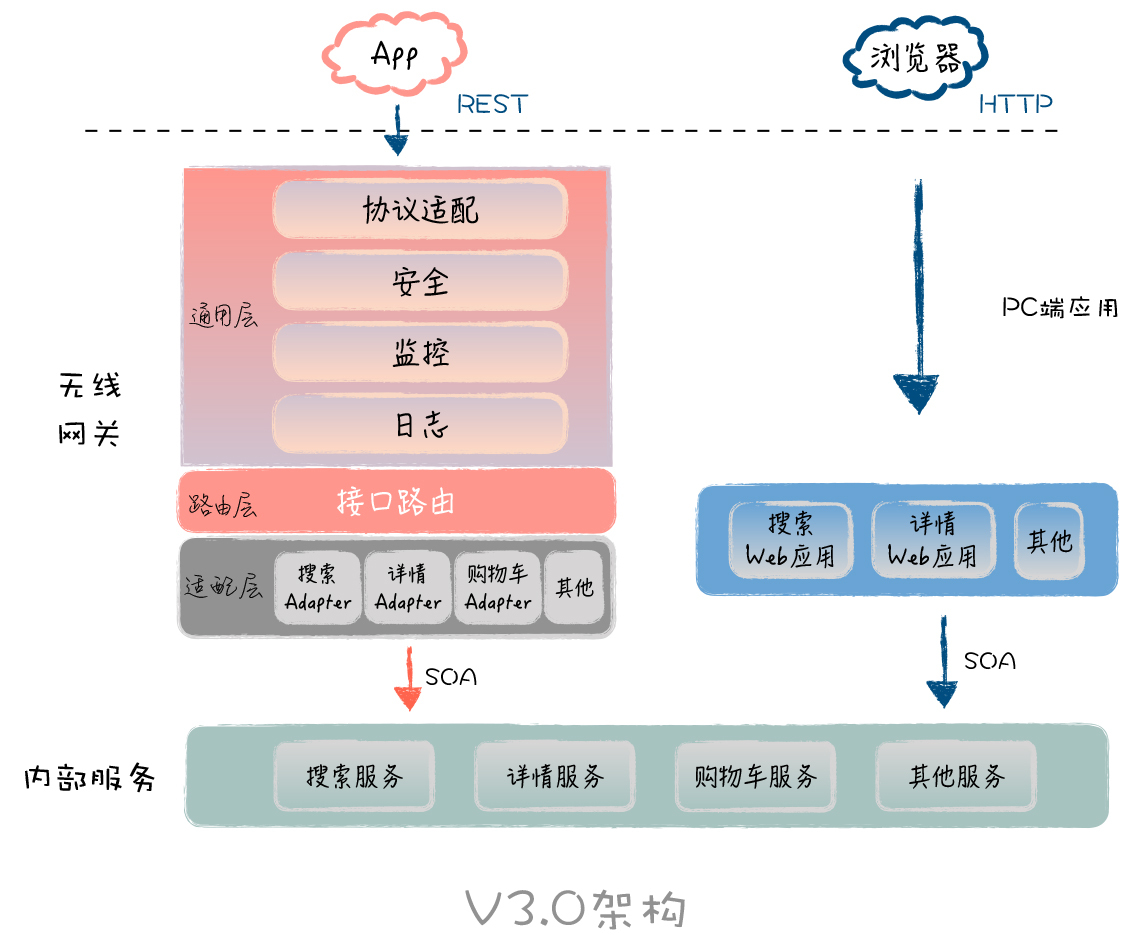

APP服务端架构的演变

大家好,我是易安! 早期2013年的时候,随着智能设备的普及和移动互联网的发展,移动端逐渐成为用户的新入口,各个电商平台都开始聚焦移动端App,如今经历了10年的发展,很多电商APP早已经没入历史的洪…...

EasyRecovery16适用于Windows和Mac的专业硬盘恢复软件

无论你对数据恢复了解多少, 我们将为您处理所有复杂的流程并简化恢复!适用于Windows和Mac的 专业硬盘恢复软件 硬盘数据无法保证绝对安全。有时会发生数据丢失,需要使用硬盘恢复工具。支持恢复不同存储介质数据:硬盘、光盘、U盘/移动硬盘、数…...

详解Jetpack Compose中的状态管理与使用

前言 引用一段官方描述,如下 由于 Compose 是声明式工具集,因此更新它的唯一方法是通过新参数调用同一可组合项。这些参数是界面状态的表现形式。每当状态更新时,都会发生重组。因此,TextField 不会像在基于 XML 的命令式视图中那…...

改进YOLOv7 | 头部解耦 | 将YOLOX解耦头添加到YOLOv7 | 涨点杀器

改进YOLOv7 | 头部解耦 | 将YOLOX解耦头添加到YOLOv7 论文地址:https://arxiv.org/abs/2107.08430 文章目录 改进YOLOv7 | 头部解耦 | 将YOLOX解耦头添加到YOLOv71. 解耦头原理2. 解耦头对收敛速度的影响3. 解耦头对精度的影响4. 代码改进方式第一步第二步第三步第四步第五步参…...

第七章 中断

中断是什么,为什么要有中断 并发是指单位时间内的累积工作量。 并行是指真正同时进行的工作量。 一个CPU在一个时间只能执行一个进程,任何瞬间任务只在一个核心上运行。 而CPU外的设备是独立于CPU的,它与CPU同步运行,CPU抽出一点…...

)

1116 Come on! Let‘s C(38行代码+详细注释)

分数 20 全屏浏览题目 作者 CHEN, Yue 单位 浙江大学 "Lets C" is a popular and fun programming contest hosted by the College of Computer Science and Technology, Zhejiang University. Since the idea of the contest is for fun, the award rules are f…...

深入学习《c语言函数》

📕博主介绍:目前大一正在学习c语言,数据结构,计算机网络。 c语言学习,是为了更好的学习其他的编程语言,C语言是母体语言,是人机交互接近底层的桥梁。 本章学习函数。 让我们开启c语言学习之旅吧…...

Pytorch从零开始实现Vision Transformer (from scratch)

Pytorch从零开始实现Vision Transformer 前言一、Vision Transformer架构介绍1. Patch Embedding2. Multi-Head Attention3. Transformer BlockFeed Forward 二、预备知识1. Einsum2. Einops 三、Vision Transformer代码实现0. 导入库1. Patch Embedding2. Residual & Norm…...

ES6函数新增了哪些扩展?

目录 一、参数二、属性函数的length属性name属性 三、作用域四、严格模式五、箭头函数 一、参数 ES6允许为函数的参数设置默认值 function log(x, y World) {console.log(x, y); }console.log(Hello) // Hello World console.log(Hello, China) // Hello China console.log(…...

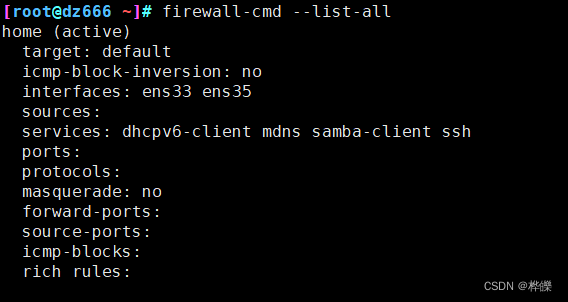

【firewalld防火墙】

目录 一、firewalld概述二、firewalld 与 iptables 的区别1、firewalld 区域的概念 三、firewalld防火墙默认的9个区域四、Firewalld 网络区域1、区域介绍2、firewalld数据处理流程 五、firewalld防火墙的配置方法1、使用firewall-cmd 命令行工具。2、使用firewall-config 图形…...

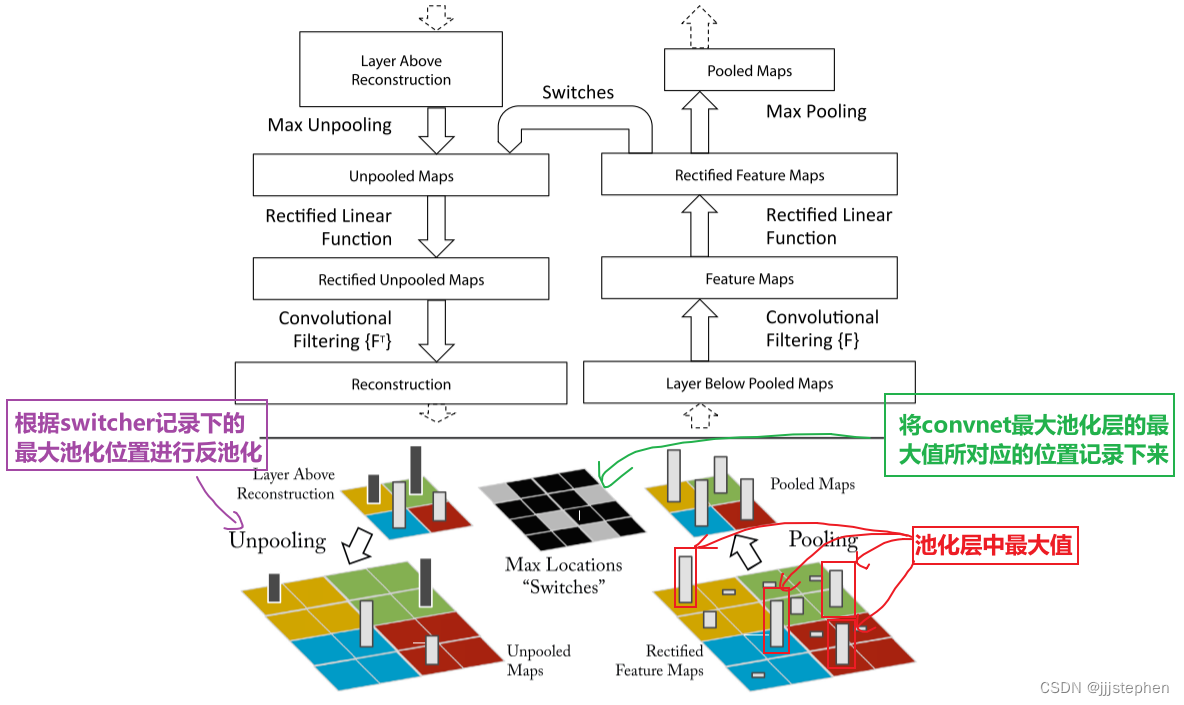

CNNs: ZFNet之CNN的可视化网络介绍

CNNs: ZFNet之CNN的可视化网络介绍 导言Deconvnet1. Unpooling2. ReLU3. Transpose conv AlexNet网络修改AlexNet Deconv网络介绍特征可视化 导言 上一个内容,我们主要学习了AlexNet网络的实现、超参数对网络结果的影响以及网络中涉及到一些其他的知识点࿰…...

云原生之深入解析Airbnb的动态Kubernetes集群扩缩容

一、前言 Airbnb 基础设施的一个重要作用是保证我们的云能够根据需求上升或下降进行自动扩缩容,我们每天的流量波动都非常大,需要依靠动态扩缩容来保证服务的正常运行。为了支持扩缩容,Airbnb 使用了 Kubernetes 编排系统,并且使…...

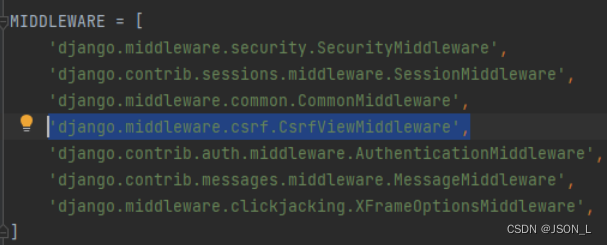

Django框架之模板其他补充

本篇文章是对django框架模板内容的一些补充。包含注释、html转义和csrf内容。 目录 注释 单行注释 多行注释 HTML转义 Escape Safe Autoescape CSRF 防止csrf方式 表单中使用 ajax请求添加 注释 单行注释 语法:{# 注释内容 #} 示例: {# 注…...

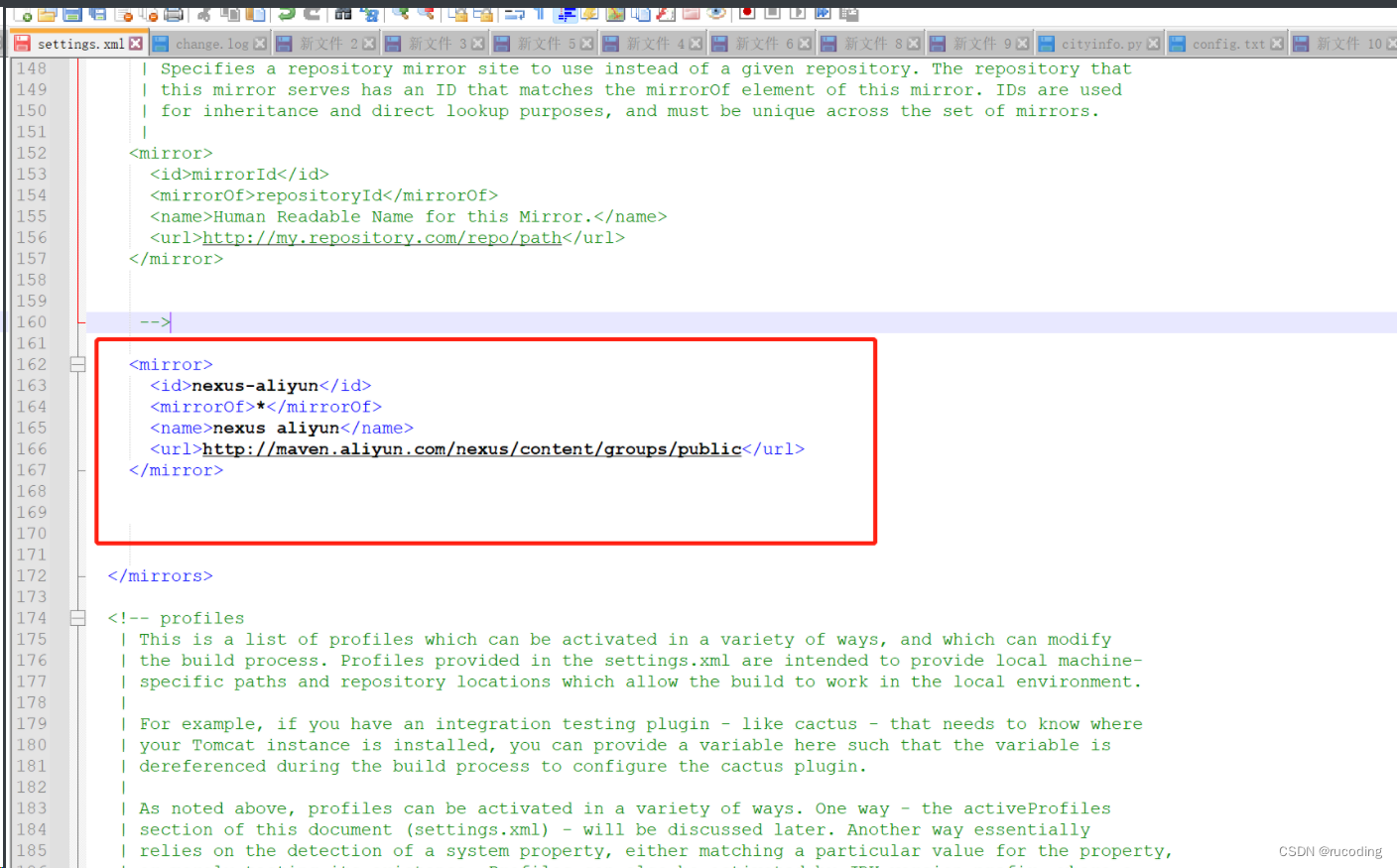

安装Maven 3.6.1:图文详细教程(适用于Windows系统)

一、官网下载对应版本 推荐使用maven3.6.1版本,对应下载链接: Maven3.6.1下载地址 或者,这里提供csdn下载地址,点击下载即可: Maven3.6.1直链下载 其他版本下载地址: 进入网址:http://mave…...

MVT协议深度解析:从Protobuf编码到GISBox实战,看它如何碾压传统栅格瓦片

MVT协议技术内幕:从二进制编码到百万级数据渲染实战 当我们打开手机地图App,双指放大查看小区楼栋轮廓时,很少有人会思考这流畅体验背后的技术革命。传统栅格瓦片就像打印在纸上的地图,放大后必然出现马赛克;而MVT协议…...

SUPER COLORIZER模型训练进阶:使用自定义数据集微调以适配特定画风

SUPER COLORIZER模型训练进阶:使用自定义数据集微调以适配特定画风 你是不是觉得直接用现成的上色模型,出来的效果总是差那么点意思?要么颜色太普通,要么风格不是你想要的。比如你想给线稿上色成那种飘逸的水墨风,或者…...

【Python 入门到精通】第 5 章:字典与结构化数据,从基础到实战全解析

前言在 Python 中,列表是我们最常用的线性数据结构,但它只能按顺序存储数据,无法快速通过 “名称” 查找对应的值。而字典(dict) 作为 Python 中最核心的 “键 - 值对” 数据结构,完美解决了这个问题 —— …...

AppImageLauncher:5分钟掌握Linux AppImage应用的终极管理方案

AppImageLauncher:5分钟掌握Linux AppImage应用的终极管理方案 【免费下载链接】AppImageLauncher Helper application for Linux distributions serving as a kind of "entry point" for running and integrating AppImages 项目地址: https://gitcode…...

PCB设计新手必看:从布局到EMC的10个实用避坑技巧

PCB设计新手必看:从布局到EMC的10个实用避坑技巧 刚接触PCB设计时,总会在各种细节上栽跟头。记得我第一次画板子时,晶振离MCU太远导致时钟信号不稳定,调试了整整两天才找到问题。这种经历让我深刻意识到,PCB设计不仅是…...

论文引用格式太复杂?9种主流标准一键搞定,2026年硕博生必备神器推荐

💡 核心要点 你是否也遇到过这样的崩溃时刻:熬夜写完论文,却被导师的一句"引用格式不规范,重新调整"打回原形?手动调整APA、MLA、GB/T 7714等不同格式,一个标点符号都不能错,一篇论文…...

日)

再次革新 .NET 的构建和发布方式(一)日

本文能帮你解决什么? 1. 搞懂FastAPI异步(async/await)到底在什么场景下能真正提升性能。 2. 掌握在FastAPI中正确使用多线程处理CPU密集型任务的方法。 3. 避开常见的坑(比如阻塞操作、数据库连接池耗尽、GIL限制)。 …...

被封杀三天后,龙虾带着“复仇版本“杀回来了

OpenClaw 4.5版本上线,能直接生成视频、图片和音乐。 有些故事,编剧都不敢这么写。 几天前,Anthropic对OpenClaw下了"封杀令"——只要系统提示词中出现OpenClaw的字样,Claude就会直接拒绝请求,返回一个冷冰…...

OpenClaw模型热切换:百川2-13B-4bits与Qwen的无缝交替使用

OpenClaw模型热切换:百川2-13B-4bits与Qwen的无缝交替使用 1. 为什么需要模型热切换? 去年冬天,我在用OpenClaw处理一个跨语言项目时遇到了典型困境:Qwen在中文材料整理上表现出色,但处理英文技术文档时总会出现微妙…...

从混乱到智能:一家精品酒店如何通过客控系统升级实现降本增效

面对激烈的市场竞争与持续攀升的能耗成本,酒店管理者选择客控系统时,品牌与技术路线的决策直接关系到运营成败。本文将通过一个真实案例,拆解一家面临典型困境的精品酒店如何通过精准的客控系统选型与实施,实现运营效率与宾客体验…...