【FPGA】Verilog:组合电路 | 3—8译码器 | 编码器 | 74LS148

前言:本章内容主要是演示Vivado下利用Verilog语言进行电路设计、仿真、综合和下载

示例:编码/译码器的应用

- 功能特性: 采用 Xilinx Artix-7 XC7A35T芯片

- 配置方式:USB-JTAG/SPI Flash

- 高达100MHz 的内部时钟速度

- 存储器:2Mbit SRAM N25Q064A SPI Flash(样图旧款为N25Q032A)

- 通用IO:Switch :x8LED:x16Button:x5DIP:x8 通用扩展IO:32pin

- 音视频/显示: 7段数码管:x8 VGA视频输出接口 Audio音频接口

- 通信接口:UART:USB转UART Bluetooth:蓝牙模块

- 模拟接口: DAC:8-bit分辨率 XADC:2路12bit 1Msps ADC

目录

Ⅰ. 前置知识

0x00 3-8译码器74LS138的工作原理

0x01 优先编码器74148的工作原理

Ⅱ. Verilog实现

0x00 优先编码器74LS148

0x01 3—8译码器

0x02 结果数据

Ⅰ. 前置知识

0x00 3-8译码器74LS138的工作原理

利用Vivado提供的IP包(如下图所示)

也可直接(见下列代码)搭建74LS138功能验证电路。

(1)当选通端e1为高电平,另两个选通端e2和e3为低电平时,芯片使能。将地址端(a2、a1、a0)的二进制编码在y0至y7对应的输出端以低电平译出。比如:a2a1a0=110时,则y6输出低电平信号。

(2)利用 e1、e2和e3可方便的级联扩展成16线译码器、32线译码器。

(3)若将选通端中的一个作为数据输入端时,74LS138还可用作数据分配器

测试74LS138逻辑关系接线图

用verilog编程实现译码功能,参考代码如下。参考程序中使能信号需要自行补全。

module converter(DB,SEG); input[2:0] DB; output[7:0] SEG; reg[7:0] SEG; always @(DB) begin case(DB) 4'b0000: SEG<=8'b11111110; 4'b0001: SEG<=8’b11111101; 4'b0010: SEG<=8’b11111011; 4'b0011: SEG<=8’b11110111; 4'b0100: SEG<=8’b11101111; 4'b0101: SEG<=8’b11011111; 4'b0110: SEG<=8’b10111111; 4'b0111: SEG<=8’b01111111; default: SEG<=8'b11111111; endcase end

endmodule 0x01 优先编码器74148的工作原理

在优先编码器电路中,允许同时输入两个以上编码信号。

不过在设计优先编码器时,已经将所有的输入信号按优先顺序排了队。在同时存在两个或两个以上输入信号时,优先编码器只按优先级高的输入信号编码,优先级低的信号则不起作用。

74148是一个8-3线优先级编码器。74148优先编码器为16脚的集成芯片,除电源脚 VCC(16)和GND(8)外,其余输入、输出脚的作用和脚号如图中所标。

其中 i0~i7为输入信号(i7优先权最高),qc、qb、qa为三位二进制编码输出信号,ei是使能输入端,eo使能输出端,gs为片优先编码输出端。

电路接线如下图所示:

编码器接线

用verilog编程实现优先编码功能,参考代码如下:

module encoder_83 (din, EI, GS, EO, dout);input [7:0] din; //编码输入端data_in,低电平有效input EI; //使能输入端EI(选通输入端),EI为 0 时芯片工作,即允许编码output [2:0] dout; //编码输出端data_outoutput GS; //片优先编码输出端,优先编码器工作工作状态标志GS,低电平有效output EO; //使能输出端EO(选通输出端)reg [2:0] dout;reg GS, EO;always @(din or EI)if(EI) begin dout <= 3'b111; GS <= 1; EO <= 1; end //所有输出端被锁存在高电平else if (din[7] == 0) begin dout <= 3'b000; GS <= 0; EO <= 1; endelse if (din[6] == 0) begin dout <= 3'b001; GS <= 0; EO <= 1; endelse if (din[5] == 0) begin dout <= 3'b010; GS <= 0; EO <= 1; endelse if (din[4] == 0) begin dout <= 3'b011; GS <= 0; EO <= 1; endelse if (din[3] == 0) begin dout <= 3'b100; GS <= 0; EO <= 1; endelse if (din[2] == 0) begin dout <= 3'b101; GS <= 0; EO <= 1; endelse if (din[1] == 0) begin dout <= 3'b110; GS <= 0; EO <= 1; endelse if (din[0] == 0) begin dout <= 3'b111; GS <= 0; EO <= 1; endelse if (din == 8'b11111111) begin dout <= 3'b111; GS <= 1; EO <= 0; end //芯片工作,但无编码输入else begin dout <= 3'b111; GS <= 1; EO <= 1; end //消除锁存器(latch)

endmodule

//EI = 0 表示允许编码,否则所有输出端被封锁在高电平(控制芯片工作)

//EO = 0 表示电路工作,但无编码输入(用于级联)

//GS = 0 表示电路工作,且有编码输入(判断输入端是否有输入)Ⅱ. Verilog实现

0x00 优先编码器74LS148

设计代码:

module encoder1(n_EI,n_I,n_Y,n_CS,n_E0);

input n_EI;

input [7:0] n_I;

output [2:0] n_Y;

output n_CS,n_E0;

reg [2:0] n_Y;

reg n_CS,n_E0;

always @(n_EI or n_I)

if(n_EI==0)

if(n_I[7]==0){n_CS,n_E0,n_Y}=5'b0_1_000;

else if(n_I[6]==0){n_CS,n_E0,n_Y}=5'b0_1_001;

else if(n_I[5]==0){n_CS,n_E0,n_Y}=5'b0_1_010;

else if(n_I[4]==0){n_CS,n_E0,n_Y}=5'b0_1_011;

else if(n_I[3]==0){n_CS,n_E0,n_Y}=5'b0_1_100;

else if(n_I[2]==0){n_CS,n_E0,n_Y}=5'b0_1_101;

else if(n_I[1]==0){n_CS,n_E0,n_Y}=5'b0_1_110;

else if(n_I[0]==0){n_CS,n_E0,n_Y}=5'b0_1_111;

else{n_CS,n_E0,n_Y}=5'b1_0_111;

else{n_CS,n_E0,n_Y}=5'b1_1_111;endmodule

仿真测试代码:

module sim_encoder1();

reg n_EI;

reg [7:0] n_I;

wire [2:0] n_Y;

wire n_CS,n_E0;

encoder1 test(.n_EI(n_EI),.n_I(n_I),.n_Y(n_Y),.n_CS(n_CS),.n_E0(n_E0));

always begin

n_EI=1'b0;n_I=8'b01111111;#100;

n_EI=1'b0;n_I=8'b10111111;#100;

n_EI=1'b0;n_I=8'b11011111;#100;

n_EI=1'b0;n_I=8'b11101111;#100;

n_EI=1'b0;n_I=8'b11110111;#100;

n_EI=1'b0;n_I=8'b11111011;#100;

n_EI=1'b0;n_I=8'b11111101;#100;

n_EI=1'b0;n_I=8'b11111110;#100;

end

endmodule

波形图:

0x01 3—8译码器

设计代码:

module encoder(B,SEG,en); input[2:0] B; input[2:0] en;output[7:0] SEG; reg[7:0] SEG; always @(B or en) if(en[2]&(~en[1])&(~en[0])) case(B) 3'b000: SEG=8'b11111110; 3'b001: SEG=8'b11111101; 3'b010: SEG=8'b11111011; 3'b011: SEG=8'b11110111; 3'b100: SEG=8'b11101111; 3'b101: SEG=8'b11011111; 3'b110: SEG=8'b10111111; 3'b111: SEG=8'b01111111; default: SEG=8'b11111111; endcase else SEG=8'b11111111;

endmodule

仿真测试代码:

module sim_encoder(); reg [2:0]B;reg [2:0]en;wire [7:0]SEG;encoder test(.B(B),.SEG(SEG),.en(en));always beginen=3'b100;B=3'b000;#100;en=3'b100;B=3'b001;#100;en=3'b100;B=3'b010;#100;en=3'b100;B=3'b011;#100;en=3'b100;B=3'b100;#100;en=3'b100;B=3'b101;#100;en=3'b100;B=3'b110;#100;en=3'b100;B=3'b111;#100;endendmodule波形图:

0x02 结果数据

74LS138功能表

| 输入 | 输出 | ||||||||||||

| 使能 | 选择 | ||||||||||||

| e1(G1) | e2(G2B) | e3(G2A) | a2(C) | a1(B) | a0(A) | y7 | y6 | y5 | y4 | y3 | y2 | y1 | y0 |

| 0 | × | × | × | × | × | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 |

| 1 | × | 1 | × | × | × | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 |

| 1 | 1 | × | × | × | × | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 |

| 1 | 0 | 0 | 0 | 0 | 0 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 0 |

| 1 | 0 | 0 | 0 | 0 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 0 | 1 |

| 1 | 0 | 0 | 0 | 1 | 0 | 1 | 1 | 1 | 1 | 1 | 0 | 1 | 1 |

| 1 | 0 | 0 | 0 | 1 | 1 | 1 | 1 | 1 | 1 | 0 | 1 | 1 | 1 |

| 1 | 0 | 0 | 1 | 0 | 0 | 1 | 1 | 1 | 0 | 1 | 1 | 1 | 1 |

| 1 | 0 | 0 | 1 | 0 | 1 | 1 | 1 | 0 | 1 | 1 | 1 | 1 | 1 |

| 1 | 0 | 0 | 1 | 1 | 0 | 1 | 0 | 1 | 1 | 1 | 1 | 1 | 1 |

| 1 | 0 | 0 | 1 | 1 | 1 | 0 | 1 | 1 | 1 | 1 | 1 | 1 | 1 |

优先编码器74LS148功能表

| 输入 | 输出 | ||||||||||||

| ei使能 | i7 | i6 | i5 | i4 | i3 | i2 | i1 | i0 | qc | qb | qa | eo 选通 | gs 扩展 |

| 1 | × | × | × | × | × | × | × | × | 1 | 1 | 1 | 1 | 1 |

| 0 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 |

| 0 | 0 | × | × | × | × | × | × | × | 0 | 0 | 0 | 1 | 0 |

| 0 | 1 | 0 | × | × | × | × | × | × | 0 | 0 | 1 | 1 | 0 |

| 0 | 1 | 1 | 0 | × | × | × | × | × | 0 | 1 | 0 | 1 | 0 |

| 0 | 1 | 1 | 1 | 0 | × | × | × | × | 0 | 1 | 1 | 1 | 0 |

| 0 | 1 | 1 | 1 | 1 | 0 | × | × | × | 1 | 0 | 0 | 1 | 0 |

| 0 | 1 | 1 | 1 | 1 | 1 | 0 | × | × | 1 | 0 | 1 | 1 | 0 |

| 0 | 1 | 1 | 1 | 1 | 1 | 1 | 0 | × | 1 | 1 | 0 | 1 | 0 |

| 0 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 0 | 1 | 1 | 1 | 1 | 0 |

、

相关文章:

【FPGA】Verilog:组合电路 | 3—8译码器 | 编码器 | 74LS148

前言:本章内容主要是演示Vivado下利用Verilog语言进行电路设计、仿真、综合和下载 示例:编码/译码器的应用 功能特性: 采用 Xilinx Artix-7 XC7A35T芯片 配置方式:USB-JTAG/SPI Flash 高达100MHz 的内部时钟速度 存储器&…...

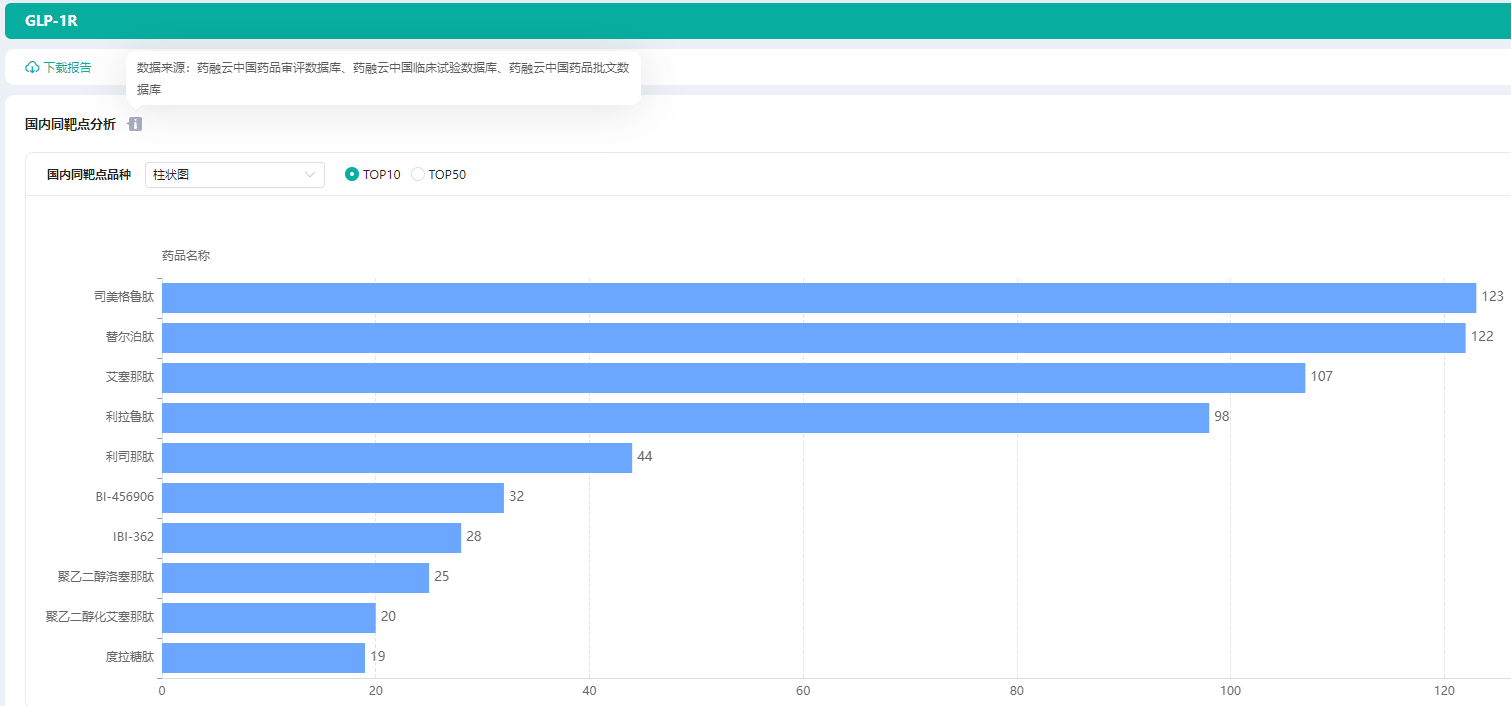

GLP-1类药物研发进展-销售数据-上市药品前景分析

据一项2021 年的报告发现,当 GLP-1 类似物用于治疗 2 型糖尿病时,全因死亡率降低了 12%,它们不仅降糖效果显著,同时还兼具减重、降压、改善血脂谱等作用。近几年,随着GLP-1R激动剂类药物市场规模不断增长,美…...

C++远程监控系统接收端- RevPlayMDIChildWnd.cpp

void CRevPlayWnd::InitMultiSock() { int RevBuf; int status; BOOL bFlag; CString ErrMsg; SOCKADDR_IN stLocalAddr; SOCKADDR_IN stDestAddr; SOCKET hNewSock; int RevLensizeof(RevBuf); //创建一个IP组播套接字 MultiSock W…...

QT之OpenGL深度测试

QT之OpenGL深度测试1. 深度测试概述1. 1 提前深度测试1.2 深度测试相关函数2. 深度测试精度2.1 深度冲突3. Demo4. 参考1. 深度测试概述 在OpenGL中深度测试(Depth Testing)是关闭的,此时在渲染图形时会产生一种现象后渲染的会把最先渲染的遮挡住。而在启用深度测试…...

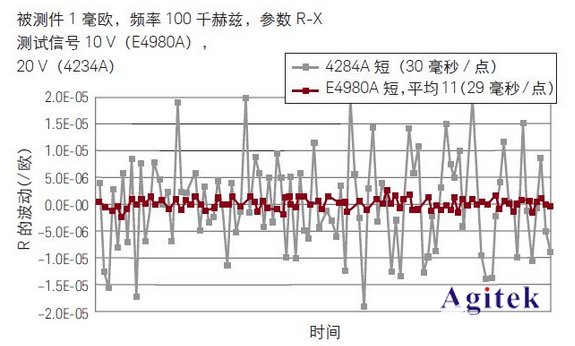

用LCR测试仪测试无线充电系统中的线圈

宽阻抗范围用来表征电感和质量因数– 高精度 DCR 测量– 制造环节快速测量– 大量夹具可供选择智能终端上不断增加新功能,电池寿命成为用户最头痛的问题之一。相比便携式电源和电缆供电而言,无线充电技术因其方便性和多功能性获得了很大的关注࿰…...

华为、南卡和漫步者蓝牙耳机怎么选?国产高性价比蓝牙耳机推荐

随着蓝牙耳机的快速发展,现如今使用蓝牙耳机的人也越来越多。其中,日益增多的国产蓝牙耳机品牌也逐渐被大众认识、认可。目前一些热销的国产蓝牙耳机,如华为、南卡和漫步者等都是大家比较熟知的品牌。那么,这三个品牌哪个性价比高…...

)

MySQl学习(从入门到精通12)

MySQl学习(从入门到精通12)第 15 章_存储过程与函数1. 存储过程概述1. 1 理解1. 2 分类2. 创建存储过程2. 1 语法分析2. 2 代码举例3. 调用存储过程3. 1 调用格式3. 2 代码举例3. 3 如何调试4. 存储函数的使用4. 1 语法分析4. 2 调用存储函数4. 3 代码举…...

08讲 | 基于STM32单片机NBIOT定位实战项目

前言 绘制基于 STM32 单片机的 NBIOT 实战开发板。 文章目录前言一、原理图1、绘制1)电源供电a、USB 转 TTL 电路b、锂电池充电管理电路c、3.3V电压转换电路d、一键开关机电路2)单片机最小系统3)ADC电压转换电路4)NBIOT 模组串口电…...

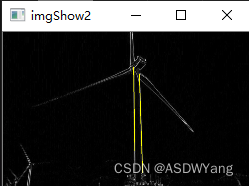

提取接近竖直物体(粗定位)

由于项目的需要提取图像之中的一个接近于竖直的物体,一般的方法是进行图像分割,分割方式使用什么OTSU方式以及hsv方法等等。但是项目中使用的相机是黑白相机,会受到一定的限制。因此想到的是使用线条提取方式。线条提取方式之中最好的方法是使…...

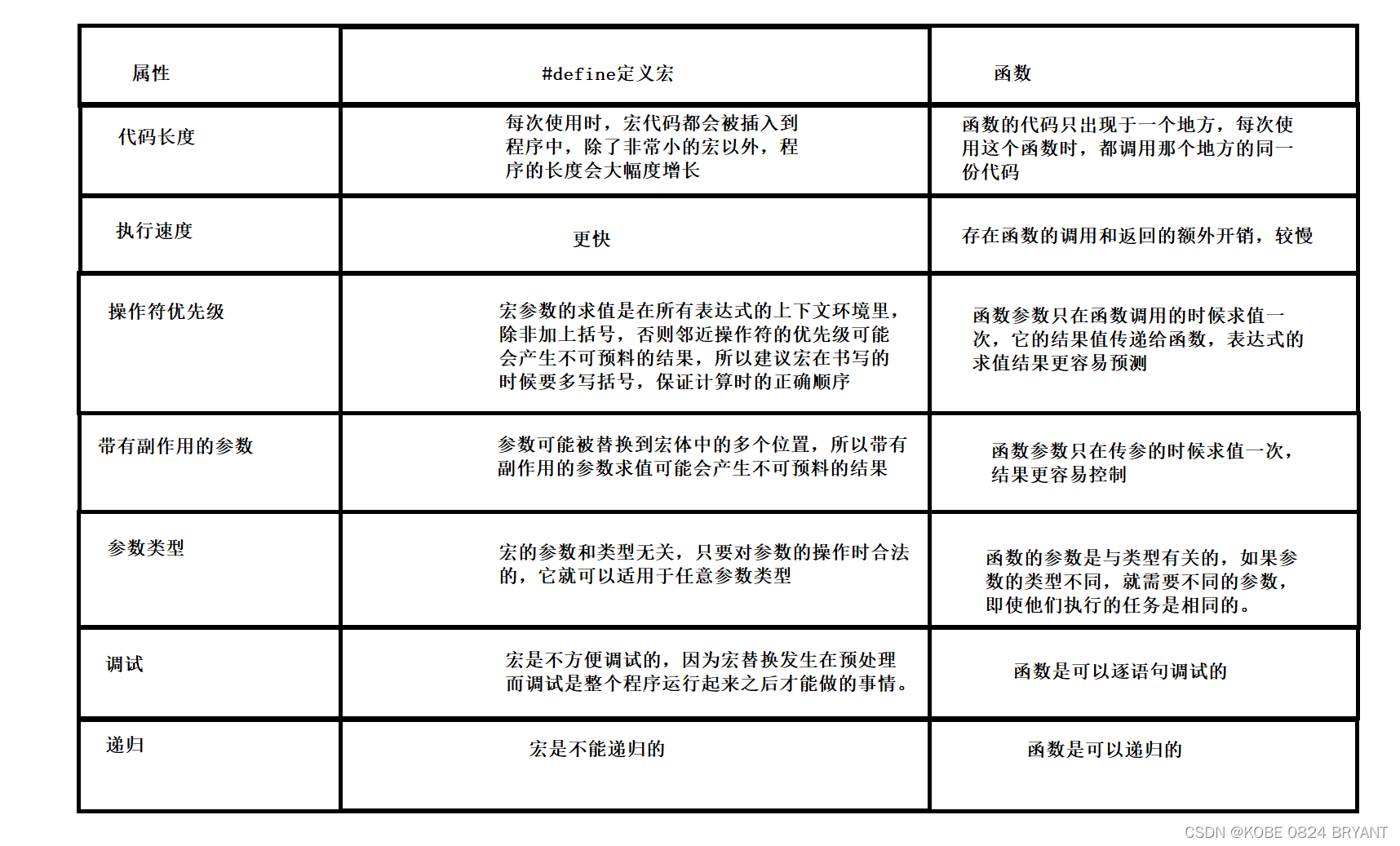

程序环境和预处理

目录一、程序的翻译环境和执行环境二、编译链接2.1 翻译环境2.2 编译2.2.1 预处理2.2.2 编译2.2.3 汇编2.3 链接2.4 结果三、运行环境四、预处理详解4.1 #define4.1.1 #define定义标识符4.1.2 #define定义宏4.1.3 #define 替换规则4.1.4 #和##4.1.5 带副作用的宏参数4.1.6 宏和…...

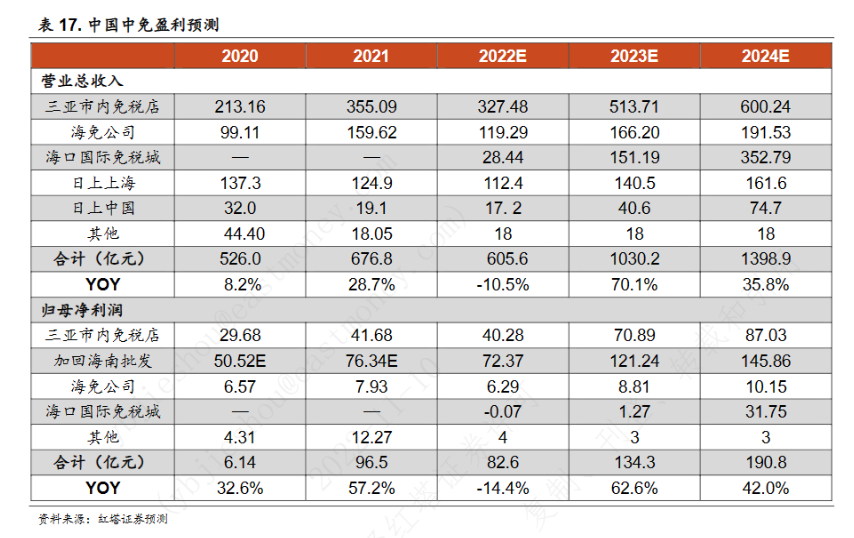

财报解读:业务复苏迹象明显,中国中免能否重写增长神话?

2月3日,中国中免披露2022年度业绩快报,2022年总营收为544.63亿元,同比下降19.52%;实现归属于上市公司股东的净利润50.25亿元,同比下降47.95%。来源:中国中免2022年度业绩快报业绩近乎腰斩,但从长…...

macOS中虚拟机桥接模式分配静态ip

1.首先使用dhclient命令,在局域网中分配一个C类地址。 2.获得地址后,输入ifconfig,查看分配的地址。 3.然后编辑vi /etc/sysconfig/network-scripts/ifcfg-en***文件 在该配置文件中编辑,设置ONBOOTyes,而后添加静态配…...

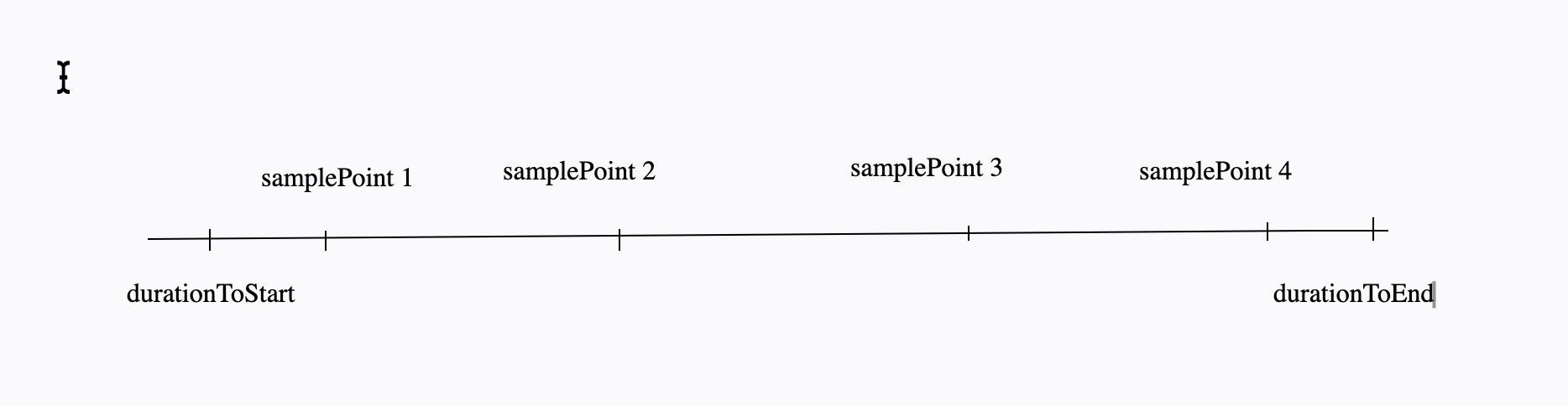

prometheus increase函数统计得到小数

今天发现prometheus的increase函数得到了小数,研究一下源码,以下是rate/increase/delta 对应的计算函数https://github.com/prometheus/prometheus/blob/d77b56e88e3d554a499e22d2073812b59191256c/promql/functions.go#L55// extrapolatedRate is a uti…...

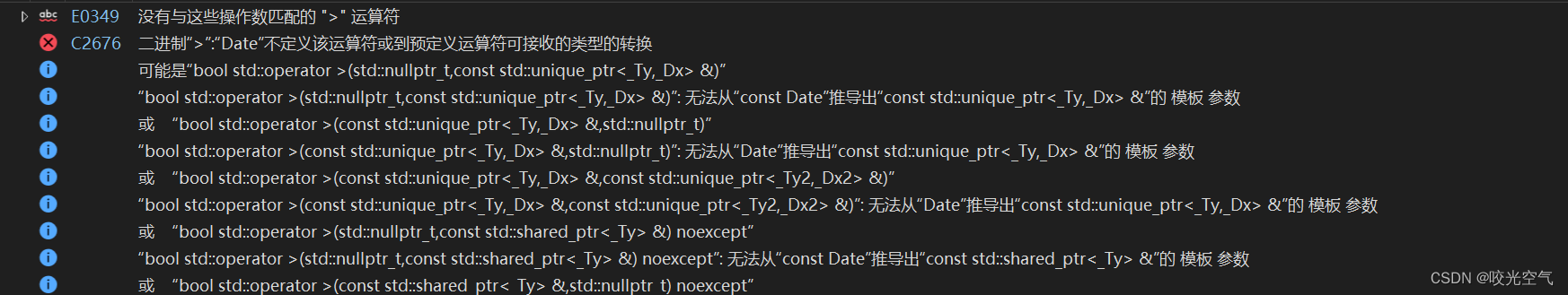

C++学习记录——유 类和对象(3)

文章目录1、赋值运算符重载1、运算符重载1、理解2、运算符重载实例2、赋值运算符重载2、日期类的实现1、加减函数1、加函数2、减函数2、前/后置--重载3.两个日期相减其他1、流插入2、流提取日期类的整体实现代码: https://gitee.com/kongqizyd/start-some-c-codes-for-learning…...

基于Hi3861平台的OpenHarmony程序是如何启动运行的

一、前言 在继续后面课程的内容讲解前,我们要知道在H3861平台上编写的代码到底是如何启动的,这一点很重要。 先分析HelloWorld程序的启动运行流程,并顺便讲解OpenHarmony在H3861平台的,系统是从哪里启动的。 反着推导函数之间具体…...

2023彻底解决Typora使用iPic微博图床失效问题

一、问题描述用Typora搭配iPic图床使用,最近csdn图片显示不出来用浏览器打开图片显示403,这里原因是微博图床出问题了导致的而使用iPic其他图床则需要一直付费,那有没有一劳永逸的解决所有问题呢?二、旧图恢复首先怎么找回旧图&am…...

Revit中添加水平仰视平面图及水平剖面

一、 Revit中如何添加水平仰视平面图 在Revit平面视图中视角是俯视视角,但是在一些特殊的情况下,我们可能需要创建仰视视角的平面视图,例如我们需要向上看天花板的灯具布置的时候。 1.下面讲一下如何在添加仰视平面视图的方法。如图1在模型中…...

Python 循环语句

Python的循环语句,程序在一般情况下是按顺序执行的。编程语言提供了各种控制结构,允许更复杂的执行路径。循环语句允许我们执行一个语句或语句组多次,下面是在大多数编程语言中的循环语句的一般形式:Python 提供了 for 循环和 whi…...

使用 ThreeJS 实现第一个三维场景(详)

文章目录参考描述index.html三维场景的基本实现导入 ThreeJS准备工作场景摄像机视锥体正交摄像机透视摄像机渲染器后续处理将摄像机添加至场景中移动摄像机设置画布尺寸将渲染器创建的画布添加到 HTML 元素中渲染物体结构材质合成将物体添加至场景中代码总汇执行效果动画reques…...

《小猫猫大课堂》三轮5——动态内存管理(通讯录动态内存化)

宝子,你不点个赞吗?不评个论吗?不收个藏吗? 最后的最后,关注我,关注我,关注我,你会看到更多有趣的博客哦!!! 喵喵喵,你对我真的很重…...

如何快速掌握WindowResizer:终极窗口强制调整工具完整指南

如何快速掌握WindowResizer:终极窗口强制调整工具完整指南 【免费下载链接】WindowResizer 一个可以强制调整应用程序窗口大小的工具 项目地址: https://gitcode.com/gh_mirrors/wi/WindowResizer 还在为那些顽固的固定尺寸窗口而烦恼吗?WindowRe…...

新手也能看懂的SQL注入绕过实战:以BUUCTF的BabySQL靶场为例,手把手教你双写绕过

从零破解BabySQL:双写绕过的艺术与科学 当你第一次接触CTF比赛中的SQL注入题目时,那种既兴奋又困惑的感觉一定记忆犹新。面对BabySQL这样的靶场,新手常会遇到一个典型困境:明明知道应该用union select来获取数据,却发现…...

django-notifications故障排除:常见问题诊断与解决方案大全

django-notifications故障排除:常见问题诊断与解决方案大全 【免费下载链接】django-notifications GitHub notifications alike app for Django 项目地址: https://gitcode.com/gh_mirrors/dj/django-notifications django-notifications是一个为Django应用…...

路由55555555

LSW2:先进入vlan,再添加mac地址,mac地址在主机处复制(此时只添加PC1还有PC2的mac地址就好了)给G0/0/1接口配置不带标签的vlan 启动mac 地址:LSW3:设置网关,看是否能够通...

终极视频字幕提取指南:如何用本地OCR工具高效提取87种语言硬字幕

终极视频字幕提取指南:如何用本地OCR工具高效提取87种语言硬字幕 【免费下载链接】video-subtitle-extractor 视频硬字幕提取,生成srt文件。无需申请第三方API,本地实现文本识别。基于深度学习的视频字幕提取框架,包含字幕区域检测…...

群晖相册AI识别解锁指南:让无GPU设备也能享受智能相册功能

群晖相册AI识别解锁指南:让无GPU设备也能享受智能相册功能 【免费下载链接】Synology_Photos_Face_Patch Synology Photos Facial Recognition Patch 项目地址: https://gitcode.com/gh_mirrors/sy/Synology_Photos_Face_Patch 你是否拥有DS918或DS3615xs等群…...

YOLOv5 COCO数据集 实战训练全流程解析 | 【从零到一】

1. 环境准备:从零搭建YOLOv5训练环境 第一次接触YOLOv5时,我最头疼的就是环境配置。记得当时为了一个CUDA版本问题折腾了整整两天,现在回想起来其实只要按步骤来就能避免90%的坑。下面是我总结的最稳环境搭建方案: 首先确保你的机…...

从零上手泰凌微TLSR8269:SIG Mesh SDK文件架构与编译环境搭建保姆级指南

泰凌微TLSR8269 SIG Mesh开发实战:从SDK解析到环境搭建全攻略 第一次打开泰凌微TLSR8269的SIG Mesh SDK时,面对密密麻麻的文件夹和文件,不少开发者都会感到无从下手。proj、proj_lib、vendor这些目录到底存放着什么?如何快速搭建起…...

网盘直链下载助手:如何从九大主流网盘中一键获取真实下载地址?

网盘直链下载助手:如何从九大主流网盘中一键获取真实下载地址? 【免费下载链接】Online-disk-direct-link-download-assistant 一个基于 JavaScript 的网盘文件下载地址获取工具。基于【网盘直链下载助手】修改 ,支持 百度网盘 / 阿里云盘 / …...

League Akari:英雄联盟客户端终极智能助手完整指南

League Akari:英雄联盟客户端终极智能助手完整指南 【免费下载链接】League-Toolkit An all-in-one toolkit for LeagueClient. Gathering power 🚀. 项目地址: https://gitcode.com/gh_mirrors/le/League-Toolkit League Akari是一款基于LCU API…...