关于单片机的时钟浅谈及STM32F103/F030单片机的内外时钟切换问题

绪论

本文主要讲解单片机的时钟系统的相关知识,并进行超频测试,同时介绍如何在STM32F0单片机上进行内外时钟的切换,在不使用外部晶振或者外部晶振不启动时自动切换内部时钟的方法。

一、杂谈

问题来源于群里的一次问答:

诚然,当使用固件库时,把外部晶振摘掉,系统确实会自动切换到内部时钟,但是只会以8M的默认值运行,显然这是十分不可行的,8M的速度直接让我们的STM32病入膏肓,今天的任务就是让STM32失去外挂(晶振)时,依旧可以激情澎湃。

时钟详解这里不过多介绍,自己也没有别人介绍的好。此帖旨在解决现实问题。

此处插播广告:

群友问过这种问题,外部接8M晶振和16M晶振有啥区别?

以我微薄的经验来看,这两个在用的时候差别不大,如果使用ST的固件库(以STM32F103为例),使用8M的晶振会更方便,不用改任何代码,时钟就是72M的全速运行状态。如果用16M晶振,则需要修改代码:

在stm32f10x.h中修改宏定义

HSE_VALUE ((uint32_t)8000000)为HSE_VALUE ((uint32_t)16000000)。

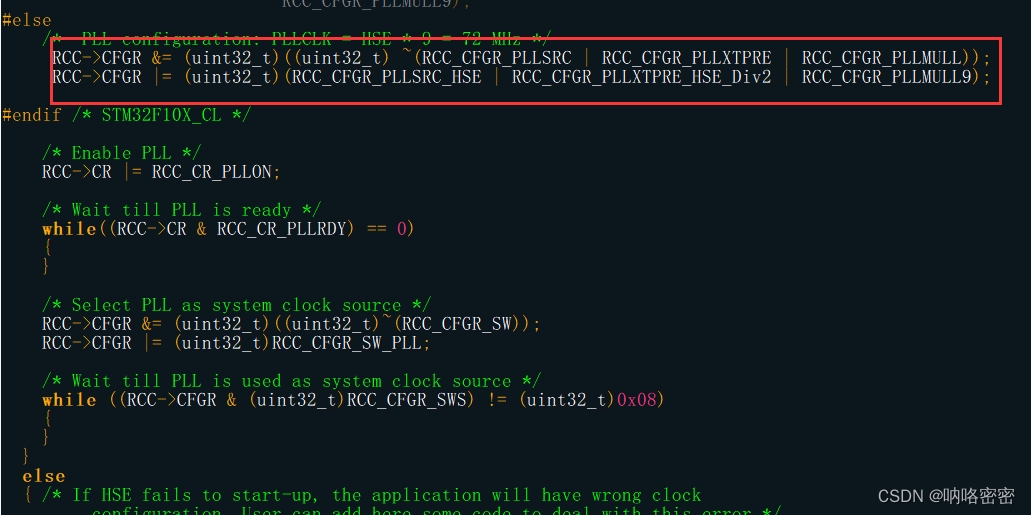

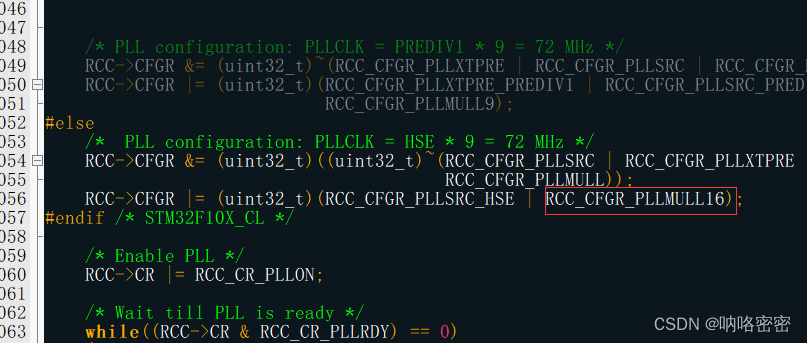

之后进入system_stm32f10x.c,将

RCC->CFGR |= (uint32_t)(RCC_CFGR_PLLSRC_HSE | RCC_CFGR_PLLMULL9);

改为

RCC->CFGR |= (uint32_t)(RCC_CFGR_PLLSRC_HSE | RCC_CFGR_PLLXTPRE_HSE_Div2 | RCC_CFGR_PLLMULL9);

此处是将输入时钟二分频为8M,再进行9倍频到72M,和使用了8M没区别。如果不进行该二分频操作,时钟还是有的,但是会以16M为基准进行9倍频到144M,此时单片机以超频模式运行,也是可以运行的。但是时钟的精准性不能得到保证。

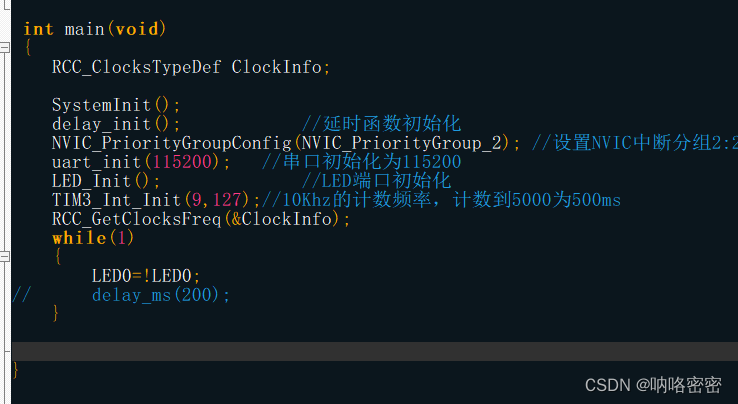

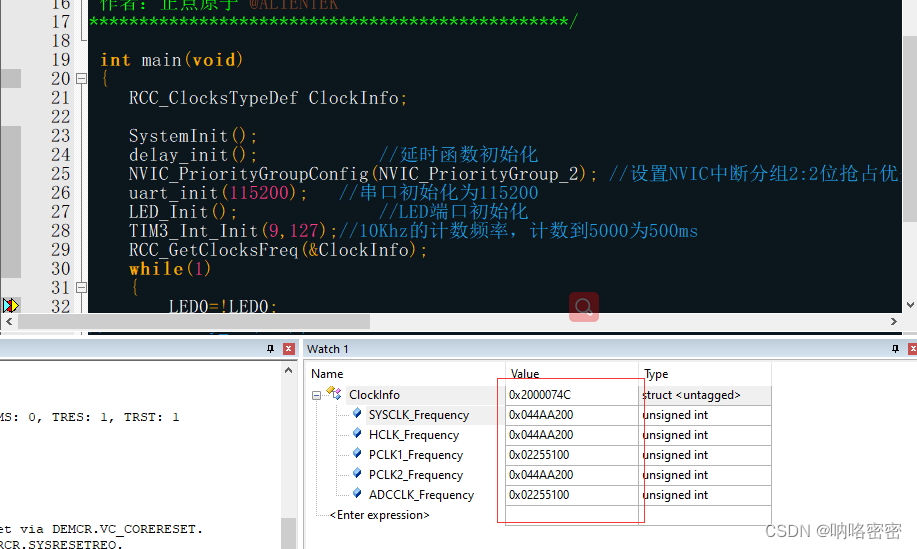

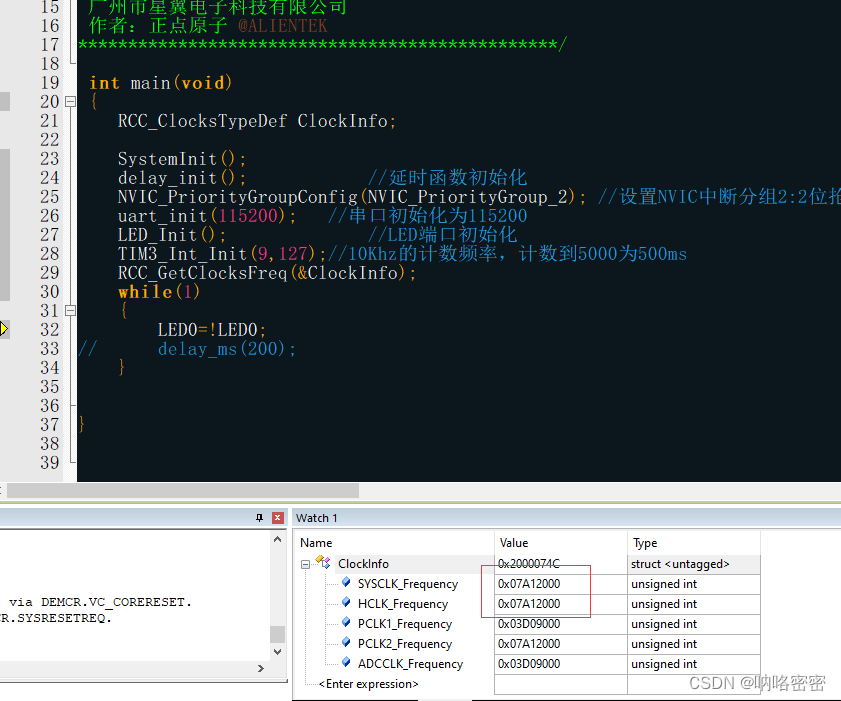

系统的时钟可以通过添加代码在debug模式下显示:

RCC_ClocksTypeDef ClockInfo;

RCC_GetClocksFreq(&ClockInfo);

通过debug模式下观察ClockInfo的值便可知道此时系统时钟速度:

这里提一下,在使用外部晶振的情况下,ST即使是超频,依旧发挥稳定,不得不夸一下ST的质量。

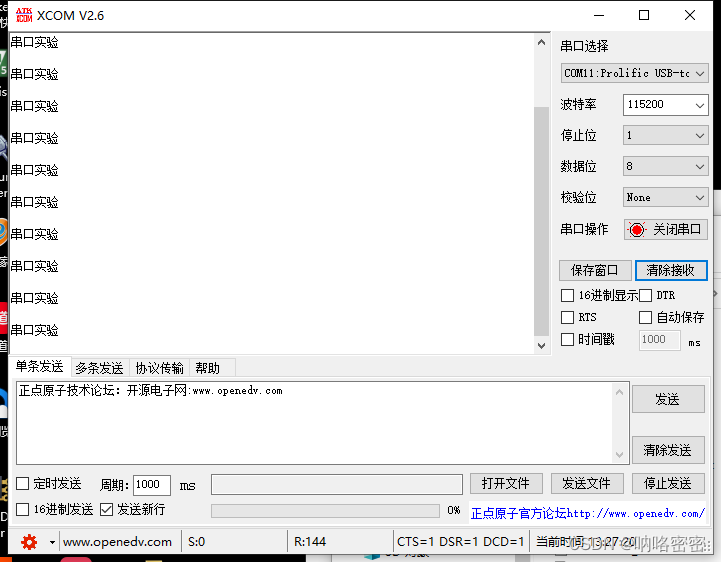

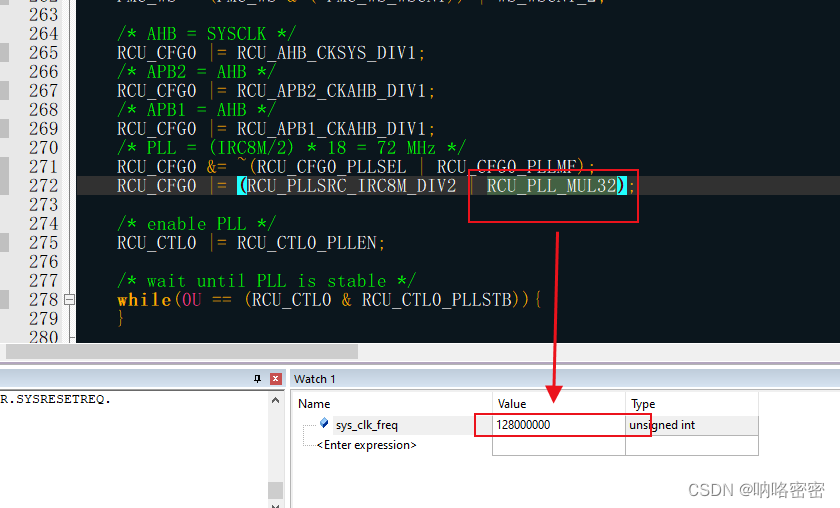

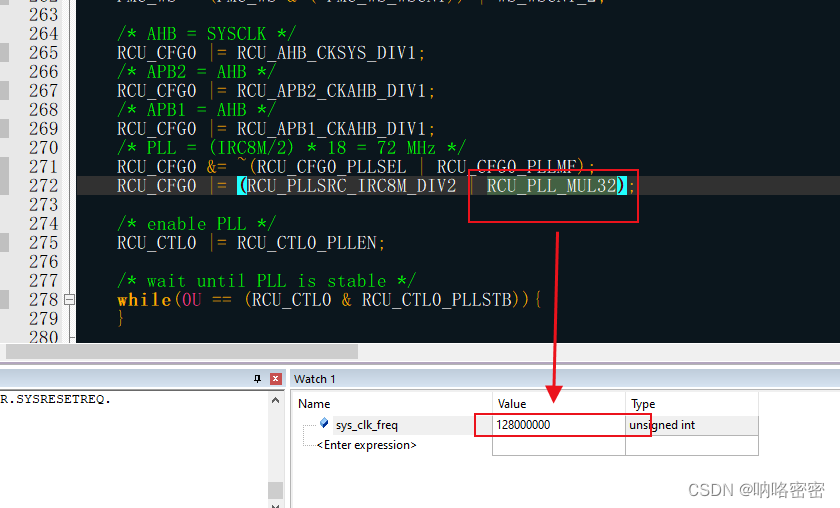

此时我将我的开发板以8M的基准倍频16倍,得到128M的主频,使用定时器定时10us,示波器测试无误差。串口通信无误。

以72M的主频跑128依旧稳定,赞一个,因为我的外部晶振只有8M最大只能倍频到128,如果使用外部16M,不知继续倍频可以到多少。不过性能还是很好的。

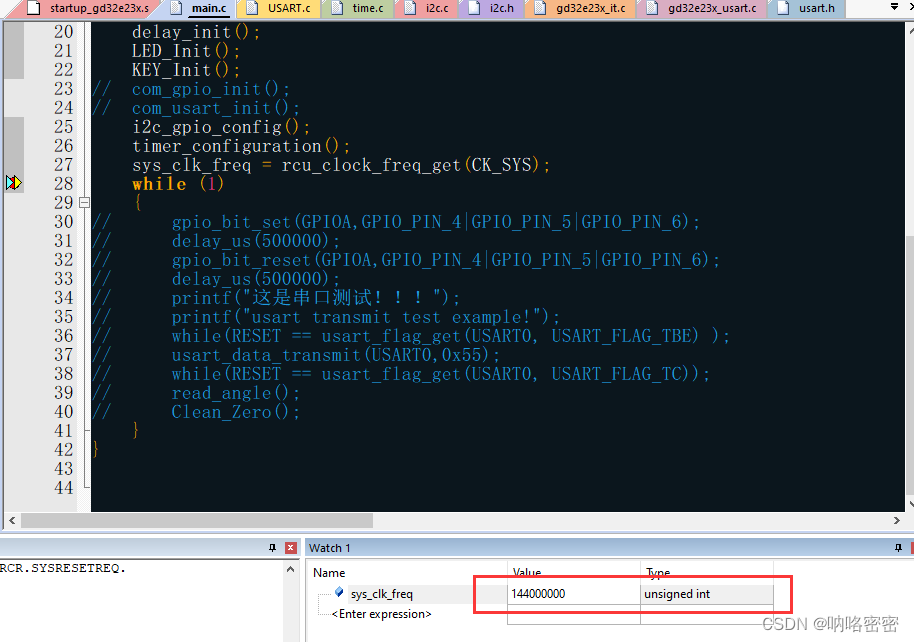

预留测试GD32的效果:

写贴时将GD的GD32E230翻出来进行了同样的测试,因为GD的倍频器倍数较高,我已经倍频到144M(标准72M),测试定时器依旧稳定。

广告很长,你忍一下。

上半场结束,下半场继续:

此处歪解一下时钟的问题,之前有群友很疑惑单片机的低功耗和时钟的关系,疑惑高速的时钟会不会增加MCU的功耗,为啥低功耗要降低时钟速度。这里讲解一下:

可以用用单位时间内执行的指令来看,高速时钟在单位时间内使系统跑了更多的指令,而低速时钟单位时间内跑的少,而单片机是直线结构,内核是不会休息的,功耗就看执行的指令多少。而单片机的低功耗就是降低时钟,让单片机跑慢点。就像人一样,低功耗相当于你不跑了,原地休息,但是你的心跳不会停止,你还是得消耗能量,即使再少还得消耗。

就像人一样,时钟就相当于心跳,只要还活着就得消耗能量,你要想跑得快,心脏就得跳得快,跳得越快能量消耗越高,即使你去睡觉,心跳只要不停止,你还得消耗能量,如果心跳没了,整个人就没了,MCU也就宕机了。所以在处理低功耗时最先解决的就是时钟频率,只有降低了时钟的频率,才能真正降低功耗。关于单片机进入低功耗和唤醒,以及降低整体运行功耗我看能不能在下文讲解,近期刚好做了一个低功耗的项目,这里留悬念吧。

二、内外时钟切换

广告结束,正文开始,不好意思,有点喧宾夺主了哈。

回到主题,为了解决时钟切换的问题,才有了这个帖子,上文全属歪楼,为最近开发时的经验总结。

我们在使用STM32103的固件库时,时钟配置在system_stm32f10x.c中,但是只是对外部晶振做了初始化,而对于内部时钟并没有添加代码,如果你的MCU没有外部晶振,当系统运行时是先启动内部时钟,然后会检测外部晶振,如果没有检测到晶振,系统便以内部的8M继续运行,这是不合理的。

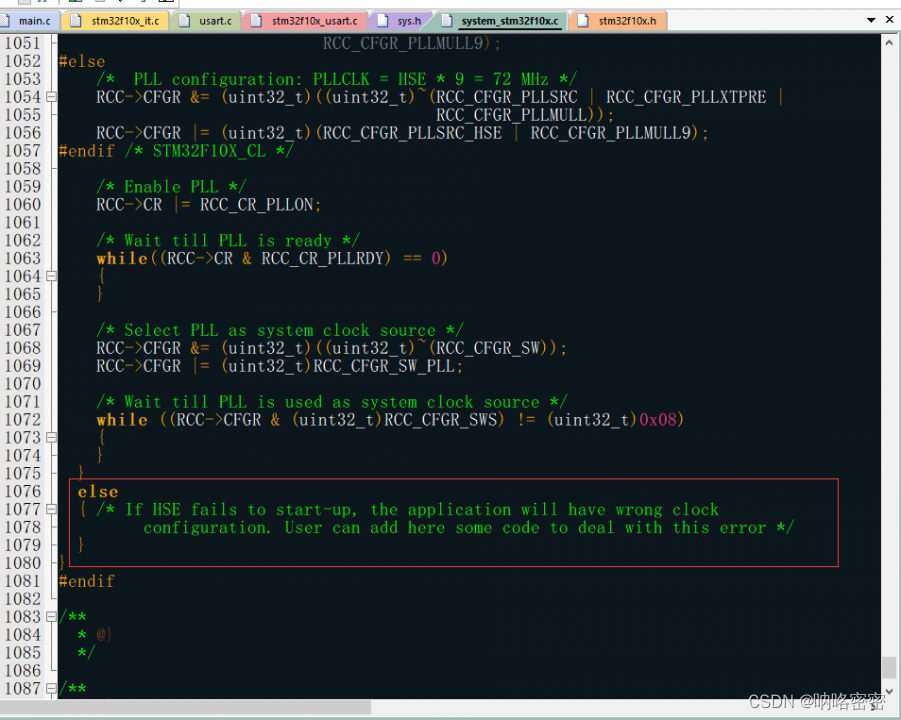

这里可以看到,如果外部启动失败,会进入这个else,但是这个else中并未添加任何代码,所以只会用8M的内钟执行,我们要做的就是在else中添加外部启动失败的代码:

/* 开启HSI 即内部晶振时钟 */RCC->CR |= (uint32_t)0x00000001; /*选择HSI为PLL的时钟源HSI必须2分频给PLL*/RCC->CFGR |= (uint32_t)RCC_CFGR_PLLSRC_HSI_Div2; /*PLLCLK=8/2*13=52MHz 设置倍频得到时钟源PLL的频率*/RCC->CFGR |= (uint32_t)RCC_CFGR_PLLMULL12;/* PLL不分频输出 */RCC->CFGR |= (uint32_t)RCC_CFGR_HPRE_DIV1;/* 使能 PLL时钟 */RCC->CR |= RCC_CR_PLLON;/* 等待PLL时钟就绪*/while((RCC->CR & RCC_CR_PLLRDY) == 0){}/* 选择PLL为系统时钟的时钟源 */RCC->CFGR &= (uint32_t)((uint32_t)~(RCC_CFGR_SW));RCC->CFGR |= (uint32_t)RCC_CFGR_SW_PLL; /* 等到PLL成为系统时钟的时钟源*/while ((RCC->CFGR & (uint32_t)RCC_CFGR_SWS) != (uint32_t)0x08){}

该代码填充后如果检测到有外部时钟,便以外部时钟为基准进行时钟的倍频处理,达到用户想要的时钟频率,如果你的MCU没有外部时钟,则会执行else内部的代码,将时钟源切换到内部时钟并进行倍频。如此便达到了自动检测时钟的目的。

问题:这是我根据STM32F031的时钟切换代码演变来的,但是这个只能用于主频小于或等于48M时使用,如果倍频因子超过12,也就是主频超过48M是,就会出现硬件错误,直接卡死。当需要更高的主频时就需要如下配置。

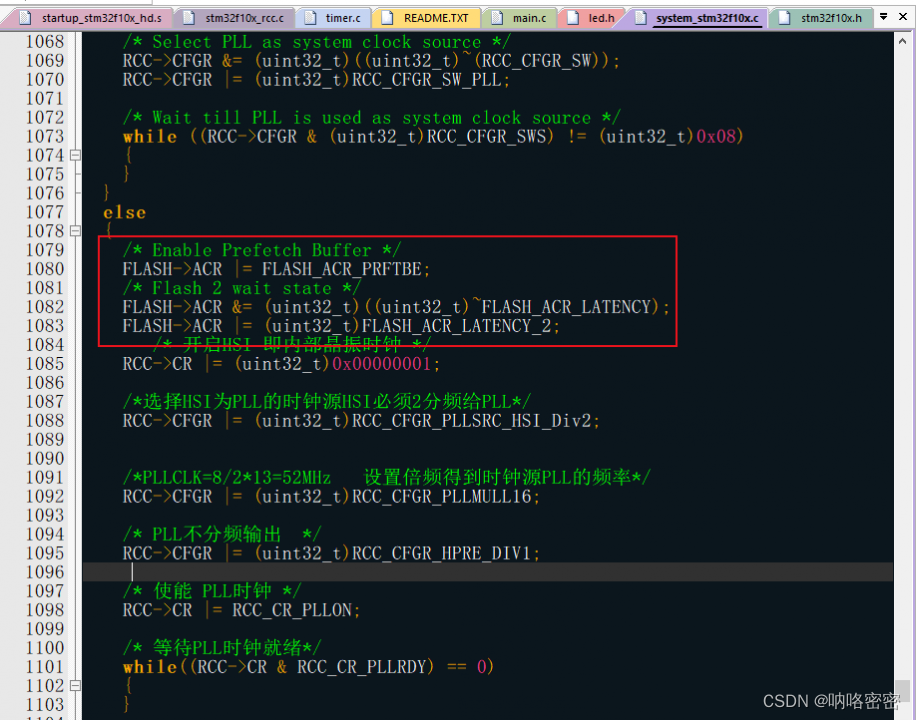

在else里面最开头添加:

/* Enable Prefetch Buffer */FLASH->ACR |= FLASH_ACR_PRFTBE;/* Flash 2 wait state */FLASH->ACR &= (uint32_t)((uint32_t)~FLASH_ACR_LATENCY);FLASH->ACR |= (uint32_t)FLASH_ACR_LATENCY_2;

问:

如果我的MCU有晶振,但是我不想用外部,就想用内部,如何处理呢?

答:

打一顿就好了,有外部不用干啥用内部呢?

上述纯属恶搞自己,被坑过。。。

因为内部时钟不准!!!测试内部时钟在使用定时器时会有偏差,本人在此吃过亏。此问题在STM32F031和GD32E230中均有体现。但是USART和SPI通信是正常的,即使我用的2.5M波特率的USART和8M的SPI。

解决办法,上述代码不用动,添加如下代码。

通过注释原文

RCC->CR |= ((uint32_t)RCC_CR_HSEON);

并添加

RCC->CR &= ~((uint32_t)RCC_CR_HSEON);可默认之以内部时钟方式启动。

注意在主函数加上SystemInit();函数哦!!!

最终代码如下:

static void SetSysClockTo72(void)

{__IO uint32_t StartUpCounter = 0, HSEStatus = 0;/* SYSCLK, HCLK, PCLK2 and PCLK1 configuration ---------------------------*/ /* Enable HSE */

// RCC->CR |= ((uint32_t)RCC_CR_HSEON);/*取消改行注释并注释上文,可默认启动内部时钟*/RCC->CR &= ~((uint32_t)RCC_CR_HSEON);/* Wait till HSE is ready and if Time out is reached exit */do{HSEStatus = RCC->CR & RCC_CR_HSERDY;StartUpCounter++; } while((HSEStatus == 0) && (StartUpCounter != HSE_STARTUP_TIMEOUT));if ((RCC->CR & RCC_CR_HSERDY) != RESET){HSEStatus = (uint32_t)0x01;}else{HSEStatus = (uint32_t)0x00;} if (HSEStatus == (uint32_t)0x01){/* Enable Prefetch Buffer */FLASH->ACR |= FLASH_ACR_PRFTBE;/* Flash 2 wait state */FLASH->ACR &= (uint32_t)((uint32_t)~FLASH_ACR_LATENCY);FLASH->ACR |= (uint32_t)FLASH_ACR_LATENCY_2; /* HCLK = SYSCLK */RCC->CFGR |= (uint32_t)RCC_CFGR_HPRE_DIV1;/* PCLK2 = HCLK */RCC->CFGR |= (uint32_t)RCC_CFGR_PPRE2_DIV1;/* PCLK1 = HCLK */RCC->CFGR |= (uint32_t)RCC_CFGR_PPRE1_DIV2;#ifdef STM32F10X_CL/* Configure PLLs ------------------------------------------------------*//* PLL2 configuration: PLL2CLK = (HSE / 5) * 8 = 40 MHz *//* PREDIV1 configuration: PREDIV1CLK = PLL2 / 5 = 8 MHz */RCC->CFGR2 &= (uint32_t)~(RCC_CFGR2_PREDIV2 | RCC_CFGR2_PLL2MUL |RCC_CFGR2_PREDIV1 | RCC_CFGR2_PREDIV1SRC);RCC->CFGR2 |= (uint32_t)(RCC_CFGR2_PREDIV2_DIV5 | RCC_CFGR2_PLL2MUL8 |RCC_CFGR2_PREDIV1SRC_PLL2 | RCC_CFGR2_PREDIV1_DIV5);/* Enable PLL2 */RCC->CR |= RCC_CR_PLL2ON;/* Wait till PLL2 is ready */while((RCC->CR & RCC_CR_PLL2RDY) == 0){}/* PLL configuration: PLLCLK = PREDIV1 * 9 = 72 MHz */ RCC->CFGR &= (uint32_t)~(RCC_CFGR_PLLXTPRE | RCC_CFGR_PLLSRC | RCC_CFGR_PLLMULL);RCC->CFGR |= (uint32_t)(RCC_CFGR_PLLXTPRE_PREDIV1 | RCC_CFGR_PLLSRC_PREDIV1 | RCC_CFGR_PLLMULL9);

#else /* PLL configuration: PLLCLK = HSE * 9 = 72 MHz */RCC->CFGR &= (uint32_t)((uint32_t)~(RCC_CFGR_PLLSRC | RCC_CFGR_PLLXTPRE |RCC_CFGR_PLLMULL));RCC->CFGR |= (uint32_t)(RCC_CFGR_PLLSRC_HSE | RCC_CFGR_PLLMULL16);

#endif /* STM32F10X_CL *//* Enable PLL */RCC->CR |= RCC_CR_PLLON;/* Wait till PLL is ready */while((RCC->CR & RCC_CR_PLLRDY) == 0){}/* Select PLL as system clock source */RCC->CFGR &= (uint32_t)((uint32_t)~(RCC_CFGR_SW));RCC->CFGR |= (uint32_t)RCC_CFGR_SW_PLL; /* Wait till PLL is used as system clock source */while ((RCC->CFGR & (uint32_t)RCC_CFGR_SWS) != (uint32_t)0x08){}}else{ /* Enable Prefetch Buffer */FLASH->ACR |= FLASH_ACR_PRFTBE;/* Flash 2 wait state */FLASH->ACR &= (uint32_t)((uint32_t)~FLASH_ACR_LATENCY);FLASH->ACR |= (uint32_t)FLASH_ACR_LATENCY_2; /* 开启HSI 即内部晶振时钟 */RCC->CR |= (uint32_t)0x00000001; /*选择HSI为PLL的时钟源HSI必须2分频给PLL*/RCC->CFGR |= (uint32_t)RCC_CFGR_PLLSRC_HSI_Div2; /*PLLCLK=8/2*13=52MHz 设置倍频得到时钟源PLL的频率*/RCC->CFGR |= (uint32_t)RCC_CFGR_PLLMULL16;/* PLL不分频输出 */RCC->CFGR |= (uint32_t)RCC_CFGR_HPRE_DIV1;/* 使能 PLL时钟 */RCC->CR |= RCC_CR_PLLON;/* 等待PLL时钟就绪*/while((RCC->CR & RCC_CR_PLLRDY) == 0){}/* 选择PLL为系统时钟的时钟源 */RCC->CFGR &= (uint32_t)((uint32_t)~(RCC_CFGR_SW));RCC->CFGR |= (uint32_t)RCC_CFGR_SW_PLL; /* 等到PLL成为系统时钟的时钟源*/while ((RCC->CFGR & (uint32_t)RCC_CFGR_SWS) != (uint32_t)0x08){}}

}

在STM32F030或者STM32F031中同样可以做类似操作:

static void SetSysClock(void)

{__IO uint32_t StartUpCounter = 0, HSEStatus = 0;/* SYSCLK, HCLK, PCLK configuration ----------------------------------------*//* Enable HSE */ RCC->CR |= ((uint32_t)RCC_CR_HSEON);//修改为内部晶振

// RCC->CR &= ~((uint32_t)RCC_CR_HSEON);/* Wait till HSE is ready and if Time out is reached exit */do{HSEStatus = RCC->CR & RCC_CR_HSERDY;StartUpCounter++; } while((HSEStatus == 0) && (StartUpCounter != HSE_STARTUP_TIMEOUT));if ((RCC->CR & RCC_CR_HSERDY) != RESET){HSEStatus = (uint32_t)0x01;}else{HSEStatus = (uint32_t)0x00;} if (HSEStatus == (uint32_t)0x01){/* Enable Prefetch Buffer and set Flash Latency */FLASH->ACR = FLASH_ACR_PRFTBE | FLASH_ACR_LATENCY;/* HCLK = SYSCLK */RCC->CFGR |= (uint32_t)RCC_CFGR_HPRE_DIV1;/* PCLK = HCLK */RCC->CFGR |= (uint32_t)RCC_CFGR_PPRE_DIV1;/* PLL configuration = HSE * 6 = 48 MHz */RCC->CFGR &= (uint32_t)((uint32_t)~(RCC_CFGR_PLLSRC | RCC_CFGR_PLLXTPRE | RCC_CFGR_PLLMULL));RCC->CFGR |= (uint32_t)(RCC_CFGR_PLLSRC_PREDIV1 | RCC_CFGR_PLLXTPRE_PREDIV1 | RCC_CFGR_PLLMULL7);/* Enable PLL */RCC->CR |= RCC_CR_PLLON;/* Wait till PLL is ready */while((RCC->CR & RCC_CR_PLLRDY) == 0){}/* Select PLL as system clock source */RCC->CFGR &= (uint32_t)((uint32_t)~(RCC_CFGR_SW));RCC->CFGR |= (uint32_t)RCC_CFGR_SW_PLL; /* Wait till PLL is used as system clock source */while ((RCC->CFGR & (uint32_t)RCC_CFGR_SWS) != (uint32_t)RCC_CFGR_SWS_PLL){}}else{ /* If HSE fails to start-up, the application will have wrong clock configuration. User can add here some code to deal with this error */// HSI 内部时钟做为PLL时钟源并配置PLL 56M做为系统时钟/* Enable Prefetch Buffer and set Flash Latency */FLASH->ACR = FLASH_ACR_PRFTBE | FLASH_ACR_LATENCY;/* HCLK = SYSCLK */RCC->CFGR |= (uint32_t)RCC_CFGR_HPRE_DIV1;/* PCLK = HCLK */RCC->CFGR |= (uint32_t)RCC_CFGR_PPRE_DIV1;// PLL configuration = (HSI/2) * 12 = 48 MHzRCC_PLLConfig(RCC_PLLSource_HSI_Div2, RCC_PLLMul_14); // 8M/2 * 14 = 56M/* Enable PLL */RCC->CR |= RCC_CR_PLLON;/* Wait till PLL is ready */while ((RCC->CR & RCC_CR_PLLRDY) == 0){}/* Select PLL as system clock source */RCC_SYSCLKConfig(RCC_SYSCLKSource_PLLCLK); // PLL 做系统时钟/* Wait till PLL is used as system clock source */while ((RCC->CFGR & (uint32_t)RCC_CFGR_SWS) != (uint32_t)RCC_CFGR_SWS_PLL){}}

}

在STM32F103中,使用内部晶振,最大时钟频率也只能到64M,受倍频因子的影响嘛,最大只能倍频16倍。 但是在STM32F031中,标准使用内部时钟主频只有48M,但是我们仍然可以继续倍频,用内部时钟进行超频达到64M。在我们的产品中就用过内部超频到56M,USART和SPI长时间无问题。

而GD32E230因为其高达32的倍频因子,内部时钟可以倍频到128M。

但是这种几分钟内没有明显发热现象,不敢做长时间测试,现在MCU有点小贵。干费一个就心疼。

总之,无论ST还是国产,其主频更适合在规定的范围内运行,但是跑极限在短时间内也没有很大的问题。这些数据仅供参考。

至此单片机时钟讲解就结束了,没有多少理论性的东西,主要是解决一些时钟使用时的问题,自己也总是忘,留帖一篇作为自省。

此帖中所有代码都经过本人测试,运行无任何问题,但是对于问题的阐述或者一些见解可能有错误,欢迎大佬们批评指正,一定接受各种批评,努力完善。

相关文章:

关于单片机的时钟浅谈及STM32F103/F030单片机的内外时钟切换问题

绪论 本文主要讲解单片机的时钟系统的相关知识,并进行超频测试,同时介绍如何在STM32F0单片机上进行内外时钟的切换,在不使用外部晶振或者外部晶振不启动时自动切换内部时钟的方法。 一、杂谈 问题来源于群里的一次问答: 诚然&…...

)

centos6.10环境下安装php7.4(基于WLNMP包)

centos6系统已经被官网停止维护,要安装软件必须用第三方的RPM包,下面使用yum安装php7.4正式版,当前基于WLNMP提供的一键安装包来安装 1、添加epel源 yum install epel-release yum install epel-release 2、添加WLNMP一键安装包源 rpm -iv…...

Qt使用第三方库openssl进行RSA加密解密操作详解

一、openssl库的编译,可以参考文档: https://blog.csdn.net/liang19890820/article/details/51658574/ 因为我这里使用的是windows操作系统,可以直接下载exe格式的安装文件,直接安装即可,就包含了我们需要的头文件和库文件,省去了编译操作。exe安装文件下载地址: htt…...

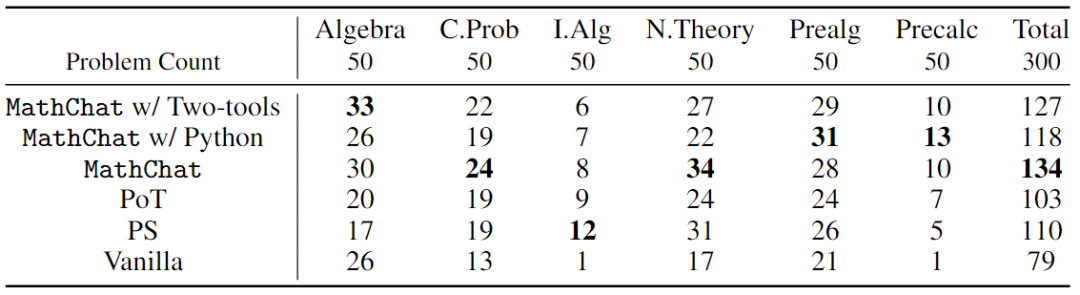

激发数学思维:GPT-4实证研究探索挑战性数学问题

深度学习自然语言处理 原创作者:wkk 考虑到自然语言在许多科学和工程领域表达的数学问题的丰富性,使用大语言模型(LLM)来解决数学问题是一项有趣的研究工作。今天给大家介绍一篇微软研究院联合欧美高校关于如何使用GPT-4解决数学问题的研究论文。 之前的…...

如何配置IP地址

一.自动获取IP 1.dhclient 2.ifconfig 通过这个命令可以查看系统有几块网卡和网卡的IP。 如果您的Linux有多块网卡,那么在Linux中它会显示成eth1, eth2 依此类推 二.手动配置IP 如果您的虚拟机不能自动获取IP,那么只能手动配置,配置方法为&am…...

CentOS + Nginx 环境自动申请和部署Let‘s Encrypt免费SSL证书教程

文章目录 步骤 1:安装Certbot工具步骤 2:配置Nginx服务器步骤 3:生成SSL证书步骤 4:配置Nginx以使用SSL证书步骤 5:重新加载Nginx配置步骤 6:自动续期证书 本文介绍如何在 CentOS Nginx 环境下,…...

浅谈对BI工具价值的看法

浅谈对BI工具价值的看法 BI的定义看法 百度百科的定义: 商业智能(Business Intelligence,简称:BI),又称商业智慧或商务智能,指用现代数据仓库技术、线上分析处理技术、数据挖掘和数据展现技术…...

创建定时任务

import schedule import timedef task():print("Im working...")if __name__ __main__:schedule.every(10).seconds.do(task) # 每10秒一次schedule.every(10).minutes.do(task) # 10分钟一次schedule.every().hour.do(task) # 每小时schedule.every().day.at(&q…...

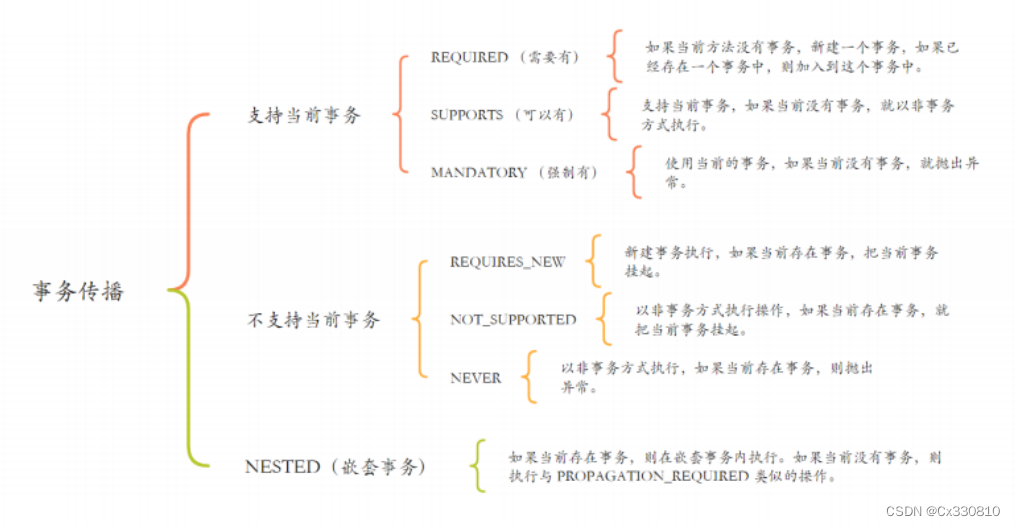

MyBatis的使用、Spring AOP、Spring事务

一、MyBatis 的使用 1、环境配置 1.1、建库建表 -- 创建数据库 drop database if exists mycnblog; create database mycnblog DEFAULT CHARACTER SET utf8mb4;-- 使⽤数据数据 use mycnblog;-- 创建表[⽤户表] drop table if exists userinfo; create table userinfo(id in…...

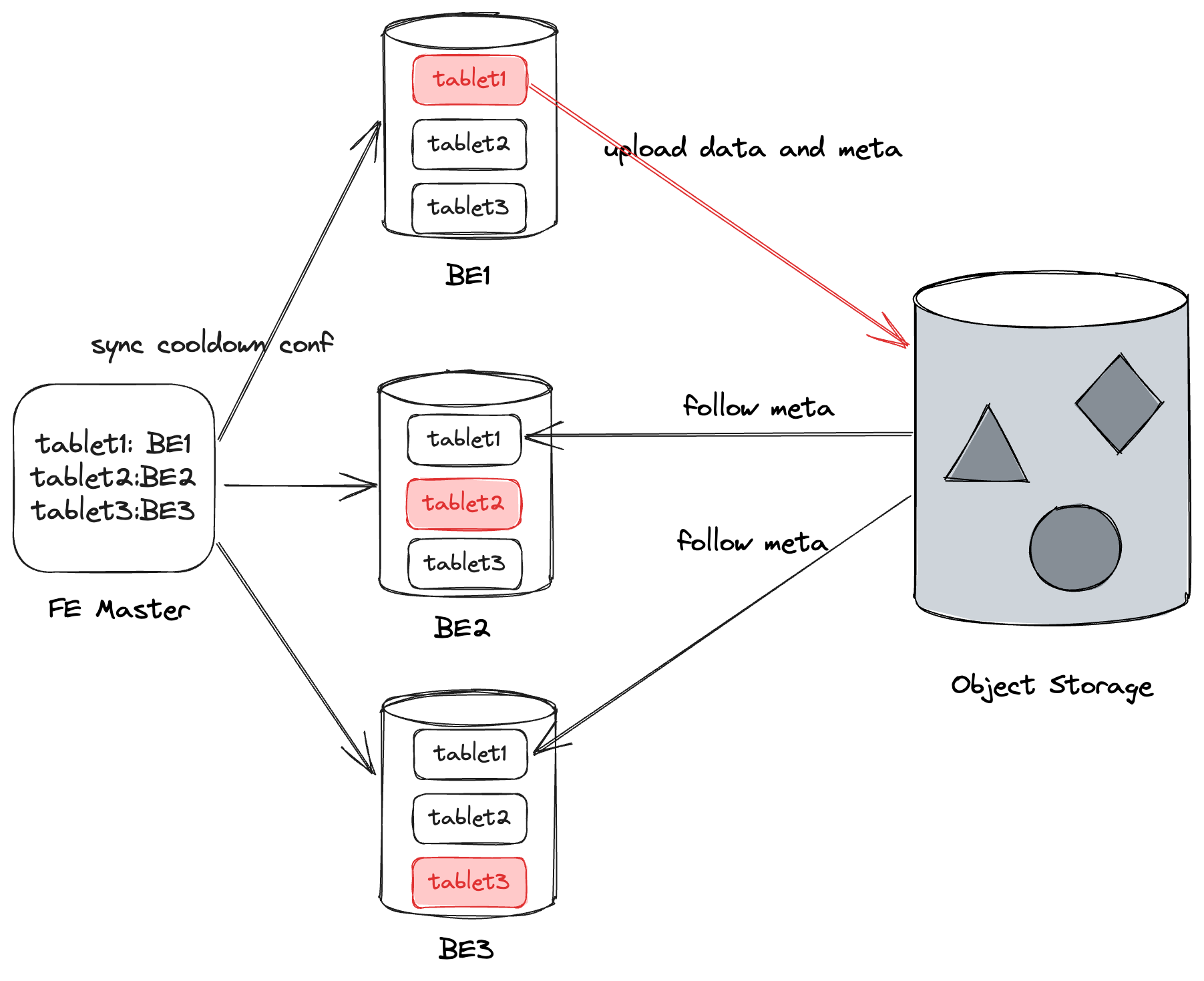

Apache Doris 冷热分层技术如何实现存储成本降低 70%?

在数据分析的实际场景中,冷热数据往往面临着不同的查询频次及响应速度要求。例如在电商订单场景中,用户经常访问近 6 个月的订单,时间较久远的订单访问次数非常少;在行为分析场景中,需支持近期流量数据的高频查询且时效…...

MySQL 两个备机同时挂掉故障分析

来源: 接报线上出现两个5.7.38的备库同时crash,crash堆栈相同,内容如下: stack_bottom 7fd7700b0d30 thread_stack 0x40000 /home/service/app/mysql33066/bin/mysqld(my_print_stacktrace0x2c)[0xf1062c] /home/service/app/m…...

序列化与反序列化深入理解

序列化与反序列化深入理解 1 介绍1.1 概述1.2 序列化实现的需求 2 常用序列化实现函数序列化语言内置开源序列化实现 3 各序列化实现比较4 各序列化实现概述XMLJSONProtobufJava 内置TLVVLE(Variable Length Encoding) 5 flex & bison5.1 介绍应用解…...

hudi系列-小文件优化

hudi使用mvcc来实现数据的读写一致性和并发控制,基于timeline实现对事务和表服务的管理,会产生大量比较小的数据文件和元数据文件。大量小文件会对存储和查询性能产生不利影响,包括增加文件系统的开销、文件管理的复杂性以及查询性能的下降。对于namenode而言,当整个集群中…...

mysql 是否包含 返回索引 截取字符串

是否包含返回索引 原文链接:https://www.cnblogs.com/shoshana-kong/p/16474175.html 方法1:使用通配符%。 通配符也就是模糊匹配,可以分为前导模糊查询、后导模糊查询和全导匹配查询,适用于查询某个字符串中是否包含另一个模糊…...

【LeetCode】74. 搜索二维矩阵

74. 搜索二维矩阵(中等) 方法一:二分查找 思路 总体思路 由于二维矩阵固定列的「从上到下」或者固定行的「从左到右」都是升序的 因此我们可以使用两次二分来定位到目标位置。 第一次二分: 从第 0 列中的「所有行」开始找&#x…...

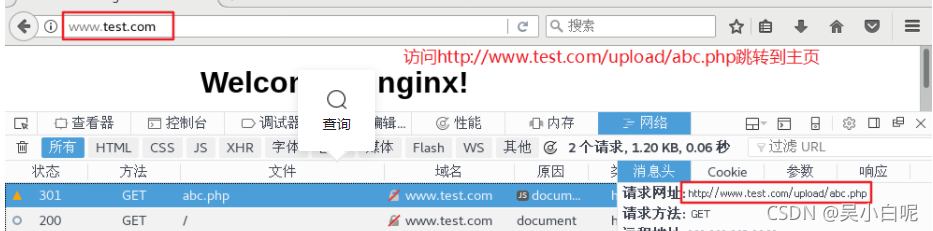

Nginx rewrite

一.location 大致可以分为三类: 精准匹配:location / {…}一般匹配:location / {…}正则匹配:location ~ / {…} 1.location 常用的匹配规则: :进行普通字符精确匹配,也就是完全匹配。^~ &am…...

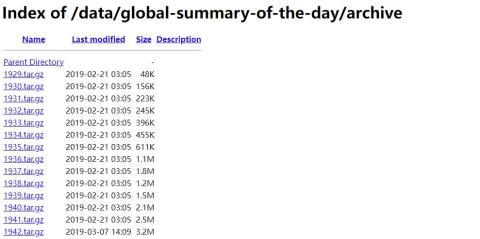

【数据分享】1929-2022年全球站点的逐日降水量(Shp\Excel\12000个站点)

气象数据是在各项研究中都经常使用的数据,气象指标包括气温、风速、降水、湿度等指标,说到常用的降水数据,最详细的降水数据是具体到气象监测站点的降水数据! 有关气象指标的监测站点数据,之前我们分享过1929-2022年全…...

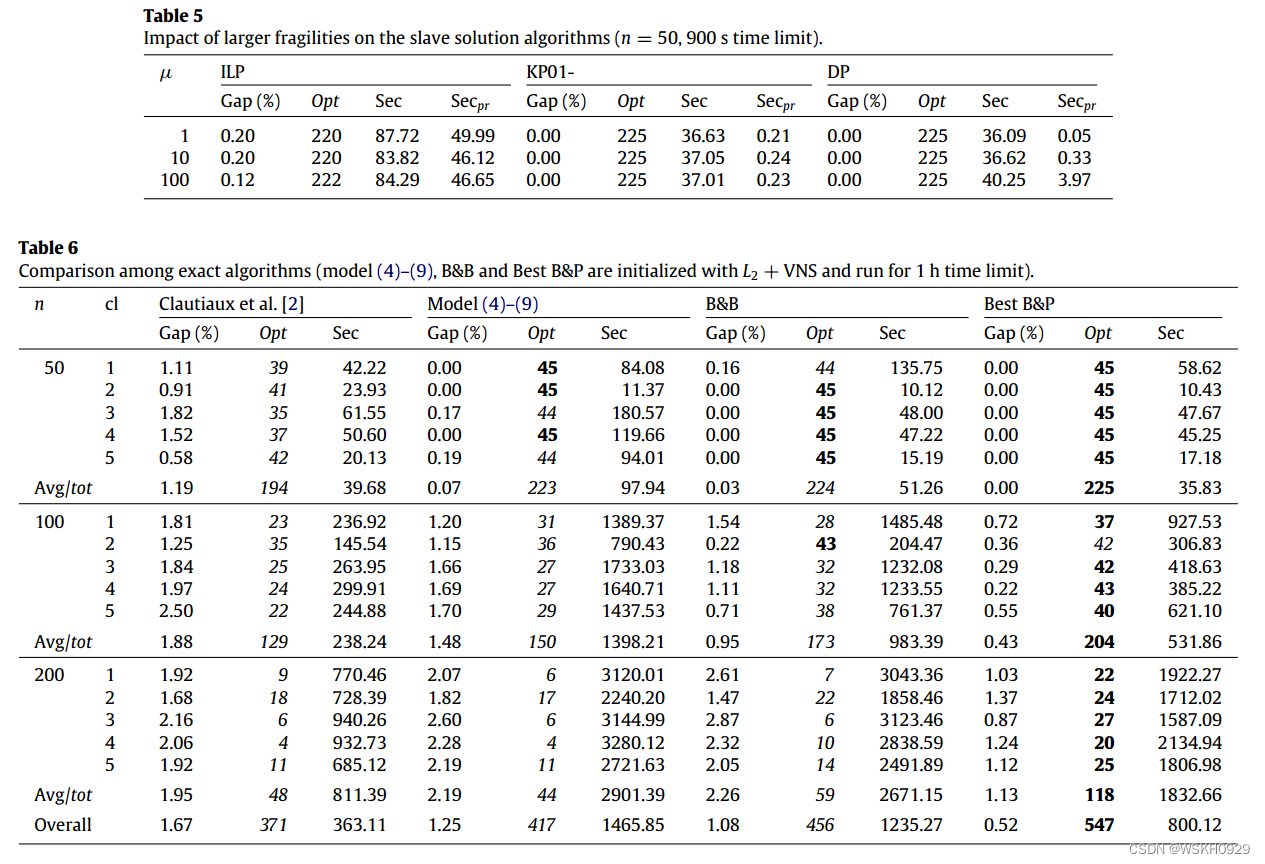

【论文阅读】(2013)Exact algorithms for the bin packing problem with fragile objects

文章目录 一、摘要二、介绍三、之前在这个问题上的工作四、易碎物品背包问题的求解4.1 ILP模型4.2 基于KP01的方法4.3 动态规划 五、二元分支方案5.1 分支方案1(基于决策变量的分支)5.2 分支方案2(基于yj和xji的分支)5.3 将L2嵌入…...

K8S YAML 部署XXLJOB 集群

apiVersion: apps/v1 kind: Deployment metadata: labels: app: xxl-job-admin name: xxl-job-admin namespace: ccetest #根据情况修改namespace spec: replicas: 3 #根据情况修改副本数 selector: matchLabels: app: xxl-job-admin strat…...

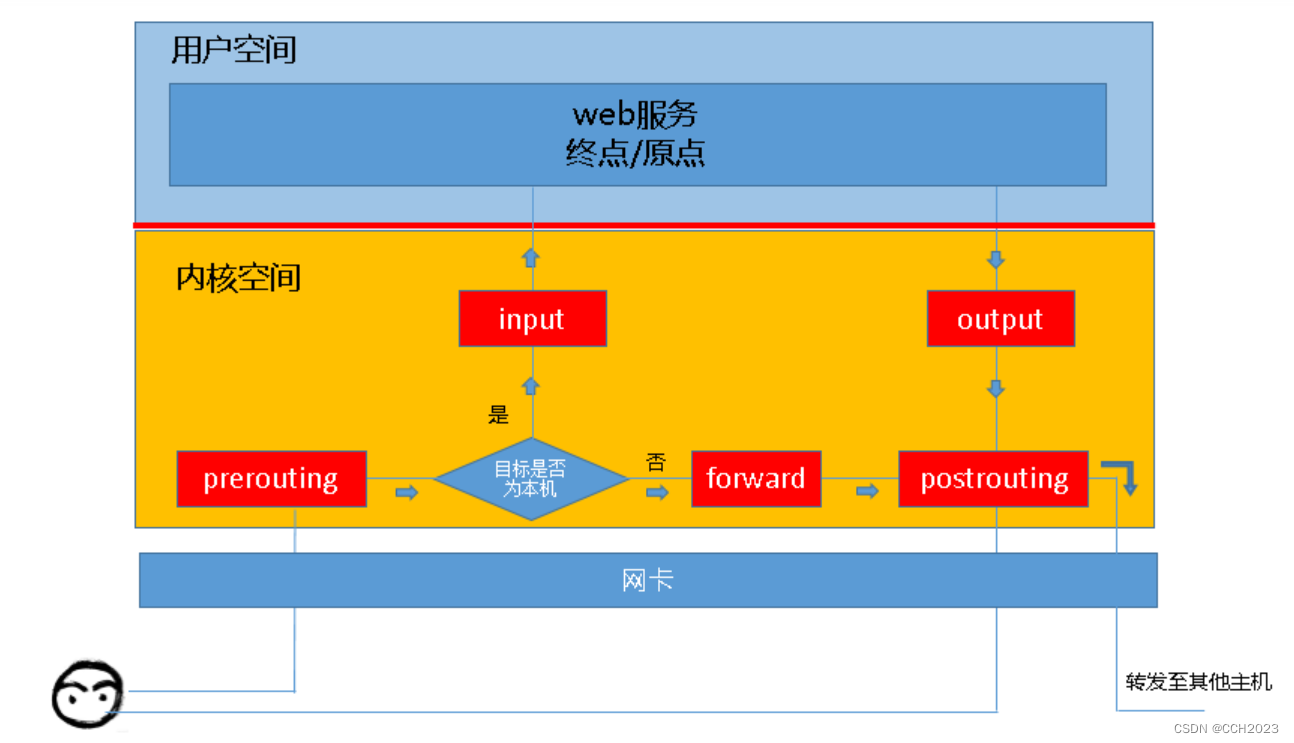

Linux防火墙学习笔记3

iptables链的概念: 当客户端访问服务器端的Web服务的时候,客户端发送请求报文到网卡,而TCP/IP协议栈是属于内核的一部分。客户端的请求报文会通过内核的TCP协议传输到用户空间的Web服务,而客户端报文的目的地址为Web服务器所监听的…...

从 AI 电影到小说:《凰标》延续《第一大道》的东方梦@凤凰标志

科技为翼,文脉为魂; 大道开路,凰标定局。一、时代之问:当AI沦为流量收割机,谁来守护东方文脉? AI 正以惊人的速度渗透文娱产业,却多数被资本用作「快餐内容」的流水线。 海棠山铁哥反其道而行—…...

联想IdeaPad 310S老本升级记:手把手教你加内存、换固态、装Win10+Ubuntu双系统

联想IdeaPad 310S性能重生指南:从硬件升级到双系统实战 每次打开这台2016年购入的联想IdeaPad 310S,风扇的嘶吼和系统卡顿都让人抓狂。作为一款定位入门级的笔记本,它搭载的i3-6006U处理器和4GB内存早已跟不上现代应用的需求。但直接换新机又…...

别再为FDC2214数据抖动发愁了!一个接地气的屏蔽线替代方案与差分测量实战

FDC2214抗干扰实战:差分测量与数据稳定化技巧 在电容式传感项目中,FDC2214作为一款高分辨率多通道电容数字转换器,常被用于纸张计数、液位检测等场景。然而实际应用中,工程师们最头疼的莫过于数据抖动问题——导线轻微移动、环境…...

R语言数据导入全指南:从CSV到SPSS的底层原理与工程实践

1. 项目概述:为什么数据导入是R语言真正的第一道门槛刚接触R的人,十有八九会在读取第一个文件时卡住。不是报错“cannot open the connection”,就是加载出来全是NA,再或者干脆卡死在进度条不动——这根本不是你手生,而…...

VIIRS/NPP夜光数据:从数据获取到区域分析的实用指南

1. VIIRS/NPP夜光数据入门指南 第一次接触VIIRS/NPP夜光数据时,我也被各种专业术语和数据产品搞得晕头转向。这种由美国国家海洋和大气管理局(NOAA)提供的夜间灯光遥感数据,已经成为城市发展、能源消耗和经济活动研究的重要数据源…...

暗黑破坏神2存档编辑器终极指南:d2s-editor让游戏体验更自由

暗黑破坏神2存档编辑器终极指南:d2s-editor让游戏体验更自由 【免费下载链接】d2s-editor 项目地址: https://gitcode.com/gh_mirrors/d2/d2s-editor 你是否曾在暗黑破坏神2中为了一件稀有装备反复刷图数小时?是否因为角色属性点加错而懊恼不已&…...

)

当点云遇上核技巧:一文搞懂K-PCA为何能处理非线性数据(附Sklearn对比实验)

当点云遇上核技巧:一文搞懂K-PCA为何能处理非线性数据(附Sklearn对比实验) 想象你手中握着一团缠绕的毛线——在三维空间里它呈现出复杂的螺旋结构。如果强行用平面镜去照射这个物体,得到的投影永远是一团混乱的线条。这正是线性P…...

终极指南:5分钟快速解密网易云音乐NCM文件,实现音乐自由

终极指南:5分钟快速解密网易云音乐NCM文件,实现音乐自由 【免费下载链接】ncmdump ncmdump - 网易云音乐NCM转换 项目地址: https://gitcode.com/gh_mirrors/ncmdu/ncmdump 还在为网易云音乐下载的NCM格式文件无法在其他播放器播放而烦恼吗&#…...

LOSEHU固件深度解析:泉盛UV-K5/K6全功能固件架构与实战部署指南

LOSEHU固件深度解析:泉盛UV-K5/K6全功能固件架构与实战部署指南 【免费下载链接】uv-k5-firmware-custom 全功能泉盛UV-K5/K6固件 Quansheng UV-K5/K6 Firmware 项目地址: https://gitcode.com/gh_mirrors/uvk5f/uv-k5-firmware-custom LOSEHU固件是一款专为…...

3分钟快速上手:VinXiangQi象棋连线工具的免费AI助手终极指南

3分钟快速上手:VinXiangQi象棋连线工具的免费AI助手终极指南 【免费下载链接】VinXiangQi Xiangqi syncing tool based on Yolov5 / 基于Yolov5的中国象棋连线工具 项目地址: https://gitcode.com/gh_mirrors/vi/VinXiangQi VinXiangQi是一款基于YOLOv5深度学…...