Vitis HLS 学习笔记--块级控制(IDE 2024.1 + 执行模式 + 默认接口实现)

目录

1. 简介

2. 默认接口实现

2.1 执行模式

2.2 接口范式

2.2.1 存储器

2.2.2 串流

2.3.3 寄存器

2.3 Vitis Kernel Flow

2.3.1 默认的协议

2.3.2 vadd 代码

2.3.3 查看报告

2.4 Vivado IP Flow

2.4.1 默认的协议

2.4.2 vadd 代码

2.4.3 查看报告

3. 测试与波形

3.1 TestBench

3.2 理解控制协议

3.3 Wave Viewer

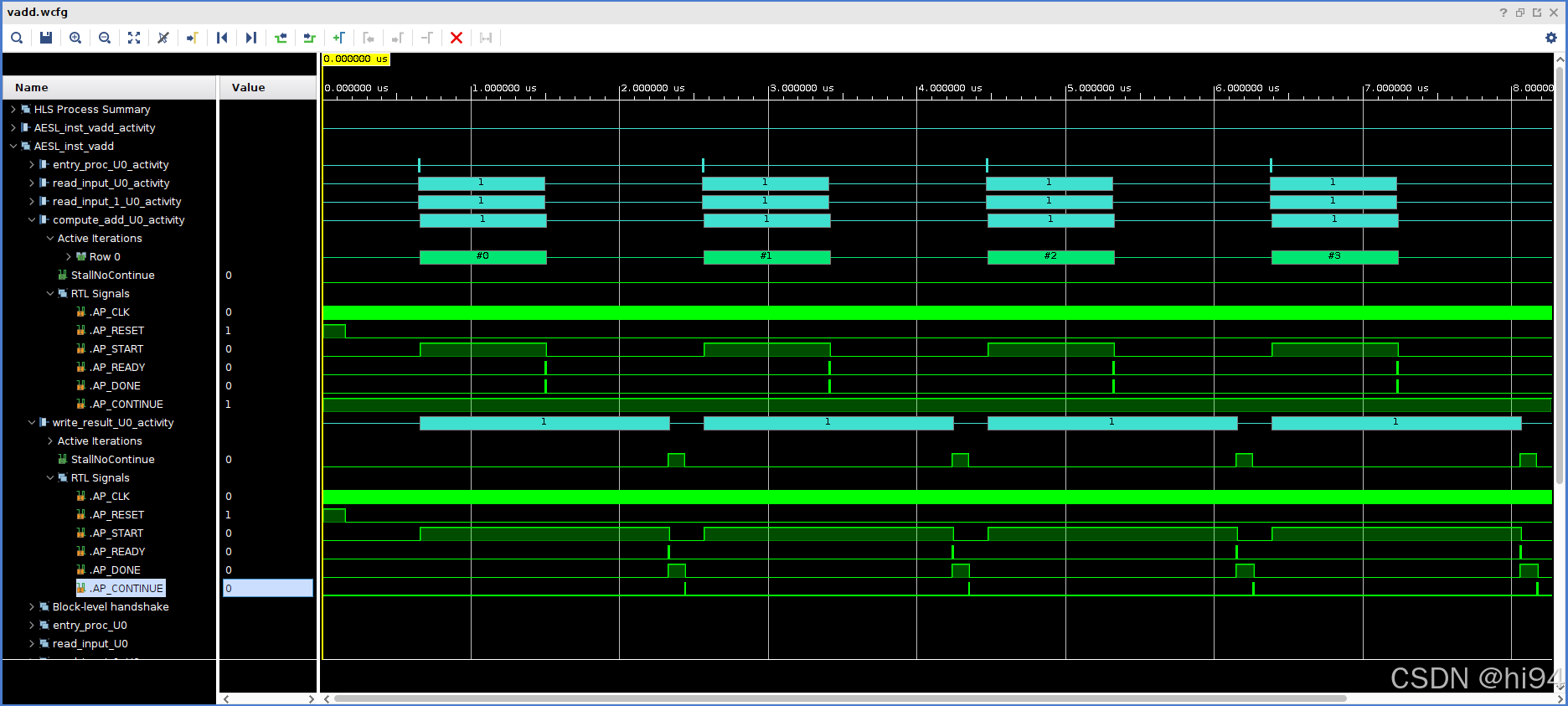

3.3.1 整体波形

3.3.2 ap_ctrl 信号

4. 模块拆分

4.1 分析

4.2 compute_add

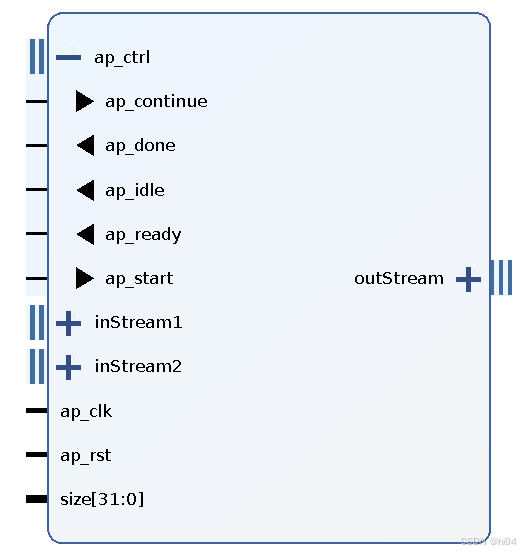

4.2 IP 图

5. 总结

1. 简介

本文总结 HLS 块级控制协议,包括以下内容:

- 执行模式

- 重叠模式

- 顺序模式

- 自动重启模式

- 接口范式

- 存储器

- 串流

- 寄存器

- 对比 Vitis Kernel Flow 与 Vivado IP Flow 示例

- 了解 Wave Viewer 中的波形

原示例:

https://github.com/Xilinx/Vitis_Accel_Examples/tree/main/hello_world![]() https://github.com/Xilinx/Vitis_Accel_Examples/tree/main/hello_world

https://github.com/Xilinx/Vitis_Accel_Examples/tree/main/hello_world

2. 默认接口实现

2.1 执行模式

1)Vitis kernel 或 Vivado IP 的执行模式由块级控制协议以及 HLS 设计中的子函数结构定义。

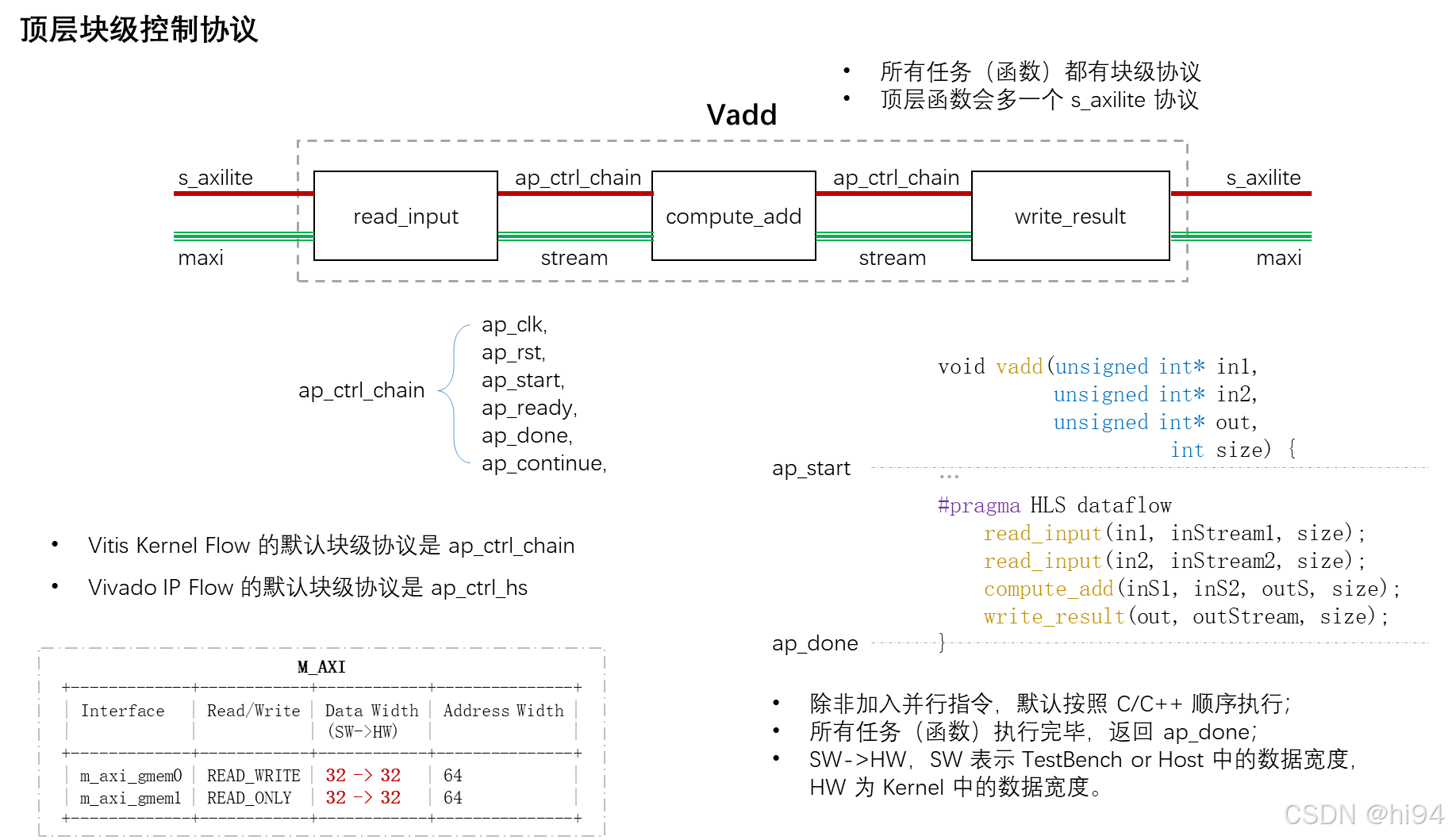

- 对于控制驱动的任务级并行(TLP),ap_ctrl_chain 和 ap_ctrl_hs 协议支持顺序执行或流水线执行。对于数据驱动的TLP,ap_ctrl_none是必需的控制协议。

- ap_ctrl_chain 控制协议是 Vitis kernel Flow 的默认协议。

- ap_ctrl_hs 块级控制协议是 Vivado IP Flow 的默认协议。

- 然而,当将 HLS 设计链接在一起时,应使用 ap_ctrl_chain,因为它能更好地支持流水线执行。

- 可以使用 INTERFACE 编译指示或指令在函数返回值(return)上指定块级控制协议。

2)重叠模式

允许在当前事务完成之前开始新事务的执行。通过函数流水线、循环回绕或数据流执行,一旦设计准备就绪,重叠的块运行就可以开始处理额外的数据。

3)顺序模式

要求当前事务完成之后,才能开始新事务的执行。

4)自动重启模式

自动重启模式允许 HLS 设计在准备好开始处理额外数据时自动重启模块。此模式同时支持重叠执行和顺序执行。自动重启是数据驱动的 TLP 设计的方法,但也可以应用于控制驱动的TLP设计。

2.2 接口范式

2.2.1 存储器

描述:内核通过存储器(如 DDR、HBM、PLRAM/BRAM/URAM)来访问数据

接口类型:ap_memory 和 AXI4 AXI4 Memory Mapped (m_axi)

2.2.2 串流

描述:数据从另一个流源(如视频处理器或其他内核)流入内核,也可以从内核流出。

接口类型:ap_fifo, AXI4-Stream (axis)

2.3.3 寄存器

描述:内核通过寄存器接口进行读写操作访问数据。

接口类型:ap_none、ap_hs、ap_ack、ap_ovld、ap_vld、AXI4-Lite adapter (s_axilite)

2.3 Vitis Kernel Flow

2.3.1 默认的协议

| C 语言实参类型 | 范式 | 接口协议 I/O/Inout |

| 标量(值传递) | 寄存器 | AXI4-Lite(s_axilite) |

| 阵列 | 存储器 | AXI4 存储器映射(m_axi) |

| 指向阵列的指针 | 存储器 | AXI4 存储器映射(m_axi) |

| 指向标量的指针 | 寄存器 | AXI4-Lite(s_axilite) |

| 引用 | 寄存器 | AXI4-Lite(s_axilite) |

| hls::stream | 串流 | AXI4-Stream(axis) |

2.3.2 vadd 代码

#include <stdint.h>

#include <hls_stream.h>const int c_size = 4096;static void read_input(unsigned int* in, hls::stream<unsigned int>& inStream, int size) {

mem_rd:for (int i = 0; i < size; i++) {

#pragma HLS LOOP_TRIPCOUNT min = c_size max = c_sizeinStream << in[i];}

}static void compute_add(hls::stream<unsigned int>& inStream1,hls::stream<unsigned int>& inStream2,hls::stream<unsigned int>& outStream,int size) {

compute:for (int i = 0; i < size; i++) {

#pragma HLS LOOP_TRIPCOUNT min = c_size max = c_sizeoutStream << (inStream1.read() + inStream2.read());}

}static void write_result(unsigned int* out, hls::stream<unsigned int>& outStream, int size) {

mem_wr:for (int i = 0; i < size; i++) {

#pragma HLS LOOP_TRIPCOUNT min = c_size max = c_sizeout[i] = outStream.read();}

}extern "C" {

void vadd(unsigned int* in1, unsigned int* in2, unsigned int* out, int size) {

#pragma HLS INTERFACE m_axi port = in1 bundle = gmem0 depth=c_size

#pragma HLS INTERFACE m_axi port = in2 bundle = gmem1 depth=c_size

#pragma HLS INTERFACE m_axi port = out bundle = gmem0 depth=c_sizestatic hls::stream<unsigned int> inStream1("input_stream_1");static hls::stream<unsigned int> inStream2("input_stream_2");static hls::stream<unsigned int> outStream("output_stream");#pragma HLS dataflowread_input(in1, inStream1, size);read_input(in2, inStream2, size);compute_add(inStream1, inStream2, outStream, size);write_result(out, outStream, size);

}

}对应的 config 文件:

part=xck26-sfvc784-2LV-c[hls]

flow_target=vitis

package.output.format=ip_catalog

package.output.syn=false

syn.file=vadd.cpp

tb.file=test.cpp

syn.top=vadd

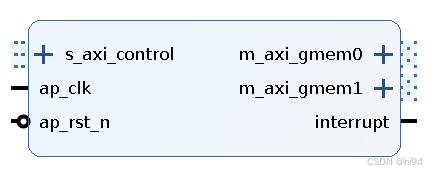

cosim.trace_level=allIP 图:

2.3.3 查看报告

================================================================

== Synthesis Summary Report of 'vadd'

================================================================

+ General Information: * Date: xxxx* Version: 2024.1 (Build 5069499 on May 21 2024)* Project: vadd* Solution: hls (Vitis Kernel Flow Target)* Product family: zynquplus* Target device: xck26-sfvc784-2LV-c+ Performance & Resource Estimates: PS: '+' for module; 'o' for loop; '*' for dataflow+----------------------------------+------+------+---------+-----------+----------+---------+------+----------+--------+----+-----------+-----------+-----+| Modules | Issue| | Latency | Latency | Iteration| | Trip | | | | | | || & Loops | Type | Slack| (cycles)| (ns) | Latency | Interval| Count| Pipelined| BRAM | DSP| FF | LUT | URAM|+----------------------------------+------+------+---------+-----------+----------+---------+------+----------+--------+----+-----------+-----------+-----+|+ vadd* | -| 0.00| 4243| 4.243e+04| -| 4173| -| dataflow| 6 (2%)| -| 3329 (1%)| 4371 (3%)| -|| + entry_proc | -| 5.46| 0| 0.000| -| 0| -| no| -| -| 3 (~0%)| 29 (~0%)| -|| + read_input | -| 0.00| 4172| 4.172e+04| -| 4172| -| no| -| -| 238 (~0%)| 785 (~0%)| -|| + read_input_Pipeline_mem_rd | -| 0.00| 4099| 4.099e+04| -| 4099| -| no| -| -| 68 (~0%)| 135 (~0%)| -|| o mem_rd | -| 7.30| 4097| 4.097e+04| 3| 1| 4096| yes| -| -| -| -| -|| + read_input_1 | -| 0.00| 4170| 4.170e+04| -| 4170| -| no| -| -| 371 (~0%)| 258 (~0%)| -|| o mem_rd | -| 7.30| 4168| 4.168e+04| 74| 1| 4096| yes| -| -| -| -| -|| + compute_add | -| 2.61| 4100| 4.100e+04| -| 4100| -| no| -| -| 71 (~0%)| 261 (~0%)| -|| + compute_add_Pipeline_compute | -| 2.61| 4098| 4.098e+04| -| 4098| -| no| -| -| 34 (~0%)| 185 (~0%)| -|| o compute | -| 7.30| 4096| 4.096e+04| 2| 1| 4096| yes| -| -| -| -| -|| + write_result | -| 0.00| 4170| 4.170e+04| -| 4170| -| no| -| -| 267 (~0%)| 786 (~0%)| -|| + write_result_Pipeline_mem_wr | -| 0.00| 4099| 4.099e+04| -| 4099| -| no| -| -| 68 (~0%)| 137 (~0%)| -|| o mem_wr | -| 7.30| 4097| 4.097e+04| 3| 1| 4096| yes| -| -| -| -| -|+----------------------------------+------+------+---------+-----------+----------+---------+------+----------+--------+----+-----------+-----------+-----+================================================================

== HW Interfaces

================================================================

* M_AXI

+-------------+------------+------------+---------------+---------+--------+----------+-----------+--------------+--------------+-------------+-------------+-------------------+

| Interface | Read/Write | Data Width | Address Width | Latency | Offset | Register | Max Widen | Max Read | Max Write | Num Read | Num Write | Resource Estimate |

| | | (SW->HW) | | | | | Bitwidth | Burst Length | Burst Length | Outstanding | Outstanding | |

+-------------+------------+------------+---------------+---------+--------+----------+-----------+--------------+--------------+-------------+-------------+-------------------+

| m_axi_gmem0 | READ_WRITE | 32 -> 32 | 64 | 64 | slave | 0 | 512 | 16 | 16 | 16 | 16 | BRAM=4 |

| m_axi_gmem1 | READ_ONLY | 32 -> 32 | 64 | 64 | slave | 0 | 512 | 16 | 16 | 16 | 16 | BRAM=2 |

+-------------+------------+------------+---------------+---------+--------+----------+-----------+--------------+--------------+-------------+-------------+-------------------+* S_AXILITE Interfaces

+---------------+------------+---------------+--------+----------+

| Interface | Data Width | Address Width | Offset | Register |

+---------------+------------+---------------+--------+----------+

| s_axi_control | 32 | 6 | 16 | 0 |

+---------------+------------+---------------+--------+----------+* S_AXILITE Registers

+---------------+----------+--------+-------+--------+----------------------------------+------------------------------------------------------------------------------------+

| Interface | Register | Offset | Width | Access | Description | Bit Fields |

+---------------+----------+--------+-------+--------+----------------------------------+------------------------------------------------------------------------------------+

| s_axi_control | CTRL | 0x00 | 32 | RW | Control signals | 0=AP_START 1=AP_DONE 2=AP_IDLE 3=AP_READY 4=AP_CONTINUE 7=AUTO_RESTART 9=INTERRUPT |

| s_axi_control | GIER | 0x04 | 32 | RW | Global Interrupt Enable Register | 0=Enable |

| s_axi_control | IP_IER | 0x08 | 32 | RW | IP Interrupt Enable Register | 0=CHAN0_INT_EN 1=CHAN1_INT_EN |

| s_axi_control | IP_ISR | 0x0c | 32 | RW | IP Interrupt Status Register | 0=CHAN0_INT_ST 1=CHAN1_INT_ST |

| s_axi_control | in1_1 | 0x10 | 32 | W | Data signal of in1 | |

| s_axi_control | in1_2 | 0x14 | 32 | W | Data signal of in1 | |

| s_axi_control | in2_1 | 0x1c | 32 | W | Data signal of in2 | |

| s_axi_control | in2_2 | 0x20 | 32 | W | Data signal of in2 | |

| s_axi_control | out_r_1 | 0x28 | 32 | W | Data signal of out_r | |

| s_axi_control | out_r_2 | 0x2c | 32 | W | Data signal of out_r | |

| s_axi_control | size | 0x34 | 32 | W | Data signal of size | |

+---------------+----------+--------+-------+--------+----------------------------------+------------------------------------------------------------------------------------+* TOP LEVEL CONTROL

+-----------+---------------+-----------+

| Interface | Type | Ports |

+-----------+---------------+-----------+

| ap_clk | clock | ap_clk |

| ap_rst_n | reset | ap_rst_n |

| interrupt | interrupt | interrupt |

| ap_ctrl | ap_ctrl_chain | |

+-----------+---------------+-----------+================================================================

== SW I/O Information

================================================================

* Top Function Arguments

+----------+-----------+---------------+

| Argument | Direction | Datatype |

+----------+-----------+---------------+

| in1 | inout | unsigned int* |

| in2 | in | unsigned int* |

| out | inout | unsigned int* |

| size | in | int |

+----------+-----------+---------------+* SW-to-HW Mapping

+----------+---------------+-----------+----------+-----------------------------------+

| Argument | HW Interface | HW Type | HW Usage | HW Info |

+----------+---------------+-----------+----------+-----------------------------------+

| in1 | m_axi_gmem0 | interface | | channel=0 |

| in1 | s_axi_control | register | offset | name=in1_1 offset=0x10 range=32 |

| in1 | s_axi_control | register | offset | name=in1_2 offset=0x14 range=32 |

| in2 | m_axi_gmem1 | interface | | channel=0 |

| in2 | s_axi_control | register | offset | name=in2_1 offset=0x1c range=32 |

| in2 | s_axi_control | register | offset | name=in2_2 offset=0x20 range=32 |

| out | m_axi_gmem0 | interface | | channel=0 |

| out | s_axi_control | register | offset | name=out_r_1 offset=0x28 range=32 |

| out | s_axi_control | register | offset | name=out_r_2 offset=0x2c range=32 |

| size | s_axi_control | register | | name=size offset=0x34 range=32 |

+----------+---------------+-----------+----------+-----------------------------------+================================================================

== M_AXI Burst Information

================================================================Note: All burst requests might be further partitioned into multiple requests during RTL generation based on max_read_burst_length or max_write_burst_length settings.* Inferred Burst Summary

+--------------+-----------+----------+-------+--------+---------------+

| HW Interface | Direction | Length | Width | Loop | Loop Location |

+--------------+-----------+----------+-------+--------+---------------+

| m_axi_gmem0 | read | variable | 32 | mem_rd | vadd.cpp:8:5 |

| m_axi_gmem0 | write | variable | 32 | mem_wr | vadd.cpp:27:5 |

| m_axi_gmem1 | read | variable | 32 | mem_rd | vadd.cpp:8:5 |

+--------------+-----------+----------+-------+--------+---------------+* All M_AXI Variable Accesses

+-------------------+----------+-----------------+-----------+--------------+----------+--------+---------------+------------+------------------------------------------------+

| HW Interface | Variable | Access Location | Direction | Burst Status | Length | Loop | Loop Location | Resolution | Problem |

+-------------------+----------+-----------------+-----------+--------------+----------+--------+---------------+------------+------------------------------------------------+

| m_axi_gmem0 | out | vadd.cpp:29:9 | write | Widen Fail | | mem_wr | vadd.cpp:27:5 | 214-234 | Sequential access length is not divisible by 2 |

| m_axi_gmem0 | out | vadd.cpp:29:9 | write | Inferred | variable | mem_wr | vadd.cpp:27:5 | | |

| m_axi_gmem0,gmem1 | in | vadd.cpp:10:11 | read | Widen Fail | | mem_rd | vadd.cpp:8:5 | 214-234 | Sequential access length is not divisible by 2 |

| m_axi_gmem0,gmem1 | in | vadd.cpp:10:11 | read | Inferred | variable | mem_rd | vadd.cpp:8:5 | | |

+-------------------+----------+-----------------+-----------+--------------+----------+--------+---------------+------------+------------------------------------------------+* Resolution URL: docs.xilinx.com/access/sources/dita/topic?Doc_Version=2024.1%20English&url=ug1448-hls-guidance&resourceid=XXX-YYY.html (replace XXX-YYY with column value)================================================================

== Bind Op Report

================================================================

+----------------------------------+-----+--------+------------+--------+----------+---------+

| Name | DSP | Pragma | Variable | Op | Impl | Latency |

+----------------------------------+-----+--------+------------+--------+----------+---------+

| + vadd | 0 | | | | | |

| + read_input | 0 | | | | | |

| icmp_ln8_fu_94_p2 | | | icmp_ln8 | setgt | auto | 0 |

| empty_fu_104_p3 | | | empty | select | auto_sel | 0 |

| + read_input_Pipeline_mem_rd | 0 | | | | | |

| icmp_ln8_fu_98_p2 | | | icmp_ln8 | setlt | auto | 0 |

| add_ln8_fu_104_p2 | | | add_ln8 | add | fabric | 0 |

| + read_input_1 | 0 | | | | | |

| icmp_ln8_fu_112_p2 | | | icmp_ln8 | setgt | auto | 0 |

| empty_fu_122_p3 | | | empty | select | auto_sel | 0 |

| icmp_ln8_1_fu_146_p2 | | | icmp_ln8_1 | setlt | auto | 0 |

| add_ln8_fu_152_p2 | | | add_ln8 | add | fabric | 0 |

| + compute_add | 0 | | | | | |

| + compute_add_Pipeline_compute | 0 | | | | | |

| icmp_ln19_fu_81_p2 | | | icmp_ln19 | setlt | auto | 0 |

| add_ln19_fu_87_p2 | | | add_ln19 | add | fabric | 0 |

| add_ln21_fu_98_p2 | | | add_ln21 | add | fabric | 0 |

| + write_result | 0 | | | | | |

| icmp_ln27_fu_85_p2 | | | icmp_ln27 | setgt | auto | 0 |

| empty_fu_105_p3 | | | empty | select | auto_sel | 0 |

| + write_result_Pipeline_mem_wr | 0 | | | | | |

| icmp_ln27_fu_102_p2 | | | icmp_ln27 | setlt | auto | 0 |

| add_ln27_fu_108_p2 | | | add_ln27 | add | fabric | 0 |

+----------------------------------+-----+--------+------------+--------+----------+---------+================================================================

== Storage Report

================================================================

+-------------------+--------------+-------------+------+------+--------+-----------+------+---------+------------------+

| Name | Usage | Type | BRAM | URAM | Pragma | Variable | Impl | Latency | Bitwidth, Depth, |

| | | | | | | | | | Banks |

+-------------------+--------------+-------------+------+------+--------+-----------+------+---------+------------------+

| + vadd | | | 6 | 0 | | | | | |

| control_s_axi_U | interface | s_axilite | | | | | | | |

| gmem0_m_axi_U | interface | m_axi | 4 | | | | | | |

| gmem1_m_axi_U | interface | m_axi | 2 | | | | | | |

| out_r_c_U | fifo channel | scalar prop | | | | out_r_c | srl | 0 | 64, 4, 1 |

| size_c1_U | fifo channel | scalar prop | | | | size_c1 | srl | 0 | 32, 2, 1 |

| inStream1_U | fifo channel | stream | | | | inStream1 | srl | 0 | 32, 2, 1 |

| inStream2_U | fifo channel | stream | | | | inStream2 | srl | 0 | 32, 2, 1 |

| size_c_U | fifo channel | scalar prop | | | | size_c | srl | 0 | 32, 2, 1 |

| outStream_U | fifo channel | stream | | | | outStream | srl | 0 | 32, 2, 1 |

+-------------------+--------------+-------------+------+------+--------+-----------+------+---------+------------------+================================================================

== Pragma Report

================================================================

* Valid Pragma Syntax

+----------------+----------------------------------------------+-----------------------------+

| Type | Options | Location |

+----------------+----------------------------------------------+-----------------------------+

| loop_tripcount | min = c_size max = c_size | vadd.cpp:9 in read_input |

| loop_tripcount | min = c_size max = c_size | vadd.cpp:20 in compute_add |

| loop_tripcount | min = c_size max = c_size | vadd.cpp:28 in write_result |

| interface | m_axi port = in1 bundle = gmem0 depth=c_size | vadd.cpp:35 in vadd |

| interface | m_axi port = in2 bundle = gmem1 depth=c_size | vadd.cpp:36 in vadd |

| interface | m_axi port = out bundle = gmem0 depth=c_size | vadd.cpp:37 in vadd |

| dataflow | | vadd.cpp:43 in vadd |

+----------------+----------------------------------------------+-----------------------------+2.4 Vivado IP Flow

2.4.1 默认的协议

| C 语言实参类型 | 支持的范式 | 默认范式 | 接口协议 | ||

| In | Out | InOut | |||

| 标量(值传递) | 寄存器 | 寄存器 | ap_none | - | - |

| 阵列 | 存储器、串流 | 存储器 | ap_memory | ap_memory | ap_memory |

| 指针 | 存储器、串流、寄存器 | 寄存器 | ap_none | ap_vld | ap_ovld |

| 引用 | 寄存器 | 寄存器 | ap_none | ap_vld | ap_vld |

| hls::stream | 串流 | 串流 | ap_fifo | ap_fifo | - |

2.4.2 vadd 代码

#include <stdint.h>

#include <hls_stream.h>const int c_size = 4096;static void read_input(unsigned int* in, hls::stream<unsigned int>& inStream, int size) {

#pragma HLS INTERFACE mode=ap_ctrl_chain port=returnmem_rd:for (int i = 0; i < size; i++) {

#pragma HLS LOOP_TRIPCOUNT min = c_size max = c_sizeinStream << in[i];}

}static void compute_add(hls::stream<unsigned int>& inStream1,hls::stream<unsigned int>& inStream2,hls::stream<unsigned int>& outStream,int size) {

#pragma HLS INTERFACE mode=ap_ctrl_chain port=returncompute:for (int i = 0; i < size; i++) {

#pragma HLS LOOP_TRIPCOUNT min = c_size max = c_sizeoutStream << (inStream1.read() + inStream2.read());}

}static void write_result(unsigned int* out, hls::stream<unsigned int>& outStream, int size) {

#pragma HLS INTERFACE mode=ap_ctrl_chain port=returnmem_wr:for (int i = 0; i < size; i++) {

#pragma HLS LOOP_TRIPCOUNT min = c_size max = c_sizeout[i] = outStream.read();}

}extern "C" {

void vadd(unsigned int* in1, unsigned int* in2, unsigned int* out, int size) {

//#pragma HLS INTERFACE mode=ap_ctrl_chain port=return

//#pragma HLS INTERFACE mode=s_axilite port=return bundle=control//#pragma HLS INTERFACE mode=s_axilite port=in1 bundle=control

//#pragma HLS INTERFACE mode=s_axilite port=in2 bundle=control

//#pragma HLS INTERFACE mode=s_axilite port=out bundle=control

//#pragma HLS INTERFACE mode=s_axilite port=size bundle=control#pragma HLS INTERFACE mode=m_axi port=in1 bundle=gmem0 depth=c_size

#pragma HLS INTERFACE mode=m_axi port=in2 bundle=gmem1 depth=c_size

#pragma HLS INTERFACE mode=m_axi port=out bundle=gmem0 depth=c_sizestatic hls::stream<unsigned int> inStream1("input_stream_1");static hls::stream<unsigned int> inStream2("input_stream_2");static hls::stream<unsigned int> outStream("output_stream");#pragma HLS dataflowread_input(in1, inStream1, size);read_input(in2, inStream2, size);compute_add(inStream1, inStream2, outStream, size);write_result(out, outStream, size);

}

}对应的 config 文件:

part=xck26-sfvc784-2LV-c[hls]

flow_target=vivado

package.output.format=ip_catalog

package.output.syn=false

syn.file=vadd.cpp

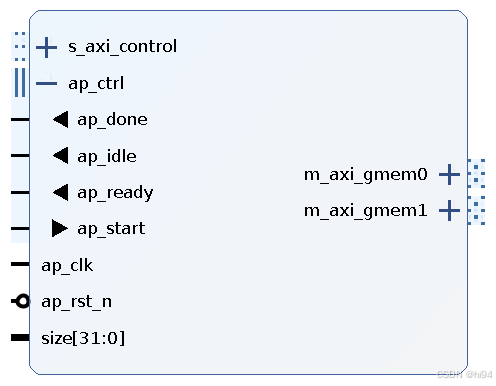

syn.top=vaddIP 图:

2.4.3 查看报告

================================================================

== Synthesis Summary Report of 'vadd'

================================================================

+ General Information: * Date: xxxx* Version: 2024.1 (Build 5069499 on May 21 2024)* Project: vadd* Solution: hls (Vivado IP Flow Target)* Product family: zynquplus* Target device: xck26-sfvc784-2LV-c+ Performance & Resource Estimates: PS: '+' for module; 'o' for loop; '*' for dataflow+----------------------------------+------+------+---------+-----------+----------+---------+------+----------+--------+----+-----------+-----------+-----+| Modules | Issue| | Latency | Latency | Iteration| | Trip | | | | | | || & Loops | Type | Slack| (cycles)| (ns) | Latency | Interval| Count| Pipelined| BRAM | DSP| FF | LUT | URAM|+----------------------------------+------+------+---------+-----------+----------+---------+------+----------+--------+----+-----------+-----------+-----+|+ vadd* | -| 0.00| 4117| 4.117e+04| -| 4110| -| dataflow| 6 (2%)| -| 3030 (1%)| 3648 (3%)| -|| + entry_proc | -| 5.46| 0| 0.000| -| 0| -| no| -| -| 3 (~0%)| 29 (~0%)| -|| + read_input | -| 0.00| 4109| 4.109e+04| -| 4109| -| no| -| -| 175 (~0%)| 449 (~0%)| -|| + read_input_Pipeline_mem_rd | -| 0.00| 4099| 4.099e+04| -| 4099| -| no| -| -| 68 (~0%)| 135 (~0%)| -|| o mem_rd | -| 7.30| 4097| 4.097e+04| 3| 1| 4096| yes| -| -| -| -| -|| + read_input_1 | -| 0.00| 4107| 4.107e+04| -| 4107| -| no| -| -| 245 (~0%)| 258 (~0%)| -|| o mem_rd | -| 7.30| 4105| 4.105e+04| 11| 1| 4096| yes| -| -| -| -| -|| + compute_add | -| 2.61| 4100| 4.100e+04| -| 4100| -| no| -| -| 71 (~0%)| 261 (~0%)| -|| + compute_add_Pipeline_compute | -| 2.61| 4098| 4.098e+04| -| 4098| -| no| -| -| 34 (~0%)| 185 (~0%)| -|| o compute | -| 7.30| 4096| 4.096e+04| 2| 1| 4096| yes| -| -| -| -| -|| + write_result | -| 0.00| 4107| 4.107e+04| -| 4107| -| no| -| -| 204 (~0%)| 463 (~0%)| -|| + write_result_Pipeline_mem_wr | -| 0.00| 4099| 4.099e+04| -| 4099| -| no| -| -| 68 (~0%)| 137 (~0%)| -|| o mem_wr | -| 7.30| 4097| 4.097e+04| 3| 1| 4096| yes| -| -| -| -| -|+----------------------------------+------+------+---------+-----------+----------+---------+------+----------+--------+----+-----------+-----------+-----+================================================================

== HW Interfaces

================================================================

* M_AXI

+-------------+------------+------------+---------------+---------+--------+----------+-----------+--------------+--------------+-------------+-------------+-------------------+

| Interface | Read/Write | Data Width | Address Width | Latency | Offset | Register | Max Widen | Max Read | Max Write | Num Read | Num Write | Resource Estimate |

| | | (SW->HW) | | | | | Bitwidth | Burst Length | Burst Length | Outstanding | Outstanding | |

+-------------+------------+------------+---------------+---------+--------+----------+-----------+--------------+--------------+-------------+-------------+-------------------+

| m_axi_gmem0 | READ_WRITE | 32 -> 32 | 64 | 0 | slave | 0 | 0 | 16 | 16 | 16 | 16 | BRAM=4 |

| m_axi_gmem1 | READ_ONLY | 32 -> 32 | 64 | 0 | slave | 0 | 0 | 16 | 16 | 16 | 16 | BRAM=2 |

+-------------+------------+------------+---------------+---------+--------+----------+-----------+--------------+--------------+-------------+-------------+-------------------+* S_AXILITE Interfaces

+---------------+------------+---------------+--------+----------+

| Interface | Data Width | Address Width | Offset | Register |

+---------------+------------+---------------+--------+----------+

| s_axi_control | 32 | 6 | 16 | 0 |

+---------------+------------+---------------+--------+----------+* S_AXILITE Registers

+---------------+----------+--------+-------+--------+----------------------+

| Interface | Register | Offset | Width | Access | Description |

+---------------+----------+--------+-------+--------+----------------------+

| s_axi_control | in1_1 | 0x10 | 32 | W | Data signal of in1 |

| s_axi_control | in1_2 | 0x14 | 32 | W | Data signal of in1 |

| s_axi_control | in2_1 | 0x1c | 32 | W | Data signal of in2 |

| s_axi_control | in2_2 | 0x20 | 32 | W | Data signal of in2 |

| s_axi_control | out_r_1 | 0x28 | 32 | W | Data signal of out_r |

| s_axi_control | out_r_2 | 0x2c | 32 | W | Data signal of out_r |

+---------------+----------+--------+-------+--------+----------------------+* Other Ports

+------+---------+-----------+----------+

| Port | Mode | Direction | Bitwidth |

+------+---------+-----------+----------+

| size | ap_none | in | 32 |

+------+---------+-----------+----------+* TOP LEVEL CONTROL

+-----------+------------+-----------------------------------+

| Interface | Type | Ports |

+-----------+------------+-----------------------------------+

| ap_clk | clock | ap_clk |

| ap_rst_n | reset | ap_rst_n |

| ap_ctrl | ap_ctrl_hs | ap_done ap_idle ap_ready ap_start |

+-----------+------------+-----------------------------------+================================================================

== SW I/O Information

================================================================

* Top Function Arguments

+----------+-----------+---------------+

| Argument | Direction | Datatype |

+----------+-----------+---------------+

| in1 | inout | unsigned int* |

| in2 | in | unsigned int* |

| out | inout | unsigned int* |

| size | in | int |

+----------+-----------+---------------+* SW-to-HW Mapping

+----------+---------------+-----------+----------+-----------------------------------+

| Argument | HW Interface | HW Type | HW Usage | HW Info |

+----------+---------------+-----------+----------+-----------------------------------+

| in1 | m_axi_gmem0 | interface | | channel=0 |

| in1 | s_axi_control | register | offset | name=in1_1 offset=0x10 range=32 |

| in1 | s_axi_control | register | offset | name=in1_2 offset=0x14 range=32 |

| in2 | m_axi_gmem1 | interface | | channel=0 |

| in2 | s_axi_control | register | offset | name=in2_1 offset=0x1c range=32 |

| in2 | s_axi_control | register | offset | name=in2_2 offset=0x20 range=32 |

| out | m_axi_gmem0 | interface | | channel=0 |

| out | s_axi_control | register | offset | name=out_r_1 offset=0x28 range=32 |

| out | s_axi_control | register | offset | name=out_r_2 offset=0x2c range=32 |

| size | size | port | | |

+----------+---------------+-----------+----------+-----------------------------------+================================================================

== M_AXI Burst Information

================================================================Note: All burst requests might be further partitioned into multiple requests during RTL generation based on max_read_burst_length or max_write_burst_length settings.* Inferred Burst Summary

+--------------+-----------+----------+-------+--------+---------------+

| HW Interface | Direction | Length | Width | Loop | Loop Location |

+--------------+-----------+----------+-------+--------+---------------+

| m_axi_gmem0 | read | variable | 32 | mem_rd | vadd.cpp:10:5 |

| m_axi_gmem0 | write | variable | 32 | mem_wr | vadd.cpp:33:5 |

| m_axi_gmem1 | read | variable | 32 | mem_rd | vadd.cpp:10:5 |

+--------------+-----------+----------+-------+--------+---------------+* All M_AXI Variable Accesses

+-------------------+----------+-----------------+-----------+--------------+----------+--------+---------------+------------+-------------------------------------------------------------------------------------------------------+

| HW Interface | Variable | Access Location | Direction | Burst Status | Length | Loop | Loop Location | Resolution | Problem |

+-------------------+----------+-----------------+-----------+--------------+----------+--------+---------------+------------+-------------------------------------------------------------------------------------------------------+

| m_axi_gmem0 | out | vadd.cpp:35:9 | write | Widen Fail | | mem_wr | vadd.cpp:33:5 | 214-353 | Could not widen since type i32 size is greater than or equal to the max_widen_bitwidth threshold of 0 |

| m_axi_gmem0 | out | vadd.cpp:35:9 | write | Inferred | variable | mem_wr | vadd.cpp:33:5 | | |

| m_axi_gmem0,gmem1 | in | vadd.cpp:12:11 | read | Widen Fail | | mem_rd | vadd.cpp:10:5 | 214-353 | Could not widen since type i32 size is greater than or equal to the max_widen_bitwidth threshold of 0 |

| m_axi_gmem0,gmem1 | in | vadd.cpp:12:11 | read | Inferred | variable | mem_rd | vadd.cpp:10:5 | | |

+-------------------+----------+-----------------+-----------+--------------+----------+--------+---------------+------------+-------------------------------------------------------------------------------------------------------+* Resolution URL: docs.xilinx.com/access/sources/dita/topic?Doc_Version=2024.1%20English&url=ug1448-hls-guidance&resourceid=XXX-YYY.html (replace XXX-YYY with column value)================================================================

== Bind Op Report

================================================================

+----------------------------------+-----+--------+-------------+--------+----------+---------+

| Name | DSP | Pragma | Variable | Op | Impl | Latency |

+----------------------------------+-----+--------+-------------+--------+----------+---------+

| + vadd | 0 | | | | | |

| + read_input | 0 | | | | | |

| icmp_ln10_fu_94_p2 | | | icmp_ln10 | setgt | auto | 0 |

| empty_fu_104_p3 | | | empty | select | auto_sel | 0 |

| + read_input_Pipeline_mem_rd | 0 | | | | | |

| icmp_ln10_fu_96_p2 | | | icmp_ln10 | setlt | auto | 0 |

| add_ln10_fu_102_p2 | | | add_ln10 | add | fabric | 0 |

| + read_input_1 | 0 | | | | | |

| icmp_ln10_fu_112_p2 | | | icmp_ln10 | setgt | auto | 0 |

| empty_fu_122_p3 | | | empty | select | auto_sel | 0 |

| icmp_ln10_1_fu_146_p2 | | | icmp_ln10_1 | setlt | auto | 0 |

| add_ln10_fu_152_p2 | | | add_ln10 | add | fabric | 0 |

| + compute_add | 0 | | | | | |

| + compute_add_Pipeline_compute | 0 | | | | | |

| icmp_ln23_fu_81_p2 | | | icmp_ln23 | setlt | auto | 0 |

| add_ln23_fu_87_p2 | | | add_ln23 | add | fabric | 0 |

| add_ln25_fu_98_p2 | | | add_ln25 | add | fabric | 0 |

| + write_result | 0 | | | | | |

| icmp_ln33_fu_85_p2 | | | icmp_ln33 | setgt | auto | 0 |

| empty_fu_105_p3 | | | empty | select | auto_sel | 0 |

| + write_result_Pipeline_mem_wr | 0 | | | | | |

| icmp_ln33_fu_100_p2 | | | icmp_ln33 | setlt | auto | 0 |

| add_ln33_fu_106_p2 | | | add_ln33 | add | fabric | 0 |

+----------------------------------+-----+--------+-------------+--------+----------+---------+================================================================

== Storage Report

================================================================

+-------------------+--------------+-------------+------+------+--------+-----------+------+---------+------------------+

| Name | Usage | Type | BRAM | URAM | Pragma | Variable | Impl | Latency | Bitwidth, Depth, |

| | | | | | | | | | Banks |

+-------------------+--------------+-------------+------+------+--------+-----------+------+---------+------------------+

| + vadd | | | 6 | 0 | | | | | |

| control_s_axi_U | interface | s_axilite | | | | | | | |

| gmem0_m_axi_U | interface | m_axi | 4 | | | | | | |

| gmem1_m_axi_U | interface | m_axi | 2 | | | | | | |

| out_r_c_U | fifo channel | scalar prop | | | | out_r_c | srl | 0 | 64, 4, 1 |

| size_c1_U | fifo channel | scalar prop | | | | size_c1 | srl | 0 | 32, 2, 1 |

| inStream1_U | fifo channel | stream | | | | inStream1 | srl | 0 | 32, 2, 1 |

| inStream2_U | fifo channel | stream | | | | inStream2 | srl | 0 | 32, 2, 1 |

| size_c_U | fifo channel | scalar prop | | | | size_c | srl | 0 | 32, 2, 1 |

| outStream_U | fifo channel | stream | | | | outStream | srl | 0 | 32, 2, 1 |

+-------------------+--------------+-------------+------+------+--------+-----------+------+---------+------------------+================================================================

== Pragma Report

================================================================

* Valid Pragma Syntax

+----------------+-----------------------------------------------+-------------------------------------+

| Type | Options | Location |

+----------------+-----------------------------------------------+-------------------------------------+

| interface | mode=ap_ctrl_chain port=return | vadd.cpp:7 in read_input, return |

| loop_tripcount | min = c_size max = c_size | vadd.cpp:11 in read_input |

| interface | mode=ap_ctrl_chain port=return | vadd.cpp:20 in compute_add, return |

| loop_tripcount | min = c_size max = c_size | vadd.cpp:24 in compute_add |

| interface | mode=ap_ctrl_chain port=return | vadd.cpp:30 in write_result, return |

| loop_tripcount | min = c_size max = c_size | vadd.cpp:34 in write_result |

| interface | mode=m_axi port=in1 bundle=gmem0 depth=c_size | vadd.cpp:41 in vadd, in1 |

| interface | mode=m_axi port=in2 bundle=gmem1 depth=c_size | vadd.cpp:42 in vadd, in2 |

| interface | mode=m_axi port=out bundle=gmem0 depth=c_size | vadd.cpp:43 in vadd, out |

| dataflow | | vadd.cpp:49 in vadd |

+----------------+-----------------------------------------------+-------------------------------------+3. 测试与波形

3.1 TestBench

#include <iostream>

#include <cstdlib>

#include <cstring>const int TEST_SIZE = 8;extern "C" void vadd(unsigned int* in1, unsigned int* in2, unsigned int* out, int size);int main() {unsigned int* in1 = new unsigned int[TEST_SIZE];unsigned int* in2 = new unsigned int[TEST_SIZE];unsigned int* out = new unsigned int[TEST_SIZE];unsigned int* expected = new unsigned int[TEST_SIZE];// 生成测试输入数据for (int i = 0; i < TEST_SIZE; i++) {in1[i] = i;in2[i] = TEST_SIZE - i;expected[i] = in1[i] + in2[i]; // 计算期望结果}// 调用 vadd 计算vadd(in1, in2, out, TEST_SIZE);vadd(in1, in2, out, TEST_SIZE);vadd(in1, in2, out, TEST_SIZE);vadd(in1, in2, out, TEST_SIZE);// 验证计算结果bool pass = true;for (int i = 0; i < TEST_SIZE; i++) {if (out[i] != expected[i]) {std::cerr << "Test failed at index " << i<< ": expected " << expected[i] << ", got " << out[i] << std::endl;pass = false;break; // 发现错误后立即停止}}if (pass) {std::cout << "Test passed successfully!" << std::endl;}// 释放内存delete[] in1;delete[] in2;delete[] out;delete[] expected;return pass ? 0 : 1;

}

3.2 理解控制协议

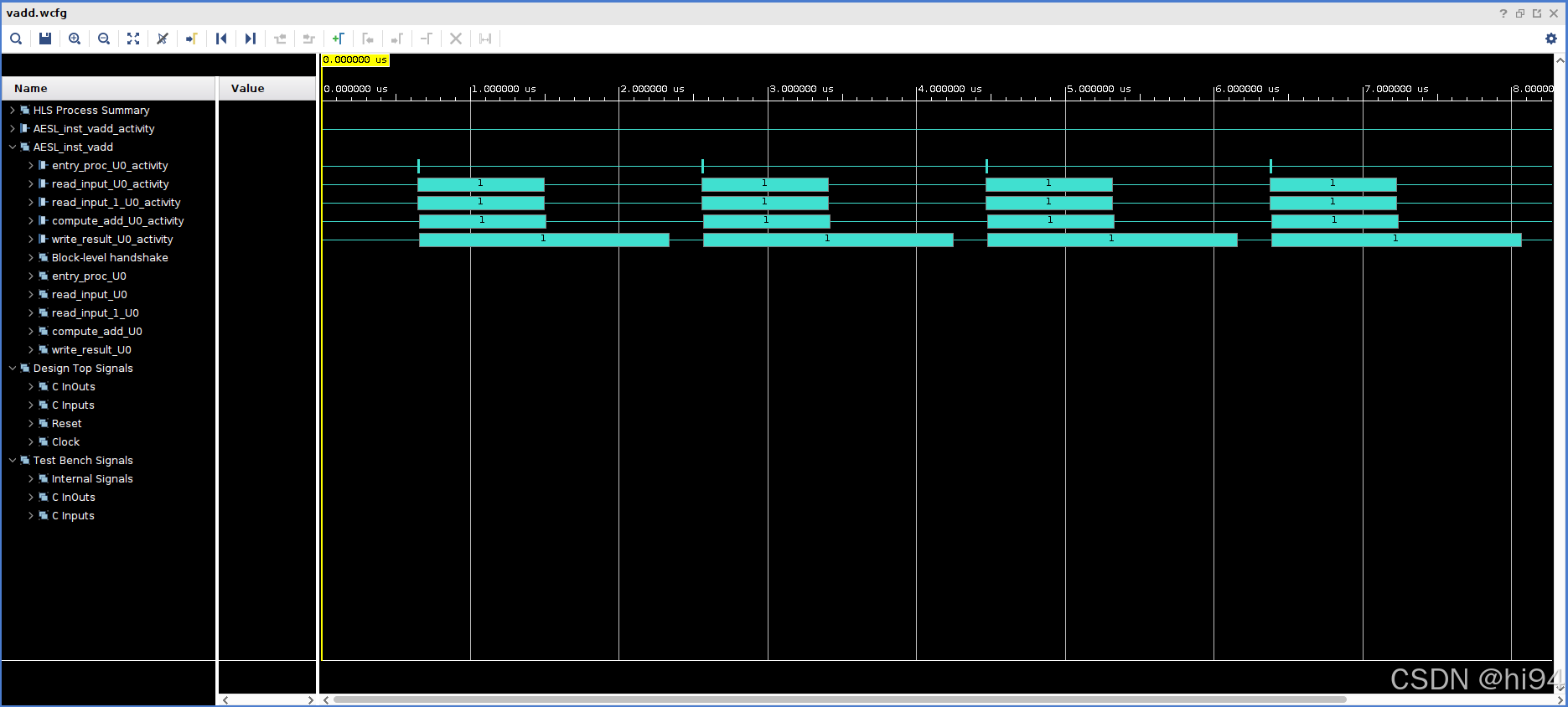

3.3 Wave Viewer

3.3.1 整体波形

通过 Wave Viewer,观察三个模块之间的块级协议是如何工作的。

3.3.2 ap_ctrl 信号

比如,ap_start ap_done ap_continue 等信号的变化。

4. 模块拆分

4.1 分析

如果将 read_input、compute_add、write_result 将失去顶层协议。

与 mm2s、s2mm 情况类似。

4.2 compute_add

#include <stdint.h>

#include <hls_stream.h>const int c_size = 4096;extern "C" {

void example(hls::stream<unsigned int>& inStream1,hls::stream<unsigned int>& inStream2,hls::stream<unsigned int>& outStream,int size) {

#pragma HLS INTERFACE mode=ap_ctrl_chain port=return

compute:for (int i = 0; i < size; i++) {

#pragma HLS LOOP_TRIPCOUNT min = c_size max = c_sizeoutStream << (inStream1.read() + inStream2.read());}

}}config file:

part=xck26-sfvc784-2LV-c[hls]

flow_target=vivado

package.output.format=ip_catalog

package.output.syn=false

syn.file=compute_vadd.cpp

syn.top=example4.2 IP 图

注意:需要修改 IP 中 stream port 的 Master/Slave 属性。

5. 总结

- 区分 axis 与 ap_fifo

- #pragma HLS interface axis port=s

相关文章:

Vitis HLS 学习笔记--块级控制(IDE 2024.1 + 执行模式 + 默认接口实现)

目录 1. 简介 2. 默认接口实现 2.1 执行模式 2.2 接口范式 2.2.1 存储器 2.2.2 串流 2.3.3 寄存器 2.3 Vitis Kernel Flow 2.3.1 默认的协议 2.3.2 vadd 代码 2.3.3 查看报告 2.4 Vivado IP Flow 2.4.1 默认的协议 2.4.2 vadd 代码 2.4.3 查看报告 3. 测试与波…...

红宝书第二十一讲:详解JavaScript的模块化(CommonJS与ES Modules)

红宝书第二十一讲:详解JavaScript的模块化(CommonJS与ES Modules) 资料取自《JavaScript高级程序设计(第5版)》。 查看总目录:红宝书学习大纲 一、模块化的意义:分而治之 模块化解决代码依赖混…...

github 页面超时解决方法

github 页面超时解决方法 每次好不容易找到github项目代码之后,满心欢喜打开却是个无法访问,心顿时又凉了半截,现在有方法可以访问github啦 快来学习 打开浏览器插件(Edge浏览器) 搜索iLink插件 并安装 打开插件 填…...

前端 vue 项目上线前操作

目录 一、打包分析 二、CDN加速 三、项目部署 1. 打包部署 2. nginx 解决 history 刷新 404 问题 3. nginx配置代理解决生产环境跨域问题 一、打包分析 项目编写完成后,就需要部署到服务器上供他人访问。但是在此之前,我们可以先预览项目的体积大…...

矩阵对角化→实对称矩阵的对角化→实对称半正定矩阵的对角化

上篇:特征值→相似矩阵→矩阵对角化(特征值分解) 实对称矩阵正交对角化 实对称矩阵是指满足 A A T \bm A \bm A^{\mathsf {T}} AAT的矩阵,其中 A T \bm A^{\mathsf T} AT是 A \bm A A的转置矩阵。对称矩阵的特征值均为实数。实…...

vue: easy-cron扩展-更友好地显示表达式

我们一个批处理调度系统里要用到cron表达式,于是就在网上找到一个现成的组件easy-cron,采用后发现,它的配置界面还是很直观的,但显示时直接显示cron表达式,这对业务人员很不友好,所以,我们就扩展…...

移动零+复写零+快乐数+盛最多水的容器+有效三角形的个数

前言 2025.3.31,今天开始每日五道算法题,今天的算法题如标题! 双指针算法 在做今天的算法题之前,先来介绍一下今天会用到的算法! 双指针算法分为了两种常见的形式:对撞指针和快慢指针! 对撞…...

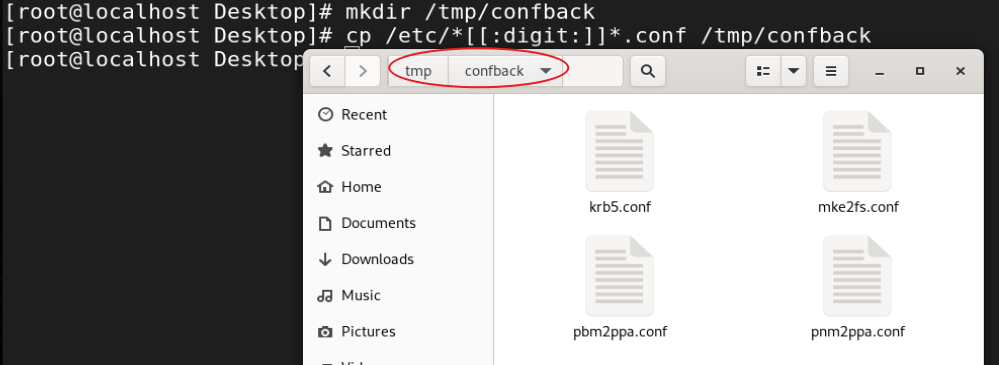

Linux中常用的文件管理命令

一、文件和目录的建立 文件 touch命令 单一文件的创建 当按下回车后我们就可以在桌面获得一个名字叫file的文件 [rootlocalhost Desktop]# touch file 同步文件访问时间和文件修改时间 由上两图可知touch file这个命令还可以把文件访问时间和文件修改时间变成touch file命…...

Root Cause Analysis in Microservice Using Neural Granger Causal Discovery

Root Cause Analysis in Microservice Using Neural Granger Causal Discovery 出处:AAAI 24 摘要 近年来,微服务因其可扩展性、可维护性和灵活性而在 IT 运营中得到广泛采用。然而,由于微服务中的复杂关系,当面临系统故障时,站点可靠性工程师 (SRE) 很难查明根本原…...

学习笔记—数据结构—二叉树(链式)

目录 二叉树(链式) 概念 结构 初始化 遍历 前序遍历 中序遍历 后序遍历 层序遍历 结点个数 叶子结点个数 第k层结点个数 深度/高度 查找值为x的结点 销毁 判断是否为完整二叉树 总结 头文件Tree.h Tree.c 测试文件test.c 补充文件Qu…...

微前端 - 以无界为例

一、微前端核心概念 微前端是一种将单体前端应用拆分为多个独立子应用的架构模式,每个子应用可独立开发、部署和运行,具备以下特点: 技术栈无关性:允许主应用和子应用使用不同框架(如 React Vue)。独立部…...

DIskgenius使用说明

文章目录 一、概述1. 软件简介2. 系统要求 二、核心功能1. 分区管理(1) 查看磁盘分区(2) 创建与删除分区(3) 调整分区大小(4) 格式化分区 2. 数据恢复(1) 恢复已删除文件(2) 恢复丢失分区(3) 恢复误格式化分区 3. 磁盘复制(1) 克隆磁盘(2) 磁盘镜像 4. 文件操作(1) 文件复制与移…...

深入理解指针5

sizeof和strlen的对比 sizeof的功能 **sizeof是**** 操作符****,用来**** 计算****变量或类型或数组所占**** 内存空间大小****,**** 单位是字节,****他不管内存里是什么数据** int main() {printf("%zd\n", sizeof(char));p…...

一文详解QT环境搭建:Windows使用CLion配置QT开发环境

在当今的软件开发领域,跨平台应用的需求日益增长,Qt作为一款流行的C图形用户界面库,因其强大的功能和易用性而备受开发者青睐。与此同时,CLion作为一款专为C/C打造的强大IDE,提供了丰富的特性和高效的编码体验。本文将…...

NE 综合实验3:基于 IP 配置、链路聚合、VLAN 管理、路由协议及安全认证的企业网络互联与外网访问技术实现(H3C)

综合实验3 实验拓扑 设备名称接口IP地址R1Ser_1/0与Ser_2/0做捆绑MP202.100.1.1/24G0/0202.100.2.1/24R2Ser_1/0与Ser_2/0做捆绑MP202.100.1.2/24G0/0172.16.2.1/24G0/1172.16.1.1/24G0/2172.16.5.1/24R3G5/0202.100.2.2/24G0/0172.16.2.2/24G0/1172.16.3.1/24G0/2172.16.7.1/…...

:机器学习中的“真相”基准)

Ground Truth(真实标注数据):机器学习中的“真相”基准

Ground Truth:机器学习中的“真相”基准 文章目录 Ground Truth:机器学习中的“真相”基准引言什么是Ground Truth?Ground Truth的重要性1. 模型训练的基础2. 模型评估的标准3. 模型改进的指导 获取Ground Truth的方法1. 人工标注2. 众包标注…...

双重token自动续期解决方案

Token自动续期实现方案详解 Token自动续期是提升用户体验和保障系统安全的关键机制,其核心在于无感刷新和安全可控。以下从原理、实现方案、安全措施和最佳实践四个维度展开说明: 一、核心原理:双Token机制 Token自动续期通常采用 Access …...

我与数学建模之启程

下面的时间线就是从我的大二上开始 9月开学就迎来了本科阶段最重要的数学建模竞赛——国赛,这个比赛一般是在9月的第二周开始。 2021年国赛是我第一次参加国赛,在报名前我还在纠结队友,后来经学长推荐找了另外两个学长。其实第一次国赛没啥…...

多段圆弧拟合离散点实现切线连续

使用多段圆弧来拟合一个由离散点组成的曲线,并且保证切线连续。也就是说,生成的每一段圆弧之间在连接点处必须有一阶导数连续,也就是切线方向相同。 点集分割 确保每个段的终点是下一段的起点,相邻段共享连接点,避免连接点位于数…...

烧结银:解锁金刚石超强散热潜力

烧结银:解锁金刚石超强散热潜力 在材料科学与热管理领域,金刚石凭借超高的热导率,被誉为 “散热之王”,然而,受限于其特殊的性质,金刚石在实际应用中难以充分发挥散热优势。而烧结银AS9335的出现&#x…...

【蓝桥杯】第十四届C++B组省赛

⭐️个人主页:小羊 ⭐️所属专栏:蓝桥杯 很荣幸您能阅读我的文章,诚请评论指点,欢迎欢迎 ~ 目录 试题A:日期统计试题B:01串的熵试题C:冶炼金属试题D:飞机降落试题E:接…...

企业级海外网络专线行业应用案例及服务商推荐

在全球化业务快速发展的今天,传统网络技术已难以满足企业需求。越来越多企业开始选择新型海外专线解决方案,其中基于SD-WAN技术的企业级海外网络专线备受关注。这类服务不仅能保障跨国数据传输,还能根据业务需求灵活调整网络配置。接下来我们…...

阿里云服务器安装docker以及mysql数据库

(1) 官方下载路径 官方下载地址: Index of linux/static/stable/x86_64/阿里云镜像地址: https://mirrors.aliyun.com/docker-ce/下载最新的 Docker 二进制文件:wget https://download.docker.com/linux/static/stable/x86_64/docker-20.10.23.tgz登录到阿里云服务…...

)

力扣经典算法篇-5-多数元素(哈希统计,排序,摩尔投票法)

题干: 给定一个大小为 n 的数组 nums ,返回其中的多数元素。多数元素是指在数组中出现次数 大于 ⌊ n/2 ⌋ 的元素。 你可以假设数组是非空的,并且给定的数组总是存在多数元素。 示例 1: 输入:nums [3,2,3] 输出&…...

axios介绍以及配置

Axios 是一个基于 Promise 的 HTTP 客户端,用于浏览器和 Node.js 环境中进行 HTTP 请求。 一、特点与基本用法 1.特点 浏览器兼容性好:能在多种现代浏览器中使用,包括 Chrome、Firefox、Safari 等。支持 Promise API:基于 Prom…...

深入解析:HarmonyOS Design设计语言的核心理念

深入解析:HarmonyOS Design设计语言的核心理念 在当今数字化迅速发展的时代,用户对操作系统的体验要求越来越高。华为的HarmonyOS(鸿蒙操作系统)应运而生,旨在为用户提供全场景、全设备的智慧体验。其背后的设计语言—…...

大数据技术之Scala:特性、应用与生态系统

摘要 Scala 作为一门融合面向对象编程与函数式编程范式的编程语言,在大数据领域展现出独特优势。本文深入探讨 Scala 的核心特性,如函数式编程特性、类型系统以及与 Java 的兼容性等。同时,阐述其在大数据处理框架(如 Apache Spa…...

:竞价指标剖析与流量对接要点)

程序化广告行业(47/89):竞价指标剖析与流量对接要点

程序化广告行业(47/89):竞价指标剖析与流量对接要点 大家好!一直以来,我都希望能和大家一同深入探索程序化广告行业的奥秘,这也是我持续撰写这一系列博客的动力。今天,咱们接着来剖析程序化广告…...

dfs记忆化搜索刷题 + 总结

文章目录 记忆化搜索 vs 动态规划斐波那契数题解代码 不同路径题解代码 最长递增子序列题解代码 猜数字大小II题解代码 矩阵中的最长递增路径题解代码 总结 记忆化搜索 vs 动态规划 1. 记忆化搜索:有完全相同的问题/数据保存起来,带有备忘录的递归 2.记忆…...

vue2 全局封装axios统一管理api

在vue项目中,经常会使用到axios来与后台进行数据交互,axios丰富的api满足我们基本的需求。但是对于项目而言,每次都需要对异常进行捕获或者处理的话,代码会很繁重冗余。我们需要将其公共部分封装起来,比如异常处理&…...