7系列 之 OSERDESE2

背景

《ug471_7Series_SelectIO.pdf》介绍了Xilinx 7 系列 SelectIO 的输入/输出特性及逻辑资源的相关内容。

第 1 章《SelectIO Resources》介绍了输出驱动器和输入接收器的电气特性,并通过大量实例解析了各类标准接口的实现。

第 2 章《SelectIO Logic Resources》介绍了输入输出数据寄存器及其双倍数据速率(DDR)操作,以及可编程输入延(IDELAY)和可编程输出延迟(ODELAY)。

第 3 章《Advanced SelectIO Logic Resources》介绍了ISERDESE2 、OSERDESE2与IO_FIFO。

了解了这个手册充分介绍的SelectIO架构和资源,以及所支持的电平标准。就可以利用相应的架构和资源实现与不同电平标准、通信速率间的外设建立起联系。

系列目录与传送门

- 基于Xilinx的7系列,

- 笔者学习、研究FPGA的过程、笔记,记录为:《凡人修FPGA传》。

说明1:本系列基于文档文档《ug471_7Series_SelectIO.pdf》而写,翻译和感悟,会出现中英文混合的情况。

说明2:虽然文中会出现一些原文的部分截图,非常支持并推荐大家去看原汁原味的官方文档

说明3:在查阅相关资料过程中,发现一些关于相关知识点的介绍零零散散,本系列会对其进行整合,力求详尽。

说明4:本博客是笔者用来记录学习过程的一个形式,并非专业论文。因此,在本博客中不会太注重图文格式的规范。

说明5:如果文章有误,欢迎诸位道友指出、讨论,笔者也会积极改正,希望大家一起进步!

文章目录

- 背景

- 系列目录与传送门

- 前言

- 1、OSERDESE2 总述

- 1.1、数据并串转换器(Data Parallel-to-Serial Converter)

- 1.2、三态并串转换器(3-State Parallel-to-Serial Conversion)

- 2 ··· OSERDESE2 原语

- 3 ··· OSERDESE2 端口

- 4 ··· OSERDESE2 属性

- 5、OSERDESE2 时钟配置方法

- 6、OSERDESE2 位宽扩展

- 7、输出反馈(Output Feedback)

- 8、OSERDESE2 延迟

- 9、Timing Characteristics

- 10、OSERDESE2 原语例化

- 11、参考文献

前言

输入串并转换器 (Input serial-to-parallel converters,ISERDESE2) ,

输出并串转换器(output parallel-to-serial converters ,OSERDESE2),

支持极高的 I/O 数据速率,使内部逻辑的运行速度可以到 I/O 速率的1/8。

1、OSERDESE2 总述

-

OSERDESE2是7系列FPGA中专用的并串转换器,集成特定的时钟与逻辑资源,专为高速源同步接口设计。

-

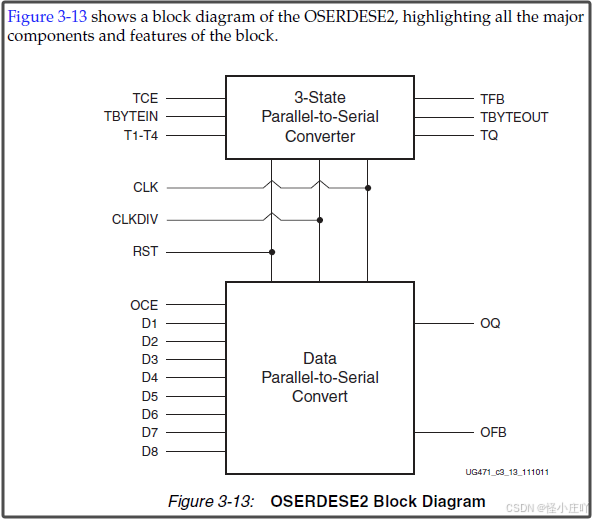

每个 OSERDESE2 模块都包含:

一个专用的数据串行器(a dedicated serializer for data)

和 一个三态控制串行器(3-state control),

可以被配置成SDR和DDR模式。

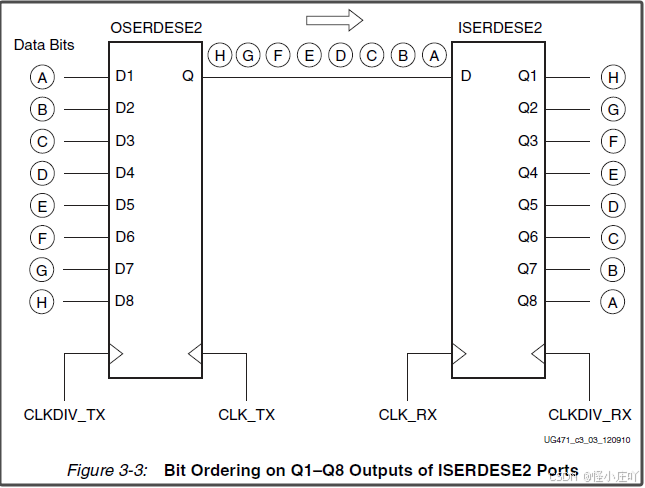

如图 3-3 所示,OSERDESE2 的输入比特顺序与 ISERDESE2 的输出顺序互为镜像。例如:

OSERDESE2的输入:字 FEDCBA 的最低有效位(LSB) A 输入至 D1 端口。

ISERDESE2 的输出:同一比特 A 从 Q8 端口输出。

如果,CLK频率为200 MHz:

SDR模式(8-bit):并串转换速率为 200 MHz × 8 = 1.6 Gbps。

DDR模式(8-bit):并串转换速率为 200 MHz × 8 × 2 = 3.2 Gbps

-

数据串行器:串行化比最高8:1(若使用OSERDESE2位宽扩展,则可达10:1和14:1)。

-

三态控制串行器:支持最高14:1串行化比。

-

OSERDESE2 模块有一个DDR3专用模式,针对高速存储器应用。

1.1、数据并串转换器(Data Parallel-to-Serial Converter)

OSERDESE2模块内的数据并串转换器接收来自FPGA逻辑的2至8位并行数据(若启用OSERDESE2位宽扩展,可支持14位),将数据串行化后通过OQ引脚输出至IOB。并行数据从最低位输入引脚(D1)开始串行传输(即D1引脚数据最先从OQ引脚输出)。该转换器支持两种工作模式:single-data rate (SDR) and double-data rate (DDR)。

OSERDESE2 使用 CLK 和 CLKDIV 这两个时钟信号来进行数据速率转换。CLK 是高速串行时钟,CLKDIV 是分频后的并行时钟。CLK 和 CLKDIV 必须相位对齐。

使用前,必须对OSERDESE2施加复位信号。 OSERDESE2 包含一个控制数据流的内部计数器。 如果未将复位信号的释放与 CLKDIV 同步,可能会产生意外输出。

此外OSERDESE2内部还有一个计数器,用来计数当前dout输出的是输入信号的第几位数据了,所以在使用OSERDESE2前,必须对OSERDESE2进行复位,复位信号可以是同步复位,也可以是异步复位,但是复位信号无效边沿必须与CLKDIV同步(即使用异步复位时,要考虑同步释放复位)。(《xilinx原语详解及仿真之OSERDESE2》)

1.2、三态并串转换器(3-State Parallel-to-Serial Conversion)

OSERDESE2模块除了具有数据并串转换功能外,还包括三态控制并串转换器,用于IOB的三态信号控制。最大支持4位并行三态信号串行化,不可级联。

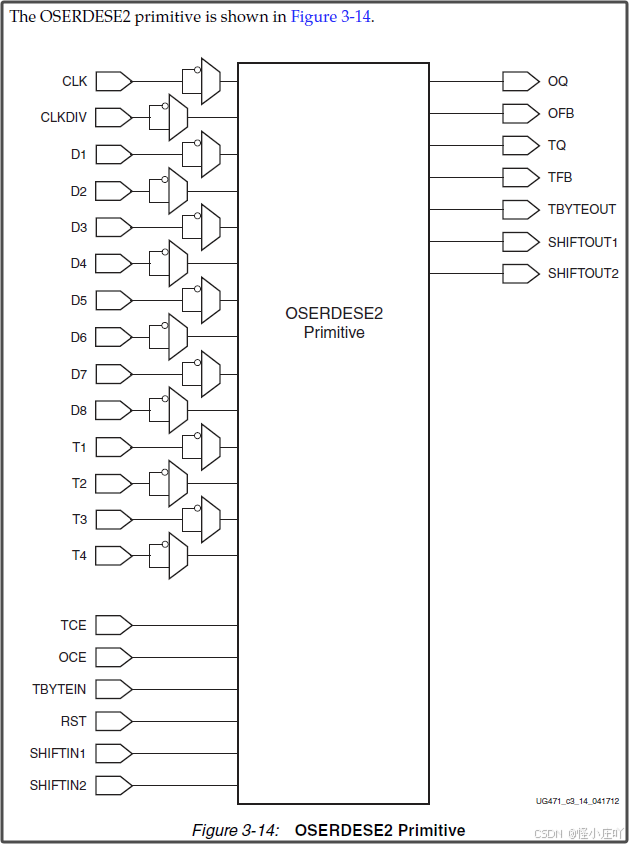

2 ··· OSERDESE2 原语

3 ··· OSERDESE2 端口

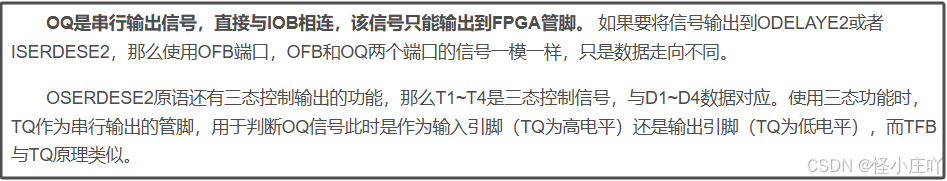

- 1、Data Path Output - OQ

OQ 是 OSERDESE2 模块的数据输出端口。输入端口 D1 的数据将首先出现在 OQ。此端口将数据并串转换器的输出连接至 IOB 的数据输入端口。OQ 不能直接驱动 ODELAYE2,必须通过 OFB 引脚实现延迟控制。

- 2、Output Feedback from OSERDESE2 - OFB

OFB 是 OSERDESE2 的串行(高速)数据反馈端口,用途包括:连接至 ODELAYE2 原语实现输出延迟,或者将串行数据回传至 ISERDESE2。

- 3、3-state Control Output - TQ

TQ 是 OSERDESE2 的三态控制输出端口,用于将三态并串转换器的输出连接至 IOB 的三态控制输入。

- 4、3-state Control Output - TFB

TFB 是 OSERDESE2 的三态状态反馈端口,可向 FPGA 逻辑端反馈当前三态状态(当 IOB 处于高阻态时有效)。

- 5、High-Speed Clock Input - CLK

CLK 是驱动并串转换器串行端的高速时钟信号。

- 6、Divided Clock Input - CLKDIV

CLKDIV 是驱动并串转换器并行端的分频时钟信号,为 CLK 的分频信号且与CLK相位对齐。

- 7、Parallel Data Inputs - D1 to D8

所有并行数据通过 D1-D8 端口输入 OSERDESE2,支持配置为 2 至 8 位(即 8:1 串行化)。通过从模式 OSERDESE2 级联可扩展至 10 或 14 位。

- 8、Reset Input - RST

复位生效(高电平):使 CLK/CLKDIV 域所有数据触发器异步输出低电平。

复位释放(同步要求):需与 CLKDIV 同步释放,内部逻辑在 CLK 第一次上升沿重新同步。

在多比特输出结构中的每个 OSERDESE2 应由相同的复位信号驱动,该信号异步断言,并与 CLKDIV 同步去断言,以确保所有 OSERDESE2 元素同步退出复位。

复位释放时,需确保 CLK/CLKDIV 已稳定。

- 9、Output Data Clock Enable - OCE

OCE 为数据路径的高电平有效时钟使能信号。

- 10、3-state Signal Clock Enable - TCE

TCE 为三态控制路径的高电平有效时钟使能信号。

- 11、Parallel 3-state Inputs - T1 to T4

所有并行三态信号通过 T1 至 T4 端口进入 OSERDESE2 模块。这些端口连接到 FPGA 内部结构。它们可配置为一位、两位或四位,或者直通。DATA_RATE_TQ 和 TRISTATE_WIDTH 属性控制这些端口的行为。

- 在博客《xilinx原语详解及仿真之OSERDESE2》中,看到如下一段话。

4 ··· OSERDESE2 属性

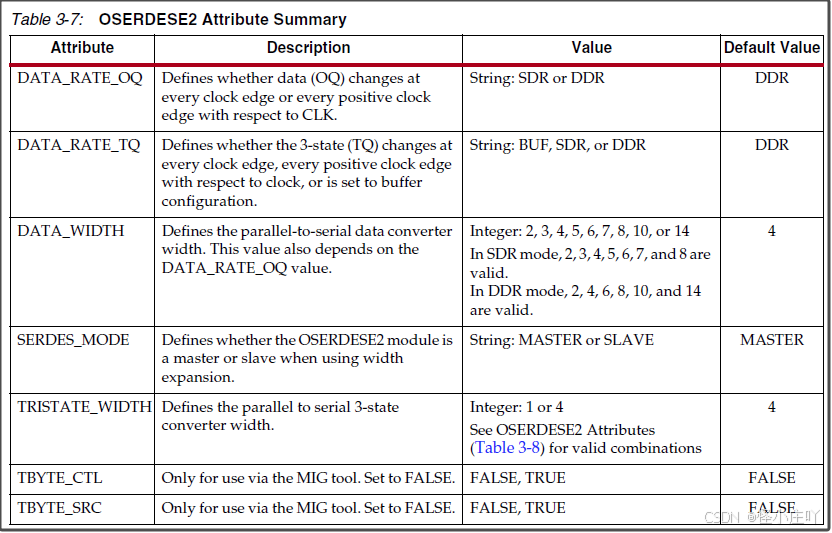

- 1、DATA_RATE_OQ

此属性定义数据以单数据速率(SDR)或双数据速率(DDR)处理。允许值为 SDR 或 DDR,默认值为 DDR。

- 2、DATA_RATE_TQ

此属性定义三态控制以单数据速率(SDR)、双数据速率(DDR)或直通模式(BUF)处理。允许值为 SDR、DDR 或 BUF,默认值为 DDR。

SDR/DDR 模式下:使用全部四个三态输入(T1-T4),其行为由 TRISTATE_WIDTH 属性配置。

BUF 模式下:

旁路 SDR/DDR 模式寄存器,因此应使用 T1 输入。T1 输入信号与所有其他信号异步,因为它仅通过 OSERDESE2 传递。

- 3、DATA_WIDTH

DATA_WIDTH 属性定义并行转串行转换器的并行数据输入位宽。

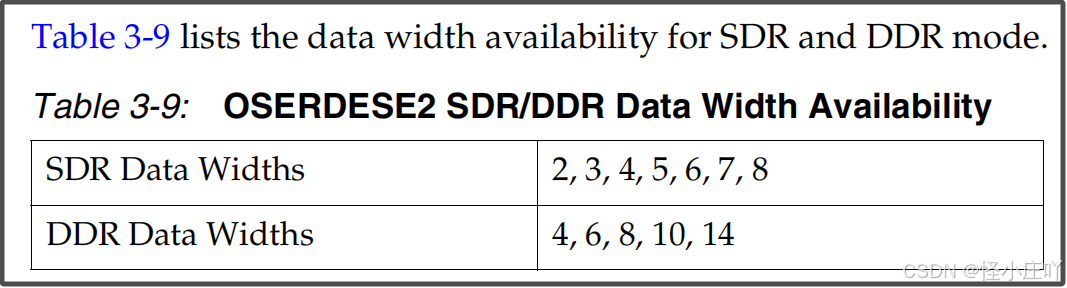

当 DATA_RATE_OQ 设置为 SDR 时,DATA_WIDTH 属性的可能取值为 2、3、4、5、6、7 和 8。当 DATA_RATE_OQ 设置为 DDR 时,DATA_WIDTH 属性的可能取值为 4、6、8、10 和 14。

当 DATA_WIDTH 设置为大于 8 的位宽时,必须将一对 OSERDESE2 配置为主从模式。

- 4、SERDES_MODE

此属性定义位宽扩展时 OSERDESE2 的主从模式,允许值为 MASTER(主)或 SLAVE(从),默认值为 MASTER。

- 5、TRISTATE_WIDTH

此属性定义三态并串转换器的并行输入位宽,其取值范围取决于 DATA_RATE_TQ:

DATA_RATE_TQ=SDR 或 BUF,TRISTATE_WIDTH=1;

DATA_RATE_TQ=DDR,TRISTATE_WIDTH=1或4;

5、OSERDESE2 时钟配置方法

理想情况下,CLK与CLKDIV需保持相位对齐(允许一定容差)。

OSERDESE2模块的有效时钟配置方案仅包含以下两种:

1、由 BUFIO 驱动 CLK , 由 BUFR 驱动 CLKDIV 。

2、CLK和CLKDIV由同一MMCM或PLL的CLKOUT[0:6]驱动。

若使用MMCM驱动OSERDESE2的CLK和CLKDIV,则供给OSERDESE2的缓冲类型不能混用。例如,若CLK由BUFG驱动,则CLKDIV也必须由BUFG驱动。

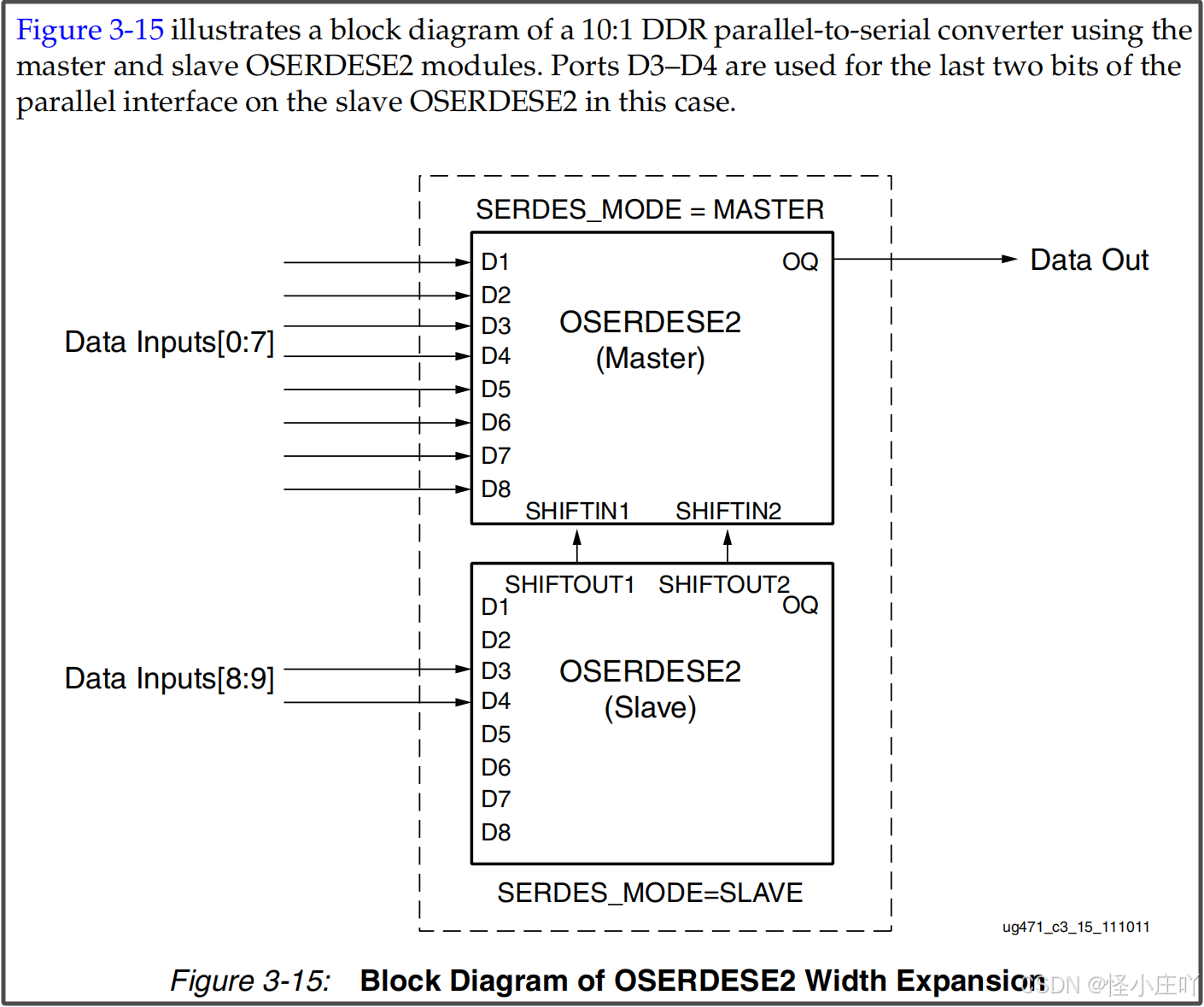

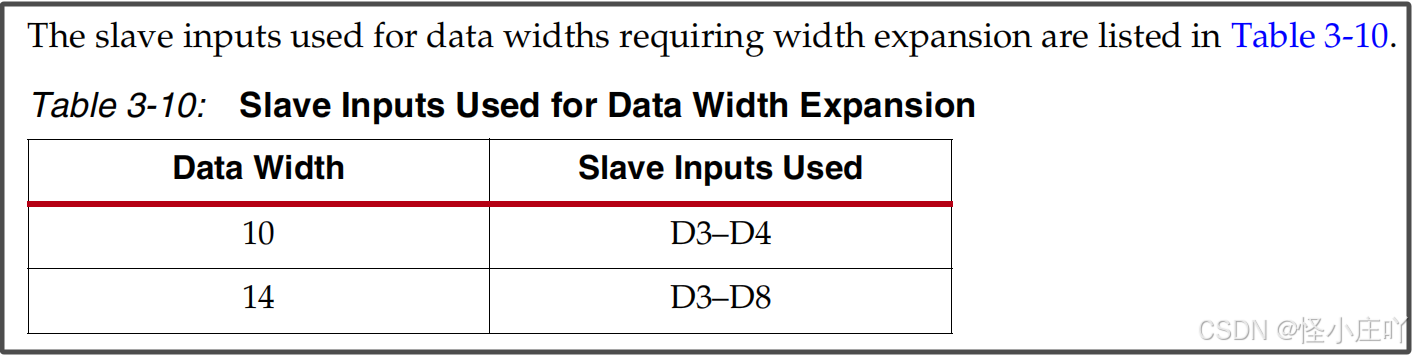

6、OSERDESE2 位宽扩展

每个I/O单元(I/O tile)有两个OSERDESE2模块:一个主模块和一个从模块。

将主OSERDESE2的SHIFTIN端口连接到从OSERDESE2的SHIFTOUT端口,可以把并串转换器扩展到10:1和14:1(仅限DDR模式)。

对于差分输出,主OSERDESE2必须位于差分输出对的正端(_P引脚)。

非差分输出时,与从OSERDESE2相关的输出缓冲区不可用,位宽扩展也无法使用。

使用互补单端标准(例如DIFF_HSTL和DIFF_SSTL)时,可能无法使用位宽扩展。这是因为互补单端标准会使用 I/O单元 内中的两个OLOGICE2/3模块(OLOGICE2/3 blocks)来传输两个互补信号,从而没有可用的OLOGICE2/3模块用于位宽扩展。

- 位宽扩展指南:

-

- 1、两个 OSERDESE2 模块必须是相邻的主从对。

-

- 2、将主 OSERDESE2 的 SERDES_MODE 属性设置为 MASTER,

从 OSERDESE2 的 SERDES_MODE 属性设置为 SLAVE。

- 2、将主 OSERDESE2 的 SERDES_MODE 属性设置为 MASTER,

-

- 3、用户必须将从模块的 SHIFTIN 引脚连接到主模块的 SHIFTOUT 引脚。

-

- 4、从模块使用 Q3 到 Q8 引脚作为输出。

-

- 5、主模块和从模块的DATA_WIDTH相等。

-

- 6、属性INTERFACE_TYPE设置为DEFAULT。

7、输出反馈(Output Feedback)

OSERDESE2引脚OFB具有以下两种功能:

• 作为反馈路径至ISERDESE2的OFB引脚。。

• 与ODELAYE2连接。OSERDESE2的输出可以通过OFB引脚路由至ODELAYE2模块,然后通过ODELAYE2进行延迟。

8、OSERDESE2 延迟

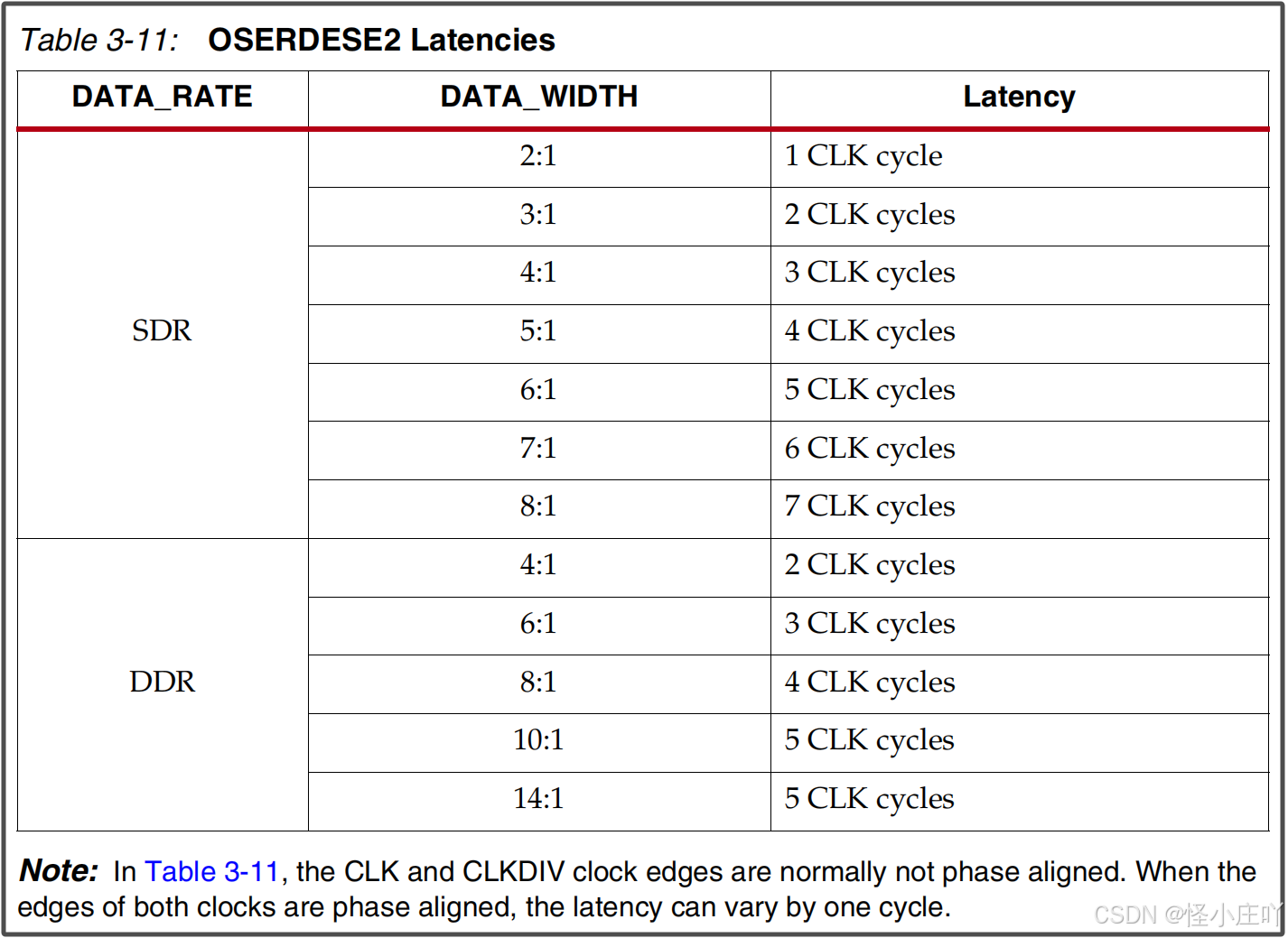

- DEFAULT Interface Type Latencies(默认接口类型延迟)

OSERDESE2模块的输入到输出延迟取决于DATA_RATE和DATA_WIDTH属性。

延迟被定义为以下两个事件之间的时间间隔:

事件(a):CLKDIV的上升沿将数据从输入端D1-D8时钟输入到OSERDESE2。

事件(b):串行流的第一位出现在OQ。

表3-11总结了各种OSERDESE2延迟值。

当CLK和CLKDIV的相位对齐时,延迟可能相差一个CLK周期,如果CLK和CLKDIV的相位没有对齐时,延迟的值取决于DATA_RATE和DATA_WIDTH的值。

9、Timing Characteristics

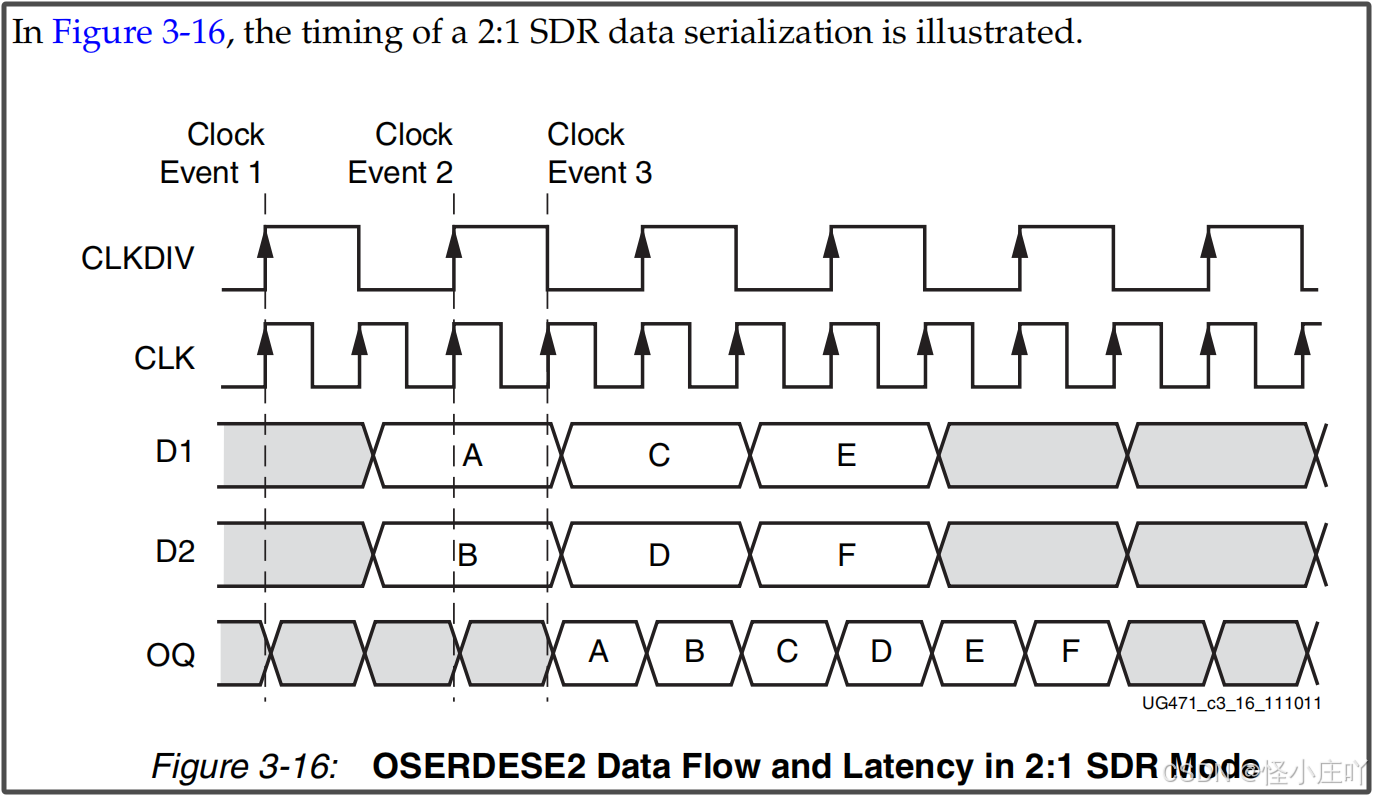

- 2:1 SDR Serialization

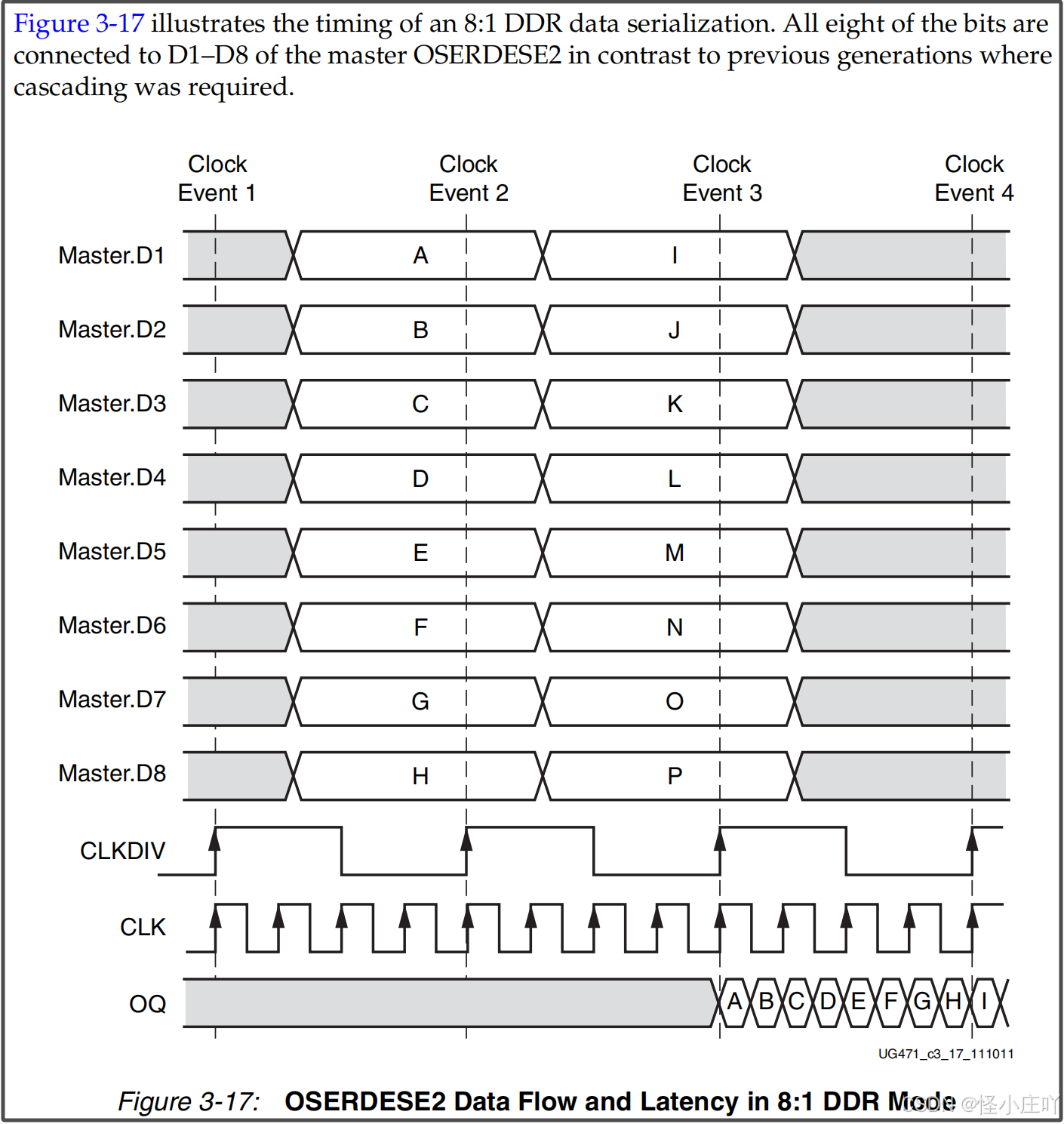

- 8:1 DDR Serialization

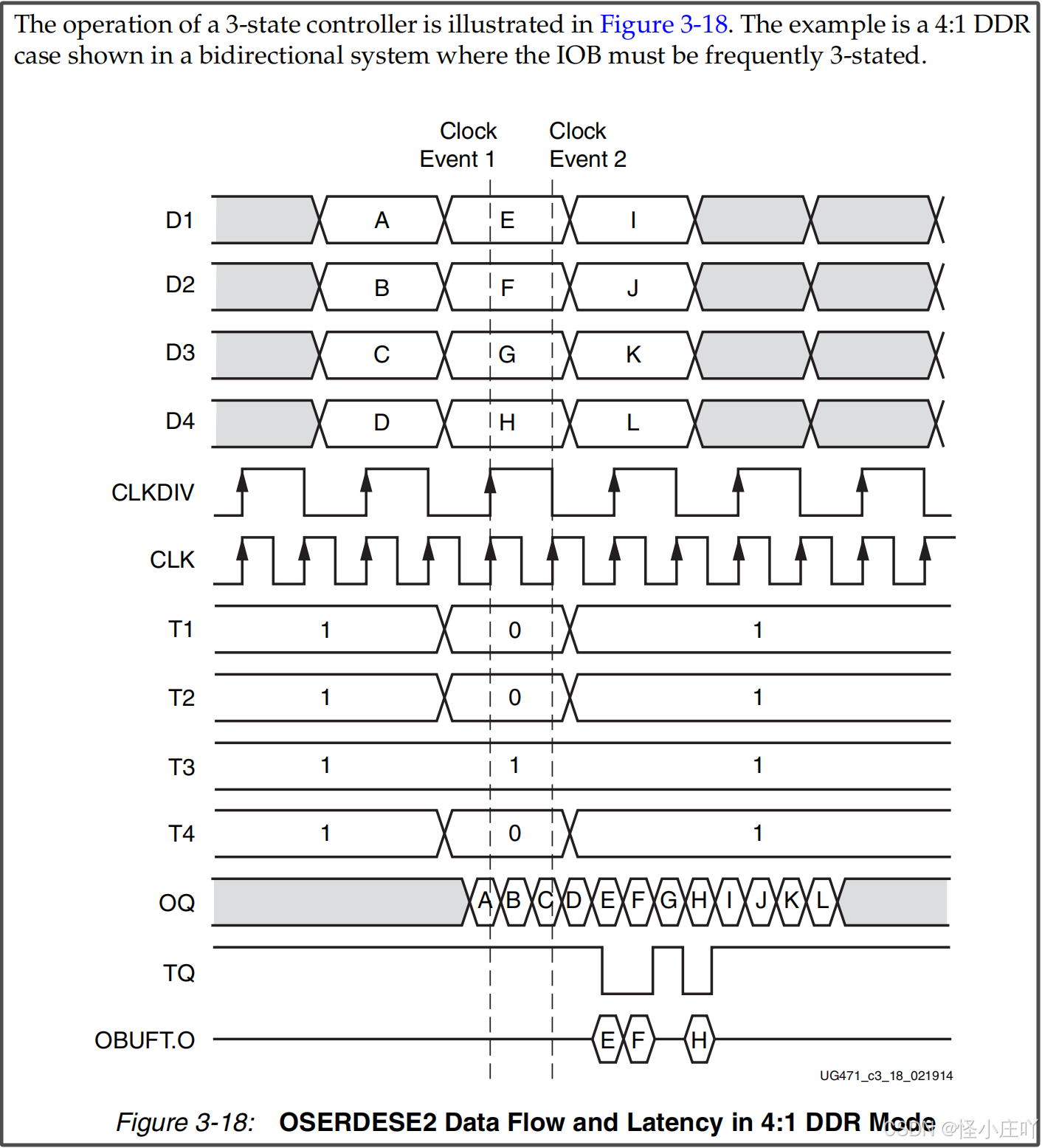

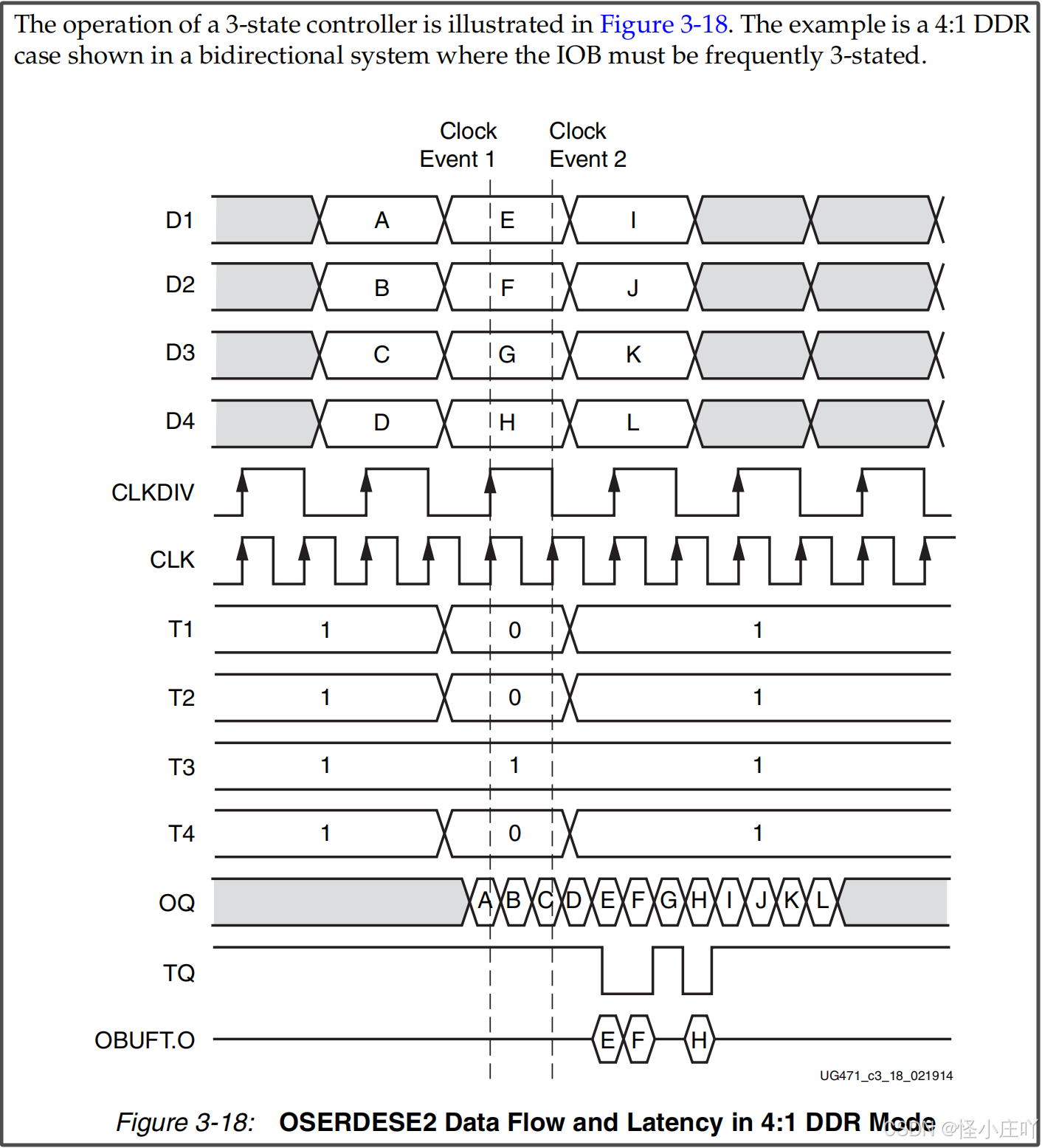

- 4:1 DDR 3-State Controller Serialization

- 4:1 DDR 3-State Controller Serialization

时钟事件1:

T1、T2和T4被置0以解除三态条件。

T1-T4和D1-D4在OSERDESE2中的串行化路径相同(包括延迟),因此在时钟事件1期间,EFGH位始终与T1-T4引脚上呈现的0010对齐。

时钟事件2:

在EFGH被采入OSERDESE2后的一个时钟周期,数据位E出现在OQ。

此延迟与表3-11中列出的4:1 DDR模式OSERDESE2延迟一个时钟周期一致。

在时钟事件1期间,T1上的三态位0在0010被采入OSERDESE2三态块后的一个时钟周期出现在TQ。此延迟与表3-11中列出的 4:1 DDR模式OSERDESE2延迟一个时钟周期一致。

10、OSERDESE2 原语例化

// OSERDESE2: Output SERial/DESerializer with bitslip

// 7 Series

// Xilinx HDL Libraries Guide, version 13.4

OSERDESE2 #(.DATA_RATE_OQ("DDR"), // DDR, SDR.DATA_RATE_TQ("DDR"), // DDR, BUF, SDR.DATA_WIDTH(4), // Parallel data width (2-8,10,14).INIT_OQ(1'b0), // Initial value of OQ output (1'b0,1'b1).INIT_TQ(1'b0), // Initial value of TQ output (1'b0,1'b1).SERDES_MODE("MASTER"), // MASTER, SLAVE.SRVAL_OQ(1'b0), // OQ output value when SR is used (1'b0,1'b1).SRVAL_TQ(1'b0), // TQ output value when SR is used (1'b0,1'b1).TBYTE_CTL("FALSE"), // Enable tristate byte operation (FALSE, TRUE).TBYTE_SRC("FALSE"), // Tristate byte source (FALSE, TRUE).TRISTATE_WIDTH(4) // 3-state converter width (1,4)

)OSERDESE2_inst (.OFB(OFB), // 1-bit output: Feedback path for data.OQ(OQ), // 1-bit output: Data path output// SHIFTOUT1 / SHIFTOUT2: 1-bit (each) output: Data output expansion (1-bit each).SHIFTOUT1(SHIFTOUT1),.SHIFTOUT2(SHIFTOUT2),.TBYTEOUT(TBYTEOUT), // 1-bit output: Byte group tristate.TFB(TFB), // 1-bit output: 3-state control.TQ(TQ), // 1-bit output: 3-state control.CLK(CLK), // 1-bit input: High speed clock.CLKDIV(CLKDIV), // 1-bit input: Divided clock// D1 - D8: 1-bit (each) input: Parallel data inputs (1-bit each).D1(D1),.D2(D2),.D3(D3),.D4(D4),.D5(D5),.D6(D6),.D7(D7),.D8(D8),.OCE(OCE), // 1-bit input: Output data clock enable.RST(RST), // 1-bit input: Reset// SHIFTIN1 / SHIFTIN2: 1-bit (each) input: Data input expansion (1-bit each).SHIFTIN1(SHIFTIN1),.SHIFTIN2(SHIFTIN2),// T1 - T4: 1-bit (each) input: Parallel 3-state inputs.T1(T1),.T2(T2),.T3(T3),.T4(T4),.TBYTEIN(TBYTEIN), // 1-bit input: Byte group tristate.TCE(TCE) // 1-bit input: 3-state clock enable

);

// End of OSERDESE2_inst instantiation11、参考文献

1、《ug471_7Series_SelectIO.pdf》

2、《xilinx原语详解及仿真之OSERDESE2》

相关文章:

7系列 之 OSERDESE2

背景 《ug471_7Series_SelectIO.pdf》介绍了Xilinx 7 系列 SelectIO 的输入/输出特性及逻辑资源的相关内容。 第 1 章《SelectIO Resources》介绍了输出驱动器和输入接收器的电气特性,并通过大量实例解析了各类标准接口的实现。 第 2 章《SelectIO Logic Resource…...

Redis--常见数据类型List列表

目录 一、概念 二、命令 2.1 LPUSH 2.2 LPUSHX 2.3 RPUSH 2.4 RPUSHX 2.5 LRANGE 2.6 LPOP 2.7 RPOP 2.8 LINDEX 2.9 LINSERT 2.10 LLEN 2.11 阻塞版本命令 三、内部编码 一、概念 列表类型是用来存储多个有序的字符串,列表中的每个字符串称为元素&…...

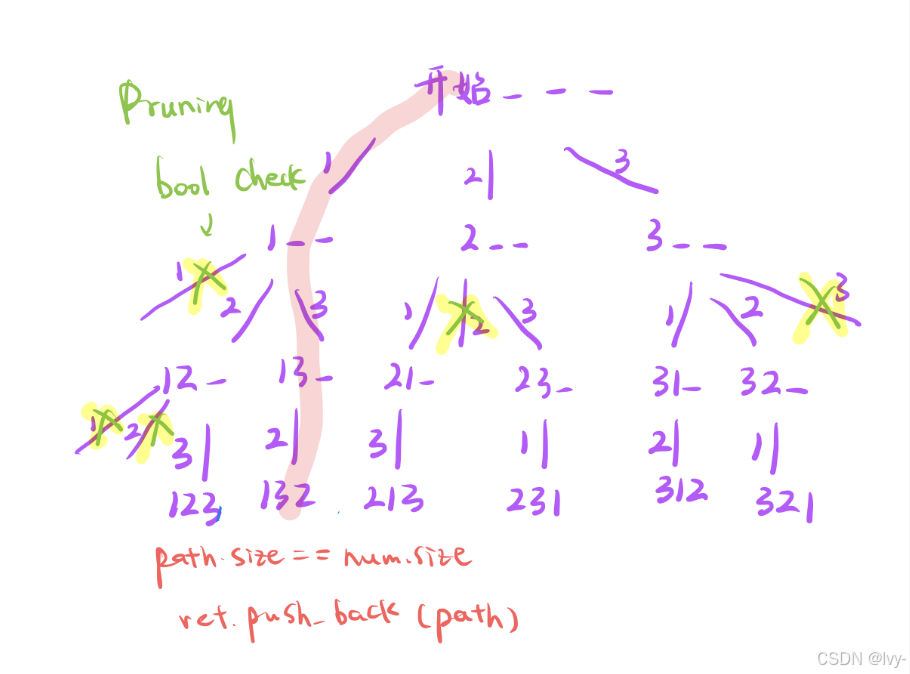

dfs 第一次加训 详解 下

目录 P1706 全排列问题 思路 B3618 寻找团伙 思路 B3621 枚举元组 思路 B3622 枚举子集(递归实现指数型枚举) 思路 B3623 枚举排列(递归实现排列型枚举) B3625 迷宫寻路 思路 P6183 [USACO10MAR] The Rock Game S 总结…...

vue3+flask+sqlite前后端项目实战

基础环境安装 pycharm 下载地址: https://www.jetbrains.com/zh-cn/pycharm/download/?sectionwindows vscode 下载地址 https://code.visualstudio.com/docs/?dvwin64user python 下载地址 https://www.python.org/downloads/windows/ Node.js(含npm…...

Java 线程的堆栈跟踪信息

Java 线程的堆栈跟踪信息,展示了线程的当前状态和执行位置。以下是详细解释: 线程基本信息 "Thread-0" #16 prio5 os_prio0 cpu0.00ms elapsed16.29s tid0x00000243105a4130 nid0x5384 waiting on condition [0x0000007687ffe000]线程名称…...

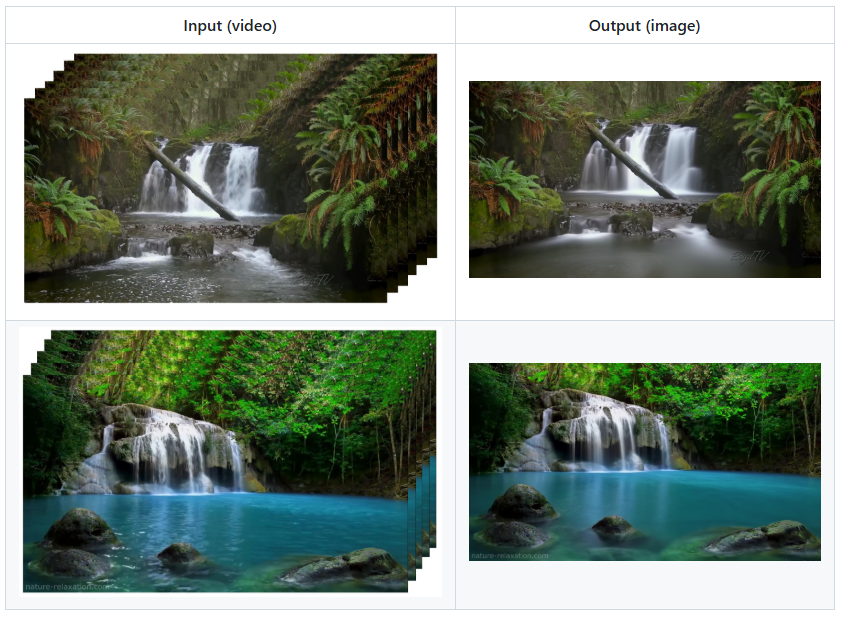

【计算机视觉】OpenCV实战项目:Long-Exposure:基于深度学习的长时间曝光合成技术

Long-Exposure:基于深度学习的长时间曝光合成技术 项目概述与技术背景项目核心功能技术原理 环境配置与安装硬件要求建议详细安装步骤可选组件安装 实战应用指南1. 基础使用:视频转长曝光2. 高级模式:自定义光轨合成3. 批量处理模式 技术实现…...

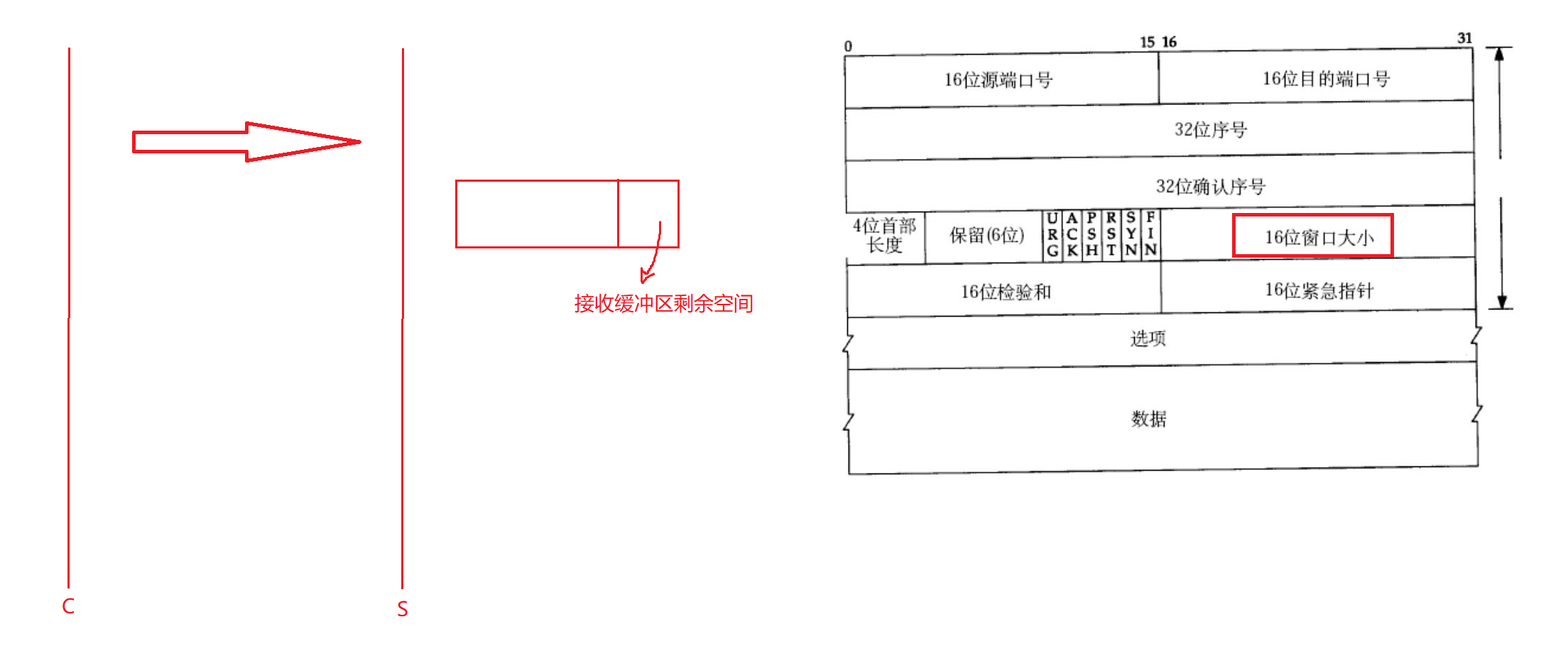

传输层协议UDP和TCP

传输层协议UDP和TCP 1、UDP2、TCP2.1、TCP协议段格式2.2、确认应答(ACK)机制2.3、超时重传机制2.4、连接管理机制2.5、理解CLOSE_WAIT状态2.6、理解TIME_WAIT状态2.7、流量控制2.8、滑动窗口2.9、拥塞控制2.10、延迟应答2.11、捎带应答2.12、面向字节流2.13、粘包问题2.14、TCP…...

浅谈大语言模型原理

1.反向传播算法 背景 反向传播算法是当前深度学习的核心技术。 神经网络 x是输入,o是输出,w是需要训练的参数(w有初始值)三层全连接的神经网络:输入层、隐藏层、输出层 激活函数 f ( x ) 1 1 x − 1 f(x)\frac…...

Clickhouse 迁移到 Doris 的最佳实践

一、引言 在将数据从 Clickhouse 迁移到 Apache Doris / SelectDB Cloud 的过程中,涉及表结构迁移、查询语句迁移以及数据迁移等多个关键环节。每个环节都有其复杂性和需要注意的细节,本文将详细介绍这些内容及对应的最佳实践方法。 二、表结构迁移 &…...

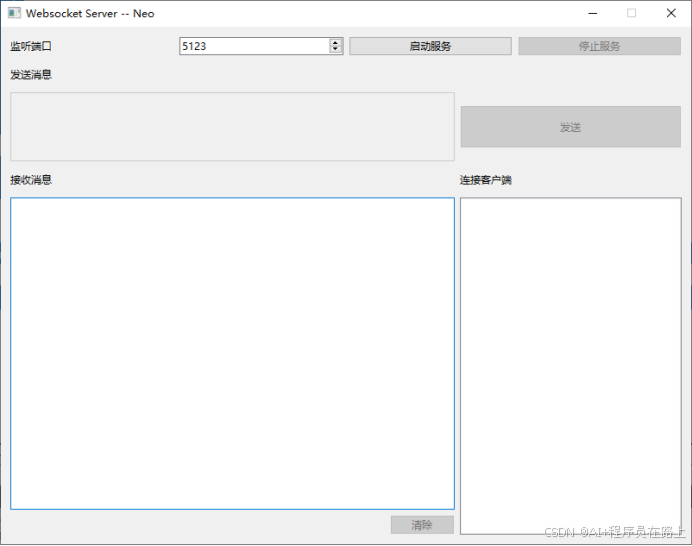

WebSocket的原理及QT示例

一.WebSocket 介绍 1.概述 WebSocket 是一种在单个 TCP 连接上进行全双工通讯的协议,它在 2011 年被 IETF 定为标准 RFC 6455,并由 RFC7936 补充规范。与传统的 HTTP 协议不同,WebSocket 允许服务器和客户端之间进行实时、双向的数据传输&a…...

数据库故障排查指南以及各类常用数据库基础用法

数据库故障排查指南大纲 数据库故障排查的基本概念 数据库故障的定义与分类常见数据库故障的表现形式故障排查的重要性与目标 数据库故障通常指数据库系统在运行过程中出现的异常情况,导致数据无法正常访问或操作。故障可以分为硬件故障、软件故障、网络故障、配…...

Spring Boot动态配置修改全攻略

精心整理了最新的面试资料和简历模板,有需要的可以自行获取 点击前往百度网盘获取 点击前往夸克网盘获取 无需重启应用,实时更新配置的终极指南 在微服务架构中,动态配置管理是提高系统灵活性的关键技术。本文将通过4种主流方案,…...

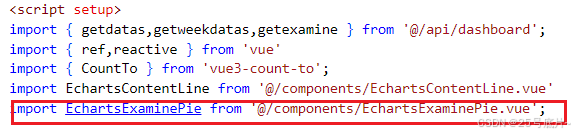

vue3:十二、图形看板- echart图表-柱状图、饼图

一、效果 如图展示增加了饼图和柱状图,并且优化了浏览器窗口大小更改,图表随着改变 二、 饼图 1、新建组件文件 新增组件EchartsExaminePie.vue,用于存储审核饼图的图表 2、写入组件信息 (1)视图层 写入一个div,写入变量chart和图表宽高 <template><div ref…...

2025年best好用的3dsmax插件和脚本

copitor 可以从一个3dsmax场景里将物体直接复制到另一个场景中 Move to surface 这个插件可以将一些物体放到一个平面上 instancer 实体器,举例:场景中有若干独立的光源,不是实体对象,我们可以使用instancer将他变成实体。 paste …...

趣谈Ai各种模型算法及应用

机器学习与深度学习模型选型终极指南:告别选择困难症! 大家好!今天,我们来聊一个让很多初学者甚至有经验的开发者都头疼的问题:面对琳琅满目的机器学习和深度学习模型,到底该如何选择?就像走进…...

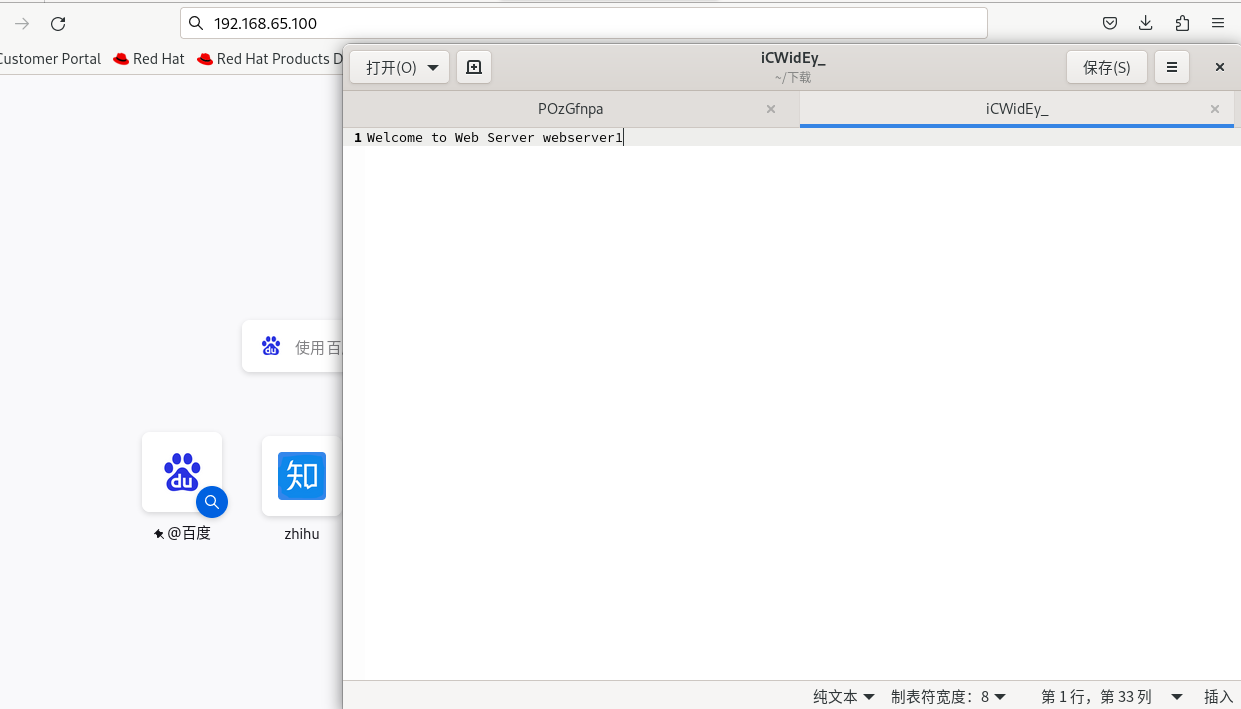

HAProxy + Keepalived + Nginx 高可用负载均衡系统

1. 项目背景 在现代Web应用中,高可用性和负载均衡是两个至关重要的需求。本项目旨在通过HAProxy实现流量分发,通过Keepalived实现高可用性,通过Nginx提供后端服务。该架构能够确保在单点故障的情况下,系统仍然能够正常运行&#…...

vue2升级vue3

vue2升级vue3 父子自定义事件插槽差异 父子自定义事件 父组件的传给子组件的自定义事件以短横形式命名,例如:my-click 子组件声明该自定义事件时为 myClick 事件可以正常触发 插槽差异 vue2: <el-table-column:label"$t(hcp_devrs…...

5.12 note

Leetcode 图 邻接矩阵的dfs遍历 class Solution { private: vector<vector<int>> paths; vector<int> path; void dfs(vector<vector<int>>& graph, int node) { // 到n - 1结点了保存 if (node graph.size() - 1)…...

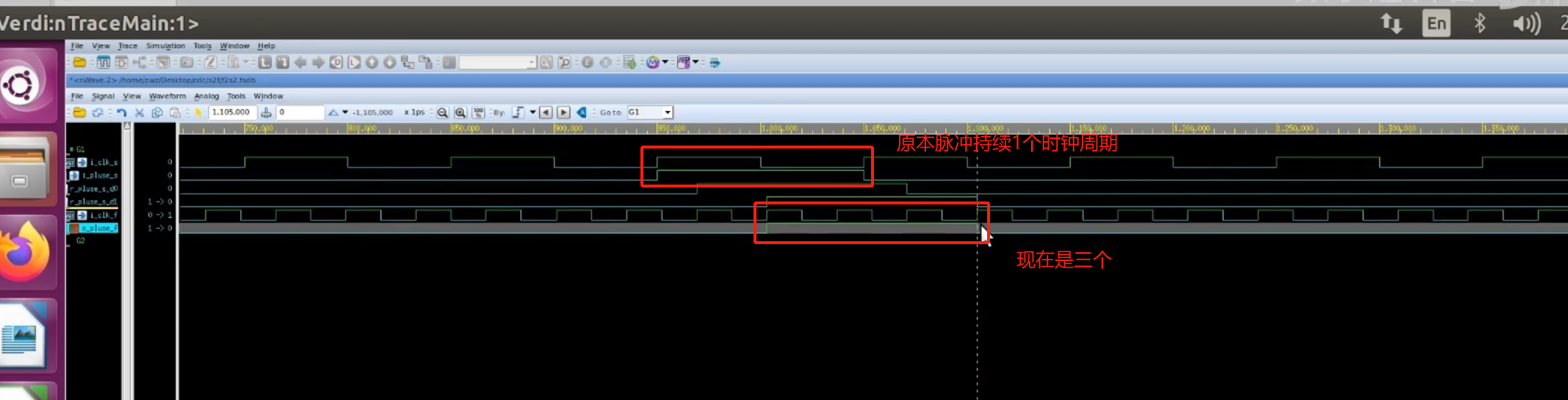

跨时钟域(CDC,clock domain crossing)信号处理

参考视频: 数字IC,FPGA秋招【单bit信号的CDC跨时钟域处理手撕代码合集】_哔哩哔哩_bilibili 一、亚稳态 原因是:建立时间和保持时间没有保持住。然后在下图的红框里面,产生亚稳态。因为电路反馈机制,最后大概率会恢复…...

鸿蒙HarmonyOS list优化一: list 结合 lazyforeach用法

list列表是开发中不可获取的,非常常用的组件,使用过程中会需要不断的优化,接下来我会用几篇文章进行list在纯原生的纯血鸿蒙的不断优化。我想进大厂,希望某位大厂的看到后能给次机会。 首先了解一下lazyforeach: Laz…...

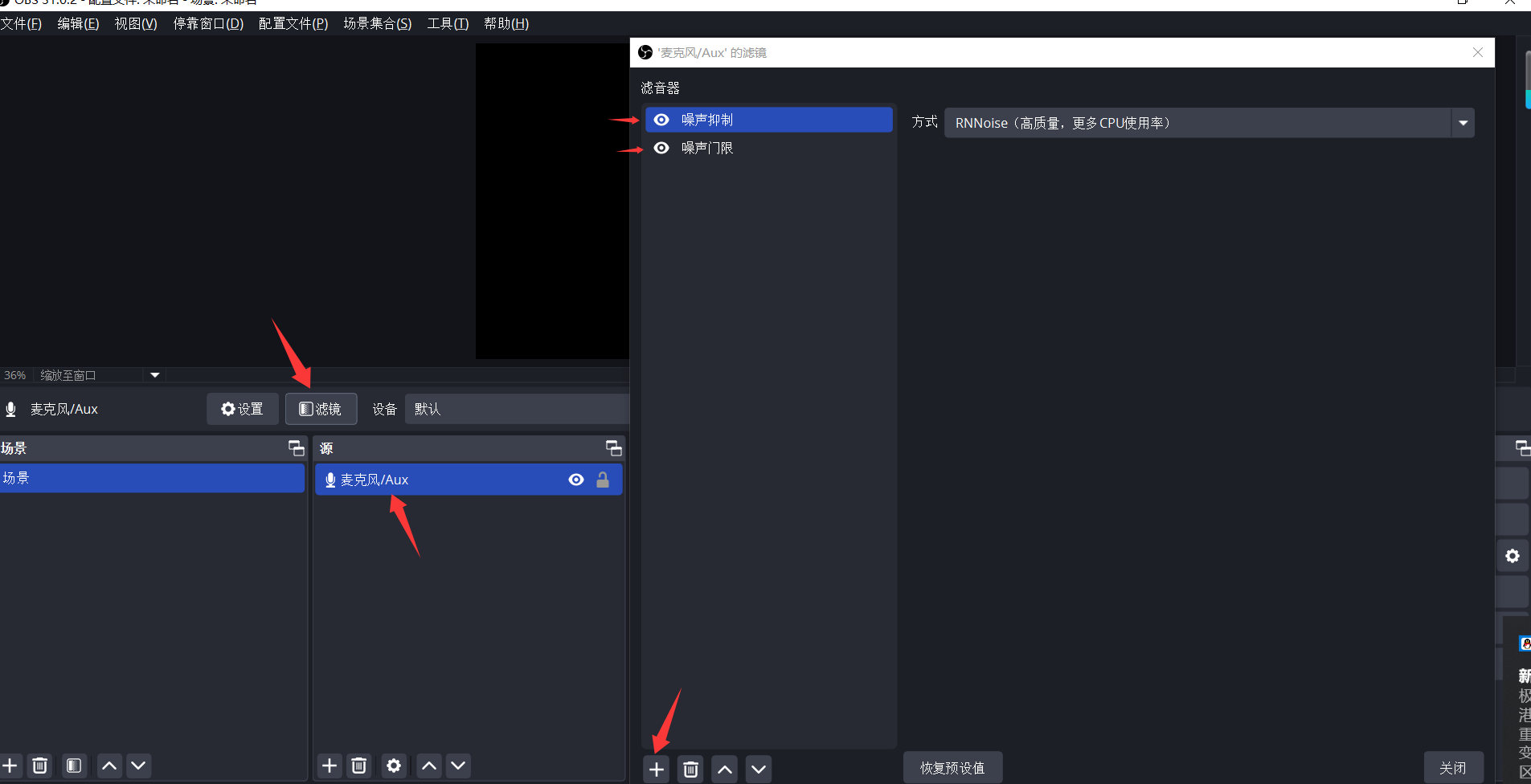

OBS studio 减少音频中的杂音(噪音)

1. 在混音器中关闭除 麦克风 之外的所有的音频输入设备 2.在滤镜中增加“噪声抑制”和“噪声门限”...

基于神经网络的 YOLOv8、MobileNet、HigherHRNet 姿态检测比较研究

摘要 随着人工智能技术的飞速发展,基于神经网络的姿态检测技术在计算机视觉领域取得了显著进展。本文旨在深入比较分析当前主流的姿态检测模型,即 YOLOv8、MobileNet 和 HigherHRNet,从模型架构、性能表现、应用场景等多维度展开研究。通过详…...

智能手表 MCU 任务调度图

智能手表 MCU 任务调度图 处理器平台:ARM Cortex-M33 系统架构:事件驱动 多任务 RTOS RTOS:FreeRTOS(或同类实时内核) 一、任务调度概览 任务名称优先级周期性功能描述App_MainTask中否主循环调度器,系统…...

青少年编程与数学 02-019 Rust 编程基础 03课题、变量与可变性

青少年编程与数学 02-019 Rust 编程基础 03课题、变量与可变性 一、使用多个文件(模块)1. 创建包结构2. 在 main.rs 中引入模块示例:main.rs 3. 定义模块文件示例:module1.rs示例:module2.rs 4. 定义子模块示例&#x…...

S7-1500——零基础入门2、PLC的硬件架构

PLC的硬件架构 一,西门子PLC概述二,CPU介绍三,数字量模块介绍四,模拟量模块介绍五,其他模块介绍一,西门子PLC概述 本节主要内容 西门子PLC硬件架构,主要内容包括PLC概述、组成、功能及S7-1500 demo的组成与安装演示。 介绍了PLC的定义、功能、应用场合,以及与继电器控…...

前端面试宝典---webpack面试题

webpack 的 tree shaking 的原理 Webpack 的 Tree Shaking 过程主要包含以下步骤: 模块依赖分析:Webpack 首先构建一个完整的模块依赖图,确定每个模块之间的依赖关系。导出值分析:通过分析模块之间的 import 和 exportÿ…...

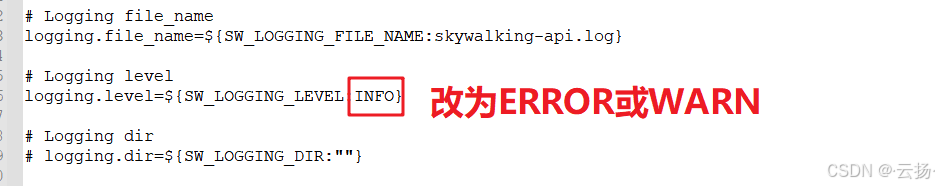

【PmHub后端篇】Skywalking:性能监控与分布式追踪的利器

在微服务架构日益普及的当下,对系统的性能监控和分布式追踪显得尤为重要。本文将详细介绍在 PmHub 项目中,如何使用 Skywalking 实现对系统的性能监控和分布式追踪,以及在这过程中的一些关键技术点和实践经验。 1 分布式链路追踪概述 在微服…...

Grafana v12.0 引入了多项新功能和改进

Grafana v12.0 引入了多项新功能和改进,旨在提升可观测性、仪表板管理和用户体验。以下是主要更新内容的总结: 🚀 主要新功能与改进 1. Git 同步仪表板(Git Sync) Grafana v12.0 支持将仪表板直接同步到 GitHub 仓库…...

利用“Flower”实现联邦机器学习的实战指南

一个很尴尬的现状就是我们用于训练 AI 模型的数据快要用完了。所以我们在大量的使用合成数据! 据估计,目前公开可用的高质量训练标记大约有 40 万亿到 90 万亿个,其中流行的 FineWeb 数据集包含 15 万亿个标记,仅限于英语。 作为…...

MongoDB使用x.509证书认证

文章目录 自定义证书生成CA证书生成服务器之间的证书生成集群证书生成用户证书 MongoDB配置java使用x.509证书连接MongoDBMongoShell使用证书连接 8.0版本的mongodb开启复制集,配置证书认证 自定义证书 生成CA证书 生成ca私钥: openssl genrsa -out ca…...