基于Verilog HDL的状态机描述方法

⭐本专栏针对FPGA进行入门学习,从数电中常见的逻辑代数讲起,结合Verilog HDL语言学习与仿真,主要对组合逻辑电路与时序逻辑电路进行分析与设计,对状态机FSM进行剖析与建模。

🔥文章和代码已归档至【Github仓库:hardware-tutorial】,需要的朋友们自取。或者关注公众号【AIShareLab】,回复 FPGA 也可获取。

文章目录

- 状态图的建立过程

- 状态图描述方法

- 单个always块描述状态机的方法(尽量避免)

- 两个always块描述状态机的方法(推荐写法)

- 使用三个always块分别描述

- 三种描述方法比较

状态图的建立过程

设计一个序列检测器电路。功能是检测出串行输入数据Sin中的4位二进制序列0101(自左至右输入),当检测到该序列时,输出Out=1;没有检测到该序列时,输出Out=0。(注意考虑序列重叠的可能性,如010101,相当于出现两个0101序列)。

解:首先,确定采用米利型状态机设计该电路。因为该电路在连续收到信号0101时,输出为1,其他情况下输出为0,所以采用米利型状态机。

其次,确定状态机的状态图。根据设计要求,该电路至少应有四个状态,分别用S1、S2、S3、S4表示。若假设电路的初始状态用S0表示,则可用五个状态来描述该电路。根据分析,可以画出图(a)所示的原始状态图。

观察该图可以看出,S2、S4为等价状态,可用S2代替S4,于是得到简化状态图。

然后,根据上面的状态图给出该状态机的输出逻辑。该状态机只有一个输出变量Out,其输出逻辑非常简单,直接标注在状态图中了。若输出变量较多,则可以列出输出逻辑真值表。

最后,就可以使用硬件描述语言对状态图进行描述了。

状态图描述方法

利用Verilog HDL语言描述状态图主要包含四部分内容:

-

利用参数定义语句parameter描述状态机中各个状态的名称,并指定状态编码。例如,对序列检测器的状态分配可以使用最简单的自然二进制码,其描述如下:

parameter S0=2'b00, S1=2'b01, S2 = 2'b10, S3 = 2'b11;或者,

parameter [1:0] S0=2'b00, S1=2'b01, S2 = 2'b10, S3 = 2'b11; -

用时序的always 块描述状态触发器实现的状态存储。

-

使用敏感表和case语句(也可以采用if-else等价语句)描述的状态转换逻辑。

-

描述状态机的输出逻辑。

描述状态图的方法多种多样,下面介绍几种:

单个always块描述状态机的方法(尽量避免)

用一个always块对该例的状态机进行描述,其代码如下:

module Detector1 ( Sin, CP, nCR, Out) ;input Sin, CP, nCR; //声明输入变量output Out ; //声明输出变量reg Out; reg [1:0] state;

// 声明两个状态触发器变量state[1]和state[0],记忆电路现态

//The state labels and their assignments

parameter [1:0] S0=2'b00, S1=2'b01, S2 = 2'b10, S3 = 2'b11;

always @(posedge CP or negedge nCR)

begin

if (~nCR)

state <= S0; //在nCR跳变为0时,异步清零

elsecase(state) S0: begin Out =1’b0; state <= (Sin==1)? S0 : S1; endS1: begin Out = 1’b0; state <= (Sin==1)? S2 : S1; endS2: begin Out = 1’b0; state <= (Sin==1)? S0 : S3; end S3: if (Sin==1) begin Out =1’b1; state <= S2; endelse begin Out =1’b0; state <= S1; end endcase

end

endmodule

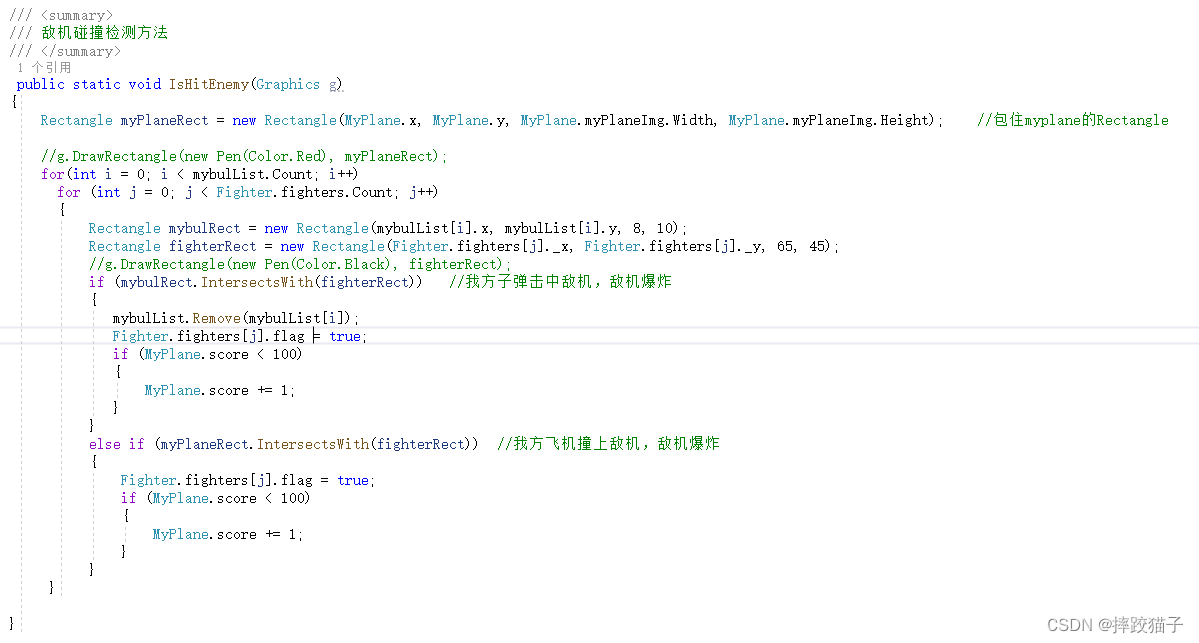

严格地说,对序列检测器电路用单个always块的描述方法所描述的逻辑存在着一个隐含的错误,即输出信号Out的描述。

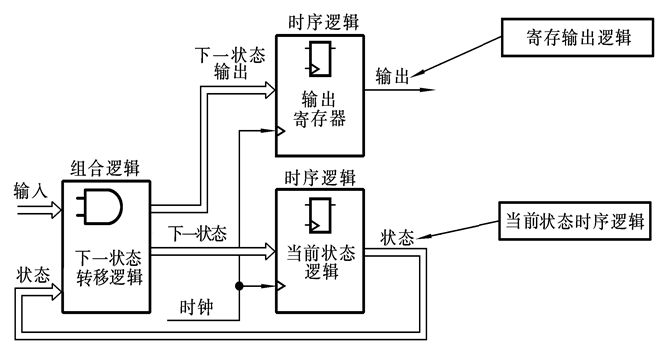

case语句中对输出向量的赋值应是下一个状态输出,这点易出错;状态向量与输出向量都由寄存器实现,面积大,不能实现异步米勒状态机。因此,单个always块描述状态机的写法仅仅适用于穆尔型状态机。单个always块写法的电路结构框图可以用下图进行概括。

两个always块描述状态机的方法(推荐写法)

用两个always块对该例的状态机进行描述,其代码如下:

module Detector2 ( Sin, CP, nCR, Out) ;

input Sin, CP, nCR; //定义输入变量

output Out ; //定义输出变量

reg Out;

reg [1:0] Current_state, Next_state;

parameter [1:0] S0=2'b00, S1=2'b01, S2 = 2'b10, S3 = 2'b11;

//状态转换,时序逻辑always @(posedge CP or negedge nCR )

begin

if (~nCR)Current_state <= S0; //异步清零

elseCurrent_state <= Next_state; //在CP上升沿触发器状态翻转end//下一状态产生和输出信号,组合逻辑

always @( Current_state or Sin) begin Next_state =2’bxx; Out=1’b 0;case(Current_state )S0: begin Out =1’b0; Next_state = (Sin==1)? S0 : S1; endS1: begin Out =1’b0; Next_state = (Sin==1)? S2 : S1; endS2: begin Out =1’b0; Next_state = (Sin==1)? S0 : S3; end S3: if (Sin==1)begin Out =1’b1; Next_state = S2; endelsebegin Out =1’b0; Next_state = S1; end endcaseend endmodule

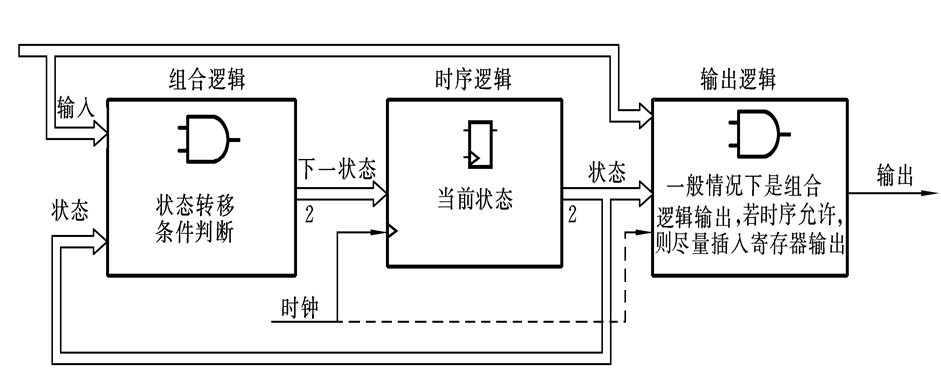

用两个always块描述状态机的写法是值得推荐的方法之一,两个always块写法的电路结构框图可以用下图进行概括。

两个always块写法的电路结构框图概括。

第一个always模块采用同步时序逻辑方式描述状态转移(中间方框); 第二个always模块采用组合逻辑方式描述状态转移规律(第一个方框)和描述电路的输出信号(第三个方框)。

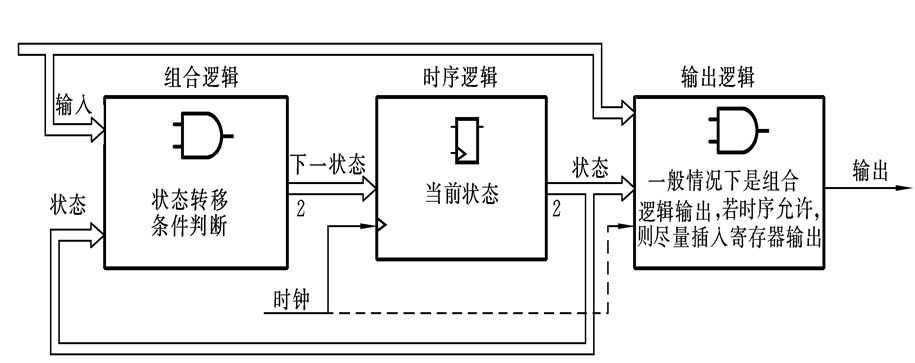

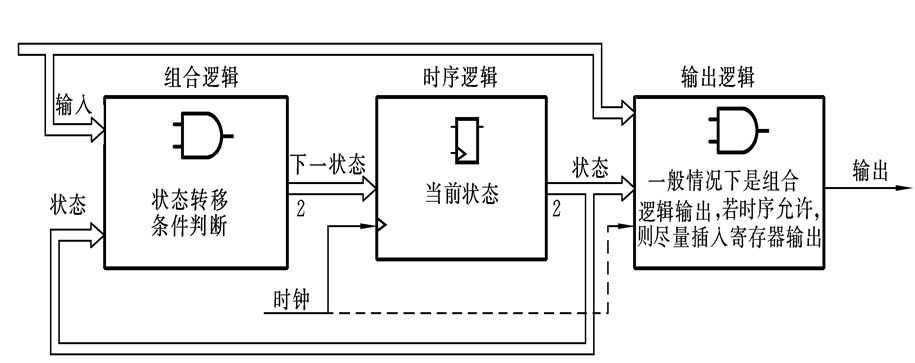

使用三个always块分别描述

即第一个always模块采用同步时序逻辑方式描述状态转移(中间方框); 第二个always模块采用组合逻辑方式描述状态转移规律(第一个方框); 第三个always模块描述电路的输出信号,在时序允许的情况下,通常让输出信号经过一个寄存器再输出,保证输出信号中没有毛刺。

用三个always块对该例的状态机进行描述,其代码如下:

module Detector3 ( Sin, CP, nCR, Out) ;input Sin, CP, nCR; //定义输入变量output Out ; //定义输出变量reg Out; reg [1:0] Current_state, Next_state;parameter [1:0] S0=2'b00, S1=2'b01, S2 = 2'b10, S3 = 2'b11;

//状态转换,时序逻辑

always @(posedge CP or negedge nCR )beginif (~nCR)Current_state <= S0; //异步清零elseCurrent_state <= Next_state; //在CP上升沿触发器状态翻转end //下一状态产生,组合逻辑

always @( Current_state or Sin) begin Next_state =2’bxx; case(Current_state )S0: begin Next_state = (Sin==1)? S0 : S1; endS1: begin Next_state = (Sin==1)? S2 : S1; endS2: begin Next_state = (Sin==1)? S0 : S3; end S3: if (Sin==1)begin Next_state = S2; endelsebegin Next_state = S1; end endcaseend /* 输出逻辑: 让输出信号经过一个寄存器再输出,可以消除Out信号中的毛刺,时序逻辑*/

always @ (posedge CP or negedge nCR )beginif (~nCR) Out <= 1’b 0;else begin case(Current_state )S0, S1, S2: Out <= 1’b0; S3: if (Sin==1) Out <= 1’b1; else Out <= 1’b0; endcaseend end

endmodule

三种描述方法比较

| 1-always | 2-always | 3-always | |

|---|---|---|---|

| 结构化设计 | 否 | 是 | 是 |

| 代码编写/理解 | 不宜,理解难 | 宜 | 宜 |

| 输出信号 | 寄存器输出 | 组合逻辑输出 | 寄存器输出 |

| 不产生毛刺 | 产生毛刺 | 不产生毛刺 | |

| 面积消耗 | 大 | 最小 | 小 |

| 时序约束 | 不利 | 有利 | 有利 |

| 可靠性、可维护性 | 低 | 较高 | 最高 |

| 后端物理设计 | 不利 | 有利 | 有利 |

参考文献:

- Verilog HDL与FPGA数字系统设计,罗杰,机械工业出版社,2015年04月

- Verilog HDL与CPLD/FPGA项目开发教程(第2版), 聂章龙, 机械工业出版社, 2015年12月

- Verilog HDL数字设计与综合(第2版), Samir Palnitkar著,夏宇闻等译, 电子工业出版社, 2015年08月

- Verilog HDL入门(第3版), J. BHASKER 著 夏宇闻甘伟 译, 北京航空航天大学出版社, 2019年03月

相关文章:

基于Verilog HDL的状态机描述方法

⭐本专栏针对FPGA进行入门学习,从数电中常见的逻辑代数讲起,结合Verilog HDL语言学习与仿真,主要对组合逻辑电路与时序逻辑电路进行分析与设计,对状态机FSM进行剖析与建模。 🔥文章和代码已归档至【Github仓库…...

6年软件测试经历:成长、迷茫、奋斗

前言 测试工作6年,经历过不同产品、共事过不同专业背景、能力的同事,踩过测试各种坑、遇到过各种bug。测试职场生涯积极努力上进业务和技术能力快速进步过、也有努力付出却一无所得过、有对测试生涯前景充满希望认为一片朝气蓬勃过、也有对中年危机思考不…...

OpenMMLab AI实战营第五次课程

语义分割与MMSegmentation 什么是语义分割 任务: 将图像按照物体的类别分割成不同的区域 等价于: 对每个像素进行分类 应用:无人驾驶汽车 自动驾驶车辆,会将行人,其他车辆,行车道,人行道、交…...

【软考】系统集成项目管理工程师(二十)项目风险管理

一、项目风险管理概述1. 风险概念2. 风险分类3. 风险成本二、项目风险管理子过程1. 规划风险管理2. 识别风险3. 实施定性风险分析4. 实施定量风险分析5. 规划风险应对6. 控制风险三、项目风险管理流程梳理一、项目风险管理概述 1. 风险概念 风险是一种不确定事件或条件,一旦…...

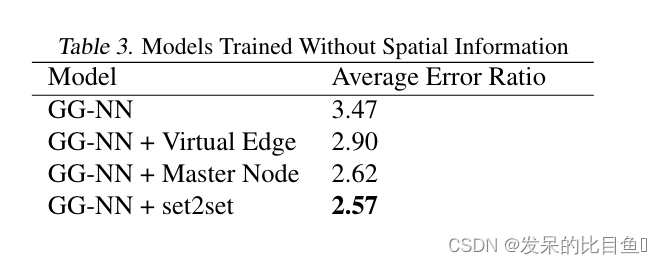

2017-PMLR-Neural Message Passing for Quantum Chemistry

2017-PMLR-Neural Message Passing for Quantum Chemistry Paper: https://arxiv.org/pdf/1704.01212.pdf Code: https://github.com/brain-research/mpnn 量子化学的神经信息传递 这篇文献作者主要是总结了先前神经网络模型的共性,提出了一种消息传递神经网络&am…...

)

Python:每日一题之全球变暖(DFS连通性判断)

题目描述 你有一张某海域 NxN 像素的照片,"."表示海洋、"#"表示陆地,如下所示: ....... .##.... .##.... ....##. ..####. ...###. ....... 其中"上下左右"四个方向上连在一起的一片陆地组成一座岛屿…...

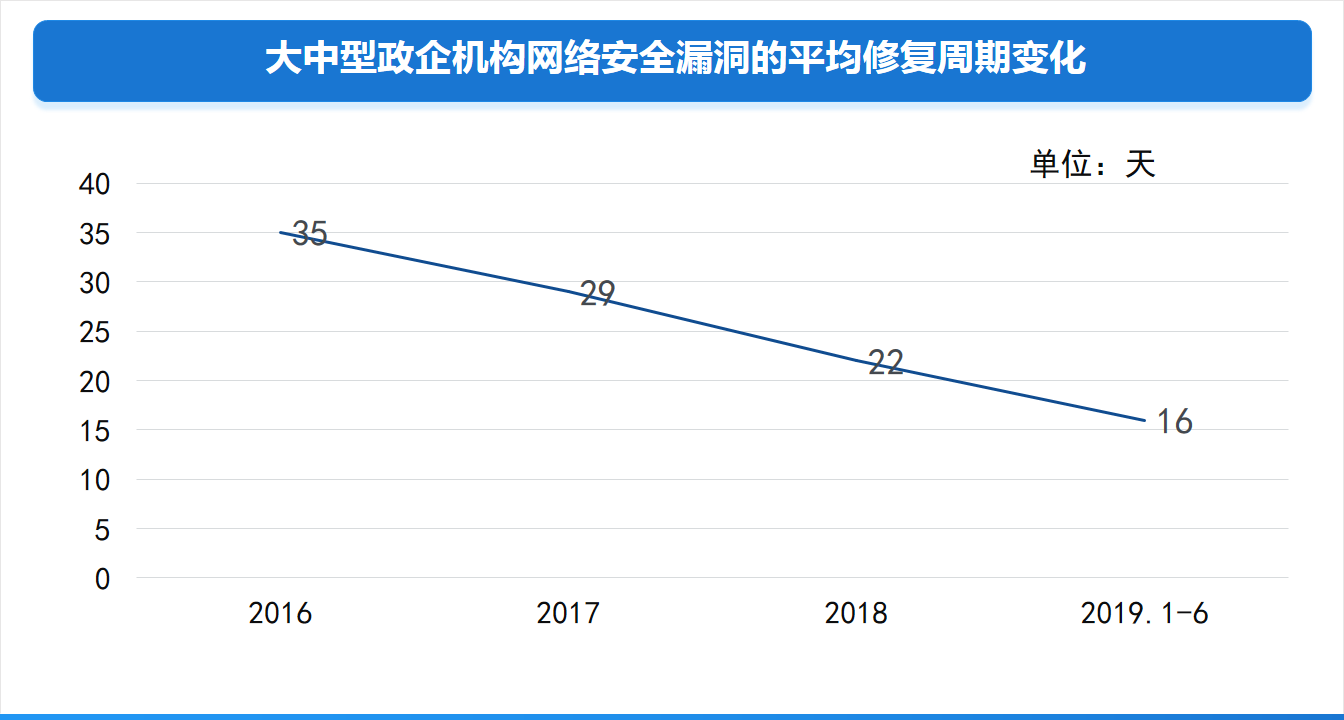

企业级安全软件装机量可能大增

声明 本文是学习大中型政企机构网络安全建设发展趋势研究报告. 而整理的学习笔记,分享出来希望更多人受益,如果存在侵权请及时联系我们 研究背景 大中型政企机构是网络安全保护的重中之重,也是国内网络安全建设投入最大,应用新技术、新产品最多的机构…...

为什么要用频谱分析仪测量频谱?

频谱分析仪是研究电信号频谱结构的仪器,用于信号失真度、调制度、谱纯度、频率稳定度和交调失真等信号参数的测量,可用以测量放大器和滤波器等电路系统的某些参数,是一种多用途的电子测量仪器。从事通信工程的技术人员,在很多时候…...

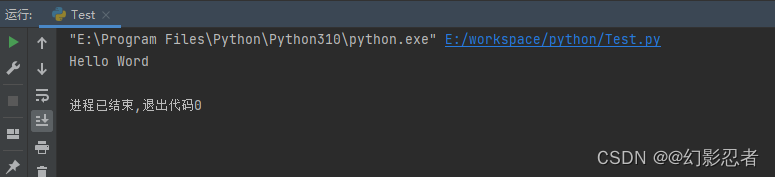

Python环境搭建、Idea整合

1、学python先要下载什么? 2、python官网 3、idea配置Python 4、idea新建python 学python先要下载什么? python是一种语言,首先你需要下载python,有了python环境,你才可以在你的电脑上使用python。现在大多使用的是pyt…...

HTTP请求返回304状态码以及研究nginx中的304

文章目录1. 引出问题2. 分析问题3. 解决问题4. 研究nginx中的3044.1 启动服务4.2 ETag说明4.3 响应头Cache-Control1. 引出问题 之前在调试接口时,代码总出现304问题,如下所示: 2. 分析问题 HTTP 304: Not Modified是什么意思? …...

【GD32F427开发板试用】使用Arm-2D显示电池电量

本篇文章来自极术社区与兆易创新组织的GD32F427开发板评测活动,更多开发板试用活动请关注极术社区网站。作者:boc 【虽迟但到】 由于快递的原因,11月份申请的,12月1日才收到GD32F427开发板。虽然姗姗来迟,但也没有减少…...

TS第二天 Typesrcipt编译

文章目录自动编译tsconfig.json配置选项include 比较重要excludeextendsfilescompilerOptions 比较重要自动编译 手动模式:每次ts文件修改完,手动编译一次 tsc 01.ts监视模式:ts文件修改完,自动监视编译 tsc 01.ts -w编译所有文…...

基于C#制作一个飞机大战小游戏

此文主要基于C#制作一个飞机大战游戏,重温经典的同时亦可学习。 实现流程1、创建项目2、界面绘制3、我方飞机4、敌方飞机5、子弹及碰撞检测实现流程 1、创建项目 打开Visual Studio,右侧选择创建新项目。 搜索框输入winform,选择windows窗体…...

git修改历史提交(commit)信息

我们在开发中使用git经常会遇到想要修改之前commit的提交信息,这里记录下怎么使用git修改之前已经提交的信息。一、修改最近一次commit的信息 首先通过git log查看commit信息。 我这里一共有6次commit记录。 最新的commit信息为“Merge branch ‘master’ of https:…...

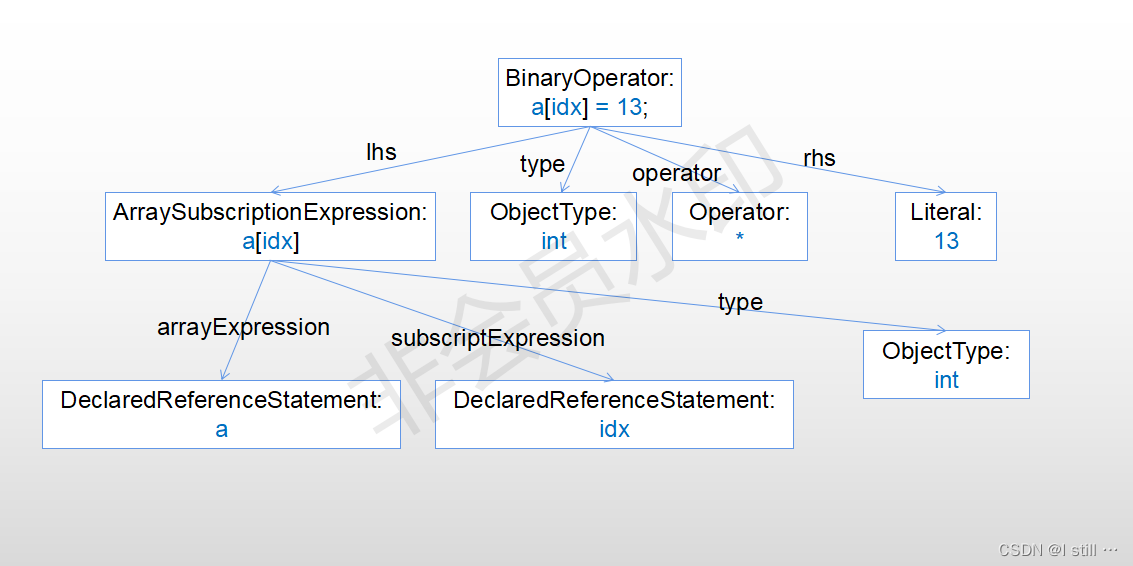

代码解析工具cpg

cpg 是一个跨语言代码属性图解析工具,它目前支持C/C (C17), Java (Java 13)并且对Go, LLVM, python, TypeScript也有支持,在这个项目的根目录下: cpg-core为cpg解析模块的核心功能,主要包括将代码解析为图,core模块只包括对C/C/Ja…...

Linux虚拟机部署Java环境-Jdk-Mysql

Linux虚拟机部署 author hf 1.安装 电脑安装x-shell工具,然后使用堡垒机基础控件windows版进行安装扫描,最后点击自动检测,保证能扫描到X-shell工具的安装路径 使用堡垒机登录快照夏选择工具点击Xshell进行连接 查看linux版本 root:~# ca…...

每日学术速递2.9

CV - 计算机视觉 | ML - 机器学习 | RL - 强化学习 | NLP 自然语言处理 Subjects: cs.CV、cs.AI、cs.LG、cs.IR 1.Graph Signal Sampling for Inductive One-Bit Matrix Completion: a Closed-form Solution(ICLR 2023) 标题:归纳单比特矩阵完成的图信号采样&am…...

【Linux】进程优先级 | 进程的切换 | 环境变量详解

🤣 爆笑教程 👉 《看表情包学Linux》👈 猛戳订阅 🔥 💭 写在前面:我们先讲解进程的优先级,探讨为什么会存在优先级,以及如何查看系统进程、进程优先级的修改。然后讲解进程的切…...

leaflet 实现左卷帘效果 (代码示例045)

第045个 点击查看专栏目录 本示例的目的是介绍演示如何在vue+leaflet中实现左卷帘效果,这里主要引用了leaflet-side-by-side这个插件,直接调用的话,CSS方面有些问题,需要自行调整一下。 直接复制下面的 vue+leaflet源代码,操作2分钟即可运行实现效果 文章目录 示例效果配…...

程序的翻译环境和执行环境

程序环境和预处理🦖程序的翻译环境和执行环境🦖详解编译链接🐳 翻译环境🐳 详解编译过程🐳 运行环境🦖预处理详解🐳 预定义符号🐳 #define🦀 #define 定义标识符…...

终极指南:5分钟让Figma界面全面中文化,设计师效率翻倍!

终极指南:5分钟让Figma界面全面中文化,设计师效率翻倍! 【免费下载链接】figmaCN 中文 Figma 插件,设计师人工翻译校验 项目地址: https://gitcode.com/gh_mirrors/fi/figmaCN 还在为Figma的英文界面而烦恼吗?每…...

前端工程化:代码审查最佳实践

前端工程化:代码审查最佳实践 前言 代码审查是保障代码质量的第一道防线。一个好的代码审查流程不仅能发现潜在的bug,还能促进团队知识共享,提升整体代码水平。今天我就来给大家讲讲如何建立一套高效的代码审查流程。 什么是代码审查 代码审查…...

本地部署YakGPT:打造私有化ChatGPT前端,实现语音交互与数据安全

1. 项目概述:为什么我们需要一个本地运行的ChatGPT UI? 如果你和我一样,已经深度依赖ChatGPT来处理日常工作,从代码调试到文案构思,那你肯定也经历过官方网页端那令人捉急的加载速度,或者在移动端上打字的…...

混合量子-经典工作流编排的云原生实践

1. 混合量子-经典工作流编排的挑战与机遇量子计算正从实验室走向实际应用,但当前NISQ(Noisy Intermediate-Scale Quantum)时代的量子设备仍面临量子比特数量有限、噪声干扰强等限制。这使得混合量子-经典工作流(Hybrid Quantum–C…...

实时代码光标同步工具:跨设备与团队协作的开发效率利器

1. 项目概述:一个为开发者设计的代码光标同步工具如果你和我一样,经常需要在多台设备、多个编辑器窗口,甚至是与同事进行远程结对编程时,保持代码编辑位置的同步,那么你肯定理解那种来回切换、手动寻找上次编辑位置的痛…...

TalkReplay:构建本地化AI编程对话时光机,实现知识持久化管理

1. 项目概述:一个为AI编程对话而生的“时光机”如果你和我一样,日常开发已经离不开Claude、Cursor这类AI编程助手,那你一定遇到过这个痛点:和AI进行了一下午的深度对话,写了几百行代码,解决了几个关键问题。…...

工程师必读:六大情感触发器,破解技术产品市场转化难题

1. 项目概述:当工程师遇上商业,一场关于“情感”的必修课最近有个工程师朋友跟我抱怨,说他团队花了两年心血打磨的产品,技术指标全面领先,结果推向市场后反响平平,远不如隔壁一个技术平平但“会讲故事”的竞…...

认知神经科学研究报告【20260045】

文章目录ForeSight 5.87.5 自动设计8位CPU架构MiniCPU-8 架构自动涌现 — 测试报告结果ForeSight 5.87.5 自动设计8位CPU架构 MiniCPU-8 架构自动涌现 — 测试报告 测试目标:验证系统能否从零开始,自主发现并实现一个能正确执行斐波那契数列计算的8位C…...

作业4:独立按键+数码管实操

文章目录 1.测试代码视频2.流水灯视频3.独立按键视频(点亮四个灯)4.独立按键视频(思考题点亮8个灯)5.数码管显示“111111”6.数码管显示“123456”7.数码管显示“11.12.13”8.数码管显示“HH8800.” 1.测试代码视频 测试2.流水灯视频 流水灯#include <reg51.h> // 包含…...

从拿订单到看方向

在企业积极应对全球化挑战的实践中,贸易型展会(如广交会)因其汇聚全球商业生态的独特属性,成为企业探索市场、验证策略、获取关键资源的核心节点。未来,供应链全球化将更加强调在动态平衡中构建网络韧性,企…...