单片机外部晶振故障后自动切换内部晶振——以STM32为例

单片机外部晶振故障后自动切换内部晶振——以STM32为例

| 作者 | 日期 | 版本 | 说明 |

|---|---|---|---|

| Dog Tao | 2023.08.02 | V1.0 | 发布初始版本 |

文章目录

- 单片机外部晶振故障后自动切换内部晶振——以STM32为例

- 背景

- 外部晶振与内部振荡器

- STM32F103时钟系统

- STM32F407时钟系统

- 代码实现

- 系统时钟设置流程

- 时钟源检测与切换

- 使用内部振荡器

- 总结

背景

时钟信号是单片机的心跳,对嵌入式系统的长期稳定运行有着至关重要的作用。现代单片机的时钟信号一般都支持外部时钟、外部晶体振荡器、内部RC振荡器等形式的输入。外部晶体振荡器(晶振)由于其高精度、高稳定性、低温飘、低成本的特性,广泛应用于各类对通讯、时间、性能要求严格的场合。

外部晶振与内部振荡器

-

外部晶振:这种时钟源来自于微控制器外部的晶振或者振荡器。晶振是一种机械振动器件,利用压电效应或反压电效应产生精确的频率。外部晶振的主要优点是精度高,稳定性好。但是,他们可能需要额外的电路空间,并且可能更容易受到环境因素如温度和震动的影响。

-

内部振荡器:这是一种集成在微控制器内部的时钟源。它通常是基于RC(电阻-电容)网络的振荡器。内部振荡器的优点是它们不需要额外的硬件,更便宜,更节省空间。但是,他们的频率精度和稳定性通常较低。

在实际应用中,选择哪种时钟源取决于具体的设计需求。对于需要高精度和稳定性的应用,通常会选择外部晶振。对于成本和空间更为重要的应用,内部振荡器可能是一个更好的选择。

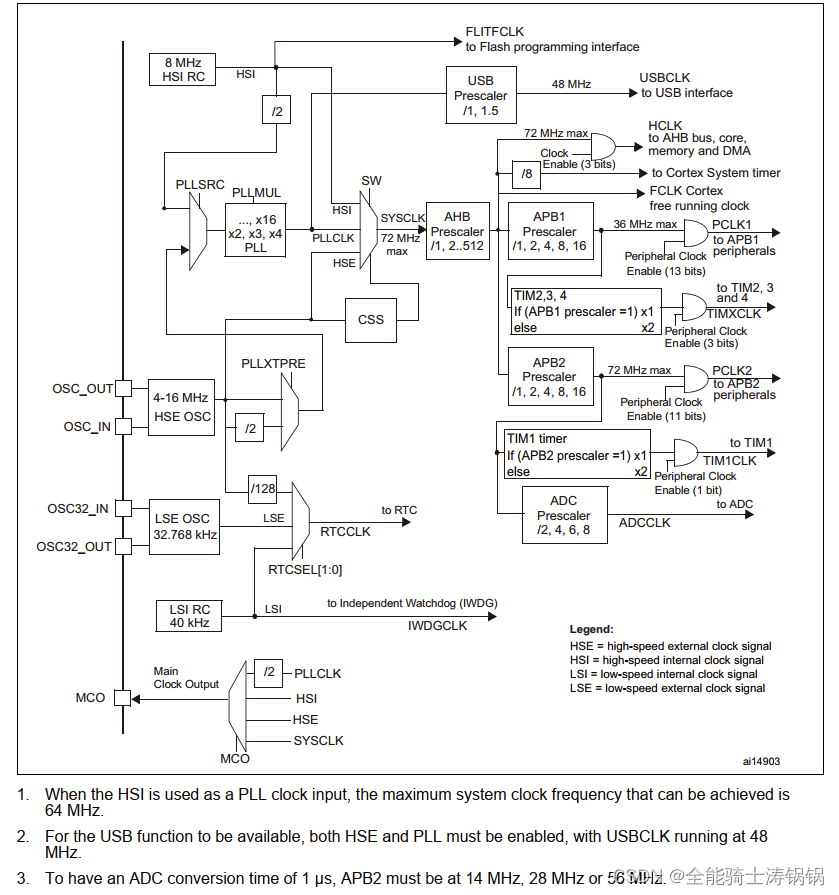

STM32F103时钟系统

STM32F103的时钟系统相当复杂,主要有四种时钟源:高速内部(HSI)时钟,高速外部(HSE)时钟,低速内部(LSI)时钟,以及低速外部(LSE)时钟。

- 高速内部(HSI)时钟:一个自校准的内部RC振荡器,提供8MHz的时钟。

- 高速外部(HSE)时钟:可以连接到一个外部4-16 MHz的晶振或者用户提供的时钟源。

- 低速内部(LSI)时钟:一个内部RC振荡器,提供40kHz的时钟,主要供独立看门狗和自动唤醒单元使用。

- 低速外部(LSE)时钟:可以连接到一个外部32.768 kHz的晶振,主要用于RTC(实时时钟)和LCD。

如果使用外部晶振(HSE),STM32F103的最大系统时钟频率可以达到72 MHz。如果使用内部振荡器(HSI),STM32F103的最大系统时钟频率可以达到64 MHz。

STM32F407时钟系统

STM32F407的时钟系统与STM32F103的类似,也包括HSI,HSE,LSI和LSE四种时钟。但是其高速内部时钟频率达到了16MHz。

在STM32F407中,无论是16 MHz的HSI还是最高可以到24 MHz的HSE,都可以通过PLL倍频到168 MHz作为系统时钟频率。

STM32F103的时钟系统

代码实现

系统时钟设置流程

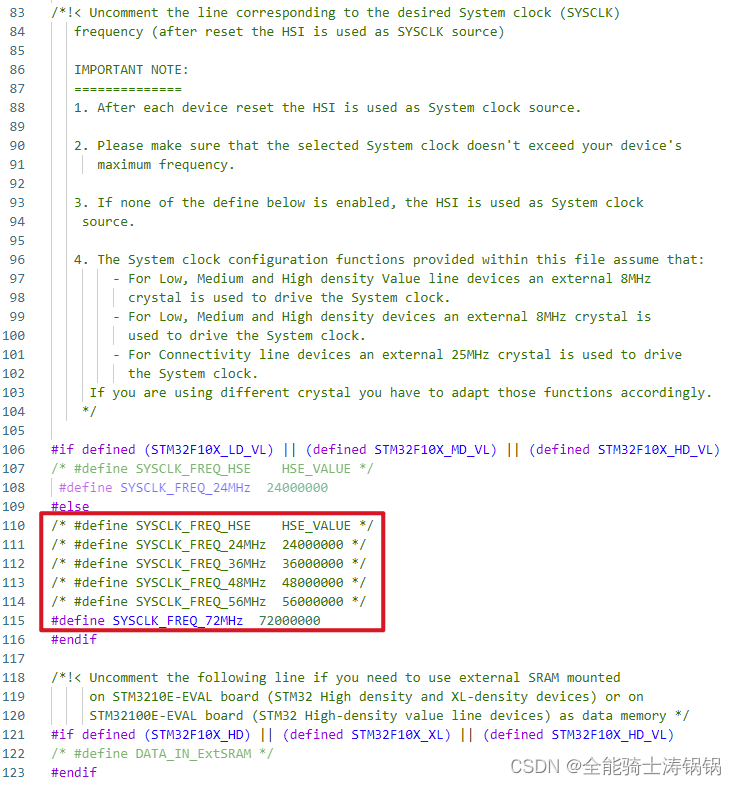

在STM32F103的标准库函数中,“system_stm32f10x.c”文件提供了多个不同频率的系统时钟设置方法,可以通过宏定义的方式条件编译指定时钟频率的设置函数,如下图所示:

基于标准库函数的系统时钟设置调用路径依次为:

基于标准库函数的系统时钟设置调用路径依次为:

- 启动文件“startup_stm32f103x8.s”调用位于“system_stm32f10x.c”文件中的

SystemInit()函数。 SystemInit()函数调用SetSysClock()函数。SetSysClock()函数根据上述宏定义调用不同的时钟设置函数,将系统时钟设置为指定频率。- 使用全局变量

SystemCoreClock可获取当前系统的时钟频率。

时钟源检测与切换

在上述位于“system_stm32f10x.c”文件中系统时钟设置函数中已经内置了相关功能的模板,以SetSysClockTo72()函数为例:

/*** @brief Sets System clock frequency to 72MHz and configure HCLK, PCLK2 * and PCLK1 prescalers. * @note This function should be used only after reset.* @param None* @retval None*/

static void SetSysClockTo72(void)

{__IO uint32_t StartUpCounter = 0, HSEStatus = 0;/* SYSCLK, HCLK, PCLK2 and PCLK1 configuration ---------------------------*/ /* Enable HSE */ RCC->CR |= ((uint32_t)RCC_CR_HSEON);/* Wait till HSE is ready and if Time out is reached exit */do{HSEStatus = RCC->CR & RCC_CR_HSERDY;StartUpCounter++; } while((HSEStatus == 0) && (StartUpCounter != HSE_STARTUP_TIMEOUT));if ((RCC->CR & RCC_CR_HSERDY) != RESET){HSEStatus = (uint32_t)0x01;}else{HSEStatus = (uint32_t)0x00;} if (HSEStatus == (uint32_t)0x01){/* Enable Prefetch Buffer */FLASH->ACR |= FLASH_ACR_PRFTBE;/* Flash 2 wait state */FLASH->ACR &= (uint32_t)((uint32_t)~FLASH_ACR_LATENCY);FLASH->ACR |= (uint32_t)FLASH_ACR_LATENCY_2; /* HCLK = SYSCLK */RCC->CFGR |= (uint32_t)RCC_CFGR_HPRE_DIV1;/* PCLK2 = HCLK */RCC->CFGR |= (uint32_t)RCC_CFGR_PPRE2_DIV1;/* PCLK1 = HCLK */RCC->CFGR |= (uint32_t)RCC_CFGR_PPRE1_DIV2;#ifdef STM32F10X_CL/* Configure PLLs ------------------------------------------------------*//* PLL2 configuration: PLL2CLK = (HSE / 5) * 8 = 40 MHz *//* PREDIV1 configuration: PREDIV1CLK = PLL2 / 5 = 8 MHz */RCC->CFGR2 &= (uint32_t)~(RCC_CFGR2_PREDIV2 | RCC_CFGR2_PLL2MUL |RCC_CFGR2_PREDIV1 | RCC_CFGR2_PREDIV1SRC);RCC->CFGR2 |= (uint32_t)(RCC_CFGR2_PREDIV2_DIV5 | RCC_CFGR2_PLL2MUL8 |RCC_CFGR2_PREDIV1SRC_PLL2 | RCC_CFGR2_PREDIV1_DIV5);/* Enable PLL2 */RCC->CR |= RCC_CR_PLL2ON;/* Wait till PLL2 is ready */while((RCC->CR & RCC_CR_PLL2RDY) == 0){}/* PLL configuration: PLLCLK = PREDIV1 * 9 = 72 MHz */ RCC->CFGR &= (uint32_t)~(RCC_CFGR_PLLXTPRE | RCC_CFGR_PLLSRC | RCC_CFGR_PLLMULL);RCC->CFGR |= (uint32_t)(RCC_CFGR_PLLXTPRE_PREDIV1 | RCC_CFGR_PLLSRC_PREDIV1 | RCC_CFGR_PLLMULL9);

#else /* PLL configuration: PLLCLK = HSE * 9 = 72 MHz */RCC->CFGR &= (uint32_t)((uint32_t)~(RCC_CFGR_PLLSRC | RCC_CFGR_PLLXTPRE |RCC_CFGR_PLLMULL));RCC->CFGR |= (uint32_t)(RCC_CFGR_PLLSRC_HSE | RCC_CFGR_PLLMULL9);

#endif /* STM32F10X_CL *//* Enable PLL */RCC->CR |= RCC_CR_PLLON;/* Wait till PLL is ready */while((RCC->CR & RCC_CR_PLLRDY) == 0){}/* Select PLL as system clock source */RCC->CFGR &= (uint32_t)((uint32_t)~(RCC_CFGR_SW));RCC->CFGR |= (uint32_t)RCC_CFGR_SW_PLL; /* Wait till PLL is used as system clock source */while ((RCC->CFGR & (uint32_t)RCC_CFGR_SWS) != (uint32_t)0x08){}}else{ /* If HSE fails to start-up, the application will have wrong clock configuration. User can add here some code to deal with this error */}

}

因此,只需要设计实现当外部晶振启动失败后的情况即可,函数框架如下:

static void SetSysClockTo72(void)

{__IO uint32_t StartUpCounter = 0, HSEStatus = 0;/* 省略无关内容 */ if (HSEStatus == (uint32_t)0x01){/* HSE启动成功 */}else{ /* 自定内容:HSE启动失败,尝试启动内部振荡器,并更新系统时钟 */SetSysClockTo48_HSI();SystemCoreClockUpdate();}

}

使用内部振荡器

HSE启动失败,尝试启动内部振荡器,并更新系统时钟的自定义代码示例如下:

static void SetSysClockTo48_HSI()

{/* 开启HSI 即内部晶振时钟 */RCC->CR |= (uint32_t)0x00000001; /*选择HSI为PLL的时钟源HSI必须2分频给PLL*/RCC->CFGR |= (uint32_t)RCC_CFGR_PLLSRC_HSI_Div2; /*PLLCLK=8/2*12=48MHz 设置倍频得到时钟源PLL的频率*/RCC->CFGR |= (uint32_t)RCC_CFGR_PLLMULL12;/* PLL不分频输出 */RCC->CFGR |= (uint32_t)RCC_CFGR_HPRE_DIV1;/* 使能 PLL时钟 */RCC->CR |= RCC_CR_PLLON;/* 等待PLL时钟就绪*/while((RCC->CR & RCC_CR_PLLRDY) == 0){}/* 选择PLL为系统时钟的时钟源 */RCC->CFGR &= (uint32_t)((uint32_t)~(RCC_CFGR_SW));RCC->CFGR |= (uint32_t)RCC_CFGR_SW_PLL; /* 等到PLL成为系统时钟的时钟源*/while ((RCC->CFGR & (uint32_t)RCC_CFGR_SWS) != (uint32_t)0x08){}

}

使用内部振荡器设置系统时钟之后,需要调用预设的SystemCoreClockUpdate()完成时钟频率的更新(更新全局变量SystemCoreClock的值)。

/*** @brief Update SystemCoreClock variable according to Clock Register Values.* The SystemCoreClock variable contains the core clock (HCLK), it can* be used by the user application to setup the SysTick timer or configure* other parameters.* * @note Each time the core clock (HCLK) changes, this function must be called* to update SystemCoreClock variable value. Otherwise, any configuration* based on this variable will be incorrect. * * @note - The system frequency computed by this function is not the real * frequency in the chip. It is calculated based on the predefined * constant and the selected clock source:* * - If SYSCLK source is HSI, SystemCoreClock will contain the HSI_VALUE(*)* * - If SYSCLK source is HSE, SystemCoreClock will contain the HSE_VALUE(**)* * - If SYSCLK source is PLL, SystemCoreClock will contain the HSE_VALUE(**) * or HSI_VALUE(*) multiplied by the PLL factors.* * (*) HSI_VALUE is a constant defined in stm32f1xx.h file (default value* 8 MHz) but the real value may vary depending on the variations* in voltage and temperature. * * (**) HSE_VALUE is a constant defined in stm32f1xx.h file (default value* 8 MHz or 25 MHz, depedning on the product used), user has to ensure* that HSE_VALUE is same as the real frequency of the crystal used.* Otherwise, this function may have wrong result.* * - The result of this function could be not correct when using fractional* value for HSE crystal.* @param None* @retval None*/

void SystemCoreClockUpdate (void)

{uint32_t tmp = 0, pllmull = 0, pllsource = 0;#ifdef STM32F10X_CLuint32_t prediv1source = 0, prediv1factor = 0, prediv2factor = 0, pll2mull = 0;

#endif /* STM32F10X_CL */#if defined (STM32F10X_LD_VL) || defined (STM32F10X_MD_VL) || (defined STM32F10X_HD_VL)uint32_t prediv1factor = 0;

#endif /* STM32F10X_LD_VL or STM32F10X_MD_VL or STM32F10X_HD_VL *//* Get SYSCLK source -------------------------------------------------------*/tmp = RCC->CFGR & RCC_CFGR_SWS;switch (tmp){case 0x00: /* HSI used as system clock */SystemCoreClock = HSI_VALUE;break;case 0x04: /* HSE used as system clock */SystemCoreClock = HSE_VALUE;break;case 0x08: /* PLL used as system clock *//* Get PLL clock source and multiplication factor ----------------------*/pllmull = RCC->CFGR & RCC_CFGR_PLLMULL;pllsource = RCC->CFGR & RCC_CFGR_PLLSRC;#ifndef STM32F10X_CL pllmull = ( pllmull >> 18) + 2;if (pllsource == 0x00){/* HSI oscillator clock divided by 2 selected as PLL clock entry */SystemCoreClock = (HSI_VALUE >> 1) * pllmull;}else{#if defined (STM32F10X_LD_VL) || defined (STM32F10X_MD_VL) || (defined STM32F10X_HD_VL)prediv1factor = (RCC->CFGR2 & RCC_CFGR2_PREDIV1) + 1;/* HSE oscillator clock selected as PREDIV1 clock entry */SystemCoreClock = (HSE_VALUE / prediv1factor) * pllmull; #else/* HSE selected as PLL clock entry */if ((RCC->CFGR & RCC_CFGR_PLLXTPRE) != (uint32_t)RESET){/* HSE oscillator clock divided by 2 */SystemCoreClock = (HSE_VALUE >> 1) * pllmull;}else{SystemCoreClock = HSE_VALUE * pllmull;}#endif}

#elsepllmull = pllmull >> 18;if (pllmull != 0x0D){pllmull += 2;}else{ /* PLL multiplication factor = PLL input clock * 6.5 */pllmull = 13 / 2; }if (pllsource == 0x00){/* HSI oscillator clock divided by 2 selected as PLL clock entry */SystemCoreClock = (HSI_VALUE >> 1) * pllmull;}else{/* PREDIV1 selected as PLL clock entry *//* Get PREDIV1 clock source and division factor */prediv1source = RCC->CFGR2 & RCC_CFGR2_PREDIV1SRC;prediv1factor = (RCC->CFGR2 & RCC_CFGR2_PREDIV1) + 1;if (prediv1source == 0){ /* HSE oscillator clock selected as PREDIV1 clock entry */SystemCoreClock = (HSE_VALUE / prediv1factor) * pllmull; }else{/* PLL2 clock selected as PREDIV1 clock entry *//* Get PREDIV2 division factor and PLL2 multiplication factor */prediv2factor = ((RCC->CFGR2 & RCC_CFGR2_PREDIV2) >> 4) + 1;pll2mull = ((RCC->CFGR2 & RCC_CFGR2_PLL2MUL) >> 8 ) + 2; SystemCoreClock = (((HSE_VALUE / prediv2factor) * pll2mull) / prediv1factor) * pllmull; }}

#endif /* STM32F10X_CL */ break;default:SystemCoreClock = HSI_VALUE;break;}/* Compute HCLK clock frequency ----------------*//* Get HCLK prescaler */tmp = AHBPrescTable[((RCC->CFGR & RCC_CFGR_HPRE) >> 4)];/* HCLK clock frequency */SystemCoreClock >>= tmp;

}

总结

本文所述的设计方法,能够在外部晶振故障后自动切换到内部晶振,提高系统的可靠性与稳定性。注意,上述示例只在单片机启动时进行时钟源检测,因此,如果是处理运行时的突发时钟故障,需要设计配套的看门狗,在系统陷入异常状态后自动重启系统。

相关文章:

单片机外部晶振故障后自动切换内部晶振——以STM32为例

单片机外部晶振故障后自动切换内部晶振——以STM32为例 作者日期版本说明Dog Tao2023.08.02V1.0发布初始版本 文章目录 单片机外部晶振故障后自动切换内部晶振——以STM32为例背景外部晶振与内部振荡器STM32F103时钟系统STM32F407时钟系统 代码实现系统时钟设置流程时钟源检测…...

)

Matlab实现决策树算法(附上多个完整仿真源码)

决策树是一种常见的机器学习算法,它可以用于分类和回归问题。在本文中,我们将介绍如何使用Matlab实现决策树算法。 文章目录 1. 数据预处理2. 构建决策树模型3. 测试模型4. 可视化决策树5. 总结6. 完整仿真源码下载 1. 数据预处理 在使用决策树算法之前…...

java中异步socket类的实现和源代码

java中异步socket类的实现和源代码 我们知道,java中socket类一般操作都是同步进行,常常在read的时候socket就会阻塞直到有数据可读或socket连接断开的时候才返回,虽然可以设置超时返回,但是这样比较低效,需要做一个循环来不停扫描…...

ElasticSearch7.6入门学习笔记

在学习ElasticSearch之前,先简单了解一下Lucene: Doug Cutting开发 是apache软件基金会4 jakarta项目组的一个子项目 是一个开放源代码的全文检索引擎工具包不是一个完整的全文检索引擎,而是一个全文检索引擎的架构,提供了完整的…...

《面试1v1》ElasticSearch架构设计

🍅 作者简介:王哥,CSDN2022博客总榜Top100🏆、博客专家💪 🍅 技术交流:定期更新Java硬核干货,不定期送书活动 🍅 王哥多年工作总结:Java学习路线总结…...

tomcat和nginx的日志记录请求时间

当系统卡顿时候,我们需要分析时间花费在哪个缓解。项目的后端接口可以记录一些时间,此外,在我们的tomcat容器和nginx网关上也可以记录一些有关请求用户,请求时间,响应时间的数据,可以提供更多的信息以便于排…...

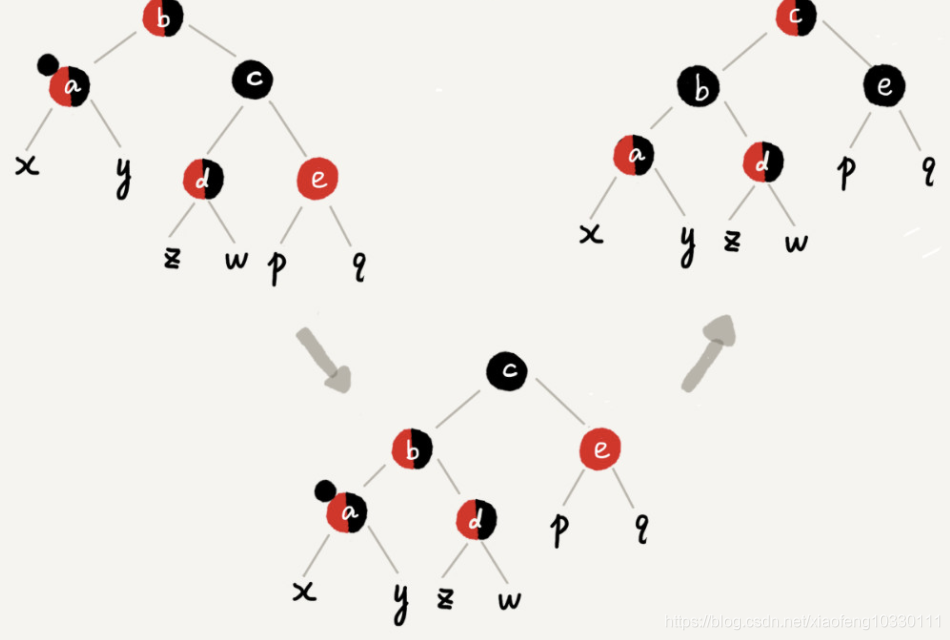

数据结构——红黑树基础(博文笔记)

数据结构在查找这一章里介绍过这些数据结构:BST,AVL,RBT,B和B。 除去RBT,其他的数据结构之前的学过,都是在BST的基础上进行微小的限制。 1.比如AVL是要求任意节点的左右子树深度之差绝对值不大于1,由此引出…...

盘点帮助中心系统可以帮到我们什么呢?

在线帮助中心系统是一种强大的软件系统,可以让我们用来组织、管理、发布、更新和维护企业的宝贵知识库和用户文档。今天looklook就详细讲讲,除了大众所熟知的这些,帮助中心系统还有什么特别作用呢? 帮助中心系统的作用 1.快速自助…...

Web3 solidity编写交易所合约 编写ETH和自定义代币存入逻辑 并带着大家手动测试

上文 Web3 叙述交易所授权置换概念 编写transferFrom与approve函数我们写完一个简单授权交易所的逻辑 但是并没有测试 其实也不是我不想 主要是 交易所也没实例化 现在也测试不了 我们先运行 ganache 启动一个虚拟的区块链环境 先发布 在终端执行 truffle migrate如果你跟着我…...

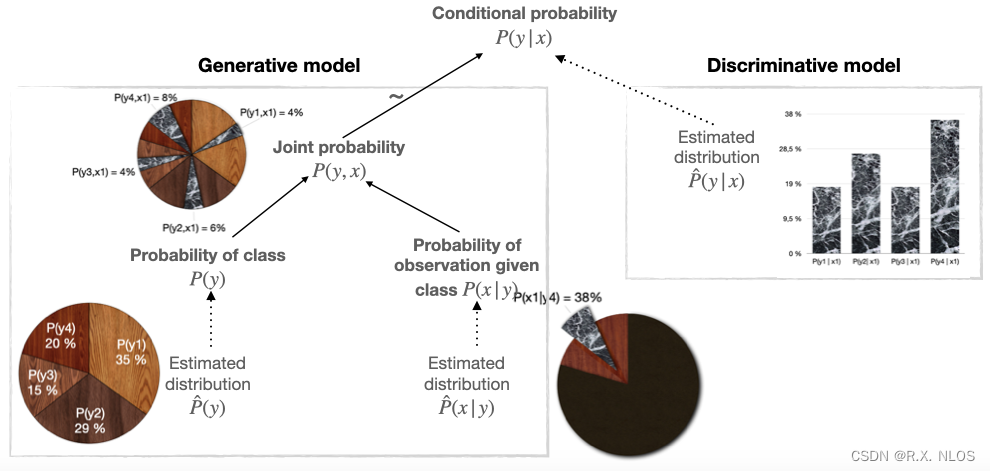

概念解析 | 生成式与判别式模型在低级图像恢复与点云重建中的角力:一场较量与可能性探索

注1:本文系“概念解析”系列之一,致力于简洁清晰地解释、辨析复杂而专业的概念。本次辨析的概念是:生成式模型与判别式模型在低级图像恢复/点云重建任务中的优劣与特性。 生成式与判别式模型在低级图像恢复与点云重建中的角力:一场较量与可能性探索 1. 背景介绍 机器学习…...

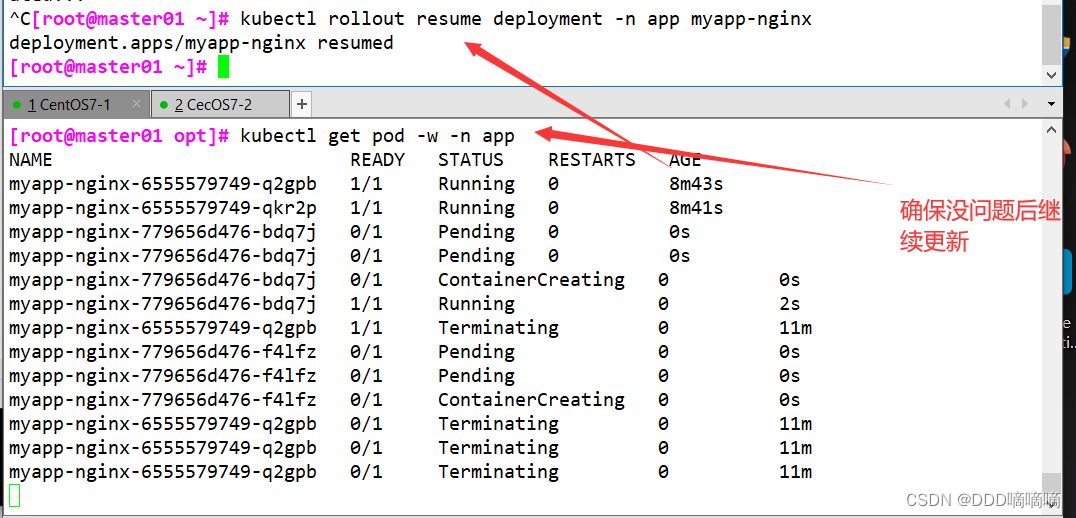

【云原生】kubectl命令的详解

目录 一、陈述式资源管理方式1.1基本查看命令查看版本信息查看资源对象简写查看集群信息配置kubectl自动补全node节点查看日志 1.3基本信息查看查看 master 节点状态查看命名空间查看default命名空间的所有资源创建命名空间app删除命名空间app在命名空间kube-public 创建副本控…...

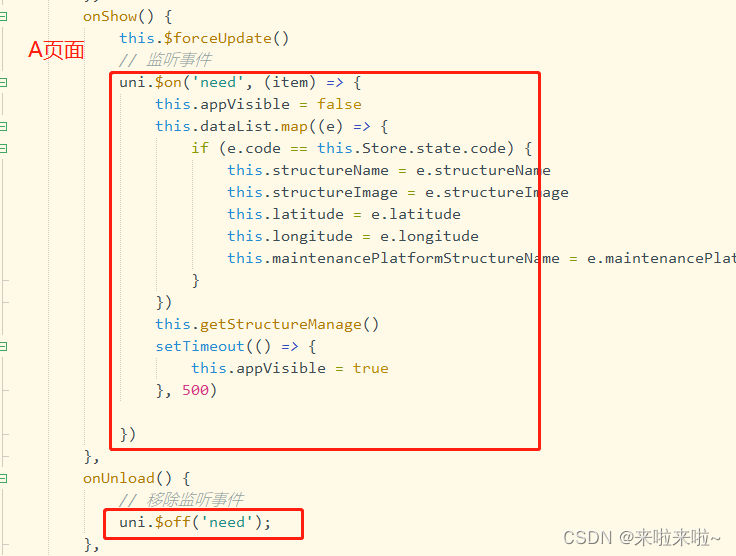

uniapp两个单页面之间进行传参

1.单页面传参:A --> B url: .....?code JSON.stringify(param), 2.单页面传参B–>Auni.$emit() uni.$on()...

uniapp运行项目到iOS基座

2022年9月,因收到苹果公司警告,目前开发者已无法在iOS真机设备使用未签名的标准基座,所以现在要运行到 IOS ,也需要进行签名。 Windows系统,HBuilderX 3.6.20以下版本,无法像MacOSX那样对标准基座进行签名…...

HTTP——九、基于HTTP的功能追加协议

HTTP 一、基于HTTP的协议二、消除HTTP瓶颈的SPDY1、HTTP的瓶颈Ajax 的解决方法Comet 的解决方法SPDY的目标 2、SPDY的设计与功能3、SPDY消除 Web 瓶颈了吗 三、使用浏览器进行全双工通信的WebSocket1、WebSocket 的设计与功能2、WebSocket协议 四、期盼已久的 HTTP/2.01、HTTP/…...

Redis 在电商秒杀场景中的应用

Redis 在电商秒杀场景中的应用 一、简介1.1 简介1.2 场景应用 二、Redis 优势与挑战2.1 优势2.2 秒杀场景的挑战 三、应用场景分析3.1 库存预热代码示例 3.2 分布式锁3.3 消息队列 四、系统设计方案4.1 架构设计4.2 技术选型4.3 数据结构设计 五、Redis 性能优化5.1 集群部署5.…...

大麦订单生成器 大麦一键生成订单

后台一键生成链接,独立后台管理 教程:修改数据库config/Conn.php 不会可以看源码里有教程 下载源码程序:https://pan.baidu.com/s/16lN3gvRIZm7pqhvVMYYecQ?pwd6zw3...

Java实现Google cloud storage 文件上传,Google oss

storage 控制台位置 创建一个bucket 点进bucket里面,权限配置里,公开访问,在互联网上公开,需要配置角色权限 新增一个访问权限 ,账号这里可以模糊搜索, 角色配置 给allUser配置俩角色就可以出现 在互联…...

适配器模式(AdapterPattern)

适配器模式 适配器模式(Adapter Pattern)是作为两个不兼容的接口之间的桥梁。这种类型的设计模式属于结构型模式,它结合了两个独立接口的功能。 优缺点 优点: 单一职责原则。你可以将接口或数据转换代码从程序主要业务逻辑中分…...

Apache Kafka Learning

目录 一、Kafka 1、Message Queue是什么? 2、Kafka 基础架构 3、Kafka安装 4、Offset自动控制 5、Acks & Retries 6、幂等性 7、事务控制 8、数据同步机制 9、Kafka-Eagle 二、Maven项目测试 1、Topic API 2、生产者&消费者 一、Kafka Kafka是…...

手把手教你用idea实现Java连接MySQL数据库

目录 1.下载MySQL 2.下载mysql 的jdbc驱动 3.将驱动jar包导入idea 4.通过Java测试数据库是否连接成功 1.下载MySQL 首先如果没有mysql的需要先下载MySQL,可以看这个教程 MYSQL安装手把手(亲测好用)_程序小象的博客-CSDN博客 2.下载mysql…...

DAB-DETR目标检测环境配置、DAB-DETR目标检测代跑训练、DAB-DETR目标检测改进创新DAB-DETR目标检测配置:Windows、Ubuntu、Centos、Macos等系统环境

DAB-DETR目标检测环境配置、 DAB-DETR目标检测代跑训练、 DAB-DETR目标检测改进创新 DAB-DETR目标检测配置:Windows、Ubuntu、Centos、Macos等系统环境,如果电脑拥有显卡,可配置GPU版本环境。 DAB-DETR目标检测代跑训练、:可支持训…...

三千年的欲望、痕迹与自感:资本批判与伦理中间件

三千年的欲望、痕迹与自感:资本批判与伦理中间件岐金兰 丙午神农---引言:被命名的与未命名的在人类文明的长河中,有一个东西从未缺席,却长期被剥夺了命名的权利。它比语言更古老,比理性更顽强,比任何社会制…...

linux source命令作用及使用场景

source 是 Linux/Unix 系统中的一个内置 Shell 命令,主要用于在当前 Shell 环境中执行脚本文件(而非启动子 Shell),从而直接影响当前环境(如变量、函数、别名等)。以下是其详细作用及使用场景: …...

2026年4月远程控制软件横评:谁才是你的“跨端神经中枢”?

转眼已至2026年,混合办公已成职场常态,AI也彻底渗透进每一寸数字土壤。曾经只负责“远程看看”的控制软件,如今已进化为融合AI辅助、超低延迟交互、全生态协同与企业级安全能力的数字生产力平台——它们不再只是工具,而是我们跨越…...

的宽带消色差超透镜Matlab核心程序探秘)

基于粒子群算法(PSO)的宽带消色差超透镜Matlab核心程序探秘

基于粒子群算法PSO宽带消色差超透镜matlab核心程序有注释便于理解代码的含义,包含FDTD仿真,文章复现案例讲解,适合学习几何相位和传输相位,消色差效果很好可以对代码进行优化在光学领域,宽带消色差超透镜是一个热门的研…...

Phi-4-mini-reasoning Chainlit插件开发:集成代码执行与结果可视化

Phi-4-mini-reasoning Chainlit插件开发:集成代码执行与结果可视化 1. 项目概述 Phi-4-mini-reasoning 是一个基于合成数据构建的轻量级开源模型,专注于高质量、密集推理的数据处理能力。作为Phi-4模型家族的一员,它特别强化了数学推理能力…...

LIF蛋白的结构特征与生物学功能研究

一、LIF蛋白的分子结构与分类白血病抑制因子属于IL-6细胞因子家族,是一种多功能的糖蛋白。该蛋白由180个氨基酸残基组成,分子量约为20至25千道尔顿,包含七个α-螺旋结构域,形成典型的上束螺旋结构。LIF蛋白的基因定位于22号染色体…...

PCB封装核心构成—焊盘,电气连接的基石

在电子设计与制造领域,PCB 封装是连接虚拟电路设计与实体元器件的关键纽带,而焊盘则是 PCB 封装中最核心、最基础的构成要素,堪称电气连接的 “基石”。没有精准设计的焊盘,元器件与电路板之间的电气连接便无从谈起,整…...

原料杂乱难管理?合并功能一键搞定

在制造行业的日常运营中,进销存管理的核心痛点往往藏在细节里——尤其是生产环节的领料流程,却常常成为拖慢效率、造成损耗的“隐形绊脚石”。很多企业在生产计划落地时,都会遇到这样的困境:同一份生产计划单中,不同成…...

4个核心预训练模型应用指南:从资源获取到问题诊断

4个核心预训练模型应用指南:从资源获取到问题诊断 【免费下载链接】so-vits-svc SoftVC VITS Singing Voice Conversion 项目地址: https://gitcode.com/gh_mirrors/so/so-vits-svc 预训练模型是so-vits-svc实现高质量语音转换的基础组件,这些经过…...