Verilog 入门

Verilog 入门

本内容来自 牛客网Verilog入门特别版

1、一个没有输入和一个输出常数1的输出的电路,输出信号为one

module top_module(one);output wire one;assign one = 1`b1;

endmodule

2、创建一个具有一个输入和一个输出的模块,其行为类似于电路上的连线。输入信号in0,输出信号out1

module wire0(in0,out1);input wire in0;output wire out1;assign out1 = in0;

endmodule

3、创建一个具有 2个输入和 3个输出的模块,使用线连接的方式:

a -> z

b -> x

b -> y

input wire a b ,output wire x y z

module top_module(a,b,x,y,z);input wire a,b;output wire x,y,z;assign a = z;assign b = x;assign c = y;

endmodule

4、输出输入信号的值的相反的值,输入in,输出out

module top_module(input in,output out

);

// assign out = !in;

assign out = ~in;

endmodule

5、创建实现 AND 门的模块,输入有三个wire,将三个信号(a b c)进行与操作,请思考在实际电路需要几个与门?请写出对应的RTL

输入:a、b、c

输出:d

module top_module( input a, input b, input c,output d

);

assign d = a & b & c;

endmodule

6、创建实现 OR和NOR 的模块,NOR 门是输出反相的 OR 门。

c 是 nor输出,d是or输出

输入:a、b

输出:c、d

module top_module( input a, input b, output c,output d

);

assign c = ~(a | b);

assign d = a | b;

endmodule

7、创建一个实现 XOR 门的模块

输入:a、b

输出:c

module top_module( input a, input b, output c

);

assign c = a ^ b;

endmodule

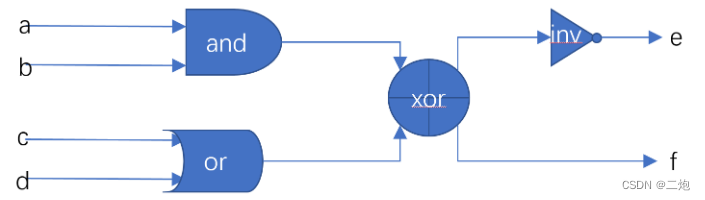

8、写出如图的rtl逻辑,限制使用最多四次assign

输入:a、b、c、d

输出:e、f

module top_module (input a,input b,input c,input d,output e,output f

);

// assign e = ~((a & b) ^ (c | d));

// assign f = (a & b) ^ (c | d);

xor(f,a&b,c|d);

assign e = ~f;

endmodule

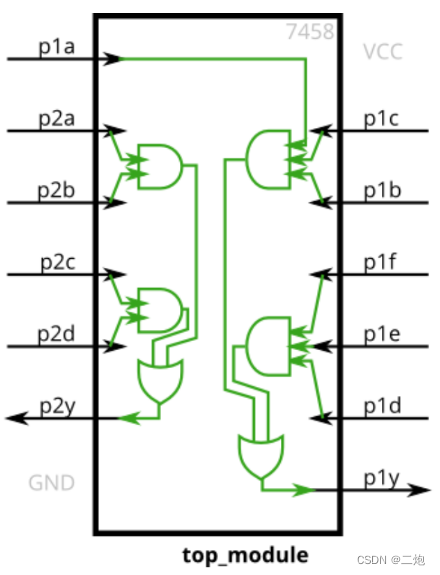

9、下图为某芯片的逻辑,请通过RTL实现它的功能

输入:p1a,,p1b,p1c,p1d,p1e,p1f,p2a,p2b,p2c,p2d

输出:p1y,p2y

module top_module ( input p1a, p1b, p1c, p1d, p1e, p1f,output p1y,input p2a, p2b, p2c, p2d,output p2y

);

// assign p1y = ((p1a & p1b & p1c) | (p1d & p1e & p1f));

// assign p2y = ((p2a & p2b) | (p2c & p2d));

or (p1y, p1c & p1b & p1a, p1f & p1e & p1d);

or (p2y, p2a & p2b, p2c & p2d);

endmodule

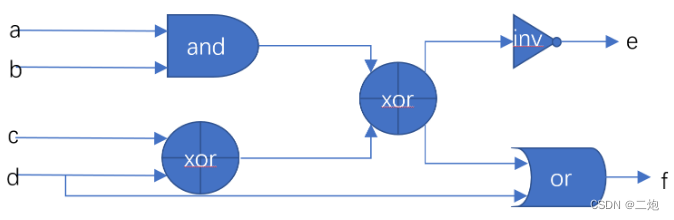

10、根据下述逻辑,给出对应的module设计

输入:a,b,c,d

输出:e,f

module top_module (input a,input b,input c,input d,output e,output f

);

assign e = ! ((a & b) ^ (c ^ d));

assign f = ((a & b) ^ (c ^ d) | d);

endmodule

11、构建一个具有一个3位输入in的信号[2:0],将其分成三个独立的输出a b c(从2到0)

输入:in

输出:a,b,c

module top_module(input [2:0] in,output a,b,c

);

assign a = in[2];

assign a = in[1];

assign a = in[0];

// 拼接字符

// assign {a,b,c} = in;

endmodule

12、一个16位信号in包含四个四位数[3:0]a [3:0]b [3:0]c [3:0]d,将它们顺序倒置为dcba输出

输入:in

输出:out

module top_module(input [15:0]in,output [15:0]out

);wire [3:0] a,b,c,d;

assign {a,b,c,d} = in;

assign out = {d,c,b,a};// genvar i;

// for (i=0; i<4; i=i+1) begin

// assign out[15 - i*4 +: 4] = in[i*4 +: 4];

// endendmodule

13、现有一个模块,输入信号为[2:0]a和[2:0]b,请输出信号的按位或[2:0]c和或信号d

输入:[2:0]a,[2:0]b

输出:[2:0]c,d

// 与: & 按位与; && 逻辑与;

// 或: | 按位或; || 逻辑或;

// 非: ~ 按位非; ! 逻辑非;

// 异或:^ 按位异或

module top_module(input [2:0] a, input [2:0] b, output [2:0] c,output d

);assign c = a | b;assign d = a || b;

endmodule

14、将一个五输入的信号分别进行的每一位进行: 全部按位与;全部按位或;全部按位异或

输入:[4:0]in

输出:out_and、out_or,、out_xor

module top_module( input [4:0] in,output out_and,output out_or,output out_xor

);assign out_and = & in[4:0];assign out_or = | in[4:0];assign out_xor = ^ in[4:0];// &in[4:0] 等同于 // in[4]&in[3]&in[2]&in[1]&in[0] |和^同理

endmodule

15、将6个输入信号串联转为四个信号输出,输入信号为[4:0]a [4:0]b [4:0]c [4:0]d [4:0]e [4:0]f,末尾增加一个宽度为两位的3,形成32位长度后,按照从前到后的顺序输出[7:0]w [7:0]x [7:0]y [7:0]z

输入:[4:0]a、[4:0]b、[4:0]c、[4:0]d、[4:0]e、[4:0]f

输出:[7:0]w、[7:0]x、[7:0]y、[7:0]z

module top_module(input [4:0] a, b, c, d, e, f,output [7:0] w, x, y, z );assign {w,x,y,z} = {a,b,c,d,e,f,2'd3};

endmodule

16、输入一个16位的信号in,将其从低位到高位输出(即反转顺序输出)为out

输入:[15:0] in

输出:[15:0] out

// 第一种reg + always语句

module top_module(input [15:0] in,output reg [15:0] out

);integer i;always @(*) beginfor(i=0; i<16; i++) beginout[i] <= in[15-i];endend

endmodule// 第二种generate for 内嵌的assign语句

// module top_module(

// input [15:0] in,

// output [15:0] out

// );

// genvar i;

// generate

// for(i=0; i<16; i=i+1) begin

// assign out[i] = in[15-i];

// end

// endgenerate

// endmodule// 疑问:

// generate for 语句内嵌的assign语句是每次循环都赋值例化一次吗?

// 这样相当于把wire类型的assign语句变量值保存下来了,最后统一输出。

// 用reg + always语句,每次循环reg值是保存的,区别是在这里吗?

17、给定四个无符号数字,找到最大值。不使用if进行判断,尽量少使用语句的情况下完成。

输入:[7:0]a b c d

输出:[7:0] max

module top_module(input [7:0] a, b, c, d,output [7:0] max

);wire [7:0] max_ab;wire [7:0] max_ab_c;assign max_ab = a>b ? a : b;assign max_ab_c = max_ab>c ? max_ab : c;assign max = max_ab_c>d ? max_ab_c : d;

endmodule

18、给定五个1bit信号(a、b、c、d 和 e),生成两种25位的数据: 一种是将信号复制五次后连接起来aaaaabbbbb…,一种是将信号连接起来复制五次成为abcdeabcde… 。比较两个25位信号,如果两个信号的同样位置的位相等,则输出1。

输入:a、b、c、d、e

输出:[24:0] out

module top_module(input a, b, c, d, e,output [24:0] out

);wire [24:0] out1, out2;assign out1 = {{5{a}},{5{b}},{5{c}},{5{d}},{5{e}}};assign out2 = {5{a,b,c,d,e}};assign out = ~(out1 ^ out2);

endmodule

19、输入5个4bit信号,根据sel的值选出对应的信号,对应关系为:0~a 1~b 2~c 3~d 4~e 其他~置零

输入:

[3:0] a b c d e

[2:0]sel

输出:

[3:0] out

module top_module( input [3:0] a, b, c, d, e, input [2:0] sel,output reg [3:0] out

);always @(*) begincase (sel)0: out = a;1: out = b;2: out = c;3: out = d;4: out = e;default: out = 4'h0;endcaseend

endmodule

20、输入一个256位信号,根据sel信号输出对应位数值,当 sel = 0 时选择 in[0],sel = 1 时选择 in[1],以此类推

输入:

[255:0] in

[7:0]sel

输出:

out

module top_module (input [255:0] in,input [7:0] sel,output reg out

);// 用此方法时,out的reg要去掉// assign out = in[sel];integer i;always @(*) beginfor(i=0; i<256; i++) begincase(sel)i: out = in[i];endcaseendend

endmodule

相关文章:

Verilog 入门

Verilog 入门 本内容来自 牛客网Verilog入门特别版 1、一个没有输入和一个输出常数1的输出的电路,输出信号为one module top_module(one);output wire one;assign one 1b1; endmodule2、创建一个具有一个输入和一个输出的模块,其行为类似于电路上的连…...

shell 简单且常用的几种

目录 一、配置环境的shell脚本 二、系统资源脚本 一、要求 二、脚本内容 三、脚本解析 四、赋权并验证 三、查看当前内存的总大小、实际使用大小、剩余大小、显示使用率百分比的脚本 一、第一种方法 二、验证 三、第二种方法 四、验证 四、查看网卡实时流量脚本 一…...

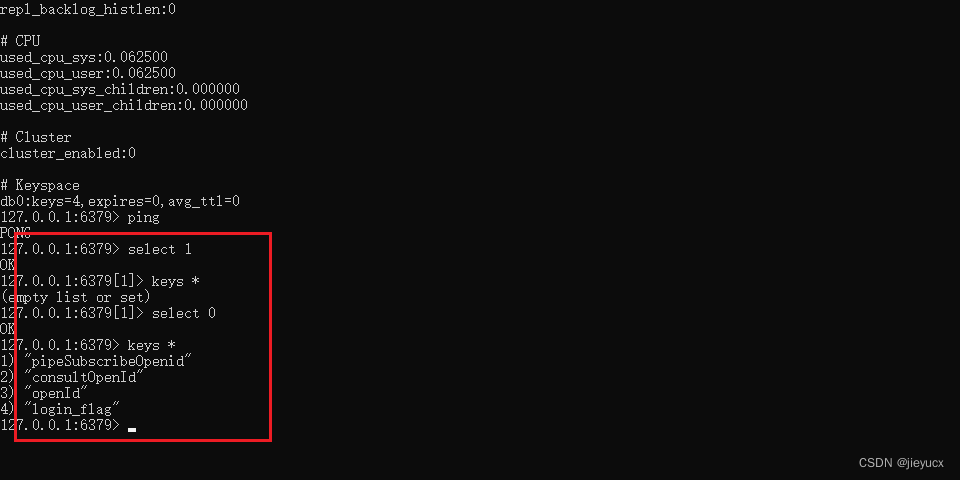

redis基本介绍以及在node中使用

文章目录 引言一、什么是redis1. redis简介2. redis的特点3. redis的应用场景 二、redis在windows下安装1. 下载安装2.验证是否安装成功3. 配置环境变量 三、redis-cli常用命令介绍1. redis-cli2. keys *3. set key value4. get key5. exists key6. del key7. info8. flushdb9.…...

React Native 文本输入基础知识

在 React Native 中提供了一个文本输入组件TextInput。此组件主要是监听键盘输入事件,并把对应的输入值显示在组件中,此组件还提供了很多功能配置参数,例如自动更正、自动大写、占位符文本和不同的键盘类型(例如数字键盘ÿ…...

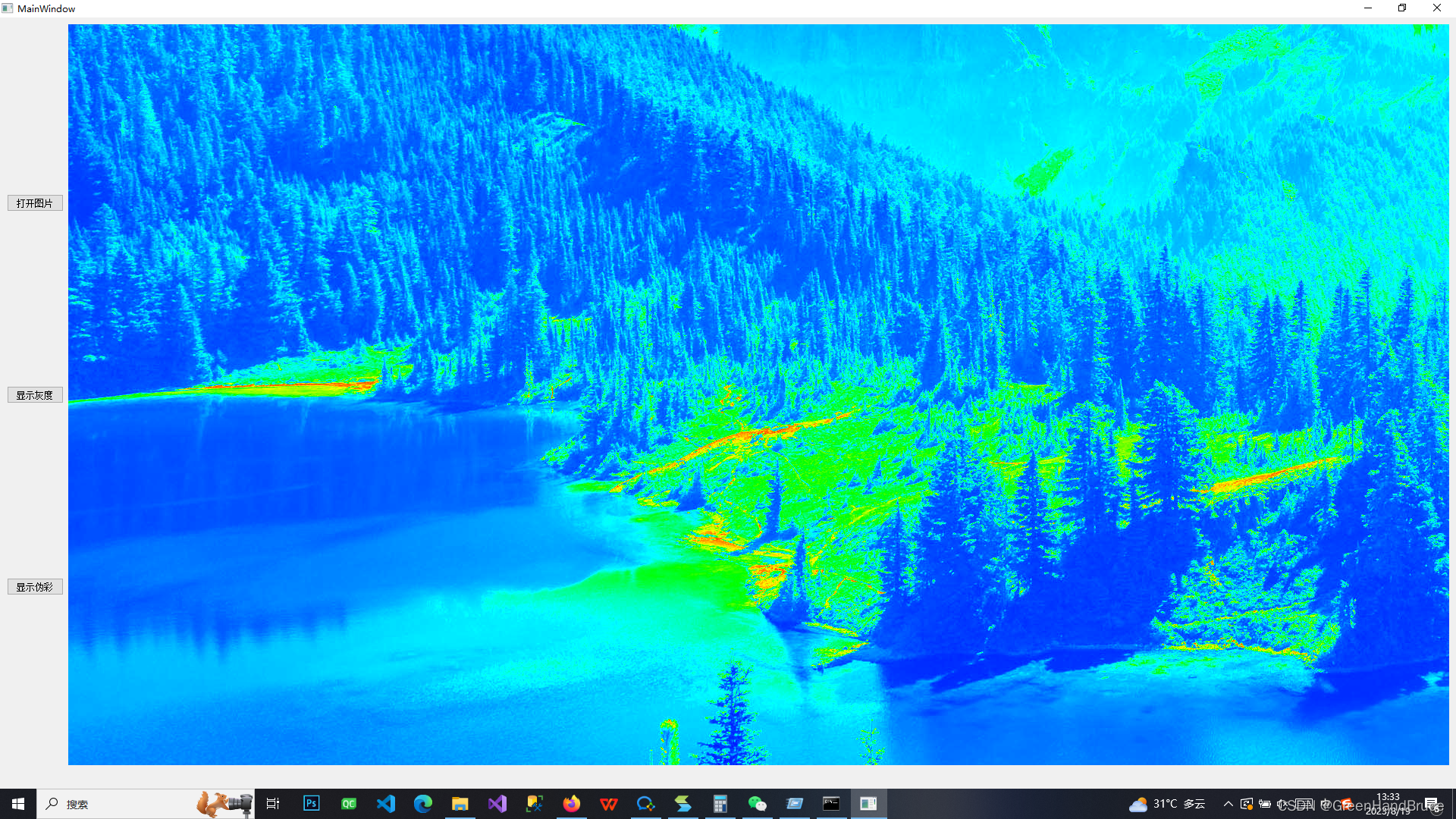

qt显示图片并转换成灰度图及伪彩图

写了个程序,可在途图片,并切换成灰度图及伪彩图显示,主要代码如下: #include "mainwindow.h" #include "ui_mainwindow.h"MainWindow::MainWindow(QWidget *parent): QMainWindow(parent), ui(new Ui::MainW…...

oj在线编程输入输出

练习地址:校招笔试真题_C工程师、golang工程师_牛客网 1.读取多行内容 输入描述: 输入包括两个正整数a,b(1 < a, b < 1000),输入数据包括多组。 输出描述: 输出ab的结果输入例子: 1 5 10 20 输出例子: 6 30imp…...

【LeetCode 算法】Add Two Integers 两整数相加-位运算

文章目录 Add Two Integers 两整数相加问题描述:分析代码递归 Tag Add Two Integers 两整数相加 问题描述: 给你两个整数 num1 和 num2,返回这两个整数的和。 − 100 < n u m 1 , n u m 2 < 100 -100 < num1, num2 < 100 −1…...

企业网络日志安全与 EventLog Analyzer

企业的网络日志安全是一项至关重要的任务。随着信息技术的迅猛发展,网络攻击和数据泄露的威胁也与日俱增。为了应对这些威胁,企业需要强大的工具来监控、分析和保护其网络日志。而ManageEngine的EventLog Analyzer正是这样一款卓越的解决方案。 网络日志…...

清风数学建模——拟合算法

拟合算法 文章目录 拟合算法概念 确定拟合曲线最小二乘法的几何解释求解最小二乘法matlab求解最小二乘法如何评价拟合的好坏计算拟合优度的代码 概念 在前面的篇幅中提到可以使用插值算法,通过给定的样本点推算出一定的曲线从而推算出一些想要的值。但存在一些问题…...

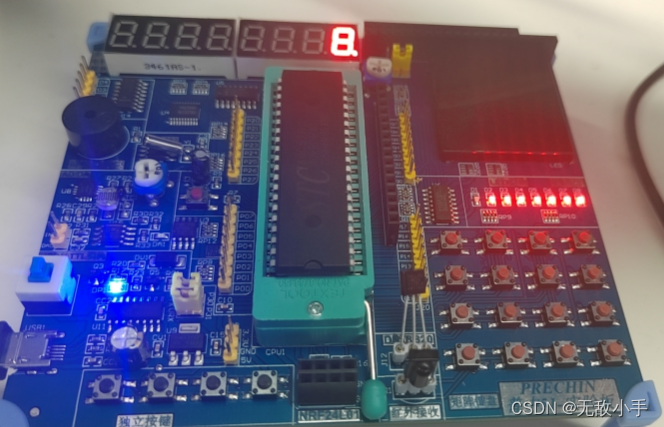

单片机 (一) 让LED灯 亮

一:硬件电路图 二:软件代码 #include "reg52.h"#define LED_PORT P2void main() {LED_PORT 0x01; // 0000 0001 D1 是灭的 } #include "reg52.h" 这个头文件的作用:包含52 系列单片机内部所有的功能寄存器 三&#…...

c++——单例模式

c单例模式 1、概念: 单例模式确保一个类只有一个实例,并提供一个全局访问点以获取该实例。这通常通过让类的构造函数为私有,以防止外部直接实例化,然后提供一个静态方法来获取实例。 2、实现方法: 实现单例模式的主…...

——FileStream、BinaryReader、MemorySream、SreamReader等之间的关系)

C# 流Stream详解(2)——FileStream、BinaryReader、MemorySream、SreamReader等之间的关系

【文件流】 电脑上的文件有很多,文本文件、音频文件、视频文件、图片文件等,这些文件会被持久化存储在磁盘上,其本质都是一堆二进制数据。 FileStream用于读取二进制文件。电脑上的所有文件,不管是文本、音频、视频还是其他任意…...

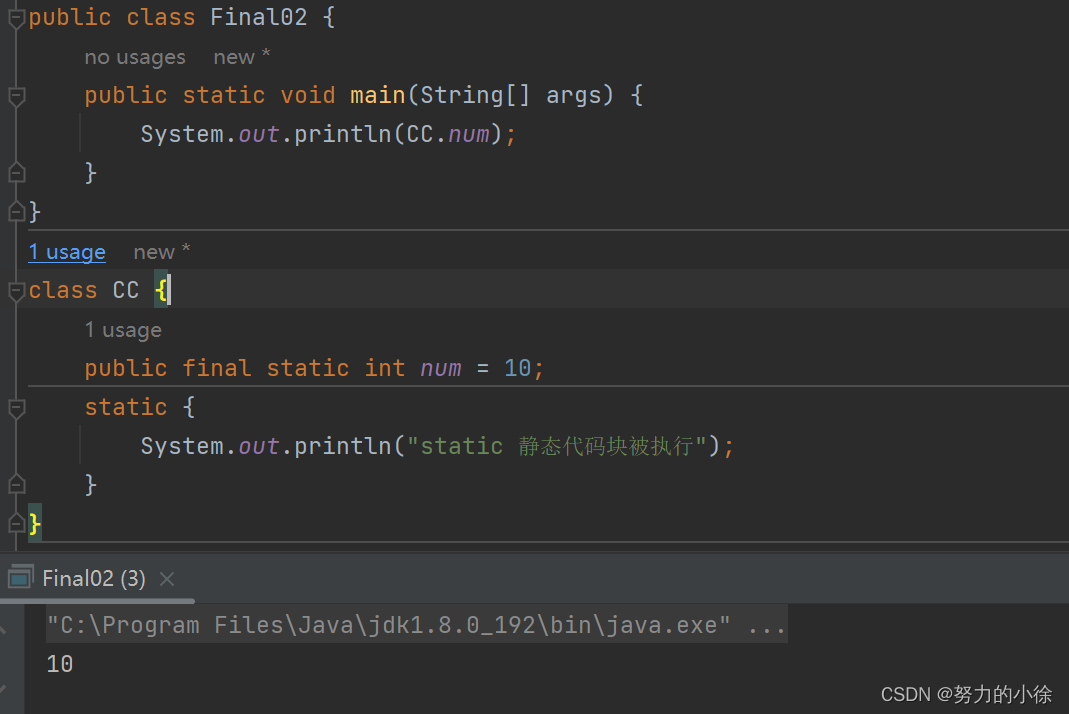

【JavaSE】详解final关键字

在Java中,final可以用来修饰类、方法和变量。final修饰类,表示该类无法被继承,并且此类的设计已被认为很完美而不需要进行修改或扩展。final修饰类中的方法,表示不可以被重写;也就是把该方法锁定了,以防止继…...

问道管理:机器人概念走势活跃,新时达涨停,拓斯达、丰立智能等大涨

机器人概念17日盘中走势活跃,到发稿,拓斯达大涨18%,昊志机电涨近16%,丰立智能涨超13%,步科股份、优德精细涨超10%,新时达涨停,天玑科技、兆龙互联、中大力德涨逾9%。 消息面上,8月16…...

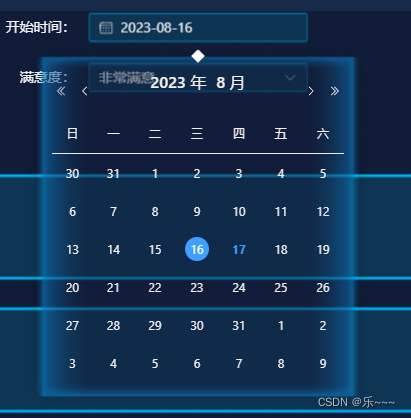

elementui 修改日期选择器el-date-picker样式

1. 案例: 2. css /* 最外层颜色 */ .el-popper.is-pure {background: url("/assets/imgList/memuBG.png") no-repeat;border: none;background-size:100% 100%}/* 日期 1.背景透明 */ .el-date-picker{background: transparent; }/* 日期 2.标题、左右图…...

自己实现 SpringMVC 底层机制 系列之-实现任务阶段 6-完成控制器方法获取参数-@RequestParam

😀前言 自己实现 SpringMVC 底层机制 系列之-实现任务阶段 6-完成控制器方法获取参数-RequestParam 🏠个人主页:尘觉主页 🧑个人简介:大家好,我是尘觉,希望我的文章可以帮助到大家,…...

数据可视化:图表绘制详解

数据可视化是一种将抽象的数字和数据转化为直观图形的技术,使数据的模式、趋势和关系一目了然。本文将详细介绍如何绘制各种类型的图表,包括柱状图、折线图、饼图、散点图和热力图等。 第一部分:图表类型和选择 1. 柱状图 柱状图是用于比较类…...

【中危】Apache Ivy<2.5.2 存在XXE漏洞 (CVE-2022-46751)

漏洞描述 Apache Ivy 是一个管理基于 ANT 项目依赖关系的开源工具,文档类型定义(DTD)是一种文档类型定义语言,它用于定义XML文档中所包含的元素以及元素之间的关系。 Apache Ivy 2.5.2之前版本中,当解析自身配置、Ivy 文件或 Apache Maven 的 POM 文件…...

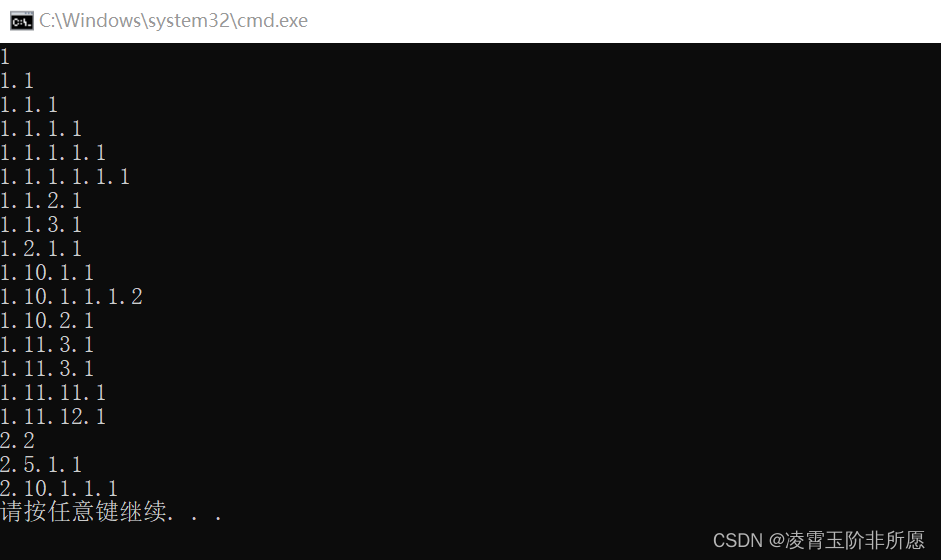

C#使用自定义的比较器对版本号(编码)字符串进行排序

给定一些数据,如下所示: “1.10.1.1.1.2”, “1.1”, “2.2”, “1.1.1.1”, “1.1.3.1”, “1.1.1”, “2.10.1.1.1”, “1.1.2.1”, “1.2.1.1”, “2.5.1.1”, “1.10.1.1”, “1.10.2.1”, “1.11.3.1”, “1.11.12.1”, “1.11.11.1”, “1.11.3.1”, “1”, “…...

AI在日常生活中的应用:从语音助手到自动驾驶

文章目录 AI的定义和发展AI在日常生活中的应用1. **智能语音助手**2. **智能家居**3. **智能医疗**4. **自动驾驶** 代码示例:使用Python实现基于机器学习的图片分类AI的未来前景结论 🎉欢迎来到AIGC人工智能专栏~探索AI在日常生活中的应用 ☆* o(≧▽≦…...

QKeyMapper:Windows平台下无需重启系统的终极按键映射解决方案

QKeyMapper:Windows平台下无需重启系统的终极按键映射解决方案 【免费下载链接】QKeyMapper [按键映射工具] QKeyMapper,Qt开发Win10&Win11可用,不修改注册表、不需重新启动系统,可立即生效和停止。支持游戏手柄映射到键鼠&am…...

为Hermes Agent配置自定义大模型提供方Taotoken的步骤

🚀 告别海外账号与网络限制!稳定直连全球优质大模型,限时半价接入中。 👉 点击领取海量免费额度 为Hermes Agent配置自定义大模型提供方Taotoken的步骤 Hermes Agent是一个流行的AI智能体开发框架,它允许开发者灵活地…...

如何5分钟完成高质量AI语音转文字:免费音频转录神器终极指南

如何5分钟完成高质量AI语音转文字:免费音频转录神器终极指南 【免费下载链接】faster-whisper-GUI faster_whisper GUI with PySide6 项目地址: https://gitcode.com/gh_mirrors/fa/faster-whisper-GUI 还在为会议录音整理而烦恼吗?还在为视频字幕…...

利用AI与间隔重复技术,在Obsidian中自动化生成学习闪卡

1. 项目概述与核心价值如果你和我一样,是个重度 Obsidian 用户,同时又对间隔重复记忆法(Spaced Repetition)情有独钟,那你肯定遇到过这个痛点:把笔记整理成闪卡(Flashcards)的过程&a…...

WindowResizer完整指南:如何强制调整任意Windows窗口大小

WindowResizer完整指南:如何强制调整任意Windows窗口大小 【免费下载链接】WindowResizer 一个可以强制调整应用程序窗口大小的工具 项目地址: https://gitcode.com/gh_mirrors/wi/WindowResizer 还在为那些无法调整大小的Windows窗口而烦恼吗?老…...

告别熬夜改稿:百考通AI如何让本科毕业论文变成一场“一次过”的通关游戏

深夜的宿舍里,电脑屏幕泛着冷光,桌面上铺满标红的查重报告、导师的修改批注,还有格式错乱的Word弹窗——这大概是许多本科生在论文终稿阶段最熟悉的场景。你也许已经熬了不知道第几个通宵,却感觉离“终稿”依然遥远。 事实上…...

告别路由器!一根网线搞定开发板调试:Windows 11 + VMware Ubuntu 22.04 直连保姆级教程

告别路由器!一根网线搞定开发板调试:Windows 11 VMware Ubuntu 22.04 直连保姆级教程 在嵌入式开发中,网络调试是最基础却最令人头疼的环节之一。想象这样的场景:深夜实验室只剩你一人,手边只有笔记本电脑、开发板和一…...

从《只狼》到你的项目:聊聊UE4布娃娃系统如何做出更‘有戏’的死亡动画

从《只狼》到你的项目:用UE4布娃娃系统打造叙事级死亡动画 在《只狼》中,当敌人从悬崖坠落时扭曲的肢体,或是Boss战败后跪地缓缓倒下的瞬间,这些死亡动画远不止是技术实现——它们成为玩家情感体验的延伸。作为UE4开发者ÿ…...

北航毕业论文LaTeX模板终极指南:三步快速搞定格式规范

北航毕业论文LaTeX模板终极指南:三步快速搞定格式规范 【免费下载链接】BUAAthesis 北航毕设论文LaTeX模板 项目地址: https://gitcode.com/gh_mirrors/bu/BUAAthesis 还在为北航毕业论文格式要求头疼吗?手动调整页眉页脚、参考文献编号、目录格式…...

揭秘Code Review 2.0革命:LLM上下文感知审查引擎如何将漏检率从17.3%压降至0.8%?

更多请点击: https://intelliparadigm.com 第一章:AI原生代码审查:2026奇点智能技术大会Code Review新范式 在2026奇点智能技术大会上,AI原生代码审查(AI-Native Code Review)正式取代传统人工规则引擎混合…...