【FPGA零基础学习之旅#11】数码管动态扫描

🎉欢迎来到FPGA专栏~数码管动态扫描

- ☆* o(≧▽≦)o *☆嗨~我是小夏与酒🍹

- ✨博客主页:小夏与酒的博客

- 🎈该系列文章专栏:FPGA学习之旅

- 文章作者技术和水平有限,如果文中出现错误,希望大家能指正🙏

- 📜 欢迎大家关注! ❤️

🎉 目录-数码管动态扫描

- 一、效果演示

- 二、电路结构

- 三、代码详解

- 四、AV4开发板演示

- 五、Spirit_V2开发板演示

一、效果演示

🥝Spirit_V2开发板按键控制数码管:

🥝AV4开发板数码管动态扫描:

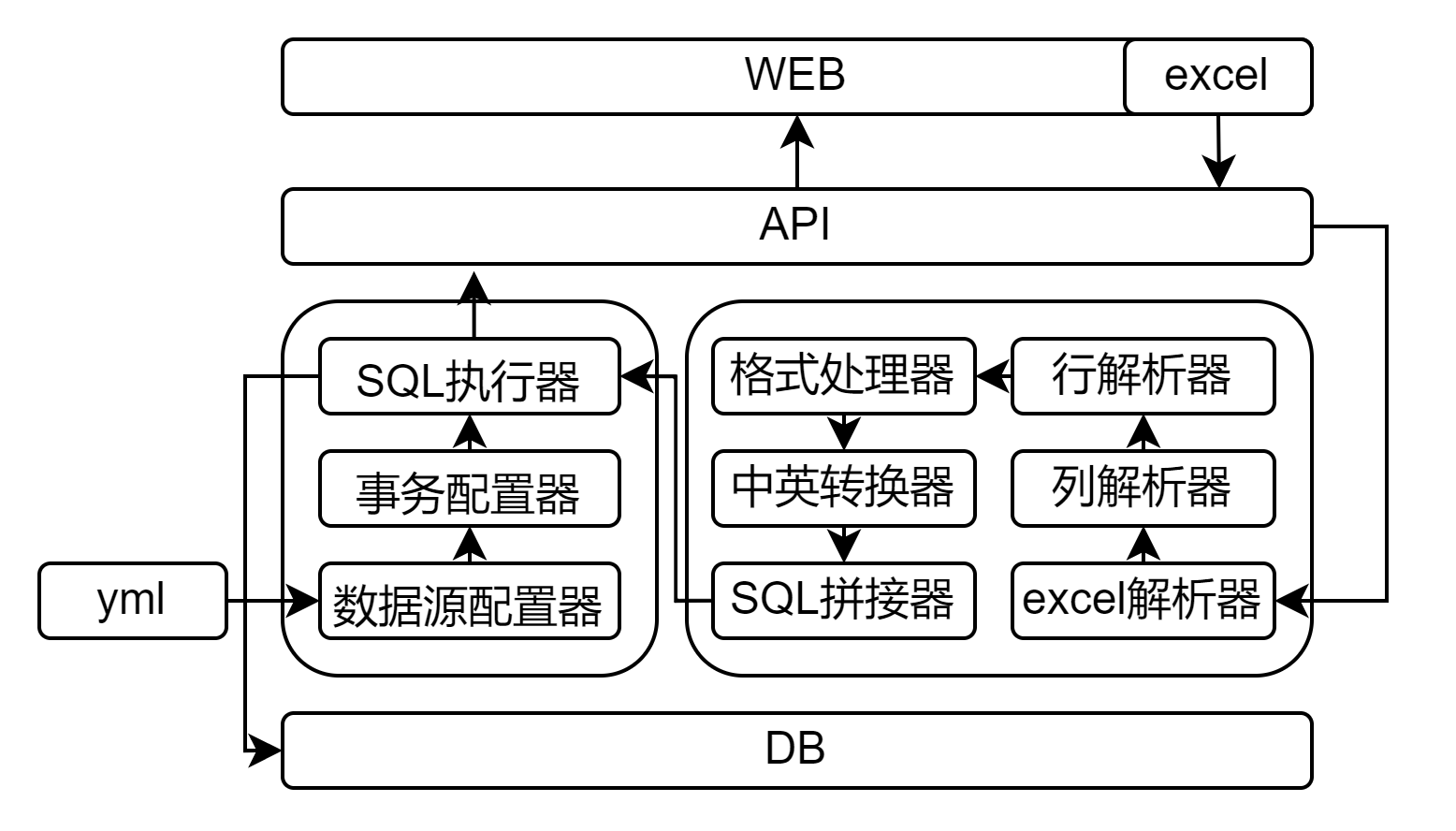

二、电路结构

上图电路结构的子模块介绍:

| 名称 | 功能描述 |

|---|---|

| divider | 分频产生1KHz的扫描时钟 |

| shift6 | 6位循环移位寄存器 |

| MUX6 | 数据输入选择 |

| MUX2 | 使能选择 |

| LUT | 数据译码器 |

由于各子模块的代码量不会特别大,因此将在一个文件中编写。

三、代码详解

先上代码:

smg_HEX.v:

module smg_HEX(input Clk, //50Minput Rst_n, //复位input En, //数码管显示使能input [23:0] disp_data, //6 × 4 = 24(6个数码管,数据格式为hex,总共输入24位)output reg [7:0] seg, //数码管段选output [5:0] sel //数码管位选(数码管选择)

);reg [5:0]sel_r;//--------<分频器>--------reg [14:0]divider_cnt;//25000-1reg clk_1K;reg [3:0]data_tmp;//待显示数据缓存//1KHz分频计数器always@(posedge Clk or negedge Rst_n)beginif(!Rst_n)divider_cnt <= 15'd0;else if(!En)divider_cnt <= 15'd0;else if(divider_cnt == 24999)divider_cnt <= 15'd0;elsedivider_cnt <= divider_cnt + 1'b1;end//1KHz扫描时钟always@(posedge Clk or negedge Rst_n)beginif(!Rst_n)clk_1K <= 1'b0;else if(divider_cnt == 24999)clk_1K <= ~clk_1K;elseclk_1K <= clk_1K;end//--------<6位循环移位寄存器>-------- always@(posedge clk_1K or negedge Rst_n)beginif(!Rst_n)sel_r <= 6'b000_001;else if(sel_r == 6'b100_000)sel_r <= 6'b000_001;elsesel_r <= sel_r << 1;end //--------<6选1多路器>-------- always@(*)begincase(sel_r)6'b00_0001:data_tmp = disp_data[3:0];6'b00_0010:data_tmp = disp_data[7:4];6'b00_0100:data_tmp = disp_data[11:8];6'b00_1000:data_tmp = disp_data[15:12];6'b01_0000:data_tmp = disp_data[19:16];6'b10_0000:data_tmp = disp_data[23:20];default:data_tmp = 4'b0000;endcaseend//--------<LUT>-------- always@(*)begincase(data_tmp)4'h0:seg = 8'hc0;4'h1:seg = 8'hf9;4'h2:seg = 8'ha4;4'h3:seg = 8'hb0;4'h4:seg = 8'h99;4'h5:seg = 8'h92;4'h6:seg = 8'h82;4'h7:seg = 8'hf8;4'h8:seg = 8'h80;4'h9:seg = 8'h90;4'ha:seg = 8'h88;4'hb:seg = 8'h83;4'hc:seg = 8'hc6;4'hd:seg = 8'ha1;4'he:seg = 8'h86;4'hf:seg = 8'h8e;endcaseend//--------<2选1多路器>-------- assign sel = (En)?(~sel_r):6'b111_111;endmodule需要注意端口列表:

module smg_HEX(input Clk, //50Minput Rst_n, //复位input En, //数码管显示使能input [23:0] disp_data, //6 × 4 = 24(6个数码管,数据格式为hex,总共输入24位)output reg [7:0] seg, //数码管段选output [5:0] sel //数码管位选(数码管选择)

);

En使能信号只有在高电平时,数码管显示。加入使能信号端口是为了低功耗设计的实现。

接下来做仿真测试:

smg_HEX_tb.v:

`timescale 1ns/1ns

`define clock_period 20module smg_HEX_tb;reg Clk; //50Mreg Rst_n;reg En; //数码管显示使能reg [23:0] disp_data;wire [7:0] seg; //数码管段选wire [5:0] sel; //数码管位选(数码管选择)smg_HEX Usmg_HEX(.Clk(Clk), //50M.Rst_n(Rst_n),.En(En), //数码管显示使能.disp_data(disp_data),.seg(seg), //数码管段选.sel(sel) //数码管位选(数码管选择));initial Clk = 1;always#(`clock_period / 2) Clk =~Clk;initial beginRst_n = 1'b0;En = 1;disp_data = 24'h123456;#(`clock_period*20);Rst_n = 1'b1;#(`clock_period*20);#20000000;disp_data = 24'h89abcd;#20000000;$stop;endendmodule仿真结果:

RTL:

四、AV4开发板演示

上述代码为数码管动态扫描的驱动代码,使用时需要添加上层模块。

AV4开发板开箱视频:【FPGA-AV4】火热售卖中!欢迎大家抢购!小月电子~(含购买链接)。

在AV4开发板上的实现,主要使用到了ISSP调试工具,ISSP的ip核创建:

🥝创建一个新的ip核:

🥝选择ISSP,选择好Verilog HDL和路径:

🥝该项目只需要用到source端口:

🥝下一步:

🥝完成:

issp.v:

// megafunction wizard: %In-System Sources and Probes%VBB%

// GENERATION: STANDARD

// VERSION: WM1.0

// MODULE: altsource_probe // ============================================================

// File Name: issp.v

// Megafunction Name(s):

// altsource_probe

//

// Simulation Library Files(s):

// altera_mf

// ============================================================

// ************************************************************

// THIS IS A WIZARD-GENERATED FILE. DO NOT EDIT THIS FILE!

//

// 13.0.0 Build 156 04/24/2013 SJ Full Version

// ************************************************************//Copyright (C) 1991-2013 Altera Corporation

//Your use of Altera Corporation's design tools, logic functions

//and other software and tools, and its AMPP partner logic

//functions, and any output files from any of the foregoing

//(including device programming or simulation files), and any

//associated documentation or information are expressly subject

//to the terms and conditions of the Altera Program License

//Subscription Agreement, Altera MegaCore Function License

//Agreement, or other applicable license agreement, including,

//without limitation, that your use is for the sole purpose of

//programming logic devices manufactured by Altera and sold by

//Altera or its authorized distributors. Please refer to the

//applicable agreement for further details.module issp (probe,source);input probe;output [23:0] source;endmodule// ============================================================

// CNX file retrieval info

// ============================================================

// Retrieval info: PRIVATE: INTENDED_DEVICE_FAMILY STRING "Cyclone IV E"

// Retrieval info: LIBRARY: altera_mf altera_mf.altera_mf_components.all

// Retrieval info: CONSTANT: ENABLE_METASTABILITY STRING "NO"

// Retrieval info: CONSTANT: INSTANCE_ID STRING "NONE"

// Retrieval info: CONSTANT: PROBE_WIDTH NUMERIC "0"

// Retrieval info: CONSTANT: SLD_AUTO_INSTANCE_INDEX STRING "YES"

// Retrieval info: CONSTANT: SLD_INSTANCE_INDEX NUMERIC "0"

// Retrieval info: CONSTANT: SOURCE_INITIAL_VALUE STRING " 0"

// Retrieval info: CONSTANT: SOURCE_WIDTH NUMERIC "24"

// Retrieval info: USED_PORT: probe 0 0 0 0 INPUT NODEFVAL "probe"

// Retrieval info: USED_PORT: source 0 0 24 0 OUTPUT NODEFVAL "source[23..0]"

// Retrieval info: CONNECT: @probe 0 0 0 0 probe 0 0 0 0

// Retrieval info: CONNECT: source 0 0 24 0 @source 0 0 24 0

// Retrieval info: GEN_FILE: TYPE_NORMAL issp.v TRUE

// Retrieval info: GEN_FILE: TYPE_NORMAL issp.inc TRUE

// Retrieval info: GEN_FILE: TYPE_NORMAL issp.cmp TRUE

// Retrieval info: GEN_FILE: TYPE_NORMAL issp.bsf TRUE

// Retrieval info: GEN_FILE: TYPE_NORMAL issp_inst.v TRUE

// Retrieval info: GEN_FILE: TYPE_NORMAL issp_bb.v TRUE

// Retrieval info: LIB_FILE: altera_mf将该ip核添加到项目文件中,并在顶层文件中例化模块:

module smg_ISSP(input Clk, //50Minput Rst_n, //复位output [7:0] seg, //数码管段选output [5:0] sel //数码管位选(数码管选择)

);wire [23:0]disp_data;smg_HEX Usmg_HEX(.Clk(Clk), //50M.Rst_n(Rst_n), //复位.En(1'b1), //数码管显示使能.disp_data(disp_data), //6 × 4 = 24(6个数码管,数据格式为hex,总共输入24位).seg(seg), //数码管段选.sel(sel) //数码管位选(数码管选择));issp Uissp(.probe(),.source(disp_data));endmodule将上述程序配置好之后,数码管显示如下:

当程序配置好之后,使用ISSP调试工具,打开步骤:

🍋在Tools中打开:

🍋未发现设备,先点击ok:

🍋在Hardware中选择对应的设备:

🍋将数据显示格式调整为hex格式:

🍋将数据改为123456:

🍋测试结果:

🍋将数据改为ABCDEF:

🍋测试结果:

五、Spirit_V2开发板演示

Spirit_V2开发板介绍:【FPGA-Spirit_V2】小精灵V2开发板初使用。

接下来在Spirit_V2开发板上实验,通过按键控制数码管亮灭,实现简单的低功耗设计:

先上RTL视图,便于理解编程思路:

按键信号经过按键消抖模块之后,有效信号进入数码管数据和使能模块,最后信号进入数码管驱动模块。

按键消抖模块的详细讲解:【FPGA零基础学习之旅#10】按键消抖模块设计与验证(一段式状态机实现)。

接下来为各模块的代码:

KeyFilter.v:

//

//模块:按键消抖模块

//key_state:输出消抖之后按键的状态

//key_flag:按键消抖结束时产生一个时钟周期的高电平脉冲

//

module KeyFilter(input Clk,input Rst_n,input key_in,output reg key_flag,output reg key_state

);//按键的四个状态localparamIDLE = 4'b0001,FILTER1 = 4'b0010,DOWN = 4'b0100,FILTER2 = 4'b1000;//状态寄存器reg [3:0] curr_st;//边沿检测输出上升沿或下降沿wire pedge;wire nedge;//计数寄存器reg [19:0]cnt;//使能计数寄存器reg en_cnt;//计数满标志信号reg cnt_full;//计数满寄存器//------<边沿检测电路的实现>------//边沿检测电路寄存器reg key_tmp0;reg key_tmp1;//边沿检测always@(posedge Clk or negedge Rst_n)beginif(!Rst_n)beginkey_tmp0 <= 1'b0;key_tmp1 <= 1'b0;endelse beginkey_tmp0 <= key_in;key_tmp1 <= key_tmp0;end endassign nedge = (!key_tmp0) & (key_tmp1);assign pedge = (key_tmp0) & (!key_tmp1);//------<状态机主程序>------ //状态机主程序always@(posedge Clk or negedge Rst_n)beginif(!Rst_n)begincurr_st <= IDLE;en_cnt <= 1'b0;key_flag <= 1'b0;key_state <= 1'b1;endelse begincase(curr_st)IDLE:beginkey_flag <= 1'b0;if(nedge)begincurr_st <= FILTER1;en_cnt <= 1'b1;endelsecurr_st <= IDLE;endFILTER1:beginif(cnt_full)beginkey_flag <= 1'b1;key_state <= 1'b0;curr_st <= DOWN;en_cnt <= 1'b0;end else if(pedge)begincurr_st <= IDLE;en_cnt <= 1'b0;endelsecurr_st <= FILTER1;endDOWN:beginkey_flag <= 1'b0;if(pedge)begincurr_st <= FILTER2;en_cnt <= 1'b1;endelsecurr_st <= DOWN;endFILTER2:beginif(cnt_full)beginkey_flag <= 1'b1;key_state <= 1'b1;curr_st <= IDLE;en_cnt <= 1'b0;end else if(nedge)begincurr_st <= DOWN;en_cnt <= 1'b0;endelsecurr_st <= FILTER2;enddefault:begincurr_st <= IDLE;en_cnt <= 1'b0;key_flag <= 1'b0;key_state <= 1'b1;endendcaseendend//------<20ms计数器>------ //20ms计数器//Clk 50_000_000Hz//一个时钟周期为20ns//需要计数20_000_000 / 20 = 1_000_000次always@(posedge Clk or negedge Rst_n)beginif(!Rst_n)cnt <= 20'd0;else if(en_cnt)cnt <= cnt + 1'b1;elsecnt <= 20'd0;endalways@(posedge Clk or negedge Rst_n)beginif(!Rst_n)cnt_full <= 1'b0;else if(cnt == 999_999)cnt_full <= 1'b1;elsecnt_full <= 1'b0;endendmoduleDataAndEn.v:

module DataAndEn(input Clk,input Rst_n,input key_flag,input key_state,output reg [23:0] disp_data,output reg En

);always@(posedge Clk or negedge Rst_n)beginif(!Rst_n)En <= 1'b0;else if(key_state == 1'b0)En <= 1'b1;else En <= 1'b0;endalways@(posedge Clk or negedge Rst_n)beginif(!Rst_n)disp_data <= 24'h0;else if(!key_state)disp_data <= 24'h89abcd;else;endendmodule数码管驱动模块的代码保持不变,接下来为顶层模块:

smg_top.v:

module smg_top(input Clk, input Rst_n, input key_in, output [7:0] seg, output [5:0] sel

);wire key_flag;wire key_state;wire En;wire [23:0] disp_data;KeyFilter UKeyFilter(.Clk(Clk),.Rst_n(Rst_n),.key_in(key_in),.key_flag(key_flag),.key_state(key_state));DataAndEn UDataAndEn(.Clk(Clk),.Rst_n(Rst_n),.key_flag(key_flag),.key_state(key_state),.disp_data(disp_data),.En(En));smg_HEX Usmg_HEX(.Clk(Clk), .Rst_n(Rst_n), .En(En), .disp_data(disp_data),.seg(seg), .sel(sel) );endmodule

🧸结尾

- ❤️ 感谢您的支持和鼓励! 😊🙏

- 📜您可能感兴趣的内容:

- 【FPGA】串口通信讲解-状态机判断数据值

- 【Python】串口通信-与FPGA、蓝牙模块实现串口通信(Python+FPGA)

- 【Arduino TinyGo】【最新】使用Go语言编写Arduino-环境搭建和点亮LED灯

- 【全网首发开源教程】【Labview机器人仿真与控制】Labview与Solidworks多路支配关系-四足爬行机器人仿真与控制

相关文章:

【FPGA零基础学习之旅#11】数码管动态扫描

🎉欢迎来到FPGA专栏~数码管动态扫描 ☆* o(≧▽≦)o *☆嗨~我是小夏与酒🍹 ✨博客主页:小夏与酒的博客 🎈该系列文章专栏:FPGA学习之旅 文章作者技术和水平有限,如果文中出现错误,希望大家能指正…...

JavaExcel:自动生成数据表并插入数据

故事背景 出于好奇,当下扫描excel读取数据进数据库 or 导出数据库数据组成excel的功能层出不穷,代码也是前篇一律,poi或者easy excel两种SDK的二次利用带来了各种封装方法。 那么为何不能直接扫描excel后根据列的属性名与行数据的属性建立S…...

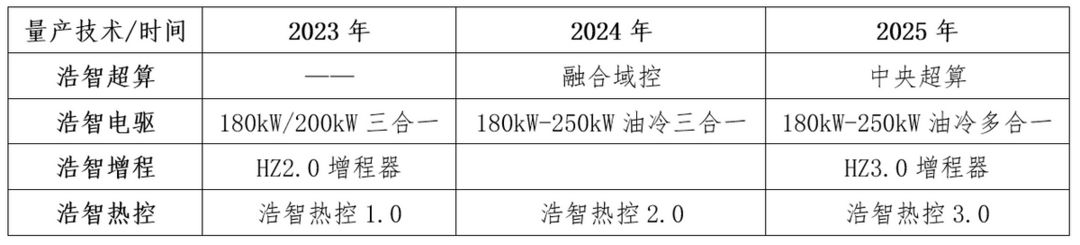

哪吒汽车“三头六臂”之「浩智电驱」

撰文 / 翟悦 编审 / 吴晰 8月21日,在哪吒汽车科技日上,哪吒汽车发布“浩智战略2025”以及浩智技术品牌2.0。根据公开信息,主编梳理了以下几点:◎浩智滑板底盘支持400V/800V双平台◎浩智电驱包括180kW 400V电驱系统和250kW 800…...

补码的反码加1为什么是原码?

搞了半个小时,终于弄懂了。 168421原码10011反码01100补码01101 学到这里了,我们肯定知道,原码补码 0,在这里也就是 19 13 32,溢出来的一位正好舍去了; 所以说,对啊,只要保证…...

光刻机是怎么做出来的

文章目录 一、光刻机的基本原理二、光刻机的制造过程三、光刻机的制造要求四、光刻机的发展趋势 光刻机是半导体工艺制造中非常重要的设备之一,它是用来制作微细结构的关键工具之一。相信大家都知道,半导体工艺中最小的制造单位是晶体管,而制…...

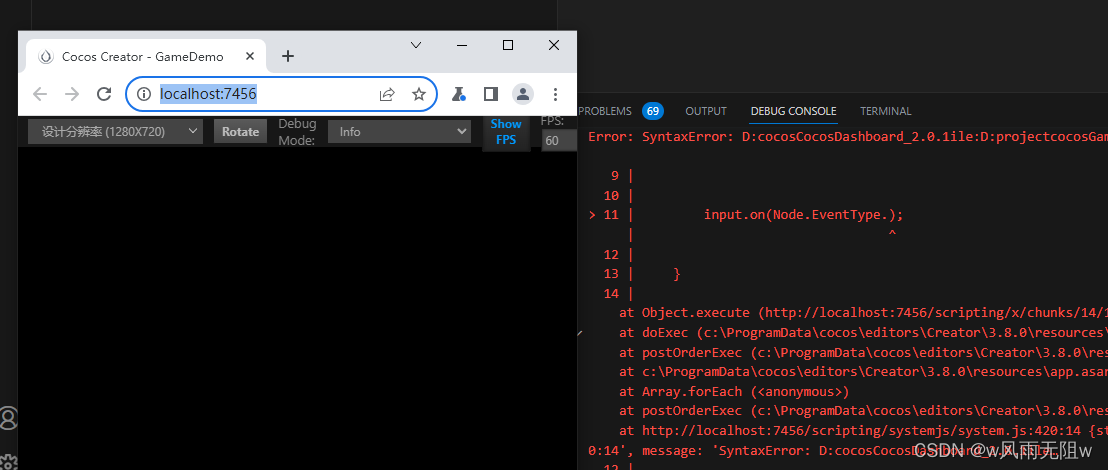

CocosCreator3.8研究笔记(二)windows环境 VS Code 编辑器的配置

一、设置文件显示和搜索过滤步骤 为了提高搜索效率以及文件列表中隐藏不需要显示的文件, VS Code 需要设置排除目录用于过滤。 比如 cocoscreator 中,编辑器运行时会自动生成一些目录:build、temp、library, 所以应该在搜索中排除…...

Rust--流程控制

循环/判断 ref: 流程控制 - Rust语言圣经(Rust Course) 判断 if condition true {// A... } else {// B... }if 语句块是表达式,所以可以为变量赋值,当然要注意的是保证返回的类型相同: fn main() {let condition true;let number if c…...

mate60的麒麟9000s和麒麟9000是一款CPU吗

答案:不是 论证: 1.在核心方便9000是1个高频A77,3个低频A77,4个A55组成的。9000S是2个高频A34核心,6个定制A78AE核心和4个A510核心并搭载超线程技术(详见新华网新华网地址) 2.GPU截然不同&am…...

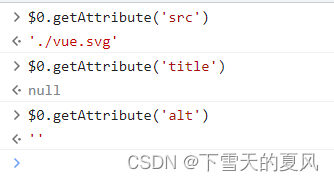

查漏补缺 - JS三 WebAPI

目录 BOMhistory DOM操作DOM1,dom.children 和 dom.childNodes 区别2,dom.remove()3,其他常用 API DOM 属性1,标准属性2,自定义属性 DOM 内容DOM样式DOM事件 JavaScript 包括 EcmaScript 和 WebAPI EcmaScript 包括 语…...

如何熟练使用vector?

🎈个人主页:🎈 :✨✨✨初阶牛✨✨✨ 🐻推荐专栏1: 🍔🍟🌯C语言初阶 🐻推荐专栏2: 🍔🍟🌯C语言进阶 🔑个人信条: 🌵知行合一 …...

gitlab-rake gitlab:backup:create 执行报错 Errno::ENOSPC: No space left on device

gitlab仓库备份执行 gitlab-rake gitlab:backup:create报错如下: 问题分析:存储备份的空间满 解决方法: 方法1:清理存放路径,删除不需要文件,释放空间。 方法2:创建一个根目录的挂载点&#x…...

【Nginx】负载均衡当其中一台服务器宕机之后

搭建一个简单的负载均衡,然后关闭其中一台再来访问,会发现我们的浏览器卡住一直转圈圈,过了很久才会显示结果。由此我们可以得出结论Nginx负载的时候如果其中一台服务挂掉了,它会把请求转发到另一个可以提供服务的机器,…...

每日一题 2511. 最多可以摧毁的敌人城堡数目

难度:简单 翻译:寻找距离最远的 1 和 -1 的组合,要求它们之间只有0 class Solution:def captureForts(self, forts: List[int]) -> int:res, t 0, -1for i, fort in enumerate(forts):if fort -1 or fort 1:if t > 0 and fort ! f…...

NLP(六十七)BERT模型训练后动态量化(PTDQ)

本文将会介绍BERT模型训练后动态量化(Post Training Dynamic Quantization,PTDQ)。 量化 在深度学习中,量化(Quantization)指的是使用更少的bit来存储原本以浮点数存储的tensor,以及使用更少的…...

机器学习和数据挖掘04-PowerTransformer与 MinMaxScaler

概念 PowerTransformer(幂变换器) PowerTransformer 是用于对数据进行幂变换(也称为Box-Cox变换)的预处理工具。幂变换可以使数据更接近正态分布,这有助于某些机器学习算法的性能提升。它支持两种常用的幂变换&#x…...

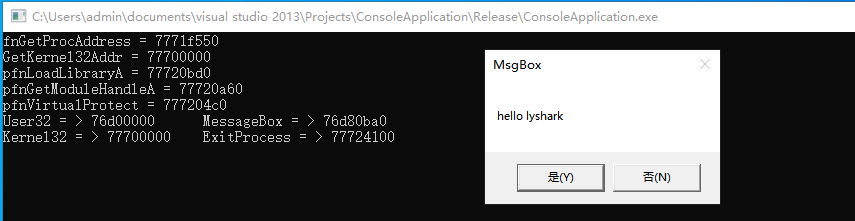

1.15 自实现GetProcAddress

在正常情况下,要想使用GetProcAddress函数,需要首先调用LoadLibraryA函数获取到kernel32.dll动态链接库的内存地址,接着在调用GetProcAddress函数时传入模块基址以及模块中函数名即可动态获取到特定函数的内存地址,但在有时这个函…...

总结ADX指标交易的好处

股神巴菲特从一个穷小子变成世界富豪,而闻名世界。anzo capital昂首资本以为这辈子再也不会和巴菲特产生任何交集,直到我看了巴菲特的发家史,才发现原来我们都使用过ADX指标盈利过,下面anzo capital昂首资本就总结一下使用ADX指…...

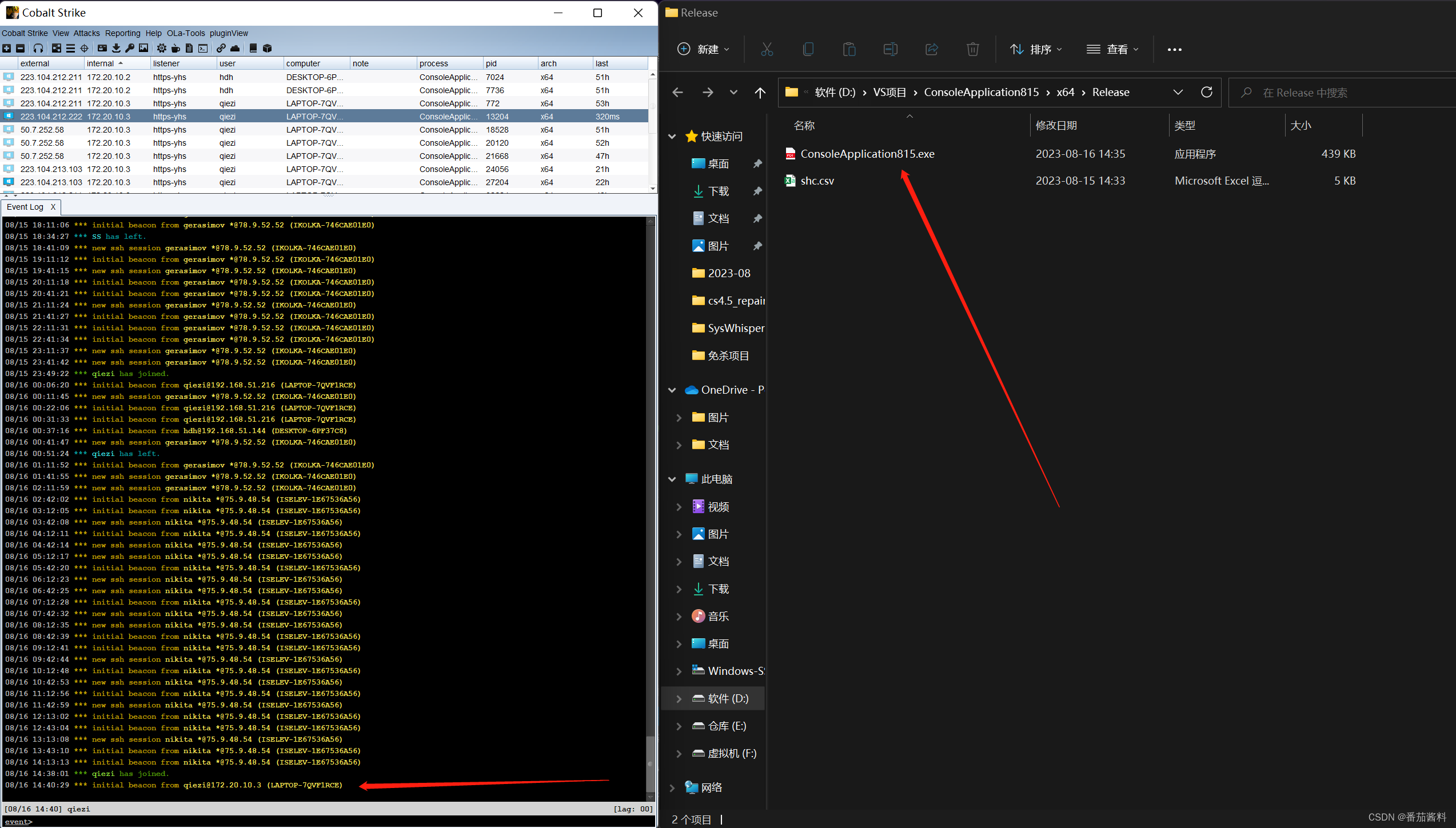

ConsoleApplication815项目(直接加载+VEH Hook Load)

上线图 ConsoleApplication815.cpp #include <iostream> #include<Windows.h> #include "detours.h" #include "detver.h" #pragma comment(lib,"detours.lib")#pragma warning(disable:4996)LPVOID Beacon_address; SIZE_T Beacon…...

事务(SQL)

事务概述 事务是一组操作的集合,他是一个不可分割的工作单位,事务会把所有的操作作为一个整体一起向西永提交或撤销操作请求。这组操作,要么全部执行成功,要么全部执行失败。 事务操作 查看/设置事务提交方式 -- 查看/设置事务…...

)

原型,原型链,继承(圣杯模式)

经典模式和圣杯模式区别 经典模式和圣杯模式都是用于解决构造函数继承和原型继承的问题,但它们在实现继承的方式上有所不同。 经典模式是通过将子类的原型对象设置为父类的实例来实现继承,然后将子类的构造函数设置为子类本身。这样子类既可以继承父类…...

GPU内存优化:深度学习检查点技术原理与实践

1. GPU内存优化:深度学习训练中的检查点技术解析在训练现代深度神经网络时,GPU内存限制往往成为制约模型规模扩展的关键瓶颈。以典型的VGG-19模型为例,当批量大小设置为256时,仅正向传播阶段就需要消耗超过20GB的显存,…...

Simulink Function子系统代码生成避坑指南:从Global配置到多输出端口的指针传递

Simulink Function子系统代码生成实战解析:从配置陷阱到高效集成 当你在Simulink中构建复杂算法时,是否遇到过这样的困境——生成的代码难以直接集成到现有系统中?传统的Simulink模型默认生成全局变量和void函数,这在需要精细控制…...

Kinovea运动视频分析:免费开源的专业动作量化工具终极指南

Kinovea运动视频分析:免费开源的专业动作量化工具终极指南 【免费下载链接】Kinovea Video solution for sport analysis. Capture, inspect, compare, annotate and measure technical performances. 项目地址: https://gitcode.com/gh_mirrors/ki/Kinovea …...

STM32 PID温度控制系统:实现±0.5°C高精度控制的完整指南

STM32 PID温度控制系统:实现0.5C高精度控制的完整指南 【免费下载链接】STM32 项目地址: https://gitcode.com/gh_mirrors/stm322/STM32 你是否曾面临温度控制系统的精度不足、响应迟缓或稳定性差的困扰?在工业自动化、实验室研究和智能家居领域…...

Pycharm更新骨架卡死C盘?罪魁祸首是torch-geometric的四个依赖库

PyCharm更新骨架卡死C盘?深入解析torch-geometric依赖库的存储陷阱 当你在PyCharm中启动一个包含torch-geometric的项目时,是否经历过C盘空间被神秘吞噬的噩梦?那个名为"Updating skeletons"的后台进程,本应是IDE的贴心…...

)

别再只用SCL当主时钟了!手把手教你用Verilog实现更可靠的I2C从机(附过采样方法)

突破传统:用Verilog构建高可靠I2C从机的过采样实战指南 在FPGA开发中,I2C从机接口的实现方式往往决定了系统的稳定性边界。当工程师们习惯性地将SCL信号直接作为时钟源时,却可能忽视了这种设计在真实硬件环境中暗藏的隐患——信号抖动引发的数…...

AI智能体技能超市:用SKILL.md标准打破AI能力壁垒

1. 项目概述:一个为AI智能体准备的“技能超市” 如果你和我一样,每天都在和各种AI编程助手打交道——Cursor、Claude Code、GitHub Copilot,那你肯定也遇到过这样的场景:想让AI帮你生成一张产品原型图,结果它告诉你“我…...

微服务测试策略-单元到集成到契约到端到端分层实战)

自动化测试(十) 微服务测试策略-单元到集成到契约到端到端分层实战

微服务测试策略:单元→集成→契约→端到端分层实战前面咱们分别聊了单元测试、接口测试、契约测试。今天把它们串起来,聊聊微服务架构下怎么设计完整的测试策略——每一层测什么、怎么测、用什么工具。一、微服务测试的"金字塔"变体 单体应用的…...

多视角时空对齐 + 跨镜轨迹融合:镜像视界打造无断点跟踪闭环

多视角时空对齐 跨镜轨迹融合:镜像视界打造无断点跟踪闭环在工业安防、智慧仓储、园区管控等全域场景智能化升级进程中,目标跟踪的连续性、精准性、全域性,始终是衡量管控体系效能的核心指标,也是传统视频监控技术难以逾越的行业…...

开源机械爪OpenClaw Max:从设计原理到实践应用全解析

1. 项目概述:从开源机械爪到OpenClaw Max的进化之路如果你和我一样,对机器人、自动化或者DIY硬件充满热情,那么“机械爪”这个组件一定不会陌生。它就像是机器人的“手”,是实现抓取、搬运、操作等复杂任务的核心执行器。市面上有…...