FPGA输出lvds信号点亮液晶屏

1 概述

该方案用于生成RGB信号,通过lvds接口驱动逻辑输出,点亮并驱动BP101WX-206液晶屏幕。

参考:下面为参考文章,内容非常详细。Xilinx LVDS Output——原语调用_vivado原语_ShareWow丶的博客![]() http://t.csdn.cn/Zy37p

http://t.csdn.cn/Zy37p

2 功能描述

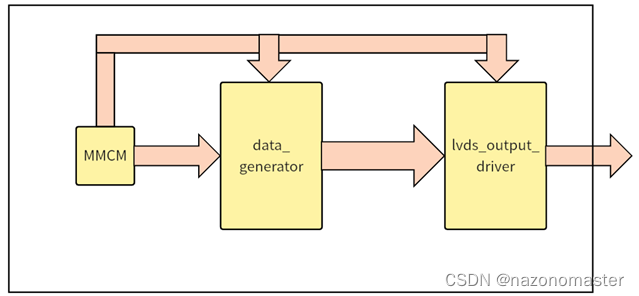

MMCM模块为时钟模块,负责将系统时钟变频与输出,产生各模块所需要的时钟;data_generator模块用于生成各种数据与信号,并传输给lvds_output_driver模块,lvds_output_driver模块将这些数据进行并串转换并按指定的lvds格式输出给液晶屏。

3 模块详细设计

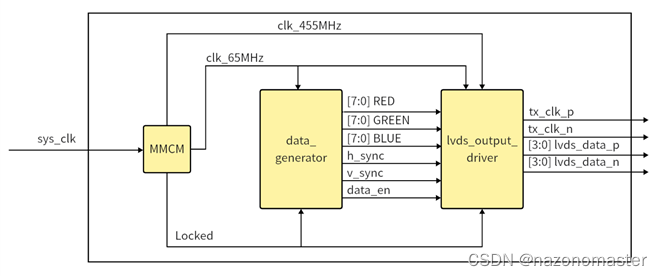

MMCM模块用于时钟的变频与输出,data_generator模块用于生成8bit RGB数据,行场同步信号(h_sync、v_sync)和数据使能信号data_en,并传输给lvds_output_driver模块,该模块将这些数据进行并串转换并按指定格式输出给液晶屏。具体详细设计图如下:

3.1 MMCM模块

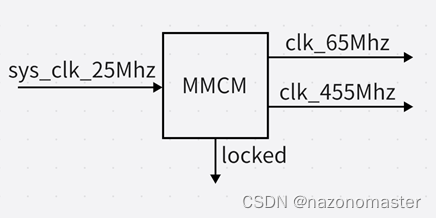

以下为时钟模块MMCM的接口示意图输出65Mhz和455Mhz的时钟,输出locked作为其他模块的复位信号,改模块采用IP核实现。

3.2 Data_generator模块设计

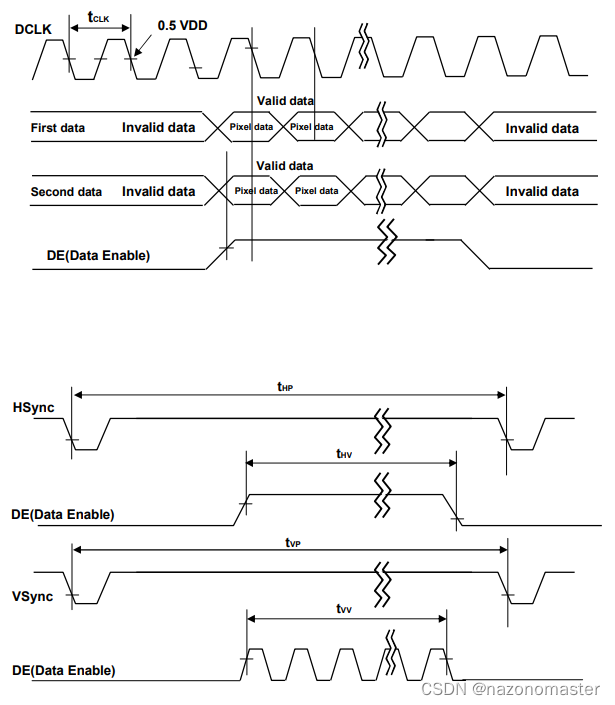

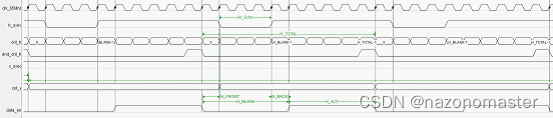

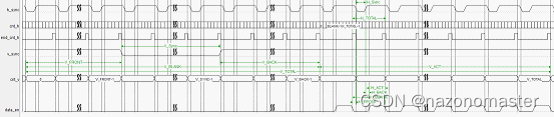

手册中给出的时序信息如下图:

依照这样的逻辑,画出大致的设计时序图:

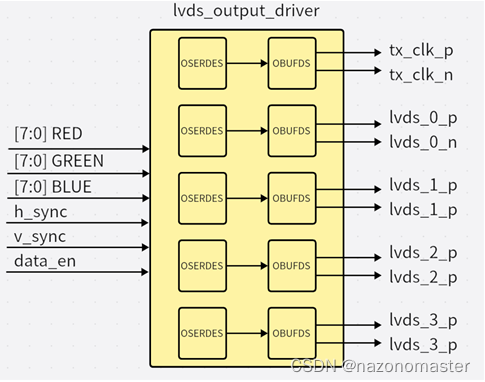

3.3 lvds_output_driver模块设计

该模块的详细设计如下:

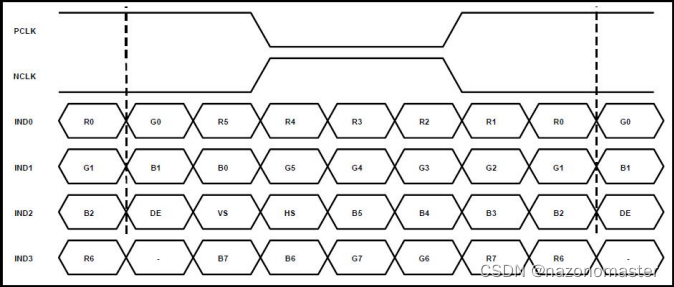

手册中的输出逻辑时序如下:

4 详细代码设计

4.1 data_generator模块详细设计

/* this module is used for data generationBP101WX1-2061280 * 800 pixel

*/

//count H_SYNC

always @(posedge i_clk_65mhz or posedge i_rst) beginif (i_rst) begincnt_h <= 0;endelse if (end_cnt_h) begincnt_h <= 0;endelse begincnt_h <= cnt_h + 1;end

end

assign end_cnt_h = cnt_h == (H_TOTAL - 1);//count V_SYNC

always @(posedge i_clk_65mhz or posedge i_rst) beginif (i_rst) begincnt_v <= 0;endelse if (end_cnt_h) beginif (end_cnt_v) begincnt_v <= 0;endelse begincnt_v <= cnt_v + 1;endend

end

assign end_cnt_v = end_cnt_h && (cnt_v == (V_TOTAL - 1));//OUTPUT h_sync v_sync DE

always @(posedge i_clk_65mhz or posedge i_rst) beginif (i_rst) begino_h_sync <= 1;endelse if ((cnt_h == H_FRONT - 1) || (cnt_h == H_FRONT + H_SYNC - 1)) begino_h_sync <= ~o_h_sync;end

endalways @(posedge i_clk_65mhz or posedge i_rst) beginif (i_rst) begino_v_sync <= 1;endelse if ((cnt_v == V_FRONT - 1 && end_cnt_h) || (cnt_v == V_FRONT + V_SYNC - 1 && end_cnt_h)) begino_v_sync <= ~o_v_sync;end

endalways @(posedge i_clk_65mhz or posedge i_rst) beginif (i_rst) begino_data_en <= 0;endelse if ((cnt_h == H_BLANK - 1 && cnt_v >= V_BLANK) || (cnt_h == H_TOTAL - 1 && cnt_v >= V_BLANK)) begino_data_en <= ~o_data_en;end

end//RGB data generation

assign x_cnt = (cnt_h >= H_BLANK)? cnt_h - (H_BLANK - 1) : 0;

assign y_cnt = (cnt_v >= V_BLANK)? cnt_v - (V_BLANK) : 0;

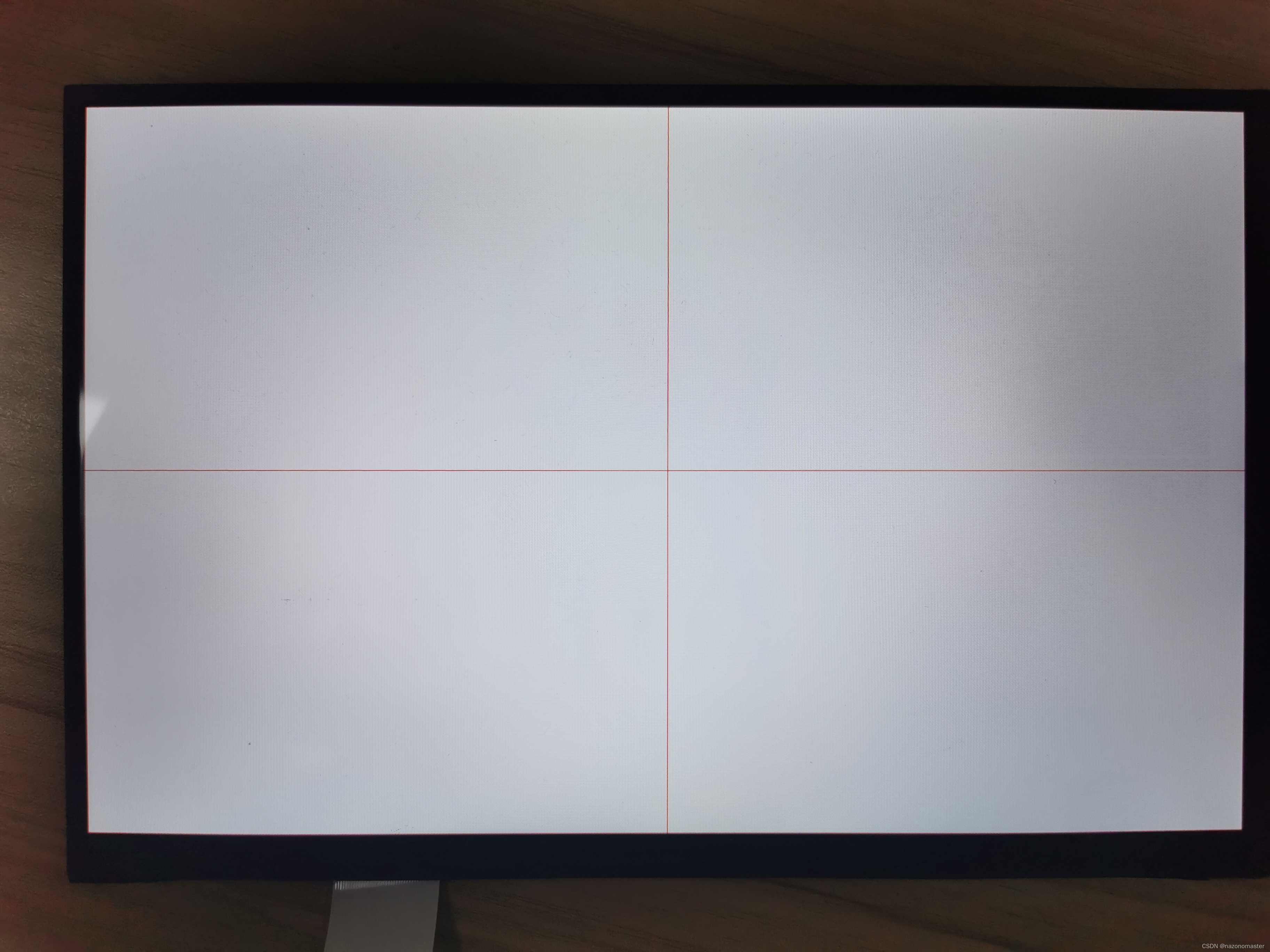

always @(posedge i_clk_65mhz or posedge i_rst) beginif (i_rst) beginrgb_data <= 0;end/* else if (x_cnt == h_vo || y_cnt == v_vo) beginrgb_data <= 24'hff_00_00;end */else if (x_cnt == 0 || x_cnt == 639 || x_cnt == 1279) beginrgb_data <= 24'hff_00_00;endelse if (y_cnt == 0 || y_cnt == 20 || y_cnt == 40) beginrgb_data <= 24'hff_00_00;endelse beginrgb_data <= 24'hffffff;end

end

assign {o_red_data, o_gre_data, o_blu_data} = rgb_data;

4.2 lvds_output_driver详细设计

第一种写法:

// CLK

OSERDESE2 #(.DATA_RATE_OQ ("SDR" ), // DDR, SDR.DATA_RATE_TQ ("SDR" ), // DDR, BUF, SDR.DATA_WIDTH (7 ), // Parallel data width (2-8,10,14).INIT_OQ (1'b0 ), // Initial value of OQ output (1'b0,1'b1).INIT_TQ (1'b0 ), // Initial value of TQ output (1'b0,1'b1).SERDES_MODE ("MASTER" ), // MASTER, SLAVE.SRVAL_OQ (1'b0 ), // OQ output value when SR is used (1'b0,1'b1).SRVAL_TQ (1'b0 ), // TQ output value when SR is used (1'b0,1'b1).TBYTE_CTL ("FALSE" ), // Enable tristate byte operation (FALSE, TRUE).TBYTE_SRC ("FALSE" ), // Tristate byte source (FALSE, TRUE).TRISTATE_WIDTH (1 ) // 3-state converter width (1,4))OSERDES_clk_inst (.OFB ( ), // 1-bit output: Feedback path for data.OQ (oserdes_clk ), // 1-bit output: Data path output// SHIFTOUT1 / SHIFTOUT2: 1-bit (each) output: Data output expansion (1-bit each).SHIFTOUT1 ( ),.SHIFTOUT2 ( ),.TBYTEOUT ( ), // 1-bit output: Byte group tristate.TFB ( ), // 1-bit output: 3-state control.TQ ( ), // 1-bit output: 3-state control.CLK (i_clk_455mhz ), // 1-bit input: High speed clock.CLKDIV (i_clk_65mhz ), // 1-bit input: Divided clock// D1 - D8: 1-bit (each) input: Parallel data inputs (1-bit each).D1 (CLK_PATTERN[0] ),.D2 (CLK_PATTERN[1] ),.D3 (CLK_PATTERN[2] ),.D4 (CLK_PATTERN[3] ),.D5 (CLK_PATTERN[4] ),.D6 (CLK_PATTERN[5] ),.D7 (CLK_PATTERN[6] ),.D8 ( ),.OCE (1'b1 ), // 1-bit input: Output data clock enable.RST (i_rst ), // 1-bit input: Reset// SHIFTIN1 / SHIFTIN2: 1-bit (each) input: Data input expansion (1-bit each).SHIFTIN1 (1'b0 ),.SHIFTIN2 (1'b0 ),// T1 - T4: 1-bit (each) input: Parallel 3-state inputs.T1 (1'b0 ),.T2 (1'b0 ),.T3 (1'b0 ),.T4 (1'b0 ),.TBYTEIN (1'b0 ), // 1-bit input: Byte group tristate.TCE (1'b0 ) // 1-bit input: 3-state clock enable);OBUFDS #(.IOSTANDARD ("DEFAULT" ), // Specify the output I/O standard.SLEW ("SLOW" ) // Specify the output slew rate) OBUFDS_CLK_inst (.O (tx_clk_p ), // Diff_p output (connect directly to top-level port).OB (tx_clk_n ), // Diff_n output (connect directly to top-level port).I (oserdes_clk ) // Buffer input );// 1 PAIR

OSERDESE2 #(.DATA_RATE_OQ ("SDR" ), // DDR, SDR.DATA_RATE_TQ ("SDR" ), // DDR, BUF, SDR.DATA_WIDTH (7 ), // Parallel data width (2-8,10,14).INIT_OQ (1'b0 ), // Initial value of OQ output (1'b0,1'b1).INIT_TQ (1'b0 ), // Initial value of TQ output (1'b0,1'b1).SERDES_MODE ("MASTER" ), // MASTER, SLAVE.SRVAL_OQ (1'b0 ), // OQ output value when SR is used (1'b0,1'b1).SRVAL_TQ (1'b0 ), // TQ output value when SR is used (1'b0,1'b1).TBYTE_CTL ("FALSE" ), // Enable tristate byte operation (FALSE, TRUE).TBYTE_SRC ("FALSE" ), // Tristate byte source (FALSE, TRUE).TRISTATE_WIDTH (1 ) // 3-state converter width (1,4))OSERDES_data_inst0 (.OFB ( ), // 1-bit output: Feedback path for data.OQ (oserdes_data[0]), // 1-bit output: Data path output// SHIFTOUT1 / SHIFTOUT2: 1-bit (each) output: Data output expansion (1-bit each).SHIFTOUT1 ( ),.SHIFTOUT2 ( ),.TBYTEOUT ( ), // 1-bit output: Byte group tristate.TFB ( ), // 1-bit output: 3-state control.TQ ( ), // 1-bit output: 3-state control.CLK (i_clk_455mhz ), // 1-bit input: High speed clock.CLKDIV (i_clk_65mhz ), // 1-bit input: Divided clock// D1 - D8: 1-bit (each) input: Parallel data inputs (1-bit each).D1 (i_gre_data[0] ),.D2 (i_red_data[5] ),.D3 (i_red_data[4] ),.D4 (i_red_data[3] ),.D5 (i_red_data[2] ),.D6 (i_red_data[1] ),.D7 (i_red_data[0] ),.D8 ( ),.OCE (1'b1 ), // 1-bit input: Output data clock enable.RST (i_rst ), // 1-bit input: Reset// SHIFTIN1 / SHIFTIN2: 1-bit (each) input: Data input expansion (1-bit each).SHIFTIN1 (1'b0 ),.SHIFTIN2 (1'b0 ),// T1 - T4: 1-bit (each) input: Parallel 3-state inputs.T1 (1'b0 ),.T2 (1'b0 ),.T3 (1'b0 ),.T4 (1'b0 ),.TBYTEIN (1'b0 ), // 1-bit input: Byte group tristate.TCE (1'b0 ) // 1-bit input: 3-state clock enable);OBUFDS #(.IOSTANDARD ("DEFAULT" ), // Specify the output I/O standard.SLEW ("SLOW" ) // Specify the output slew rate) OBUFDS_DATA_inst0 (.O (lvds_data_p[0] ), // Diff_p output (connect directly to top-level port).OB (lvds_data_n[0] ), // Diff_n output (connect directly to top-level port).I (oserdes_data[0]) // Buffer input );// 2 PAIR

OSERDESE2 #(.DATA_RATE_OQ ("SDR" ), // DDR, SDR.DATA_RATE_TQ ("SDR" ), // DDR, BUF, SDR.DATA_WIDTH (7 ), // Parallel data width (2-8,10,14).INIT_OQ (1'b0 ), // Initial value of OQ output (1'b0,1'b1).INIT_TQ (1'b0 ), // Initial value of TQ output (1'b0,1'b1).SERDES_MODE ("MASTER" ), // MASTER, SLAVE.SRVAL_OQ (1'b0 ), // OQ output value when SR is used (1'b0,1'b1).SRVAL_TQ (1'b0 ), // TQ output value when SR is used (1'b0,1'b1).TBYTE_CTL ("FALSE" ), // Enable tristate byte operation (FALSE, TRUE).TBYTE_SRC ("FALSE" ), // Tristate byte source (FALSE, TRUE).TRISTATE_WIDTH (1 ) // 3-state converter width (1,4))OSERDES_data_inst1 (.OFB ( ), // 1-bit output: Feedback path for data.OQ (oserdes_data[1]), // 1-bit output: Data path output// SHIFTOUT1 / SHIFTOUT2: 1-bit (each) output: Data output expansion (1-bit each).SHIFTOUT1 ( ),.SHIFTOUT2 ( ),.TBYTEOUT ( ), // 1-bit output: Byte group tristate.TFB ( ), // 1-bit output: 3-state control.TQ ( ), // 1-bit output: 3-state control.CLK (i_clk_455mhz ), // 1-bit input: High speed clock.CLKDIV (i_clk_65mhz ), // 1-bit input: Divided clock// D1 - D8: 1-bit (each) input: Parallel data inputs (1-bit each).D1 (i_blu_data[1] ),.D2 (i_blu_data[0] ),.D3 (i_gre_data[5] ),.D4 (i_gre_data[4] ),.D5 (i_gre_data[3] ),.D6 (i_gre_data[2] ),.D7 (i_gre_data[1] ),.D8 ( ),.OCE (1'b1 ), // 1-bit input: Output data clock enable.RST (i_rst ), // 1-bit input: Reset// SHIFTIN1 / SHIFTIN2: 1-bit (each) input: Data input expansion (1-bit each).SHIFTIN1 (1'b0 ),.SHIFTIN2 (1'b0 ),// T1 - T4: 1-bit (each) input: Parallel 3-state inputs.T1 (1'b0 ),.T2 (1'b0 ),.T3 (1'b0 ),.T4 (1'b0 ),.TBYTEIN (1'b0 ), // 1-bit input: Byte group tristate.TCE (1'b0 ) // 1-bit input: 3-state clock enable);OBUFDS #(.IOSTANDARD ("DEFAULT" ), // Specify the output I/O standard.SLEW ("SLOW" ) // Specify the output slew rate) OBUFDS_DATA_inst1 (.O (lvds_data_p[1] ), // Diff_p output (connect directly to top-level port).OB (lvds_data_n[1] ), // Diff_n output (connect directly to top-level port).I (oserdes_data[1]) // Buffer input );// 3 PAIR

OSERDESE2 #(.DATA_RATE_OQ ("SDR" ), // DDR, SDR.DATA_RATE_TQ ("SDR" ), // DDR, BUF, SDR.DATA_WIDTH (7 ), // Parallel data width (2-8,10,14).INIT_OQ (1'b0 ), // Initial value of OQ output (1'b0,1'b1).INIT_TQ (1'b0 ), // Initial value of TQ output (1'b0,1'b1).SERDES_MODE ("MASTER" ), // MASTER, SLAVE.SRVAL_OQ (1'b0 ), // OQ output value when SR is used (1'b0,1'b1).SRVAL_TQ (1'b0 ), // TQ output value when SR is used (1'b0,1'b1).TBYTE_CTL ("FALSE" ), // Enable tristate byte operation (FALSE, TRUE).TBYTE_SRC ("FALSE" ), // Tristate byte source (FALSE, TRUE).TRISTATE_WIDTH (1 ) // 3-state converter width (1,4))OSERDES_data_inst2 (.OFB ( ), // 1-bit output: Feedback path for data.OQ (oserdes_data[2]), // 1-bit output: Data path output// SHIFTOUT1 / SHIFTOUT2: 1-bit (each) output: Data output expansion (1-bit each).SHIFTOUT1 ( ),.SHIFTOUT2 ( ),.TBYTEOUT ( ), // 1-bit output: Byte group tristate.TFB ( ), // 1-bit output: 3-state control.TQ ( ), // 1-bit output: 3-state control.CLK (i_clk_455mhz ), // 1-bit input: High speed clock.CLKDIV (i_clk_65mhz ), // 1-bit input: Divided clock// D1 - D8: 1-bit (each) input: Parallel data inputs (1-bit each).D1 (i_data_en ),.D2 (i_v_sync ),.D3 (i_h_sync ),.D4 (i_blu_data[5] ),.D5 (i_blu_data[4] ),.D6 (i_blu_data[3] ),.D7 (i_blu_data[2] ),.D8 ( ),.OCE (1'b1 ), // 1-bit input: Output data clock enable.RST (i_rst ), // 1-bit input: Reset// SHIFTIN1 / SHIFTIN2: 1-bit (each) input: Data input expansion (1-bit each).SHIFTIN1 (1'b0 ),.SHIFTIN2 (1'b0 ),// T1 - T4: 1-bit (each) input: Parallel 3-state inputs.T1 (1'b0 ),.T2 (1'b0 ),.T3 (1'b0 ),.T4 (1'b0 ),.TBYTEIN (1'b0 ), // 1-bit input: Byte group tristate.TCE (1'b0 ) // 1-bit input: 3-state clock enable);OBUFDS #(.IOSTANDARD ("DEFAULT" ), // Specify the output I/O standard.SLEW ("SLOW" ) // Specify the output slew rate) OBUFDS_DATA_inst2 (.O (lvds_data_p[2] ), // Diff_p output (connect directly to top-level port).OB (lvds_data_n[2] ), // Diff_n output (connect directly to top-level port).I (oserdes_data[2]) // Buffer input );// 4 PAIR

OSERDESE2 #(.DATA_RATE_OQ ("SDR" ), // DDR, SDR.DATA_RATE_TQ ("SDR" ), // DDR, BUF, SDR.DATA_WIDTH (7 ), // Parallel data width (2-8,10,14).INIT_OQ (1'b0 ), // Initial value of OQ output (1'b0,1'b1).INIT_TQ (1'b0 ), // Initial value of TQ output (1'b0,1'b1).SERDES_MODE ("MASTER" ), // MASTER, SLAVE.SRVAL_OQ (1'b0 ), // OQ output value when SR is used (1'b0,1'b1).SRVAL_TQ (1'b0 ), // TQ output value when SR is used (1'b0,1'b1).TBYTE_CTL ("FALSE" ), // Enable tristate byte operation (FALSE, TRUE).TBYTE_SRC ("FALSE" ), // Tristate byte source (FALSE, TRUE).TRISTATE_WIDTH (1 ) // 3-state converter width (1,4))OSERDES_data_inst3 (.OFB ( ), // 1-bit output: Feedback path for data.OQ (oserdes_data[3]), // 1-bit output: Data path output// SHIFTOUT1 / SHIFTOUT2: 1-bit (each) output: Data output expansion (1-bit each).SHIFTOUT1 ( ),.SHIFTOUT2 ( ),.TBYTEOUT ( ), // 1-bit output: Byte group tristate.TFB ( ), // 1-bit output: 3-state control.TQ ( ), // 1-bit output: 3-state control.CLK (i_clk_455mhz ), // 1-bit input: High speed clock.CLKDIV (i_clk_65mhz ), // 1-bit input: Divided clock// D1 - D8: 1-bit (each) input: Parallel data inputs (1-bit each).D1 (DON_CR ),.D2 (i_blu_data[7] ),.D3 (i_blu_data[6] ),.D4 (i_gre_data[7] ),.D5 (i_gre_data[6] ),.D6 (i_red_data[7] ),.D7 (i_red_data[6] ),.D8 ( ),.OCE (1'b1 ), // 1-bit input: Output data clock enable.RST (i_rst ), // 1-bit input: Reset// SHIFTIN1 / SHIFTIN2: 1-bit (each) input: Data input expansion (1-bit each).SHIFTIN1 (1'b0 ),.SHIFTIN2 (1'b0 ),// T1 - T4: 1-bit (each) input: Parallel 3-state inputs.T1 (1'b0 ),.T2 (1'b0 ),.T3 (1'b0 ),.T4 (1'b0 ),.TBYTEIN (1'b0 ), // 1-bit input: Byte group tristate.TCE (1'b0 ) // 1-bit input: 3-state clock enable);OBUFDS #(.IOSTANDARD ("DEFAULT" ), // Specify the output I/O standard.SLEW ("SLOW" ) // Specify the output slew rate) OBUFDS_DATA_inst3 (.O (lvds_data_p[3] ), // Diff_p output (connect directly to top-level port).OB (lvds_data_n[3] ), // Diff_n output (connect directly to top-level port).I (oserdes_data[3]) // Buffer input );

第二种写法,采用generate语句:

parameter DON_CR = 0;

parameter CLK_PATTERN = 7'b11_000_11;wire [23:0] din;wire oserdes_clk ; // oserdes output clk

wire [3:0] oserdes_data; // oserdes output datagenvar i;assign din = { DON_CR, i_blu_data[7:6], i_gre_data[7:6], i_red_data[7:6], i_data_en, i_v_sync ,i_h_sync, i_blu_data[5:2], i_blu_data[1:0], i_gre_data[5:1],i_gre_data[0], i_red_data[5:0]};// CLK

OSERDESE2 #(.DATA_RATE_OQ ("SDR" ), // DDR, SDR.DATA_RATE_TQ ("SDR" ), // DDR, BUF, SDR.DATA_WIDTH (7 ), // Parallel data width (2-8,10,14).INIT_OQ (1'b0 ), // Initial value of OQ output (1'b0,1'b1).INIT_TQ (1'b0 ), // Initial value of TQ output (1'b0,1'b1).SERDES_MODE ("MASTER" ), // MASTER, SLAVE.SRVAL_OQ (1'b0 ), // OQ output value when SR is used (1'b0,1'b1).SRVAL_TQ (1'b0 ), // TQ output value when SR is used (1'b0,1'b1).TBYTE_CTL ("FALSE" ), // Enable tristate byte operation (FALSE, TRUE).TBYTE_SRC ("FALSE" ), // Tristate byte source (FALSE, TRUE).TRISTATE_WIDTH (1 ) // 3-state converter width (1,4))OSERDES_clk_inst (.OFB ( ), // 1-bit output: Feedback path for data.OQ (oserdes_clk ), // 1-bit output: Data path output// SHIFTOUT1 / SHIFTOUT2: 1-bit (each) output: Data output expansion (1-bit each).SHIFTOUT1 ( ),.SHIFTOUT2 ( ),.TBYTEOUT ( ), // 1-bit output: Byte group tristate.TFB ( ), // 1-bit output: 3-state control.TQ ( ), // 1-bit output: 3-state control.CLK (i_clk_455mhz ), // 1-bit input: High speed clock.CLKDIV (i_clk_65mhz ), // 1-bit input: Divided clock// D1 - D8: 1-bit (each) input: Parallel data inputs (1-bit each).D1 (CLK_PATTERN[0] ),.D2 (CLK_PATTERN[1] ),.D3 (CLK_PATTERN[2] ),.D4 (CLK_PATTERN[3] ),.D5 (CLK_PATTERN[4] ),.D6 (CLK_PATTERN[5] ),.D7 (CLK_PATTERN[6] ),.D8 ( ),.OCE (1'b1 ), // 1-bit input: Output data clock enable.RST (i_rst ), // 1-bit input: Reset// SHIFTIN1 / SHIFTIN2: 1-bit (each) input: Data input expansion (1-bit each).SHIFTIN1 (1'b0 ),.SHIFTIN2 (1'b0 ),// T1 - T4: 1-bit (each) input: Parallel 3-state inputs.T1 (1'b0 ),.T2 (1'b0 ),.T3 (1'b0 ),.T4 (1'b0 ),.TBYTEIN (1'b0 ), // 1-bit input: Byte group tristate.TCE (1'b0 ) // 1-bit input: 3-state clock enable);OBUFDS #(.IOSTANDARD ("DEFAULT" ), // Specify the output I/O standard.SLEW ("SLOW" ) // Specify the output slew rate) OBUFDS_CLK_inst (.O (o_tx_clk_p ), // Diff_p output (connect directly to top-level port).OB (o_tx_clk_n ), // Diff_n output (connect directly to top-level port).I (oserdes_clk ) // Buffer input );// DATA

generatefor (i = 0; i<4; i=i+1) beginOSERDESE2 #(.DATA_RATE_OQ ("SDR" ), // DDR, SDR.DATA_RATE_TQ ("SDR" ), // DDR, BUF, SDR.DATA_WIDTH (7 ), // Parallel data width (2-8,10,14).INIT_OQ (1'b0 ), // Initial value of OQ output (1'b0,1'b1).INIT_TQ (1'b0 ), // Initial value of TQ output (1'b0,1'b1).SERDES_MODE ("MASTER" ), // MASTER, SLAVE.SRVAL_OQ (1'b0 ), // OQ output value when SR is used (1'b0,1'b1).SRVAL_TQ (1'b0 ), // TQ output value when SR is used (1'b0,1'b1).TBYTE_CTL ("FALSE" ), // Enable tristate byte operation (FALSE, TRUE).TBYTE_SRC ("FALSE" ), // Tristate byte source (FALSE, TRUE).TRISTATE_WIDTH (1 ) // 3-state converter width (1,4))OSERDES_data_inst0 (.OFB ( ), // 1-bit output: Feedback path for data.OQ (oserdes_data[i]), // 1-bit output: Data path output// SHIFTOUT1 / SHIFTOUT2: 1-bit (each) output: Data output expansion (1-bit each).SHIFTOUT1 ( ),.SHIFTOUT2 ( ),.TBYTEOUT ( ), // 1-bit output: Byte group tristate.TFB ( ), // 1-bit output: 3-state control.TQ ( ), // 1-bit output: 3-state control.CLK (i_clk_455mhz ), // 1-bit input: High speed clock.CLKDIV (i_clk_65mhz ), // 1-bit input: Divided clock// D1 - D8: 1-bit (each) input: Parallel data inputs (1-bit each).D1 (i_gre_data[i*8+6]),.D2 (i_red_data[i*8+5]),.D3 (i_red_data[i*8+4]),.D4 (i_red_data[i*8+3]),.D5 (i_red_data[i*8+2]),.D6 (i_red_data[i*8+1]),.D7 (i_red_data[i*8+0]),.D8 ( ),.OCE (1'b1 ), // 1-bit input: Output data clock enable.RST (i_rst ), // 1-bit input: Reset// SHIFTIN1 / SHIFTIN2: 1-bit (each) input: Data input expansion (1-bit each).SHIFTIN1 (1'b0 ),.SHIFTIN2 (1'b0 ),// T1 - T4: 1-bit (each) input: Parallel 3-state inputs.T1 (1'b0 ),.T2 (1'b0 ),.T3 (1'b0 ),.T4 (1'b0 ),.TBYTEIN (1'b0 ), // 1-bit input: Byte group tristate.TCE (1'b0 ) // 1-bit input: 3-state clock enable);OBUFDS #(.IOSTANDARD ("DEFAULT" ), // Specify the output I/O standard.SLEW ("SLOW" ) // Specify the output slew rate) OBUFDS_DATA_inst0 (.O (o_lvds_data_p[i]), // Diff_p output (connect directly to top-level port).OB (o_lvds_data_n[i]), // Diff_n output (connect directly to top-level port).I (oserdes_data[i] ) // Buffer input );end

endgenerate

4.3 顶层设计

module a_top (input clk , // sys_clkoutput pwm_pannel , // backlightoutput o_tx_clk_p ,output o_tx_clk_n ,output [3:0] lvds_data_p ,output [3:0] lvds_data_n

);wire clk_65mhz ;

wire clk_455mhz ;wire rst ;wire [7:0] red_data ;

wire [7:0] gre_data ;

wire [7:0] blu_data ;

wire h_sync ;

wire v_sync ;

wire data_en ; assign pwm_pannel = 1;// MMCM

clk_wiz_0 u_clk_wiz_0(/* output */ .clk_out1 (clk_65mhz ),/* output */ .clk_out2 (clk_455mhz ),/* output */ .locked (rst ),/* input */ .clk_in1 (clk )

);data_generator u_data_generator(/* input */ .i_clk_65mhz (clk_65mhz ), //input 65MHz clk, period : 15.38ns/* input */ .i_rst (!rst ),/* output [7:0] */ .o_red_data (red_data ),/* output [7:0] */ .o_gre_data (gre_data ),/* output [7:0] */ .o_blu_data (blu_data ),/* output reg */ .o_h_sync (h_sync ),/* output reg */ .o_v_sync (v_sync ),/* output reg */ .o_data_en (data_en )

);lvds_output_driver u_lvds_output_driver(/* input */ .i_clk_455mhz (clk_455mhz ),/* input */ .i_clk_65mhz (clk_65mhz ),/* input */ .i_rst (!rst ),/* input [7:0] */ .i_red_data (red_data ),/* input [7:0] */ .i_gre_data (gre_data ),/* input [7:0] */ .i_blu_data (blu_data ),/* input */ .i_v_sync (v_sync ),/* input */ .i_h_sync (h_sync ),/* input */ .i_data_en (data_en ),/* output */ .tx_clk_p (o_tx_clk_p ),/* output */ .tx_clk_n (o_tx_clk_n ),/* output [3:0] */ .lvds_data_p (lvds_data_p),/* output [3:0] */ .lvds_data_n (lvds_data_n)

);endmodule //a_top5 实现效果

相关文章:

FPGA输出lvds信号点亮液晶屏

1 概述 该方案用于生成RGB信号,通过lvds接口驱动逻辑输出,点亮并驱动BP101WX-206液晶屏幕。 参考:下面为参考文章,内容非常详细。Xilinx LVDS Output——原语调用_vivado原语_ShareWow丶的博客http://t.csdn.cn/Zy37p 2 功能描述 …...

算法面试-深度学习基础面试题整理(2023.8.29开始,每天下午持续更新....)

一、无监督相关(聚类、异常检测) 1、常见的距离度量方法有哪些?写一下距离计算公式。 1)连续数据的距离计算: 闵可夫斯基距离家族: 当p 1时,为曼哈顿距离;p 2时,为欧…...

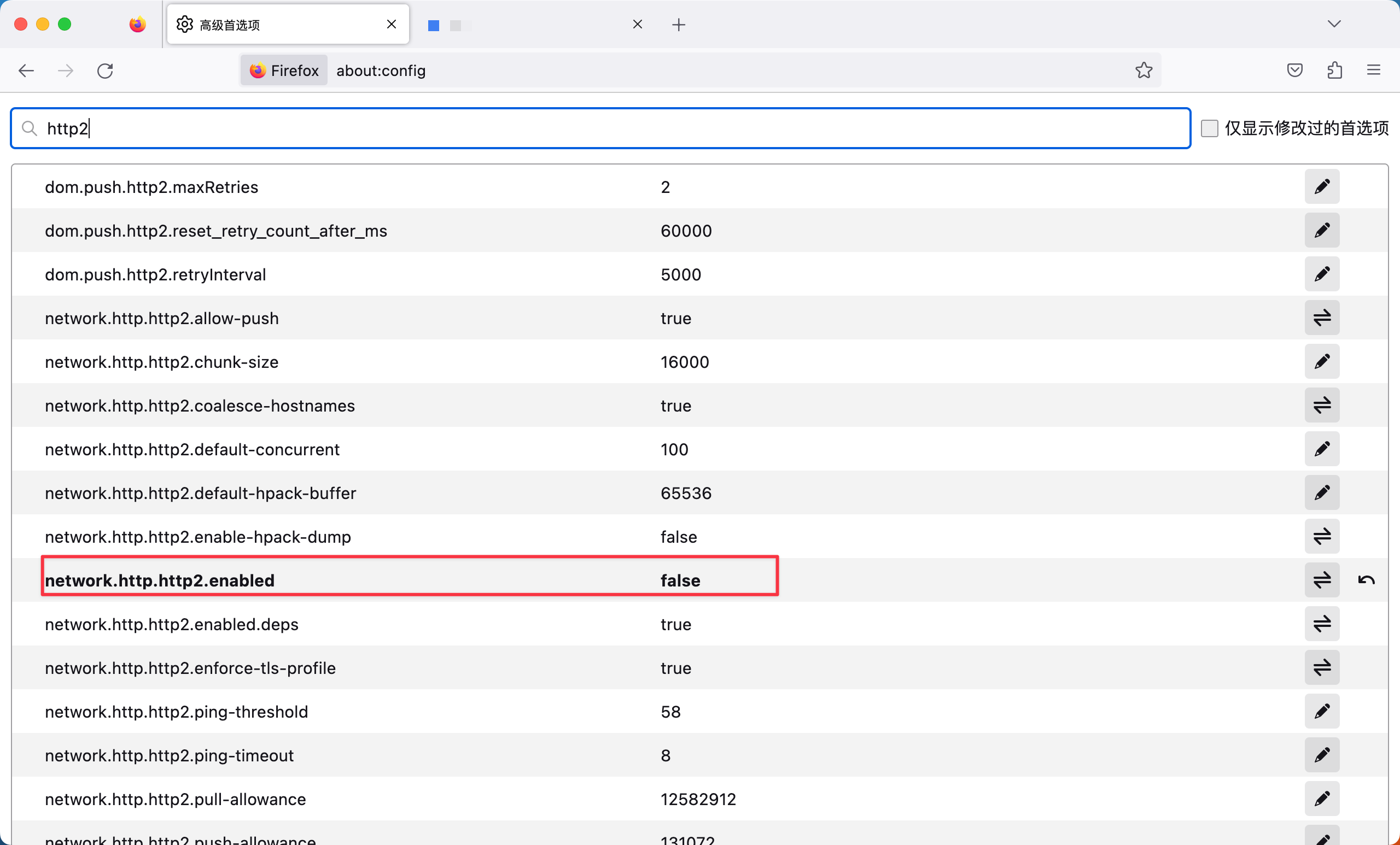

FireFox禁用HTTP2

问题 最近需要调试接口,但是,Chrome都是强制使用h2协议,即HTTP/2协议。为了排除h2协议排除对接口调用的影响,需要强制浏览器使用HTTP1协议。 解决 FireFox 设置firefox的network.http.http2.enabled为禁用,这样就禁…...

搭建HTTPS服务器

HTTPS代理服务器的作用与价值 HTTPS代理服务器可以帮助我们实现网络流量的转发和加密,提高网络安全性和隐私保护。本文将指导您从零开始搭建自己的HTTPS代理服务器,让您更自由、安全地访问互联网。 1. 准备工作:选择服务器与操作系统 a. 选…...

无人化在线静电监控系统的组成

无人化在线静电监控系统是一种用于检测和监控静电情况的系统,它可以自动地实时监测各个区域的静电水平,并在出现异常情况时发出报警信号。静电监控报警器则是该系统中的一个重要组成部分,用于接收和传达报警信号。 无人化在线静电监控系统通…...

element ui级联选择器数据处理

后端同事返回的级联选择器数据的children是childrens,而组件渲染只识别children,所以需要props自定义传入,代码如下 <el-form-item label"应用页面:" prop"appId"><el-cascader:props"{ child…...

zookeeper-3.6.4集群搭建

1、上传zookeeper安装包并解压 上传路径:/opt/software/ 解压路径:/opt/module/ 2、创建数据目录及日志目录 #数据目录:/data/zookeeper/data/ #3台机器创建存储目录: sudo mkdir -p /data/zookeeper/data#日志目录:…...

15种下载文件的方法文件下载方法汇总超大文件下载

15种下载文件的方法&文件下载方法汇总&超大文件下载 15种下载文件的方法Pentesters经常将文件上传到受感染的盒子以帮助进行权限提升,或者保持在计算机上的存在。本博客将介绍将文件从您的计算机移动到受感染系统的15种不同方法。对于那些在盒子上存在且需要…...

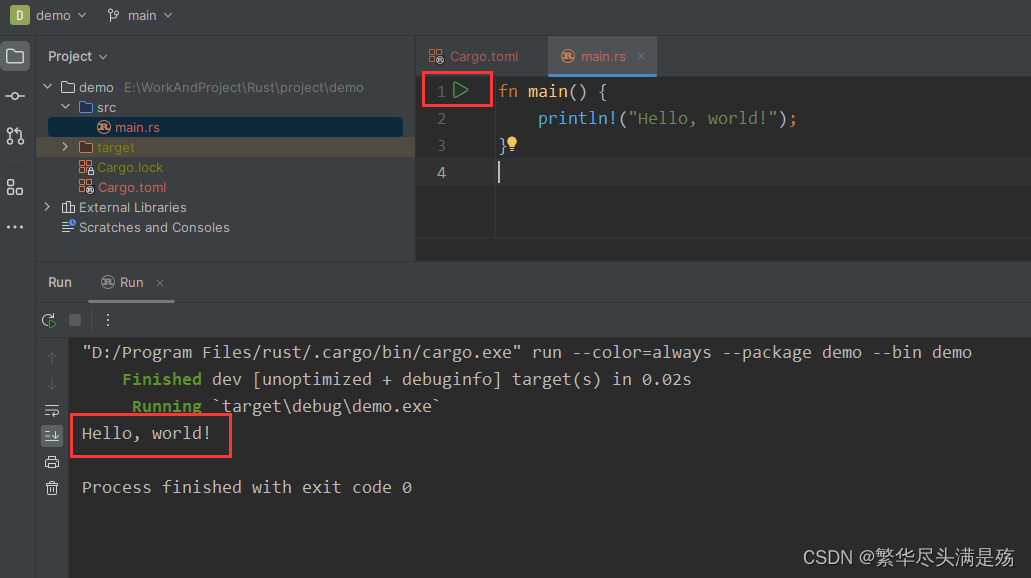

Windows安装配置Rust(附CLion配置与运行)

Windows安装配置Rust(附CLion配置与运行) 前言一、下载二、安装三、配置标准库!!!四、使用 CLion 运行 rust1、新建rust项目2、配置运行环境3、运行 前言 本文以 windows 安装为例,配置编译器为 minGW&…...

【ROS】例说mapserver静态地图参数(对照Rviz、Gazebo环境)

文章目录 例说mapserver静态地图参数1. Rviz中显示的地图2. mapserver保存地图详解3. 补充实验 例说mapserver静态地图参数 1. Rviz中显示的地图 在建图过程中,rviz会显示建图的实时情况,其输出来自于SLAM,浅蓝色区域为地图大小,…...

【RapidAI】P0 项目总览

RapidAI 项目总览 ** 内容介绍 ** Author: SWHL、omahs Github: https://github.com/RapidAI/Knowledge-QA-LLM/ CSDN Author: 脚踏实地的大梦想家 UI Demo: ** 读者须知 ** 本系列博文,主要内容为将 RapidAI 项目逐…...

初识c++

文章目录 前言一、C命名空间1、命名空间2、命名空间定义 二、第一个c程序1、c的hello world2、std命名空间的使用惯例 三、C输入&输出1、c输入&输出 四、c中缺省参数1、缺省参数概念2、缺省参数分类3、缺省参数应用 五、c中函数重载1、函数重载概念2、函数重载应用 六、…...

【面试经典150题】跳跃游戏Ⅱ

题目链接 给定一个长度为 n 的 0 索引整数数组 nums。初始位置为 nums[0]。 每个元素 nums[i] 表示从索引 i 向前跳转的最大长度。换句话说,如果你在 nums[i] 处,你可以跳转到任意 nums[i j] 处: 0 < j < nums[i]i j < n 返回到达 nums[n…...

20230831-完成登录框的按钮操作,并在登录成功后进行界面跳转

登录框的按钮操作,并在登录成功后进行界面跳转 app.cpp #include "app.h" #include <cstdio> #include <QDebug> #include <QLineEdit> #include <QLabel> #include <QPainter> #include <QString> #include <Q…...

039 - sql逻辑操作符

前提: 做两个表employee和movie,用来练习使用; 表一:employee -- 创建表employee CREATE TABLE IF NOT EXISTS employee(id INT NOT NULL AUTO_INCREMENT,first_name VARCHAR(100) NOT NULL,last_name VARCHAR(100) NOT NULL,t…...

DbLInk使用

DbLInk介绍 DbLink是一种数据库连接技术,在不同的数据库之间进行数据传输和共享。它提供了一种透明的方法,让一个数据库访问另一个数据库的数据。 DbLink的优点是可以在多个数据库间实现数据共享,并且为不同数据库间的数据访问提供了便捷的…...

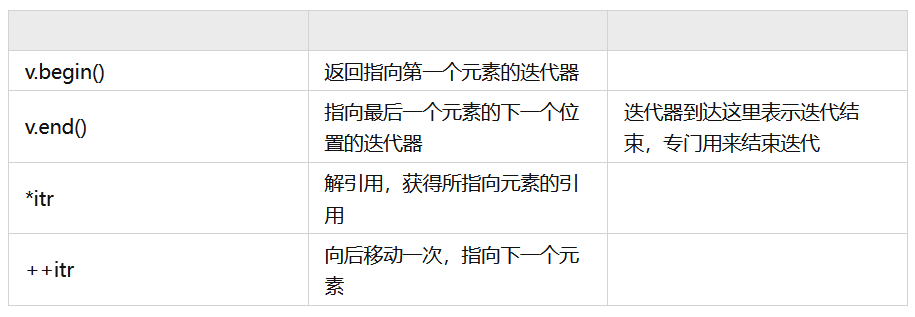

2.3 Vector 动态数组(迭代器)

C数据结构与算法 目录 本文前驱课程 1 C自学精简教程 目录(必读) 2 Vector<T> 动态数组(模板语法) 本文目标 1 熟悉迭代器设计模式; 2 实现数组的迭代器; 3 基于迭代器的容器遍历; 迭代器语法介绍 对迭…...

【ES6】Proxy的高级用法,实现一个生成各种 DOM 节点的通用函数dom

下面的例子则是利用get拦截,实现一个生成各种 DOM 节点的通用函数dom。 <body> </body><script>const dom new Proxy({}, {get(target, property) {return function(attrs {}, ...children) {const el document.createElement(property);for …...

气象站是什么设备?功能是什么?

气象站是一种用于测量和记录气象数据的设备。它通常是由各种传感器及其数据传输设备、固定设备和供电设备组成,可以测量风速、风向、温度、湿度、气压、降水量等气象要素,并将这些数据记录下来,以便进一步分析和研究。 气象站通常设置在广阔…...

227. 基本计算器 II Python

文章目录 一、题目描述示例 1示例 2示例 3 二、代码三、解题思路 一、题目描述 给你一个字符串表达式 s ,请你实现一个基本计算器来计算并返回它的值。 整数除法仅保留整数部分。 你可以假设给定的表达式总是有效的。所有中间结果将在 [-2^31, 2^31 - 1]的范围内…...

【计算机毕业设计】基于Springboot的工作流程管理系统设计与实现+万字文档

博主介绍:✌全网粉丝3W,csdn特邀作者、CSDN新星计划导师、Java领域优质创作者,掘金/华为云/阿里云/InfoQ等平台优质作者、专注于Java技术领域和学生毕业项目实战,高校老师/讲师/同行前辈交流✌ 技术范围:SpringBoot、Vue、SSM、HLMT、Jsp、PHP、Nodejs、…...

别再让API请求拖慢你的Python应用:用cachetools实现LRU缓存,性能提升实测

别再让API请求拖慢你的Python应用:用cachetools实现LRU缓存,性能提升实测 当你的Python应用开始频繁调用外部API或进行重复计算时,性能瓶颈往往悄然而至。想象一下,每次用户请求都需要等待数秒的API响应,或是相同的数据…...

)

解放双手!用STAR-CCM+的3D-CAD模块快速清理与简化仿真几何(保姆级教程)

解放双手!用STAR-CCM的3D-CAD模块快速清理与简化仿真几何(保姆级教程) 在CAE仿真领域,几何模型的质量往往直接决定仿真效率与结果可靠性。许多工程师都有过这样的经历:从设计部门拿到一个细节完美的CAD模型,…...

Tomcat 超精简总结

1. 定位轻量级 Java Web 服务器 / Servlet 容器只跑 Java 项目(jsp、servlet、springboot 内嵌)处理 动态请求,不擅长静态资源2. 核心作用解析 Servlet、JSP监听端口,接收浏览器请求调用 Java 代码执行业务返回页面 / 数据给客户端…...

)

别再死记公式了!图解STM32 PWM生成与频率测量原理(以20Hz/50%占空比方波为例)

图解STM32 PWM核心原理:从水桶模型到实战波形测量 想象一下你正在用漏水的水桶给花园浇水——水桶每滴完500毫升就自动重新加满,而你通过控制水龙头开关的时间比例来调节湿润程度。这恰恰是STM32定时器生成PWM波形的底层逻辑。对于刚接触嵌入式开发的工程…...

BBDown实用指南:高效下载B站视频的完整解决方案

BBDown实用指南:高效下载B站视频的完整解决方案 【免费下载链接】BBDown Bilibili Downloader. 一个命令行式哔哩哔哩下载器. 项目地址: https://gitcode.com/gh_mirrors/bb/BBDown BBDown是一个功能强大的命令行式哔哩哔哩视频下载器,专为技术爱…...

你还在手动切Relax Mode?3行Discord Bot脚本自动识别任务优先级并智能分流——附GitHub可运行代码

更多请点击: https://intelliparadigm.com 第一章:Relax Mode的本质与Discord任务分流的底层逻辑 Relax Mode并非一种简单的“低负载”开关,而是基于事件驱动与资源感知的动态调度策略。其核心在于将非实时性、可延迟、可重试的后台任务&…...

Unity URP专业UI模糊效果实战指南:4步实现高性能毛玻璃界面

Unity URP专业UI模糊效果实战指南:4步实现高性能毛玻璃界面 【免费下载链接】Unified-Universal-Blur UI blur (translucent) effect for Unity. 项目地址: https://gitcode.com/gh_mirrors/un/Unified-Universal-Blur 在Unity游戏开发中,UI界面的…...

)

保姆级教程:在VMware上安装BCLinux for Euler 21.10最小化系统(附镜像校验与网络配置)

虚拟化环境实战:BCLinux for Euler 21.10最小化系统部署全指南 在云计算和容器化技术盛行的今天,本地虚拟化环境仍然是开发者进行系统测试、软件验证的重要工具。BCLinux for Euler作为一款针对企业级场景优化的Linux发行版,其21.10版本在性能…...

SoM嵌入式开发实战:从选型到量产的全流程解析

1. 项目概述:为什么SoM正在重塑嵌入式开发 在嵌入式系统开发这个行当里干了十几年,我亲眼见证了开发模式从“一切从零开始”到“模块化集成”的巨大转变。早期做一个项目,从选型MCU、画原理图、设计PCB、焊接调试,再到底层驱动移植…...