龙芯GS232(MIPS 32)架构cache管理笔记

1 mips32架构

MIPS架构是一种基于精简指令集(Reduced Instruction Set Computer,RISC)的计算机处理器架构。MIPS架构由MIPS Technologies公司在1981年开发,并在1984年发布了第一款MIPS处理器。

MIPS架构的特点包括:

精简指令集:MIPS指令集简洁,指令长度固定,易于硬件实现和编译器优化。

超标量流水线:MIPS架构支持超标量技术,可以在一个时钟周期内同时执行多条指令,提高了处理器的执行效率。

延迟槽:MIPS架构的指令在执行前需要取指令、译码等操作,为了充分利用处理器的资源,MIPS架构引入了延迟槽的概念,即指令的执行结果可以延迟一个时钟周期返回,用于执行下一条指令。

加载/存储架构:MIPS架构采用加载/存储架构,只有加载/存储指令可以访问内存,其他指令需要通过寄存器传递数据。

MIPS架构被广泛应用于路由器、交换机、数字信号处理器等嵌入式系统领域,以及游戏机、工作站等领域。

1.1 高速缓存

MIPS架构是一种基于精简指令集(Reduced Instruction Set Computer,RISC)的计算机处理器架构。MIPS架构由MIPS Technologies公司在1981年开发,并在1984年发布了第一款MIPS处理器。

MIPS架构的特点包括:

精简指令集:MIPS指令集简洁,指令长度固定,易于硬件实现和编译器优化。

超标量流水线:MIPS架构支持超标量技术,可以在一个时钟周期内同时执行多条指令,提高了处理器的执行效率。

延迟槽:MIPS架构的指令在执行前需要取指令、译码等操作,为了充分利用处理器的资源,MIPS架构引入了延迟槽的概念,即指令的执行结果可以延迟一个时钟周期返回,用于执行下一条指令。

加载/存储架构:MIPS架构采用加载/存储架构,只有加载/存储指令可以访问内存,其他指令需要通过寄存器传递数据。

MIPS架构被广泛应用于路由器、交换机、数字信号处理器等嵌入式系统领域,以及游戏机、工作站等领域。

1.1.1 术语说明

写回:write back 将cache中的数据,重新写到主存中。如网络发送数据时候,先写到cache,然后执行写回操作,在发送数据。

失效:invailidate:数据清除cache,下次引用时,会从内存中重新读取。

硬件什么时候操作写回?

2 高速缓存访问流程

MIPS架构的高速缓存通常采用哈希表或相联存储器的方式进行地址映射,实现快速的地址查找,其访问流程一般如下:

地址解码:处理器从指令中获取要访问的内存地址,并将其传递给高速缓存控制器。

地址匹配:高速缓存控制器将解码后的地址与缓存中的地址进行比较,以判断是否存在缓存中。

缓存命中:如果缓存中存在该地址对应的数据,则高速缓存控制器将数据从缓存中取出,并返回给处理器,完成访问。

缓存未命中:如果缓存中不存在该地址对应的数据,则高速缓存控制器需要从主存中读取数据,并存储到缓存中,然后返回给处理器,完成访问。

在访问过程中,如果高速缓存已满,会发生缓存溢出的情况,此时高速缓存控制器需要采用替换算法来选择合适的缓存行进行替换,以确保缓存的使用效率。常见的替换算法包括LRU(最近最少使用)、FIFO(先进先出)和随机替换等。

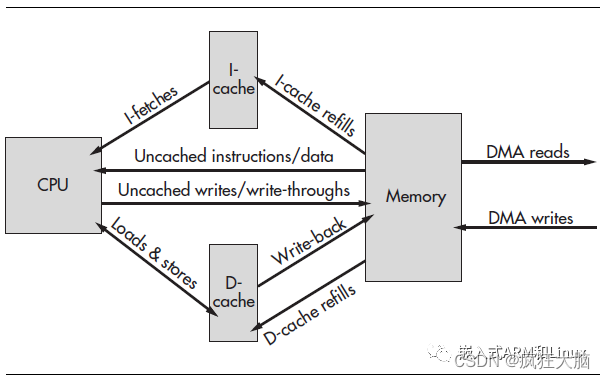

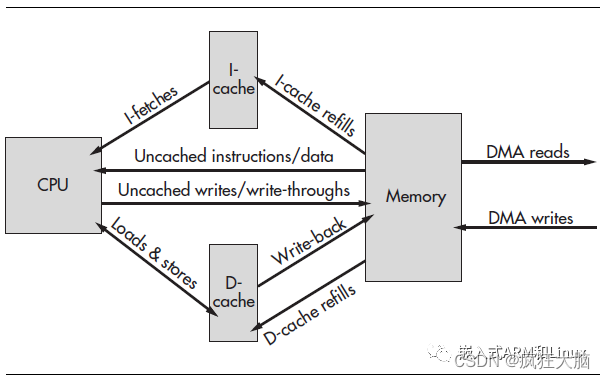

cache访问流程

Cache和内存之间的传输总是以16字节或32字节对齐的内存块作为传输单元。

即使CPU只是读取一个字节,仍然会加载这样的内存块到Cache行中。

2.1 cache和主存不一致的原因

缓存和主存不一致的原因可能有以下几种:

CPU修改数据:当CPU修改某个数据时,会先在缓存中修改,然后在某个时刻将修改后的数据写回主存。如果在这个时刻之前,DMA或其他设备读取了这个数据,就会读到缓存中的旧数据,导致缓存和主存中的数据不一致。

DMA修改数据:与CPU类似,DMA也可以访问缓存,并在某个时刻将修改后的数据写回主存。如果在这个时刻之前,CPU或其他设备访问了这个数据,就会读到缓存中的旧数据,导致缓存和主存中的数据不一致。

缓存失效:当CPU访问某个数据时,如果这个数据不在缓存中,就需要从主存中读取。如果之前的缓存中的数据已经失效,但还未被写回主存,那么就会读取到主存中的旧数据,导致缓存和主存中的数据不一致。

多级缓存:在多级缓存系统中,如果L1缓存和L2缓存中的数据不一致,就可能导致缓存和主存中的数据不一致。

因此,为了保证系统的正确性和可靠性,需要采取一些措施来管理缓存和主存之间的数据一致性,如使用缓存一致性协议、缓存写回策略等。

2.2 DMA管理中一致性问题

在MIPS架构中,在使用DMA传输数据时,需要特别注意传输的数据的一致性,以避免出现数据不一致的问题。

当DMA控制器与主存交换数据时,由于数据可能会存在缓存中,可能会出现主存和缓存中数据不一致的情况。因此,在使用DMA传输数据时,软件需要注意以下几点:

DMA传输数据前,需要将待传输数据所在的缓存行从缓存中刷出,以保证待传输的数据和主存中的数据一致。

DMA传输完成后,需要对已传输的数据所在的缓存行进行更新,以保证缓存中的数据和主存中的数据一致。

如果在传输数据期间需要修改数据所在的缓存行,需要在修改前先将该缓存行从缓存中刷出,以保证修改后的数据与主存中的数据一致。

如果使用Write-Back方式的高速缓存,还需要注意数据写回的时机,以避免在缓存中的数据被覆盖前未写回到主存而导致数据丢失。

因此,软件在使用DMA传输数据时需要考虑缓存与主存之间的数据一致性,并且需要对传输数据前后的缓存行进行正确的处理,以确保数据传输的正确性和一致性。

3 cache写回(write-back)策略

3.1 什么情况需要写回?

在MIPS32中,写回操作是指将被修改过的脏数据从缓存中写回到主存中。一般来说,MIPS32中的写回操作可以分为以下几种情况:

Cache替换策略:当缓存需要替换一部分数据时,被替换的数据会被写回到主存。

写操作:当CPU执行写操作时,将修改的数据写入缓存中,同时标记该缓存行为"dirty",表示该缓存行的数据已被修改。

缓存刷新:当执行缓存刷新指令(如CacheWriteBack)时,会将所有被修改过的缓存行写回到主存中。

缓存失效:当执行缓存失效指令(如CacheInvalidate)时,会将被失效的缓存行写回到主存中(如果该缓存行被修改过)。

需要注意的是,在执行写回操作时,需要先判断该缓存行是否已被修改过(即是否是dirty)。如果是,则需要将其写回到主存中,以确保数据的完整性。同时,为了提高效率,MIPS32中的缓存通常采用写回策略,即只有在缓存需要被替换或者被失效时才会进行写回操作,而不是每次执行写操作都进行写回操作。

3.2 如何写回

在 MIPS32 中,当一个缓存行被修改过后,它就被标记为“脏”的状态。当需要将这个脏的缓存行写回到主存中时,MIPS32 中的写回操作分为两种情况:

写回并且不需要失效(WriteBack)。当需要将一个脏的缓存行写回到主存中,但是不需要失效它,可以使用 MIPS32 汇编指令 c0(cache 操作指令),操作码为 0x08,功能号为 0x01,这个指令的格式为:c0 op, offset(base),其中 op 的取值为 0x2,表示写回操作,offset 表示缓存行的地址偏移,base 表示缓存行的起始地址。

写回并且失效(WriteBack and Invalidate)。当需要将一个脏的缓存行写回到主存中,并且失效它,可以使用 MIPS32 汇编指令 c0(cache 操作指令),操作码为 0x08,功能号为 0x05,这个指令的格式为:c0 op, offset(base),其中 op 的取值为 0x2,表示写回操作,offset表示缓存行的地址偏移,base 表示缓存行的起始地址。

需要注意的是,在进行写回操作之前,应该先使用 MIPS32 汇编指令sync 将写缓冲区中的数据刷新到主存中,以保证数据的一致性。

4 指令说明

MIPS32指令集架构中提供了一些操作cache的指令,包括:

CACHE 指令:可以用于对一个地址范围内的缓存进行控制,包括使缓存行有效/无效,清空/刷出缓存等。

ERET 指令:在从异常处理返回时,可以用于清空指令/数据缓存,确保缓存中的内容不会影响到新的指令执行。

SYNC 指令:用于同步存储器和缓存,确保数据已经被写入到缓存或存储器中。

TLBP 指令:用于查询TLB中一个特定的入口,同时可以用来强制一个缓存行失效。

TLBWI 和 TLBWR 指令:用于将一个新的页表项写入到TLB中,同时可以用来强制一个缓存行失效。

TLBWR 指令:用于将一个新的页表项写入到TLB中,同时可以用来强制一个缓存行失效。

TLBWI 指令:用于将一个新的页表项写入到TLB中,同时可以用来强制一个缓存行失效。

TLBWR 指令:用于将一个新的页表项写入到TLB中,同时可以用来强制一个缓存行失效。

4.1 sync使用

在 MIPS 指令集架构中,sync 指令用于同步缓存和内存之间的数据,确保在写缓存之后再写内存,从而保证缓存和内存中的数据一致性。它有以下两个主要的使用场景:

写缓存中的数据到内存:在写缓存中的数据后,如果需要将缓存中的数据立即写回到内存中,可以使用 sync 指令来确保写回已经完成。例如,当要将缓存中的数据同步到共享内存中时,可以使用如下指令:

sw $t0, 0($t1) # 将 $t0 寄存器中的值存入缓存中的地址 $t1

sync # 确保缓存中的数据已经写回内存

刷新指令缓存:在修改指令后,为了确保下次读取到的是最新的指令,需要将修改后的指令刷新到指令缓存中。可以使用 sync 指令来强制指令缓存刷新,如下所示:

add $t0, $t1, $t2 # 修改指令

sync # 刷新指令缓存

在软件编写时,建议在修改缓存中的数据后及时调用 sync 指令,以确保缓存和内存中的数据一致性,避免数据异常的情况发生。同时,需要注意,由于 sync 操作会影响处理器的性能,因此不要滥用 sync 指令,只在必要时使用。

4.2 cache指令说明

00000 Index Invalidate INDEX_INVALIDATE_I (I)

00001 Index WriteBack Invalidate INDEX_WRITEBACK_INV_D (D)

00101 Index Load Tag INDEX_LOAD_TAG_D (D)

01001 Index Store Tag INDEX_STORE_TAG_D (D)

10001 Hit Invalidate HIT_INVALIDATE_D (D)

10101 Hit WriteBack Invalidate HIT_WRITEBACK_INV_D (D)

// R10000-specific cacheops

11001 Index Load Data INDEX_LOAD_DATA_D (D)

11101 Index Store Data INDEX_STORE_DATA_D (D)

00011 Index WriteBack Invalidate INDEX_WRITEBACK_INV_S(/D) (S)

00111 Index Load Tag INDEX_LOAD_TAG_S(/D) (S)

01011 Index Store Tag INDEX_STORE_TAG_S(/D) (S)

10011 Hit Invalidate HIT_INVALIDATE_S(/D) (S)

10111 Hit WriteBack Invalidate HIT_WRITEBACK_INV_S(/D) (S)

11011 Index Load Data INDEX_LOAD_DATA_S (S)

11111 Index Store Data INDEX_STORE_DATA_S (S)

1.3.1 Index WriteBack Invalidate (S)

Index WriteBack Invalidate(IWBINV)是一种MIPS架构中的缓存指令,用于将指定索引处的缓存行从缓存中写回到主存并使其无效。

具体来说,这条指令会按照给定的索引,在缓存中查找与之对应的缓存行,并将其中被修改过的数据写回到主存中。同时,该指令还会将缓存行置为无效状态,这意味着缓存中的数据不再可用,后续访问该地址时需要从主存中读取数据。

IWBINV指令一般用于保证缓存和主存数据的一致性。在DMA发送数据前,需要先将待发送数据所在的缓存行从缓存中刷出并使其无效,以确保DMA发送的数据与主存中的数据保持一致。类似地,在对于DMA接收数据后,需要使用IWBINV指令将缓存行设置为有效,以保证后续访问该地址时能够从缓存中获取最新数据。

下面是一个IWBINV指令的示例,假设需要将索引为i的缓存行写回到主存并使其无效:

.set noreorder.set noat# 将索引i左移5位并加上标志位0x18,得到IWBINV指令的操作码li $at, ((i << 5) | 0x18)# 将操作码存入C0协处理器的16号寄存器mtc0 $at, $16# 执行IWBINV指令cache 0x1, 0($index)

在上面的示例中,$index是一个指向索引为i的缓存行的指针。首先将操作码通过mtc0指令写入C0协处理器的寄存器中,然后使用cache指令执行IWBINV操作。这样就可以将该缓存行从缓存中写回到主存并使其无效。

1.3.2 Hit WriteBack Invalidate (S)

"Hit WriteBack Invalidate"是一种缓存写回策略,在缓存一致性协议中常用。当CPU写入一个缓存行时,如果该缓存行已经在缓存中,并且是修改过的(dirty),则执行该策略:将该缓存行写回到主存,同时将该缓存行标记为无效(invalid)。这样,在之后的访问中,如果发现缓存中的数据被修改过,就会重新从主存中读取最新的数据,以保证数据的一致性。

需要注意的是,如果该缓存行没有被修改过,那么不需要写回到主存,而是可以直接将该缓存行标记为无效。这样可以避免不必要的主存访问,提高访问效率。

(待续)

相关文章:

龙芯GS232(MIPS 32)架构cache管理笔记

1 mips32架构 MIPS架构是一种基于精简指令集(Reduced Instruction Set Computer,RISC)的计算机处理器架构。MIPS架构由MIPS Technologies公司在1981年开发,并在1984年发布了第一款MIPS处理器。 MIPS架构的特点包括: …...

js去重

<script>let arr [{ id: 0, name: "张三" },{ id: 1, name: "李四" },{ id: 2, name: "王五" },{ id: 3, name: "赵六" },{ id: 1, name: "孙七" },{ id: 2, name: "周八" },{ id: 2, name: "吴九&qu…...

小白都能看懂的C语言入门教程

文章目录C语言入门教程1. 第一个C语言程序HelloWorld2. C语言的数据类型3. 常量变量的使用4. 自定义标识符#define5. 枚举的使用6. 字符串和转义字符7. 判断和循环8. 函数9. 数组的使用10. 操作符的使用11. 结构体12. 指针的简单使用C语言入门教程 1. 第一个C语言程序HelloWor…...

leetcode 21~30 学习经历

leetcode 21~30 学习经历21. 合并两个有序链表22. 括号生成23. 合并K个升序链表24. 两两交换链表中的节点25. K 个一组翻转链表26. 删除有序数组中的重复项27. 移除元素28. 找出字符串中第一个匹配项的下标29. 两数相除30. 串联所有单词的子串小结21. 合并两个有序链表 将两个升…...

让ArcMap变得更加强大,用python执行地理处理以及编写自定义脚本工具箱

文章目录一、用python执行地理处理工具1.1 例:乘以0.00011.2 例:裁剪栅格1.3 哪里查看调用某工具的代码?二、用python批量执行地理处理工具2.1 必需的python语法知识for循环语句缩进的使用注释的使用2.2 一个批处理栅格的代码模板三、创建自定…...

SAP 项目实施阶段全过程

在sap实施项目的周期和步骤上,根据各公司对业务的理解不同,也被划分为各个阶段,但其中由普华永道提出的分七步走,个人觉得对刚进入这一行业的人很有帮助,接下来一起分享和讨论下: sap实施项目生命周期&…...

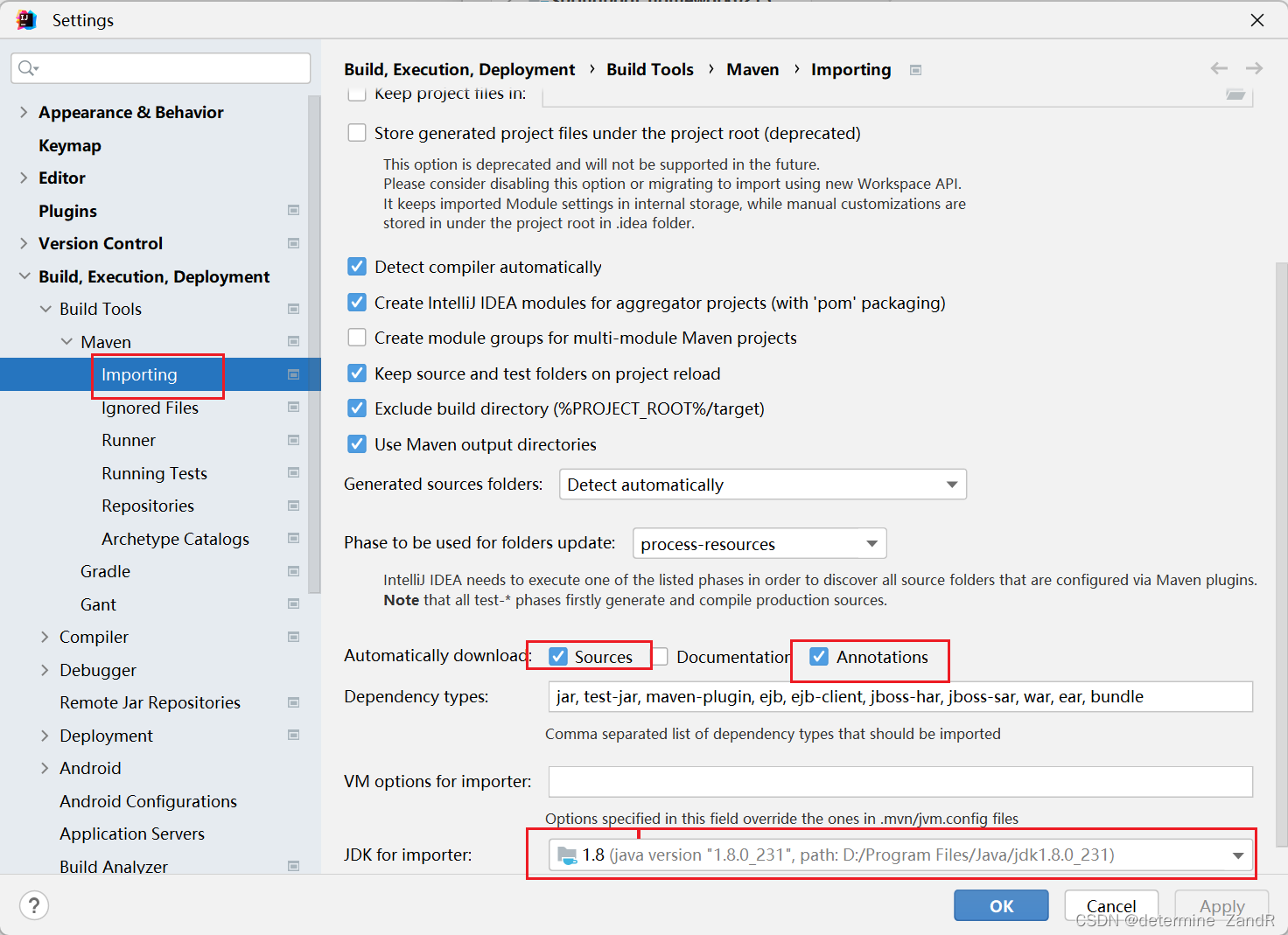

idea中的Maven导包失败问题解决总结

idea中的Maven导包失败问题解决总结 先确定idea和Maven 的配置文件settings 没有问题 找到我们本地的maven仓库,默认的maven仓库路径是在\C:\Users\用户名.m2下 有两个文件夹,repositotry是放具体jar包的,根据报错包的名,找对应文…...

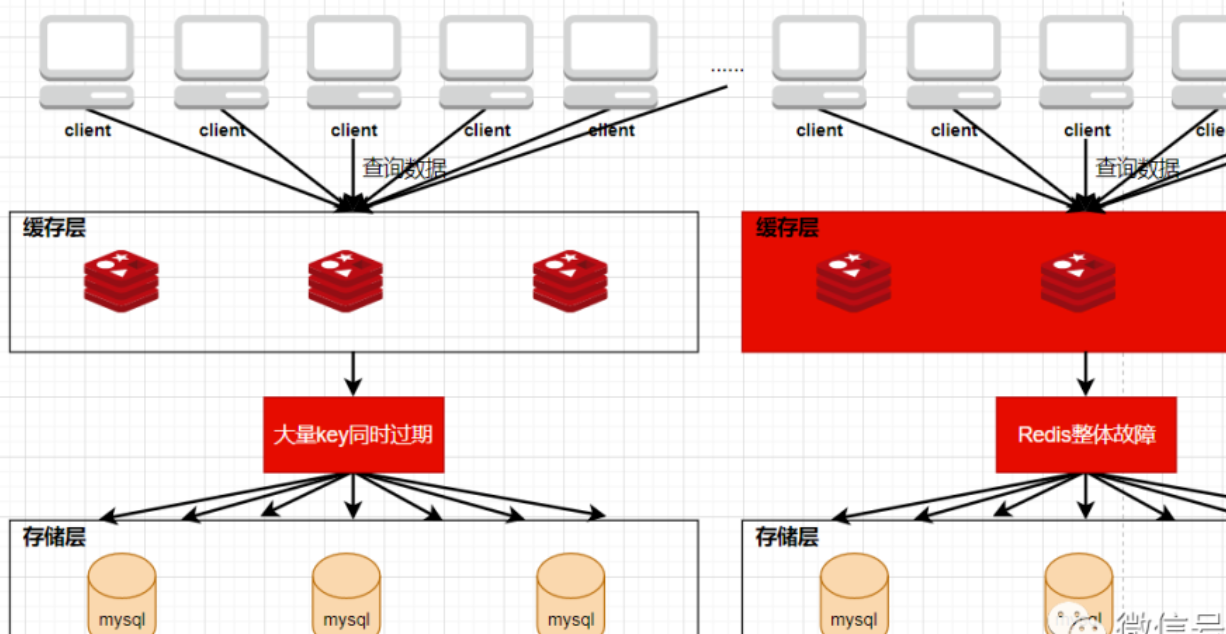

REDIS中的缓存穿透,缓存击穿,缓存雪崩原因以及解决方案

需求引入一般在项目的开发中,都是使用关系型数据库来进行数据的存储,通常不会存在什么高并发的情况,可是一旦涉及大数据量的需求,比如商品抢购,网页活动导致的主页访问量瞬间增大,单一使用关系型数据库来保存数据的系统…...

数据库及缓存之MySQL(一)

思维导图 常见知识点 1.mysql存储引擎: 2.innodb与myisam区别: 3.表设计字段选择: 4.mysql的varchar(M)最多存储数据: 5.事务基本特性: 6.事务并发引发问题: 7.mysql索引: 8.三星索引…...

项目管理中,项目经理需要具备哪些能力?

项目经理是团队的领导者,是带领项目团队对项目进行策划、执行,完成项目目标,对于项目经理来说,想要有序推进项目,使项目更成功,光有理论知识是不够的,也要具备这些能力: 1、分清主…...

itk中的一些图像处理

文章目录1.BinomialBlurImageFilter计算每个维度上的最近邻居平均值2.高斯平滑3.图像的高阶导数 RecursiveGaussianImageFilter4.均值滤波5.中值滤波6.离散高斯平滑7.曲率驱动流去噪图像 CurvatureFlowImageFilter8.由参数alpha和beta控制的幂律自适应直方图均衡化9.Canny 边缘…...

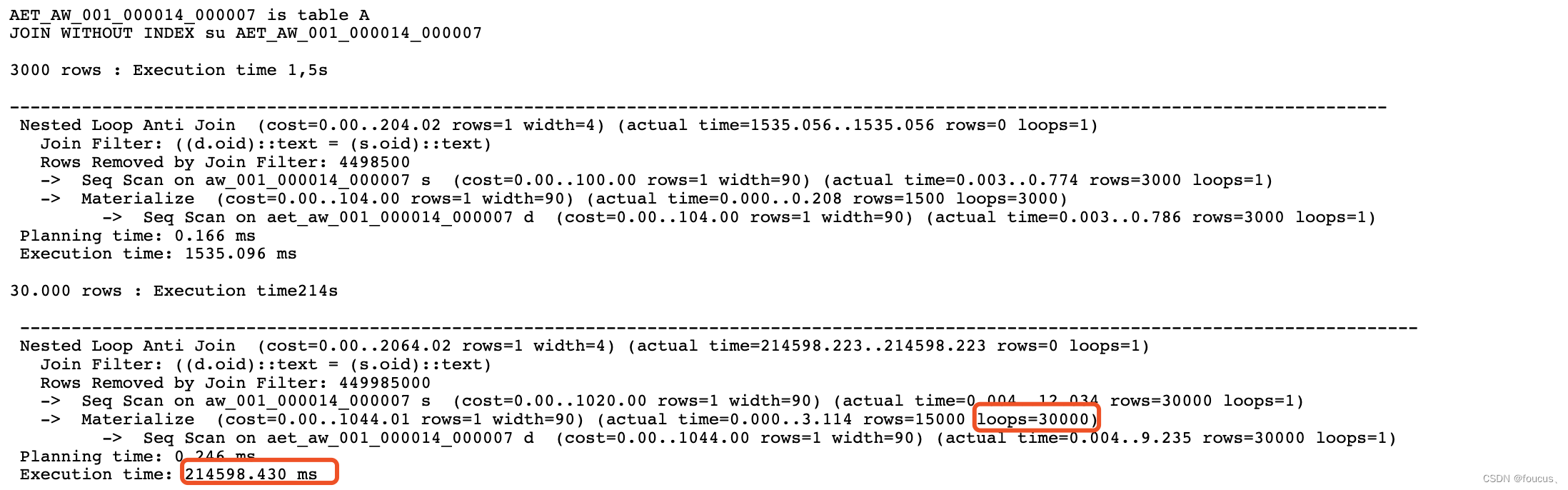

Endless lseek导致的SQL异常

最近碰到同事咨询的一个问题,在执行一个函数时,发现会一直卡在那里。 strace抓了下发现会话一直在执行lseek,大致情况如下: 16:13:55.451832 lseek(33, 0, SEEK_END) 1368064 <0.000037> 16:13:55.477216 lseek(33, 0, SE…...

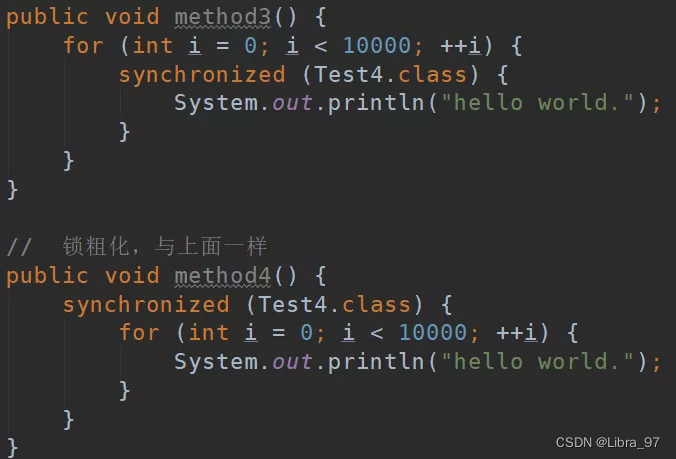

JUC-day01

JUC-day01 什么是JUC线程的状态: wait sleep关键字:同步锁 原理(重点)Lock接口: ReentrantLock(可重入锁)—>AQS CAS线程之间的通讯 1 什么是JUC 1.1 JUC简介 在Java中,线程部分是一个重点,本篇文章说的JUC也是关于线程的。JUC就是java.util .con…...

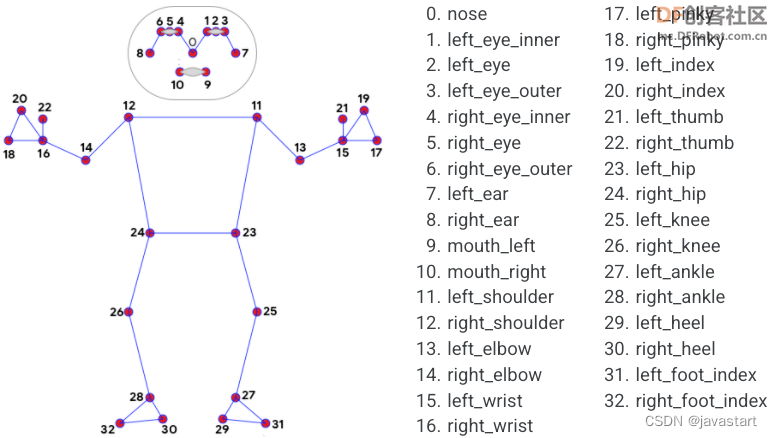

Mind+Python+Mediapipe项目——AI健身之跳绳

原文:MindPythonMediapipe项目——AI健身之跳绳 - DF创客社区 - 分享创造的喜悦 【项目背景】跳绳是一个很好的健身项目,为了获知所跳个数,有的跳绳上会有计数器。但这也只能跳完这后看到,能不能在跳的过程中就能看到,…...

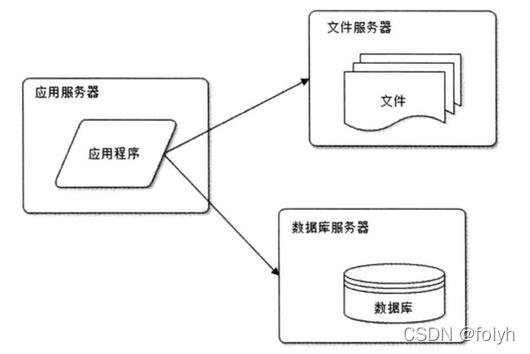

数据库概述

20世纪60年代后期,就出现了数据库技术。取得成就如下:造就了四位图灵奖得主发展成为以数据建模和DBMS核心技术为主,内容丰富的一门学科。带动了一个巨大的软件产业-DBMS产品及其相关工具和解决方案。四个基本概念数据数据是数据库中存储的基本…...

【已解决】解决IDEA的maven刷新依赖时出现Connot reconnect错误

前言 小编我将用CSDN记录软件开发求学之路上亲身所得与所学的心得与知识,有兴趣的小伙伴可以关注一下!也许一个人独行,可以走的很快,但是一群人结伴而行,才能走的更远!让我们在成长的道路上互相学习&#…...

文件的变编译和引用、执行)

动态链接库(.so)文件的变编译和引用、执行

动态链接库(.so)文件的变编译和引用 动态链接库:SO(Shared Object)是一种动态链接库,也被称为共享库。它是一种可被多个程序共享使用的二进制代码库,其中包含已编译的函数和代码。与静态链接库不同,动态链接…...

文件解压命令)

linux(centos8)文件解压命令

linux解压命令tar 解压命令常用解压命令1 [.tar] 文件 解压到当前文件夹2 [.tar.gz] 文件 解压到当前文件夹3 [.tar] 解压到指定文件夹 -C 必须是大写unzip 解压命令常用解压命令1 [.zip]解压到当前文件夹2 [.zip] 解压到指定文件夹2 [.zip] 解压到指定文件夹(强行覆…...

阅读笔记6——通道混洗

一、逐点卷积 当前先进的轻量化网络大都使用深度可分离卷积或组卷积,以降低网络的计算量,但这两种操作都无法改变特征图的通道数,因此需要使用11的卷积。总体来说,逐点的11卷积有如下两点特性: 可以促进通道之间的信息…...

上海亚商投顾:沪指失守3300点 卫星导航概念全天强势

上海亚商投顾前言:无惧大盘涨跌,解密龙虎榜资金,跟踪一线游资和机构资金动向,识别短期热点和强势个股。市场情绪指数早间低开后震荡回升,沪指盘中一度翻红,随后又再度走低,创业板指午后跌近1%。…...

从基础到卓越:Mac Mouse Fix的技术演进与用户价值提升之路

从基础到卓越:Mac Mouse Fix的技术演进与用户价值提升之路 【免费下载链接】mac-mouse-fix Mac Mouse Fix - A simple way to make your mouse better. 项目地址: https://gitcode.com/GitHub_Trending/ma/mac-mouse-fix 解决鼠标体验痛点:从功能…...

若依框架多数据源实战:如何用@DataSource注解轻松切换MySQL主从库

若依框架多数据源实战:用DataSource注解实现MySQL主从库智能切换 当系统流量逐渐攀升,数据库的读写压力开始显现时,很多开发者都会面临一个关键决策:如何在保证数据一致性的前提下,有效分散数据库负载?若依…...

深入解析BLE空口报文抓取:从GAP广播到LESC安全通信全流程

1. BLE空口报文抓取基础 想要分析BLE设备间的通信过程,抓取空口报文是最直接有效的方法。这就像在两个人对话时,用录音设备记录下他们的每一句话。不过BLE通信使用的是2.4GHz无线频段,我们无法直接用耳朵听到这些"对话",…...

谷歌浏览器结合Selenium IDE实现自动化脚本录制与Python导出)

(三)谷歌浏览器结合Selenium IDE实现自动化脚本录制与Python导出

1. 为什么你需要Selenium IDE脚本录制工具 最近有个测试同事跟我吐槽,说他每天要花3小时重复点击同一个电商网站,就为了检查商品详情页的展示逻辑。我听完直接给他安利了Selenium IDE——这个藏在谷歌浏览器里的小工具,5分钟就能搞定他半天的…...

电动汽车车队虚拟发电厂的强化学习控制策略探索

电动汽车车队虚拟发电厂的强化学习控制策略 本论文基于 RL 代理的开发,该代理通过家庭环境中的电动汽车充电站管理 VPP。 VPP 的主要优化目标是:填谷、削峰和随时间推移实现零负荷(供需负荷平衡)。 为实现目标而采取的主要行动是&…...

GG3M 元模型完整详解:从东方哲学数学化到文明级智慧操作系统

GG3M 元模型完整详解:从东方哲学数学化到文明级智慧操作系统摘要: GG3M 是全球首个以贾子理论(Kucius Theory)为核心、定位文明级智慧操作系统的 AGI 项目。其元模型(Meta-Model)以 3M 三层架构(…...

)

AI早报 | 2026.03.29(周日)

🤖 AI 早报 | 2026.03.29(周日) 采集时间:2026-03-29 13:25 (Asia/Shanghai) 🛡️ 安全/治理 1️⃣ Anthropic 安全漏洞泄露下一代模型 Mythos Anthropic 公司遭遇数据安全事件,未受保护的数据存储中泄露了…...

腾讯音乐开源的SuperSonic到底强在哪?手把手教你配置专属数据分析Agent

腾讯音乐SuperSonic深度解析:如何打造智能数据问答Agent 当企业数据量呈指数级增长时,传统BI工具已经难以满足实时决策的需求。腾讯音乐开源的SuperSonic作为新一代AIBI平台,通过融合Chat BI与Headless BI两大范式,正在重新定义数…...

DanKoe 视频笔记:写作技能:掌握写作,驾驭未来十年

概述 在本节课中,我们将要学习为什么写作是未来十年最重要的元技能,以及如何通过一个清晰的六步框架和一套实用的写作方法,开启你的个人写作事业。我们将探讨写作如何放大你的其他技能,并为你提供一套从零开始构建影响力的具体行…...

MS5803-14BA I²C驱动开发:嵌入式压力传感器实战指南

1. MS5803-14BA压力传感器库深度解析:面向嵌入式工程师的IC驱动开发实践1.1 传感器核心特性与工程定位MS5803-14BA是TE Connectivity(原Measurement Specialties)推出的高精度数字压力/温度复合传感器,采用MEMS压阻式传感原理与Δ…...