FPGA纯verilog代码实现H.264/AVC视频解码,提供工程源码和技术支持

目录

- 1、前言

- 2、硬件H.264/AVC视频解码优势

- 3、vivado工程设计架构

- 4、代码架构分析

- 5、vivado仿真

- 6、福利:工程代码的获取

1、前言

本设计是一种verilog代码实现的低功耗H.264/AVC解码器(baseline ),硬件ASIC设计,不使用任何GPP/DSP等内核,完全有可综合的verilog代码实现,没有任何ip,可在Xilinx、Intel、国产FPGA间任意移植;

本文详细描述了纯verilog实现设计方案,可直接项目移植,适用于在校学生做毕业设计、研究生项目开发,也适用于在职工程师做项目开发,可应用于医疗、军工等行业的视频解码领域;提供完整的、跑通的工程源码和技术支持;

本设计只做到了仿真层面并验证通过,并没有实际应用于真实项目,但理论上讲是可行的,作为研究FPGA实现H.264的学习性参考资料很完美,既有verilog源码又有仿真文件,作为工程应用可能需要自行搭建使用平台,我也可以提供技术支持;

H.264和AVC是两个不同机构定义的不同名称,其实质是同一个东西,也就是视频压缩和解压的算法,由于叫的人多了,也就习惯叫H.264了,不必纠结这些名称性的东西。

关于H.264编解码的理论知识,请看官自行搜索,CSDN也有很多大佬写得很详细,我就不写这部分了,我们详细讲讲用verilog实现的过程和本工程的组成结构。

2、硬件H.264/AVC视频解码优势

本H.264/AVC解码器(baseline)具有以下特点:

一个字:牛逼,表现如下:

1:Verilog-HDL实现,没有任何IP核,学习性和阅读性达到天花板;

2:目前只支持QCI分辨率(176X144)的实时H.264/AVC解码,但可修改代码以适应更高分辨率视频;

3:由于使用verilog代码实现,所以具有流水线操作和并行操作的特点,解码速度直接拉满;

4:帧间和帧内自适应流水线设计;

5:分层内存组织设计,减少外部内存访问;

6:低开销的帧内预测单元;

7:优化的帧间预测单元(运动补偿);

8:最大频率200MHz,可提供高达980kMB/s的吞吐量;

9:QCIF 30fps的实时解码仅需约1.5MHz时钟,只有169k个逻辑门,实测功耗低至293µW;

10:移植性达到天花板,Xilinx、Altera和国产FPGA之间自由移植;

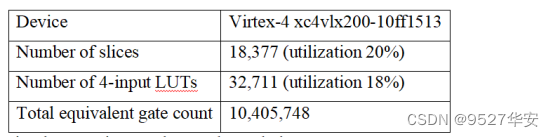

以Virtex-4 xc4vlx200的FPGA实现本解码器的资源消耗如下:

用专用ASIC实现本解码器的资源消耗如下:

3、vivado工程设计架构

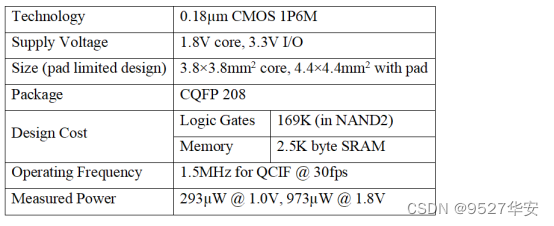

vivado工程设计架构如下:

代码运行仿真流程如下:

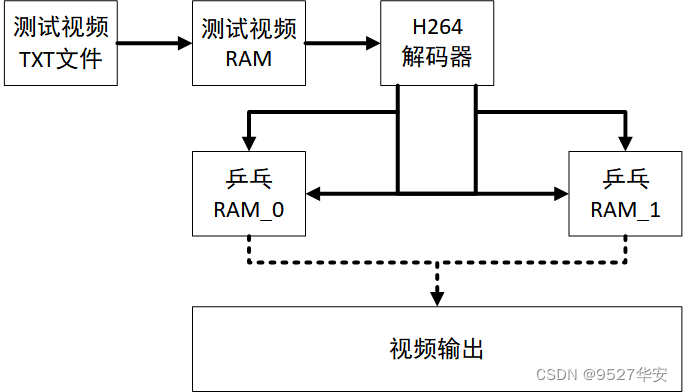

1:使用10个300帧的QCIF视频序列作为输入源,它们由JM94软件编码产生位TXT文件,生成的模拟视频流文件放在仿真文件夹下,如图:

2:测试视频RAM:负责将读取视频流文件送到H264解码器进行解码,该模块由H264解码器的视频流控制模块控制,只作为仿真应用,在实际使用中并不需要;模块很简单,源码如下:

module Beha_BitStream_ram(input clk ,input BitStream_ram_ren ,input [16:0] BitStream_ram_addr, output reg [15:0] BitStream_ram_data

);reg [15:0] BitStream_ram[0:`Beha_Bitstream_ram_size]; initial begin$readmemh("akiyo300_1ref.txt",BitStream_ram);endalways @ (posedge clk)if (BitStream_ram_ren == 0) BitStream_ram_data <= #2 BitStream_ram[BitStream_ram_addr]; endmodule

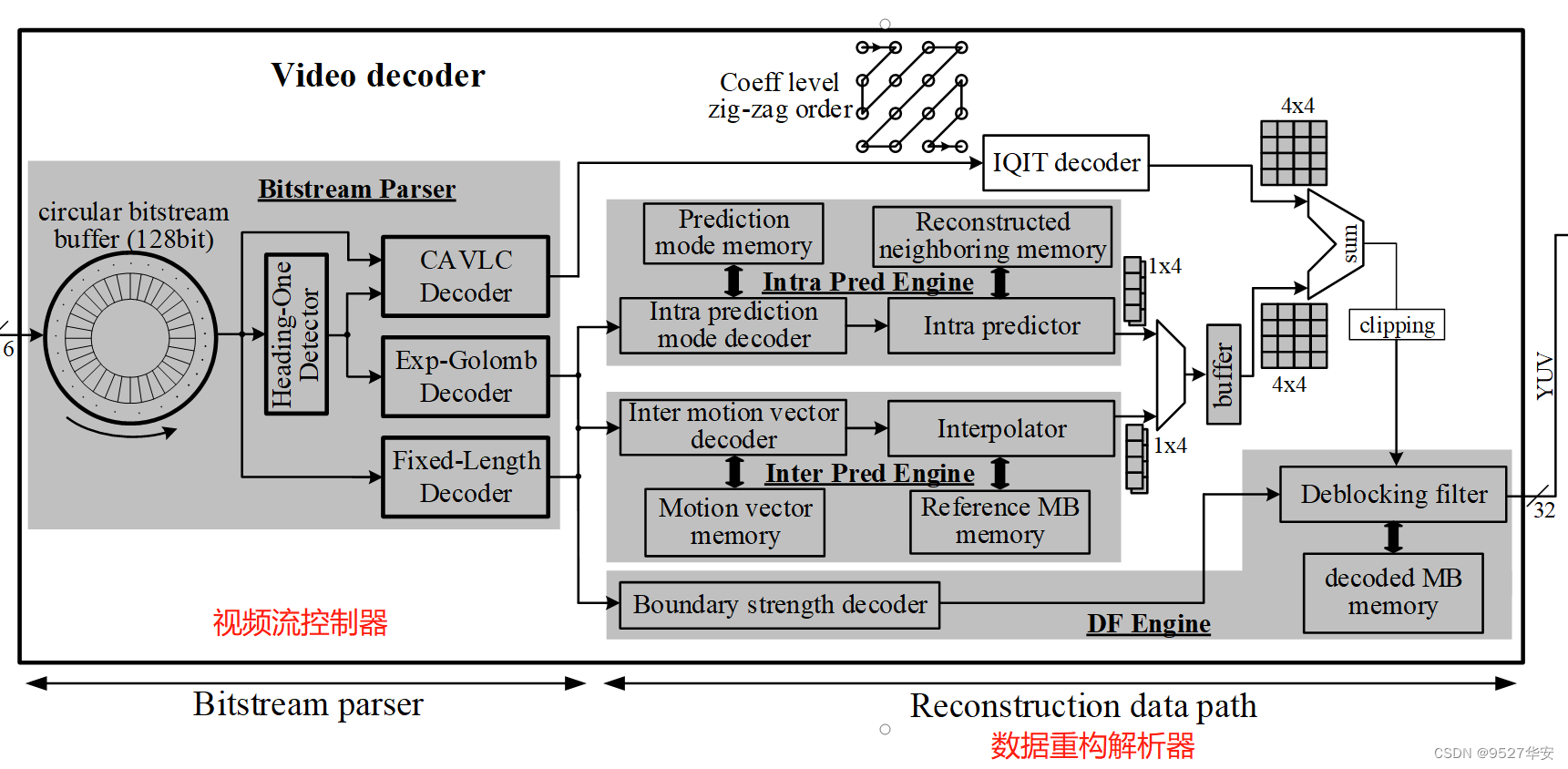

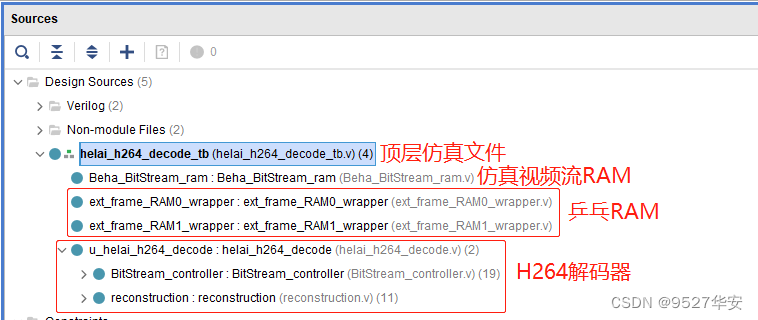

3:H264解码器:当测试视频RAM深度填充至一半时,开始发送测试视频流给到H264解码器;H264解码器由视频流控制器和数据重构解析器组成;如下:

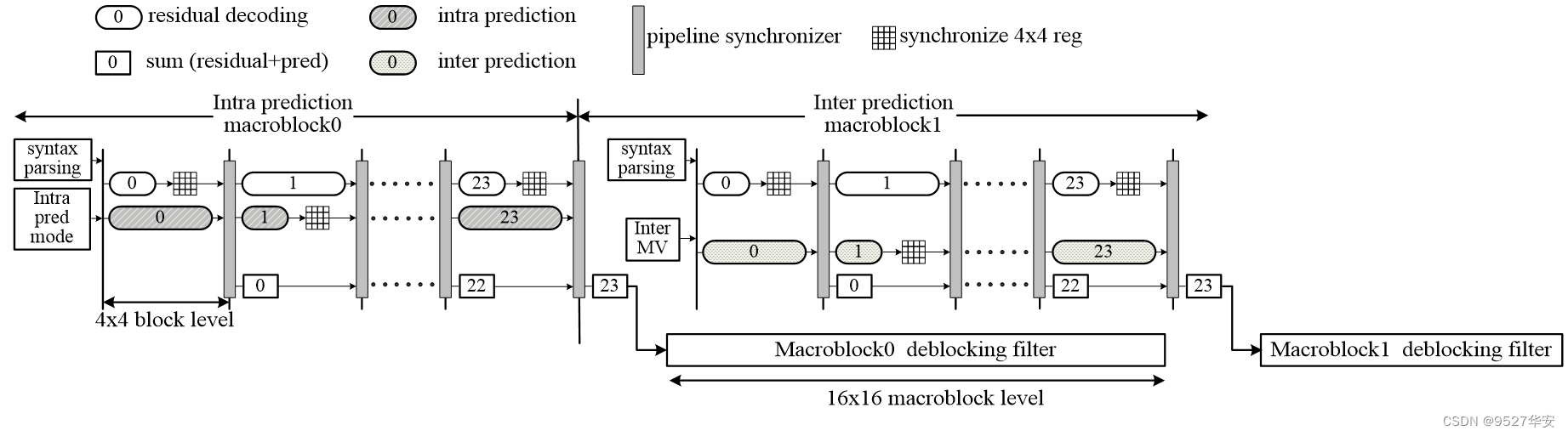

其中的4×4/16×16混合流水线机制如下:

关于H264解码器具体代码级详情,请联系我看源码,不是我不愿具体写,而是代码量实在有点大,写不完也装不下,如果具体写的话估计得出5本书。。。

H264解码器顶层接口如下:

module helai_h264_decode (input clk ,input reset_n ,input [15:0] BitStream_buffer_input,input pin_disable_DF ,input freq_ctrl0 ,input freq_ctrl1 , output BitStream_ram_ren ,output [16:0] BitStream_ram_addr ,output [5:0] pic_num ,//---ext_frame_RAM0---output ext_frame_RAM0_cs_n ,output ext_frame_RAM0_wr ,output [13:0] ext_frame_RAM0_addr ,input [31:0] ext_frame_RAM0_data ,//---ext_frame_RAM1---output ext_frame_RAM1_cs_n ,output ext_frame_RAM1_wr ,output [13:0] ext_frame_RAM1_addr ,input [31:0] ext_frame_RAM1_data ,output [31:0] dis_frame_RAM_din ,output slice_header_s6 );

4:乒乓RAM:设置了两个乒乓RAM,一个用来缓存一帧数据,作为H264解码器解析用,比如帧预测;另一个作为输出显示的缓存;当其中一个RAM完成自己的任务时,H264解码器控制二者角色互换;RAM顶层接口如下:

H264解码器通过片选信号ext_frame_RAM0_cs_n达到控制二者乒乓效果;

module ext_frame_RAM0_wrapper (input clk , input reset_n ,input ext_frame_RAM0_cs_n,input ext_frame_RAM0_wr ,input [13:0] ext_frame_RAM0_addr,input [31:0] dis_frame_RAM_din ,input [5:0] pic_num ,input slice_header_s6 ,output reg [31:0] ext_frame_RAM0_data

);

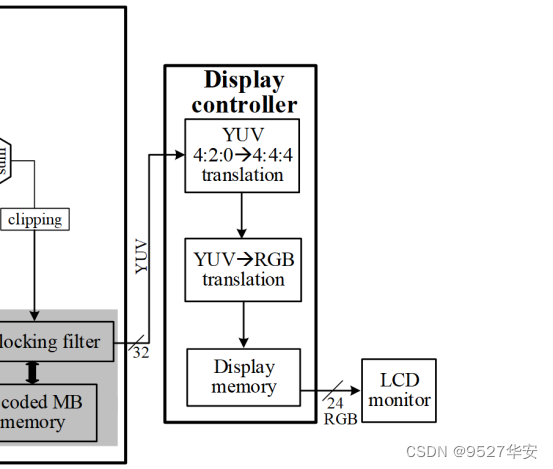

5:视频输出

H264解码器解码后的视频颜色空间为YUV4:2:0,需要转换为YUV4:4:4或者RGB8:8:8再输出显示,框图如下:

4、代码架构分析

总体代码架构如下:

下面我们重点看看H264解码器代码级组成:

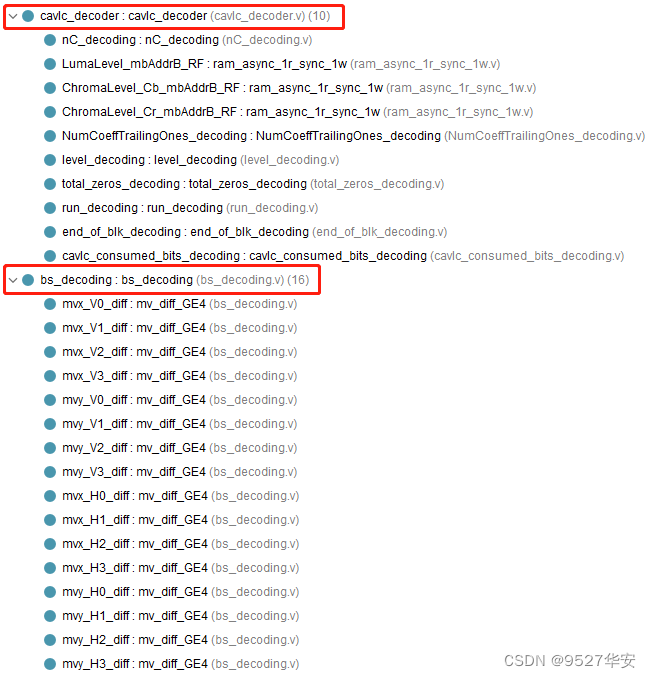

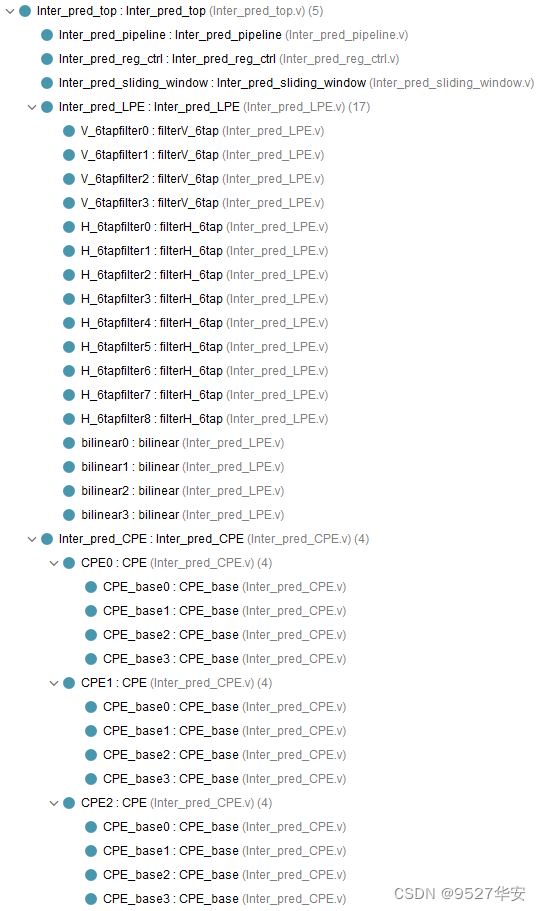

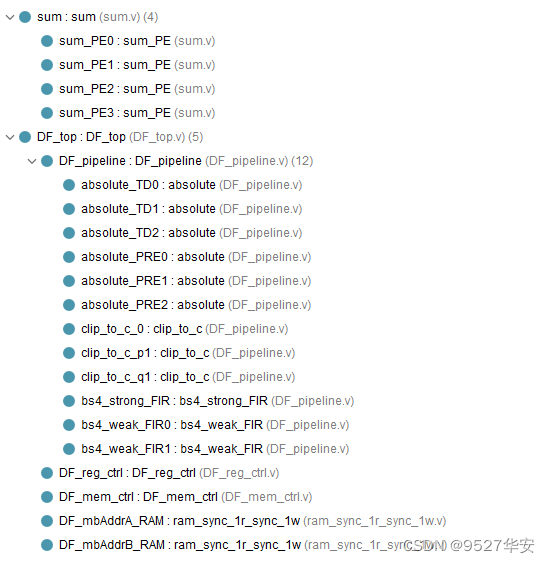

视频流控制器完整verilog代码组成如下:

数据重构解析器完整verilog代码组成如下:

关于H264解码器具体代码级详情,请联系我看源码,不是我不愿具体写,而是代码量实在有点大,写不完也装不下,如果具体写的话估计得出5本书。。。

5、vivado仿真

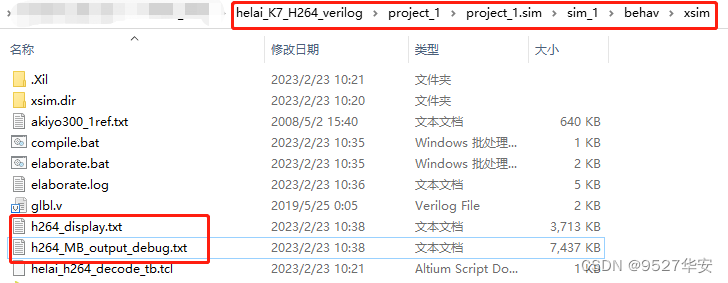

仿真后,H264解码器会输出两个文件,文件位置如下:

h264_display.txt:存放H264解码器输出的像素数据,可以将此文件转成图片显示;

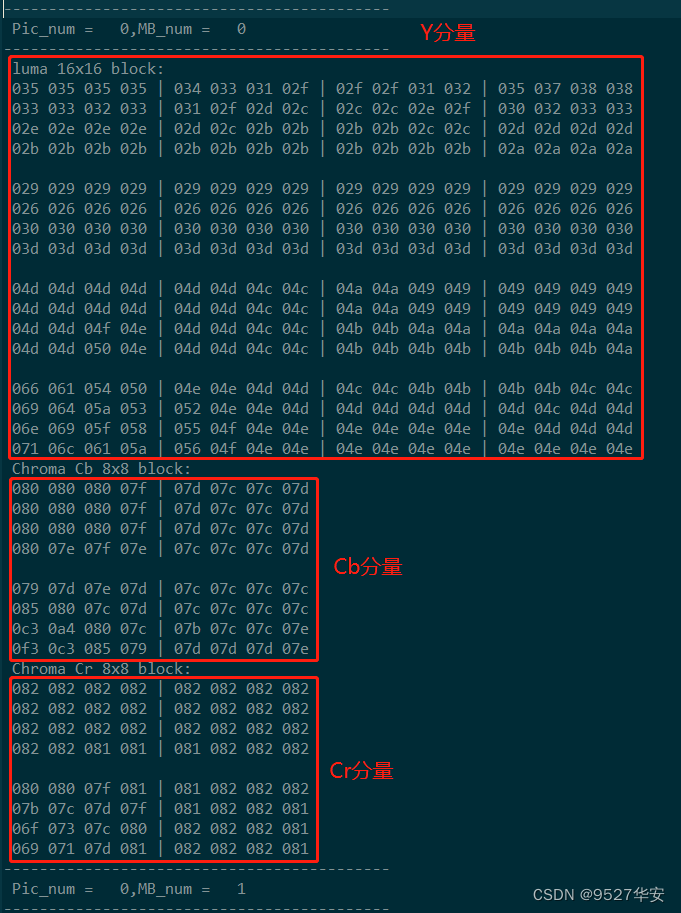

h264_MB_output_debug.txt:存放H264解码器输出的debug数据,可清晰看到输出过程,如下:

6、福利:工程代码的获取

福利:工程代码的获取

代码太大,无法邮箱发送,以某度网盘链接方式发送,

资料获取方式:私,或者文章末尾的V名片。

网盘资料如下:

相关文章:

FPGA纯verilog代码实现H.264/AVC视频解码,提供工程源码和技术支持

目录1、前言2、硬件H.264/AVC视频解码优势3、vivado工程设计架构4、代码架构分析5、vivado仿真6、福利:工程代码的获取1、前言 本设计是一种verilog代码实现的低功耗H.264/AVC解码器(baseline ),硬件ASIC设计,不使用任何GPP/DSP等内核&#…...

通俗神经网络

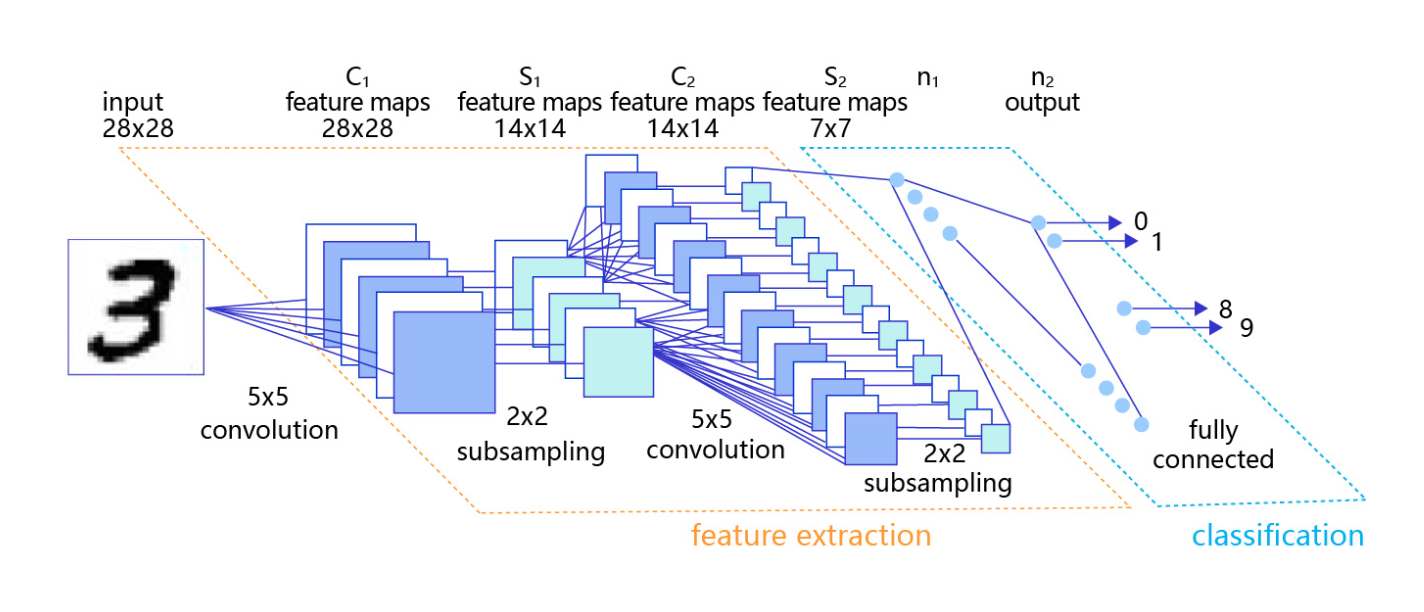

经典的全连接神经网络 经典的全连接神经网络来包含四层网络:输入层、两个隐含层和输出层,将手写数字识别任务通过全连接神经网络表示,如 图3 所示。 图3:手写数字识别任务的全连接神经网络结构输入层:将数据输入给神经…...

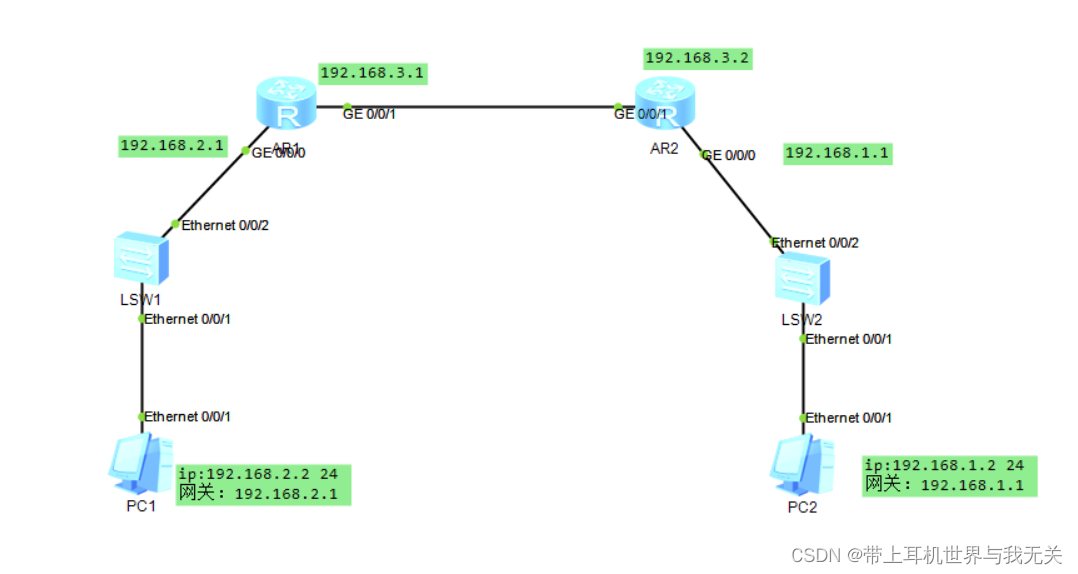

网络工程(一) 简单的配置

网络工程 简单的配置 需求 两台交换机 两台路由器 两台PC AR1配置静态路由 system-view [HUAWEI]sysname ar1 [ar1]interface g 0/0/0 [ar1-G…0/0/0]ip address 192.168.2.1 24 [ar1-G…0/0/0]quit [ar1]interface g 0/0/1 [ar1-G…0/0/1]ip address 192.168.3.1 24 [ar1-G…...

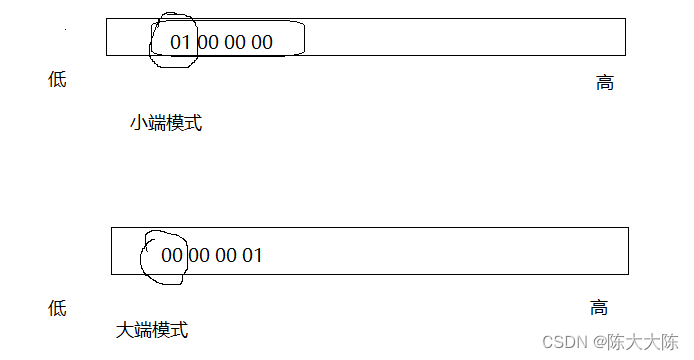

深度剖析数据在内存中的存储(上)

目录 1. 数据类型介绍 1.1 类型的基本归类 2. 整形在内存中的存储 2.1 原码、反码、补码 2.2 大小端介绍 2.3 一道小题 本章重点 1. 数据类型详细介绍 2. 整形在内存中的存储:原码、反码、补码 3. 大小端字节序介绍及判断 4. 浮点型在内存中的存储解析 正文…...

CF Edu 130 A-D vp 补题

CF Edu 130 A-D vp 补题 数模也是终于结束了。开始恢复vp。今天这场vp发挥比上次好一些,三题rank3600。A,B题做的很顺利。C题标记没弄全多WA了两发。D题是个交互题,也是研究了一下。基本思路正确。 题目链接 A. Parkway Walk 贪心 题意&am…...

4707: 统计数字个数

描述给定一个非负整数a,求其中含有数字b的个数(0<a<2147483647,0<b<9)。如100001中含所有0的个数为4,1的个数为2。输入输入数据有多组,每组一行,每行为两个整数,即a和b&…...

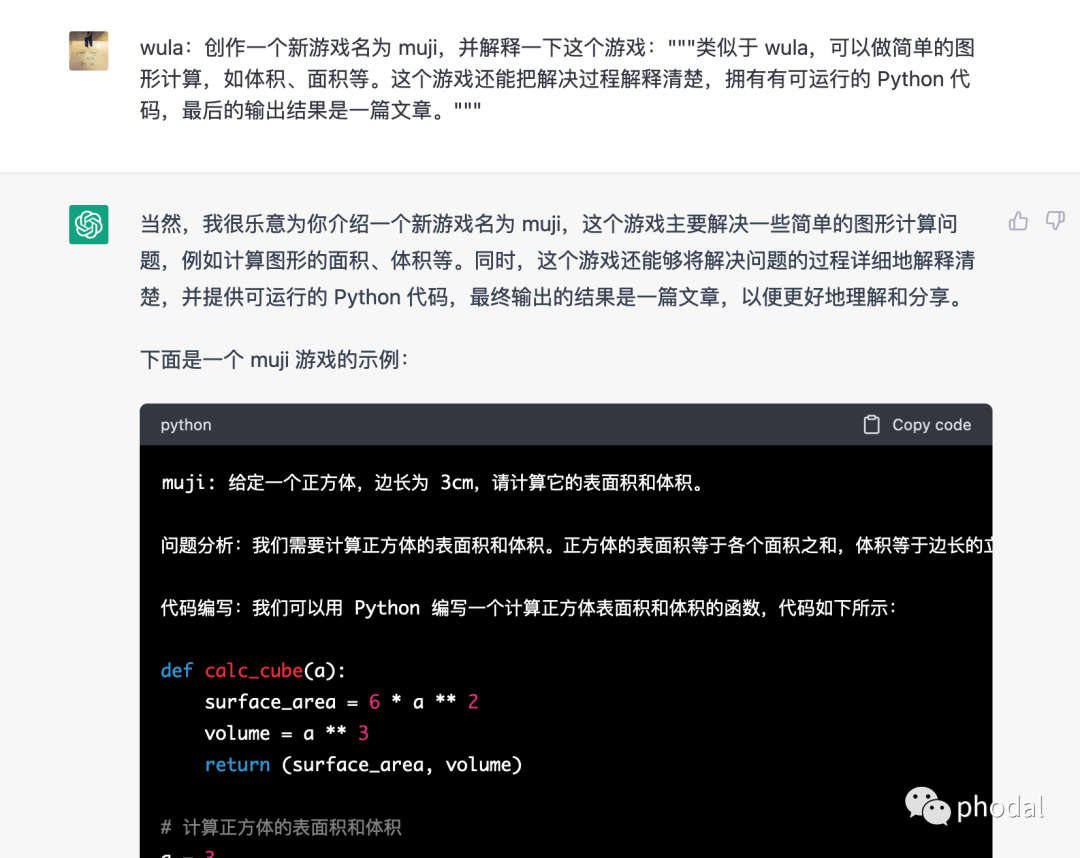

ChatGPT 编写模式:如何高效地将思维框架赋予 AI ?

如何理解 Prompt ?Prompt Enginneeringprompt 通常指的是一个输入的文本段落或短语,作为生成模型输出的起点或引导。prompt 可以是一个问题、一段文字描述、一段对话或任何形式的文本输入,模型会基于 prompt 所提供的上下文和语义信息&#x…...

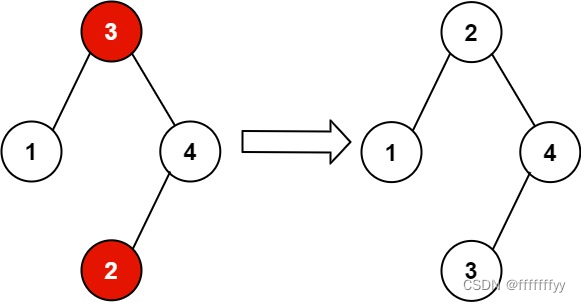

Leetcode力扣秋招刷题路-0099

从0开始的秋招刷题路,记录下所刷每道题的题解,帮助自己回顾总结 99. 恢复二叉搜索树 给你二叉搜索树的根节点 root ,该树中的 恰好 两个节点的值被错误地交换。请在不改变其结构的情况下,恢复这棵树 。 示例 1: 输入…...

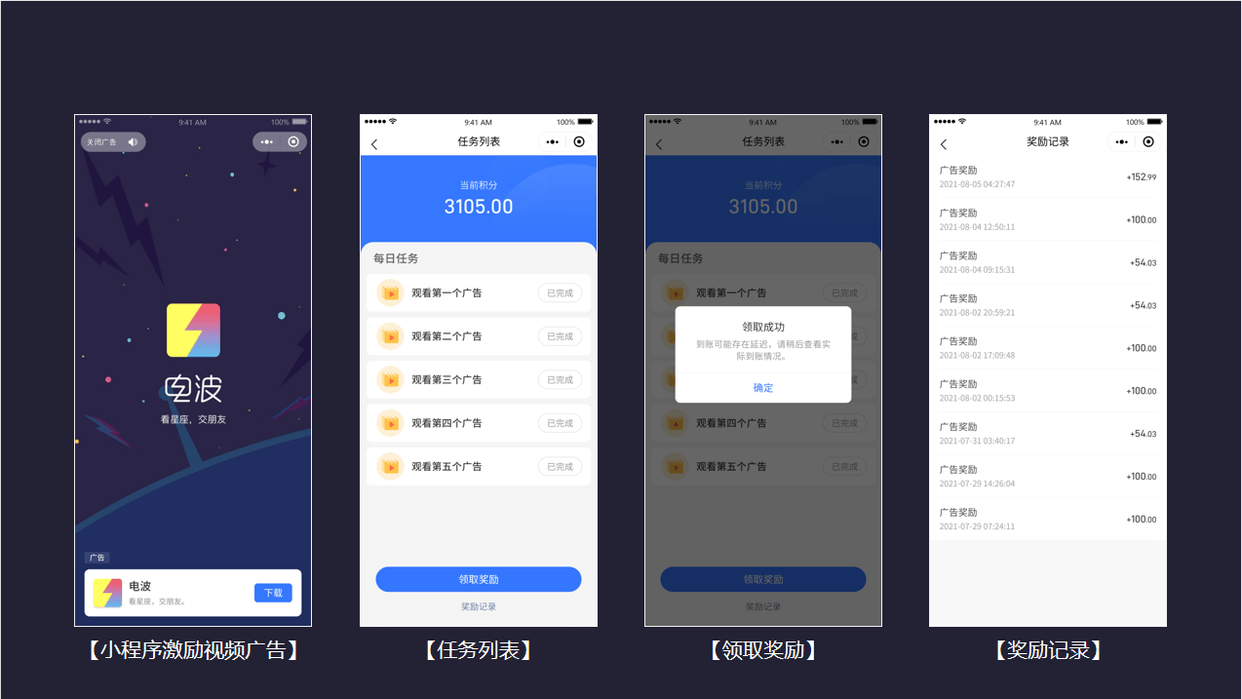

消费升级趋势下,平台如何在广告电商模式中攫取新流量

如今电商平台飞速发展,越来越多的人加入电商运营的行列,同行竞争逐渐变得激烈起来,为了能够让平台有更多的展现机会,提升平台的商品转化率,大家都很重视平台的优化,因为一个好的平台可以给自身带来更多的流…...

华为OD机试真题 用 C++ 实现 - 众数和中位数 | 多看题,提高通过率

最近更新的博客 华为OD机试 - 入栈出栈(C++) | 附带编码思路 【2023】 华为OD机试 - 箱子之形摆放(C++) | 附带编码思路 【2023】 华为OD机试 - 简易内存池 2(C++) | 附带编码思路 【2023】 华为OD机试 - 第 N 个排列(C++) | 附带编码思路 【2023】 华为OD机试 - 考古…...

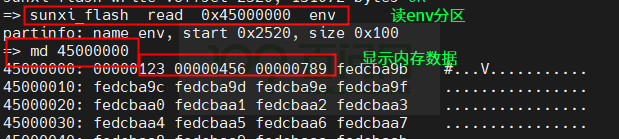

Linux NOR 开发指南

Linux NOR 开发指南 1 简介 编写目的 此文档描述Sunxi NOR 模块的使用方法,为相关人员调试提供指导 适用范围 boot0: 适用于brandy-2.0u-boot: 适用于u-boot-2018kernel: 适用于linux-4.9/linux-5.4 内核 BSP 的开发人员、测试人员 2 模块介绍 2.1 模块功能…...

免费领取丨精算与金融建模行业解决方案白皮书,不要错过!

一、我国精算行业现状 精算学是对人类社会所面临的各种风险及其他客观事务进行量化分析和处理的一门科学。在保险、金融、投资和各类风险管理等许多领域得到广泛应用,尤其在保险和社会保障领域,已成为不可或缺的科学和技术,以保险公司为例&a…...

ideal创建maven项目

前置工作本机安装mavenIdea 设置使用本机maven 工具Settings--->Maven开始创建maven项目创建maven项目,勾选通过模板创建,选择 maven-archetype-webapp 模板GroupId: 公司名倒序ArtifactId: 项目名设置本地maven仓库配置项目文件显示名,和…...

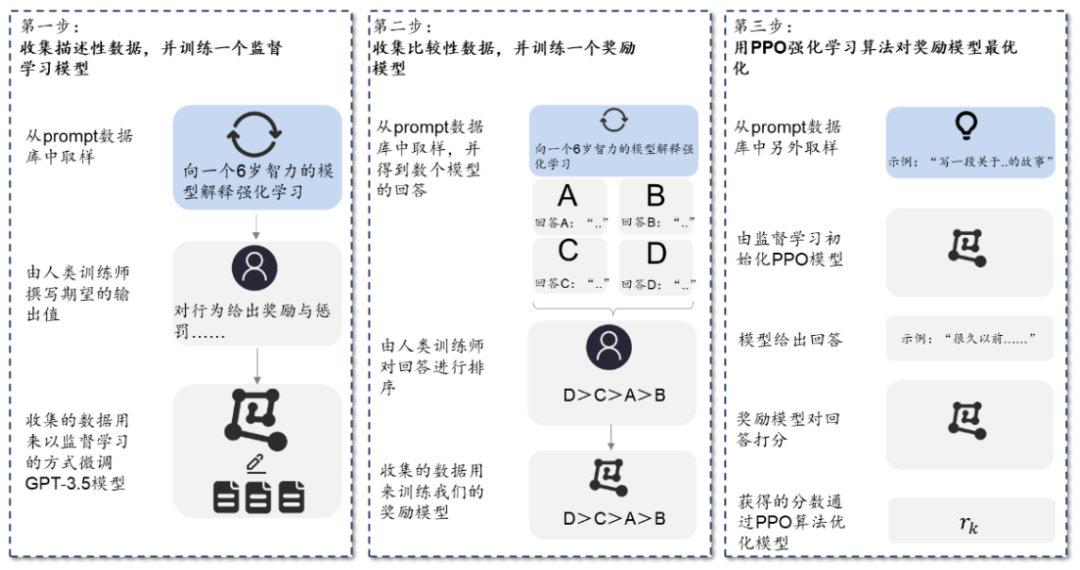

ChatGPT是什么?为何会引爆国内算力需求?

过去十年中,通过“深度学习大算力”从而获得训练模型是实现人工智能的主流技术途径。由于深度学习、数据和算力这三个要素都已具备,全世界掀起了“大炼模型”的热潮,也催生了大批人工智能企业。大模型是人工智能的发展趋势和未来大模型&#…...

【Linux】进程间通信(万字详解)—— 匿名管道 | 命名管道 | System V | 共享内存

🌈欢迎来到Linux专栏~~进程通信 (꒪ꇴ꒪(꒪ꇴ꒪ )🐣,我是Scort目前状态:大三非科班啃C中🌍博客主页:张小姐的猫~江湖背景快上车🚘,握好方向盘跟我有一起打天下嘞!送给自己的一句鸡汤…...

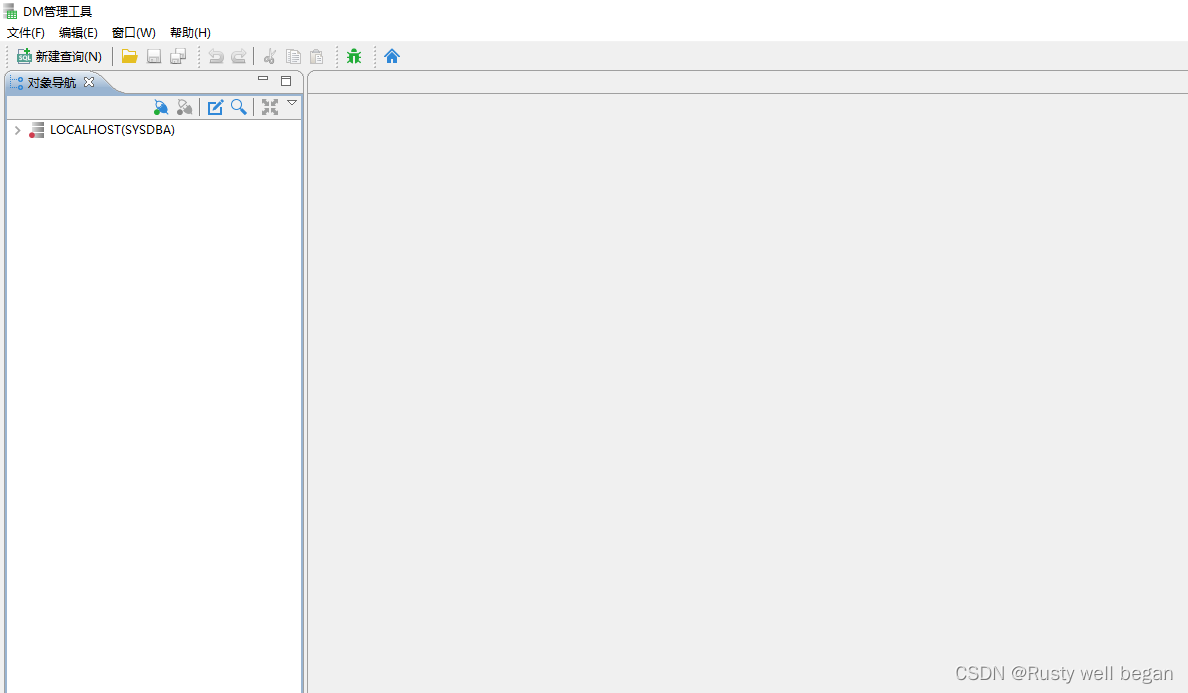

【Database-02】达梦数据库 - DM Manager管理工具安装

1、简介 DM Manager是达梦数据库自带的图形化界面管理工具,在安装达梦数据库的时候就会自动安装。 Linux环境,默认安装路径为:达梦安装目录/tool/manager,如果Linux是安装GUI,那么就可以直接启动使用。 实际大部分使…...

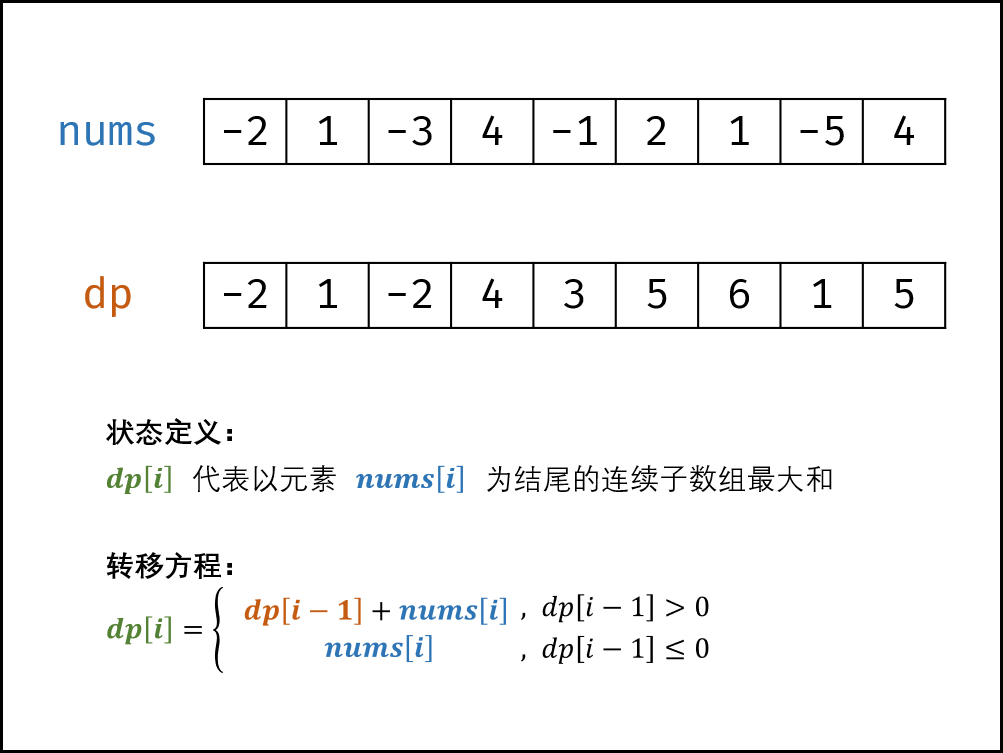

剑指 Offer 42. 连续子数组的最大和

剑指 Offer 42. 连续子数组的最大和 难度:easy\color{Green}{easy}easy 题目描述 输入一个整型数组,数组中的一个或连续多个整数组成一个子数组。求所有子数组的和的最大值。 要求时间复杂度为O(n)。 示例1: 输入: nums [-2,1,-3,4,-1,2,1,-5,4] 输…...

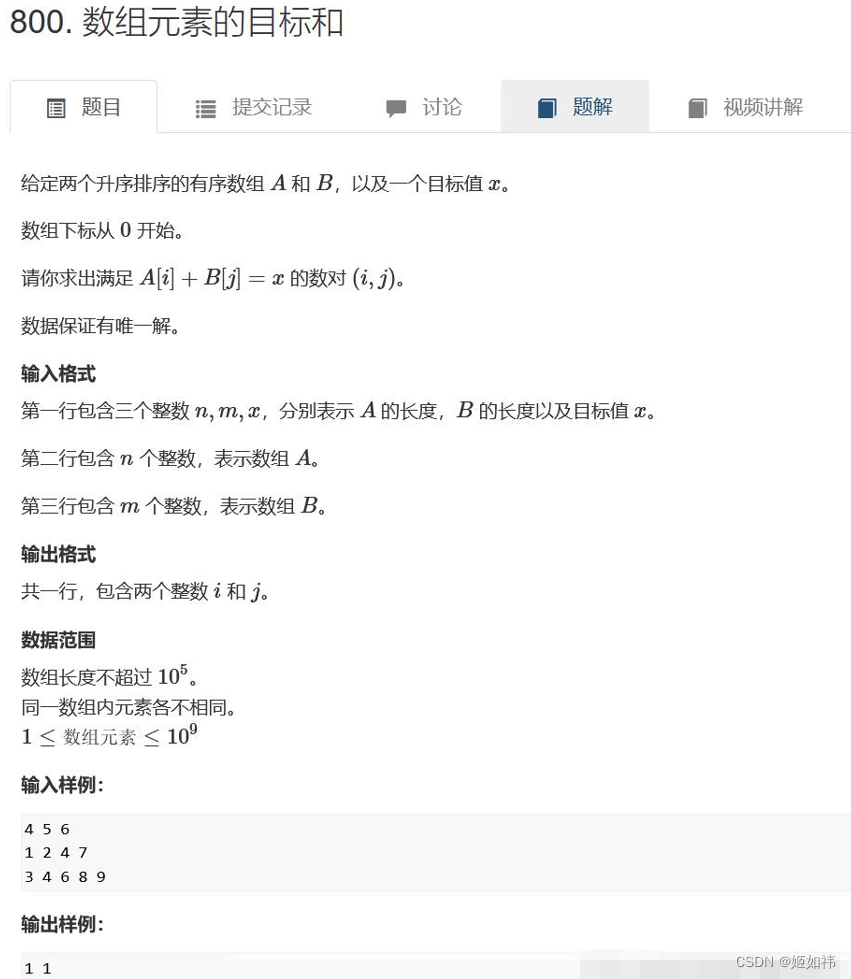

双指针 (C/C++)

1. 双指针 双指针算法的核心思想:将暴力解法的时间复杂度,通常是O(N*N),通过某种特殊的性质优化到O(N)。 做题思路:先想想暴力解法的思路,然后分析这道题的特殊性质,一般是单调性。然后得出双指针算法的思路…...

CVE-2023-23752 Joomla未授权访问漏洞分析

漏洞概要 Joomla 在海外使用较多,是一套使用 PHP 和 MySQL 开发的开源、跨平台的内容管理系统(CMS)。 Joomla 4.0.0 至 4.2.7 版本中的 ApiRouter.php#parseApiRoute 在处理用户的 Get 请求时未对请求参数有效过滤,导致攻击者可向 Joomla 服务端点发送包…...

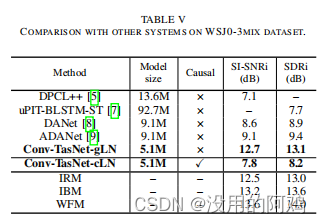

单通道说话人语音分离——Conv-TasNet(Convolutional Time-domain audio separation Network)

单通道说话人语音分离——Conv-TasNet模型(Convolutional Time-domain audio separation Network) 参考文献:《Conv-TasNet: Surpassing Ideal Time-FrequencyMagnitude Masking for Speech Separation》 1.背景 在真实的声学环境中,鲁棒的语音处理通常…...

Wan2.2-I2V-A14B在Qt桌面程序中的应用:开发本地化视频创作工具

Wan2.2-I2V-A14B在Qt桌面程序中的应用:开发本地化视频创作工具 1. 引言:让AI视频生成触手可及 想象一下,一个普通用户无需学习复杂的命令行,只需拖拽图片、滑动几个调节条,就能轻松将静态图片变成生动的视频。这正是…...

用快马AI快速原型你的技能组合:一键生成个人技能展示页

今天想和大家分享一个快速验证技能组合的小技巧——用InsCode(快马)平台一键生成个人技能展示页。作为开发者,我们经常需要向团队或客户展示自己的技术栈,但手动写前端页面太耗时。最近发现用AI生成原型特别高效,整个过程不到10分钟就能获得可…...

小白也能玩转AI绘画:AnythingtoRealCharacters2511动漫转真人快速入门

小白也能玩转AI绘画:AnythingtoRealCharacters2511动漫转真人快速入门 1. 动漫转真人的神奇魔法 你是否曾经盯着动漫角色想象:"如果这个角色变成真人会是什么样子?"现在,这个想象可以轻松实现了。AnythingtoRealChara…...

)

汽车ECU安全解锁实战:手把手教你用C语言实现AES-CMAC算法(附完整源码)

汽车ECU安全访问实战:AES-CMAC算法深度解析与工程实现 在汽车电子控制单元(ECU)的安全访问机制中,27服务作为常见的诊断协议,其核心安全认证流程往往依赖于AES-CMAC算法。本文将带您深入理解这一算法的工程实现细节&am…...

如何用abcjs在浏览器中快速生成专业五线谱:完整免费教程

如何用abcjs在浏览器中快速生成专业五线谱:完整免费教程 【免费下载链接】abcjs javascript for rendering abc music notation 项目地址: https://gitcode.com/gh_mirrors/ab/abcjs 在数字化音乐创作与分享的时代,abcjs作为一个强大的JavaScript…...

RBTray完全指南:Windows任务栏清理终极解决方案

RBTray完全指南:Windows任务栏清理终极解决方案 【免费下载链接】rbtray A fork of RBTray from http://sourceforge.net/p/rbtray/code/. 项目地址: https://gitcode.com/gh_mirrors/rb/rbtray 你是否经常感到Windows任务栏拥挤不堪?各种后台程序…...

单片机自动脱模剂喷雾控制系统

/***实现功能:检测报警信号,脱模剂开模数计数信号***/ /***参数:1:脱模剂开模数 2:喷雾时间 3:延时时间 ***/ /***串口接收触摸屏参数设置字符串,接收并保存******/ /***端子输入口读开模数,比较设定值后输出到电磁阀**/ /***端子输入口读报警信号,到设定值关闭电机及加热**/#i…...

破解3DS游戏格式兼容难题:3dsconv工具的技术实现与应用指南

破解3DS游戏格式兼容难题:3dsconv工具的技术实现与应用指南 【免费下载链接】3dsconv Python script to convert Nintendo 3DS CCI (".cci", ".3ds") files to the CIA format 项目地址: https://gitcode.com/gh_mirrors/3d/3dsconv 问题…...

C++性能调优第一步:手把手教你用QueryPerformanceCounter和chrono精准测量微秒级函数耗时

C性能调优实战:微秒级耗时测量的艺术与科学 在追求极致性能的世界里,每一微秒都至关重要。高频交易系统中,1微秒的延迟可能意味着数百万美元的损失;游戏引擎里,帧间时间的细微波动会导致画面卡顿;实时音视频…...

快速构建SpringBoot微服务:Phi-3-mini智能代码生成与架构咨询

快速构建SpringBoot微服务:Phi-3-mini智能代码生成与架构咨询 1. 引言:当AI助手遇上Java开发 最近接手了一个新项目,需要快速搭建一套SpringBoot微服务架构。正当我对着空白的IDE发愁时,同事推荐了Phi-3-mini这个AI助手。说实话…...