Verilog零基础入门(边看边练与测试仿真)-状态机-笔记(7-10讲)

文章目录

- 第七讲

- 第八讲

- 第九讲

- 第十讲

第七讲

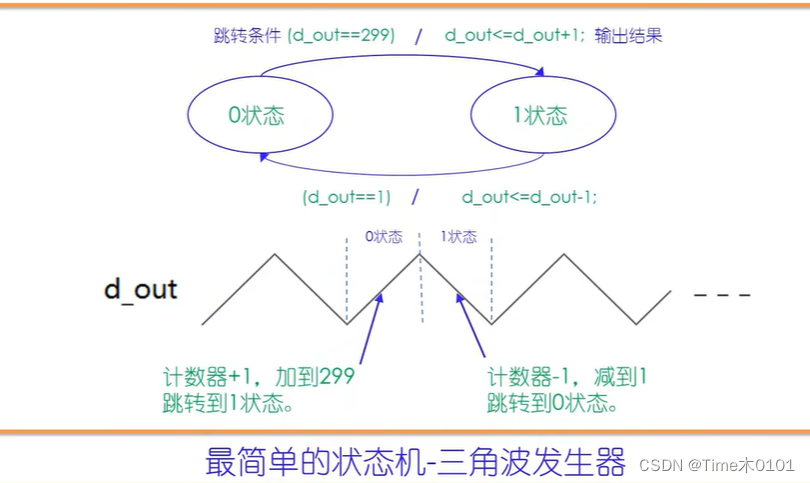

1、最简单的状态机-三角波发生器

1、两种状态的代码:

//最简单的状态机,三角波发生器;

`timescale 1ns/10ps

module tri_gen(clk,res,d_out);

input clk;

input res;

output[8:0] d_out;reg state;//主状态机寄存器

reg[8:0] d_out;always@(posedge clk or negedge res )

if(~res)beginstate<=0;d_out<=0;

end

else begincase(state)0://上升;begind_out<=d_out+1;if(d_out==299)beginstate<=1;endend1://下降begind_out<=d_out-1;if(d_out==1)beginstate<=0;endend endcase

endendmodule//---------testbench of tri_gen-----

module tri_gen_tb;

reg clk,res;

wire[8:0] d_out;

tri_gen U1(.clk(clk),.res(res),.d_out(d_out));initial beginclk<=0;res<=0;#17 res<=1;#8000 $stop;

endalways #5 clk<=~clk;

endmodule

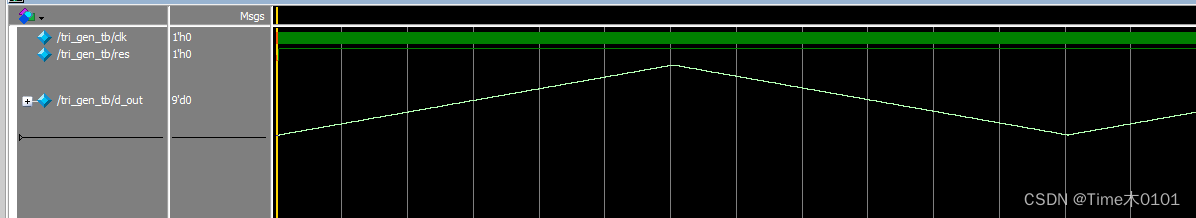

仿真结果:

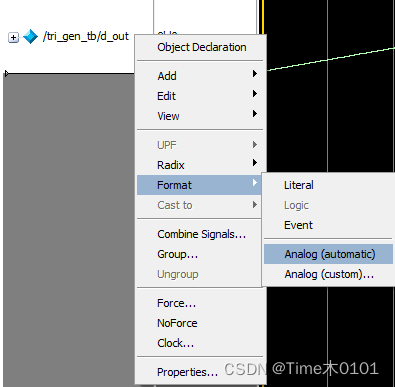

另一种波形查看方法

2、四种状态的代码

//2023-0913,time

//最简单的状态机,三角波发生器;

`timescale 1ns/10ps

module tri_gen(clk,res,d_out);

input clk;

input res;

output[8:0] d_out;reg[1:0] state;//主状态机寄存器

reg[8:0] d_out;reg[7:0] con;//计数器,记录平顶周期个数always@(posedge clk or negedge res )

if(~res)beginstate<=0;d_out<=0;con<=0;

end

else begincase(state)0://上升;begind_out<=d_out+1;if(d_out==299)beginstate<=1;endend1://平顶beginif(con==200)beginstate<=2;con<=0;endelse begincon<=con+1;end end2://下降begind_out<=d_out-1;if(d_out==1)beginstate<=3;endend 3://平顶beginif(con==200)beginstate<=0;con<=0;endelse begincon<=con+1;end endendcase

endendmodule//---------testbench of tri_gen-----

module tri_gen_tb;

reg clk,res;

wire[8:0] d_out;

tri_gen U1(.clk(clk),.res(res),.d_out(d_out));initial beginclk<=0;res<=0;#17 res<=1;#40000 $stop;

endalways #5 clk<=~clk;

endmodule

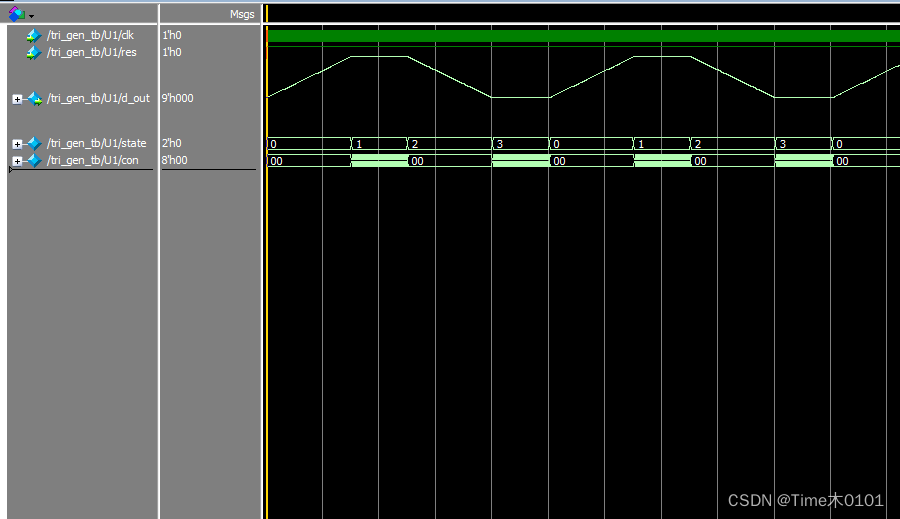

仿真波形:

3、如果state定义的[1:0],也就是有四种状态,那么如果有没用到的状态,应该用default写完全。

第八讲

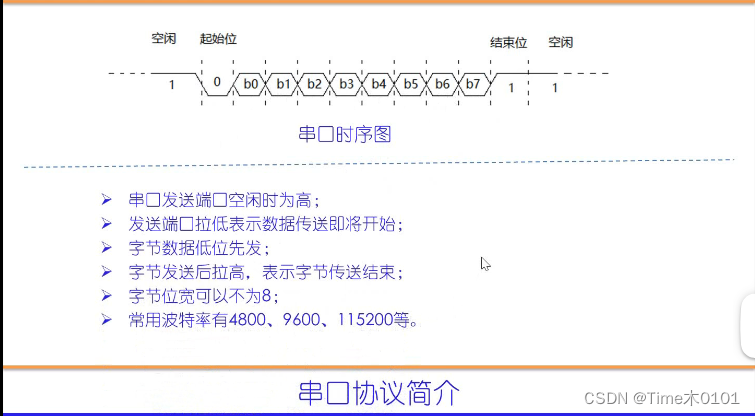

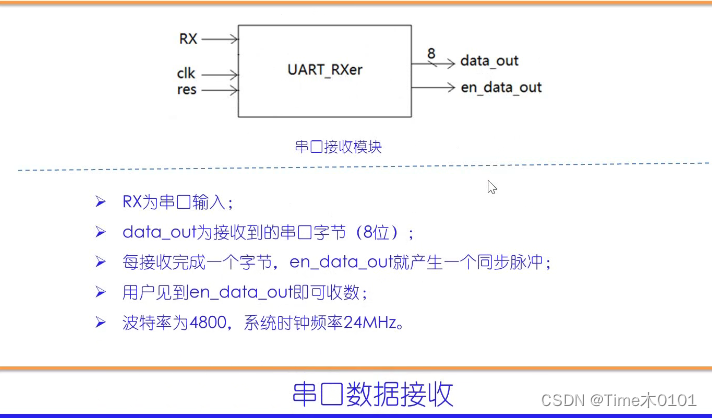

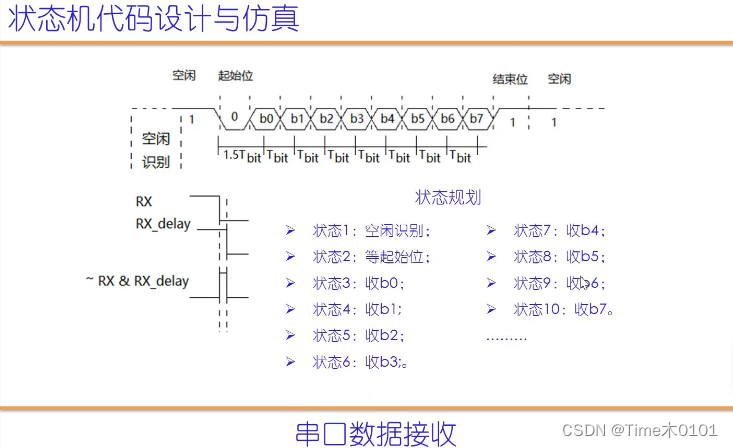

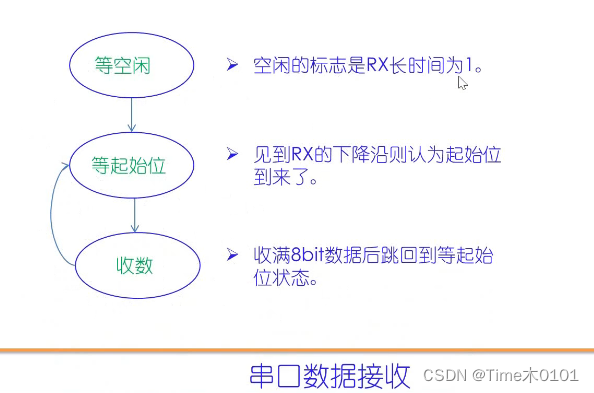

1、串口数据接收

代码:

//2023-09-18,time

//串口数据接收

`timescale 1ns/10ps

module UART_RXer(clk,res,RX,data_out,en_data_out);

input clk;

input res;

input RX;

output[7:0] data_out;//接受字节输出;

output en_data_out;//输出势能;reg[7:0] data_out;

reg[7:0] state;//主状态机;

reg[12:0] con;//用于计算比特宽度;

reg[3:0] con_bits;// 用于计算比特数;reg RX_delay;//RX的延时;

reg en_data_out;

always@(posedge clk or negedge res)

if(~res)beginstate<=0;con<=0;con_bits<=0;RX_delay<=0;en_data_out<=0;data_out<=0;

end

else beginRX_delay<=RX;case(state)0://等空闲:beginif(con==5000-1)begincon<=0;endelse begincon<=con+1;endif(con==0)beginif(RX)begincon_bits<=con_bits+1;endelse begincon_bits<=0;endendif(con_bits==12)beginstate<=1;end end1://等起始位beginen_data_out<=0;if(~RX&RX_delay)beginstate<=2;endend2://收最低位b0;beginif(con==7500-1)begincon<=0;data_out[0]<=RX;state<=3;endelse begincon<=con+1;endend3://收最低位b1;beginif(con==5000-1)begincon<=0;data_out[1]<=RX;state<=4;endelse begincon<=con+1;endend4://收最低位b2;beginif(con==5000-1)begincon<=0;data_out[2]<=RX;state<=5;endelse begincon<=con+1;endend5://收最低位b3;beginif(con==5000-1)begincon<=0;data_out[3]<=RX;state<=6;endelse begincon<=con+1;endend6://收最低位b4;beginif(con==5000-1)begincon<=0;data_out[4]<=RX;state<=7;endelse begincon<=con+1;endend7://收最低位b5;beginif(con==5000-1)begincon<=0;data_out[5]<=RX;state<=8;endelse begincon<=con+1;endend8://收最低位b6;beginif(con==5000-1)begincon<=0;data_out[6]<=RX;state<=9;endelse begincon<=con+1;endend9://收最低位b7;beginif(con==5000-1)begincon<=0;data_out[7]<=RX;state<=10;endelse begincon<=con+1;endend10://产生使能信号脉冲;beginen_data_out<=1;state<=1;enddefault://beginstate<=0;con<=0;con_bits<=0;en_data_out<=0;endendcase

endendmodule//-------testbench of UART_RXer-------

module UART_RXer_tb;

reg clk,res;

wire RX;

wire[7:0] data_out;

wire en_data_out;reg[25:0] RX_send;//里面装有串口字节发送数据

assign RX=RX_send[0];//连接RX;reg[12:0] con;UART_RXer UART_RXer( //同名例化;clk,res,RX,data_out,en_data_out);

initial beginclk<=0;res<=0;RX_send<={1'b1,8'haa,1'b0,16'hffff};con<=0;#17 res<=1;#4000000 $stop;

endalways #5 clk<=~clk;always@(posedge clk) beginif(con==5000-1)begincon<=0;endelse begincon<=con+1;endif(con==0)beginRX_send[24:0]<=RX_send[25:1];RX_send[25]<=RX_send[0];endend

endmodule

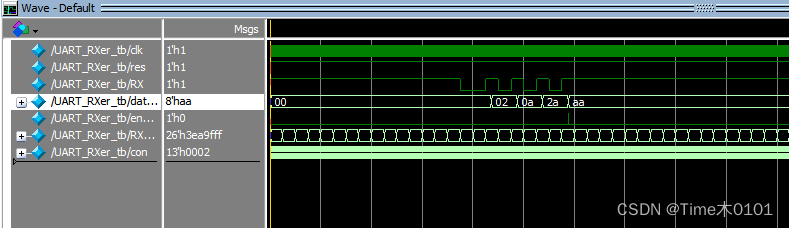

仿真波形:

小结:

第九讲

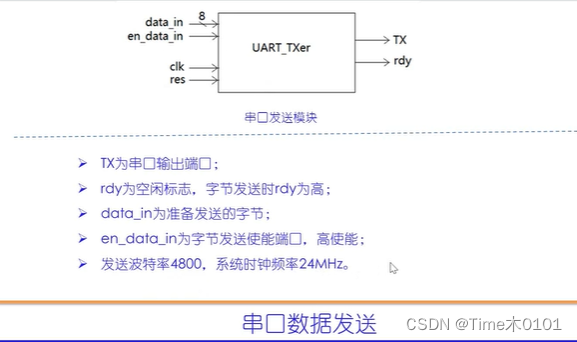

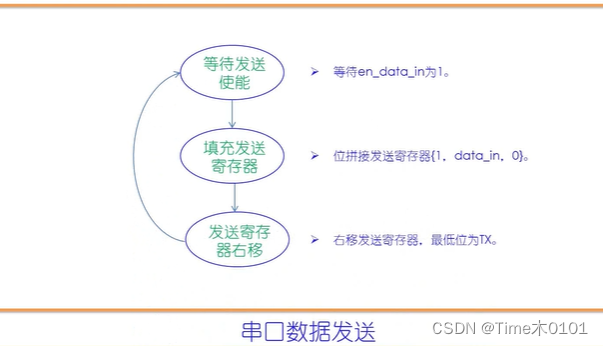

1、串口数据发送

代码:

//2023-09-18,time

//串口发送模块

`timescale 1ns/10ps

module UART_TXer(clk,res,data_in,en_data_in,TX,rdy);

input clk;

input res;

input[7:0] data_in;//准备发送的数据

input en_data_in;//发送使能

output TX;

output rdy;//空闲标志,0表示空闲reg[3:0] state;//主状态机寄存器;

reg[9:0] send_buf;//发送寄存器;

assign TX=send_buf[0];//连接TX;reg[9:0] send_flag;//用于判断右移结束;reg[12:0] con;//用于计算波特周期;

reg rdy;always@(posedge clk or negedge res)

if(~res)beginstate<=0;send_buf<=1;con<=0;send_flag<=10'b10_0000_0000;rdy<=0;

end

else begincase(state)0://等待使能信号beginif(en_data_in)beginsend_buf={1'b1,data_in,1'b0};send_flag<=10'b10_0000_0000;rdy<=1;state<=1;endend1://串口发送,寄存器右移;beginif(con==5000-1)begincon<=0;endelse begincon<=con+1;endif(con==5000-1)beginsend_buf[8:0]<=send_buf[9:1];send_flag[8:0]<=send_flag[9:1];endif(send_flag[0])beginrdy<=0;state<=0;endendendcase

end

endmodule//------testbench of UART_TXer--------

module UART_TXer_tb;

reg clk,res;

reg[7:0] data_in;

reg en_data_in;

wire TX;

wire rdy;

UART_TXer UART_TXer(clk,res,data_in,en_data_in,TX,rdy);initial beginclk<=0;res<=0;data_in<=8'h7f;en_data_in<=0;#17 res<=1;#30 en_data_in<=1;#10 en_data_in<=0;#2000000 $stop;

endalways #5 clk=~clk;endmodule

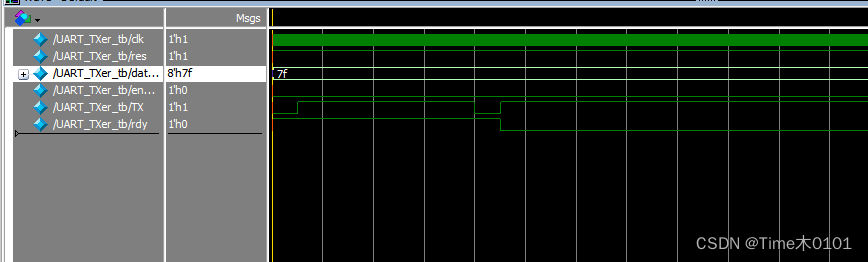

仿真波形:

小结:

第十讲

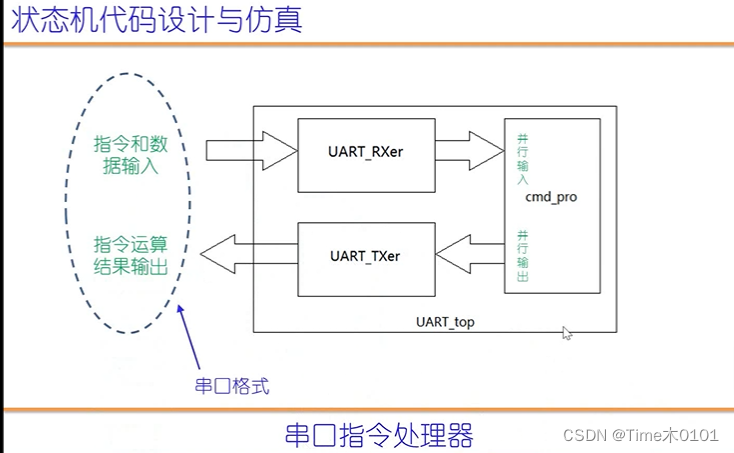

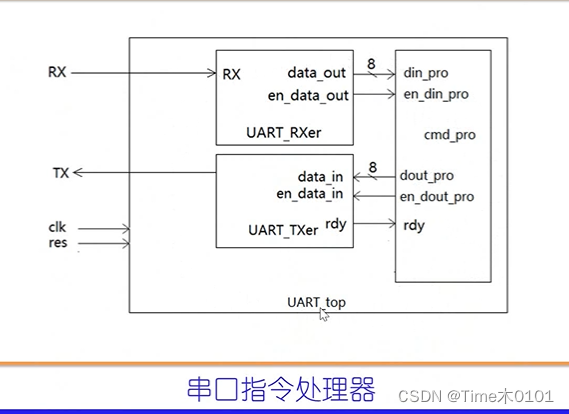

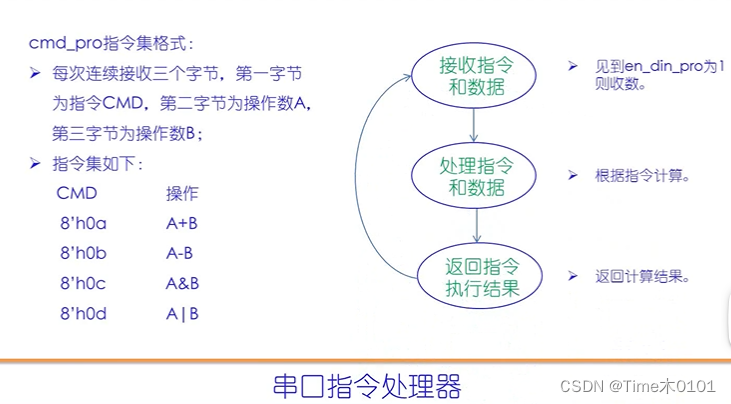

1、串口指令处理器

代码:

//2023-09-19,time

//指令处理器

module cmd_pro(clk,res,din_pro,en_din_pro,dout_pro,en_dout_pro,rdy);

input clk;

input res;

input[7:0] din_pro;//指令和数据输入端口;

input en_din_pro;//输入使能;

output[7:0] dout_pro;//指令执行结果;

output en_dout_pro;//指令输出使能;

output rdy;//串口发送模块空闲标志,0表示空闲;parameter add_ab=8'h0a;

parameter sub_ab=8'h0b;

parameter and_ab=8'h0c;

parameter or_ab =8'h0d;reg[2:0] state;//主状态机寄存器

reg[7:0] cmd_reg,A_reg,B_reg;//存放指令、A和B;

reg[7:0] dout_pro;

reg en_dout_pro;always@(posedge clk or negedge res)begin

if(~res)beginstate<=0;cmd_reg<=0;A_reg<=0;B_reg<=0;dout_pro<=0;en_dout_pro<=0;

end

else begincase(state)0://等指令;beginen_dout_pro<=0;if(en_din_pro)begincmd_reg<=din_pro;state<=1;endend1://收Abeginif(en_din_pro)beginA_reg<=din_pro;state<=2;endend2://收Bbeginif(en_din_pro)beginB_reg<=din_pro;state<=3;endend3://指令译码和执行;beginstate<=4;//指令译码一个时钟周期就可以,所以可以没条件case(cmd_reg)add_ab: begin dout_pro<=A_reg+B_reg; endsub_ab: begin dout_pro<=A_reg-B_reg; endand_ab: begin dout_pro<=A_reg&B_reg; endor_ab: begin dout_pro<=A_reg|B_reg; endendcaseend4://发送指令执行结果;beginif(~rdy)beginen_dout_pro<=1;state<=0;endenddefault://beginstate<=0;en_dout_pro<=0;endendcase

end

endmodule

//2023-09-19,time

//串口指令处理器;

`timescale 1ns/10ps

module UART_top(clk,res,RX,TX);

input clk;

input res;

input RX;

output TX;wire[7:0] din_pro;

wire en_din_pro;

wire[7:0] dout_pro;

wire en_dout_pro;

wire rdy;UART_RXer UART_RXer( .clk(clk),.res(res),.RX(RX),.data_out(din_pro),.en_data_out(en_din_pro));UART_TXer UART_TXer( .clk(clk),.res(res),.data_in(dout_pro),.en_data_in(en_data_),.TX(TX),.rdy(rdy));cmd_pro cmd_pro(.clk(clk),.res(res),.din_pro(din_pro),.en_din_pro(en_din_pro),.dout_pro(dout_pro),.en_dout_pro(en_dout_pro),.rdy(rdy));

endmodule //-------testbench of UART_top------

module UART_top_tb;

reg clk,res;

wire RX;

wire TX;reg[45:0] RX_send;//里面装有串口字节发送数据

assign RX=RX_send[0];//连接RX;reg[12:0] con;UART_top UART_top(clk,res,RX,TX);initial beginclk<=0;res<=0;RX_send<={1'b1,8'h09,1'b0,1'b1,8'h06,1'b0,1'b1,8'h0a,1'b0,16'hffff};con<=0;#17 res<=1;#4000000 $stop;

endalways #5 clk<=~clk;always@(posedge clk) beginif(con==5000-1)begincon<=0;endelse begincon<=con+1;endif(con==0)beginRX_send[44:0]<=RX_send[45:1];RX_send[45]<=RX_send[0];endend

endmodule

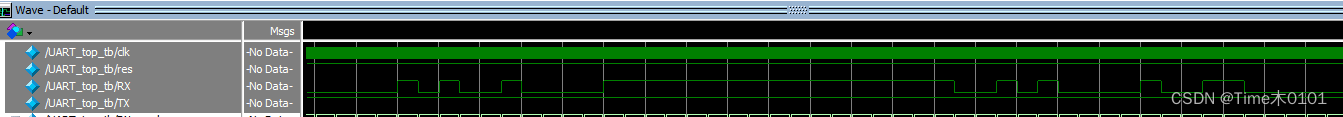

仿真波形:

小结:

相关文章:

Verilog零基础入门(边看边练与测试仿真)-状态机-笔记(7-10讲)

文章目录 第七讲第八讲第九讲第十讲 第七讲 1、最简单的状态机-三角波发生器 1、两种状态的代码: //最简单的状态机,三角波发生器; timescale 1ns/10ps module tri_gen(clk,res,d_out); input clk; input res; o…...

【Hadoop】HDFS API 操作大全

🍁 博主 "开着拖拉机回家"带您 Go to New World.✨🍁 🦄 个人主页——🎐开着拖拉机回家_Linux,大数据运维-CSDN博客 🎐✨🍁 🪁🍁 希望本文能够给您带来一定的帮助…...

Webpack打包图片

一、在js文件中引入图片 二、在package.config.js中配置加载器 module.exports {mode: "production", // 设置打包的模式:production生产模式 development开发模式module: {rules: [// 配置img加载器{test: /\.(jpg|png|gif)$/i,type:"asset/resou…...

DipC 构建基因组 3D 结构(学习笔记)

背景 本文主要记录了 DipC 数据的复现过程、学习笔记及注意事项。 目录 下载 SRA 数据使用 SRA Toolkit 转换 SRA 数据为 Fastq 格式使用 bwa 比对测序数据使用 Hickit 计算样本的基因组 3D 结构使用散点图展示 3D 结构计算 3D 结构重复模拟的稳定性其他 步骤 1. 下载 SRA…...

Qt中音频的使用

对于音频我们在使用的过程中一般是录制音频、播放音频。针对这两个需求介绍Qt中音频的使用。 Qt中音频的录制 步骤: 1、获取系统中的音频设备。 2、创建QAudioRecorder对象,指定使用的音频设备,通过QAudioRecorder的setAudioInput函数设置…...

[centos]centos7源码编译cmake报错Could NOT find OpenSSL

测试环境: centos7.9 cmake3.25.0 ./bootstrap以后报错如下: Could NOT find OpenSSL, try to set the path to OpenSSL root folder in the system variable OPENSSL_ROOT_DIR (missing: OPENSSL_CRYPTO_LIBRARY OPENSSL_INCLUDE_DIR) CMake Error …...

vue若依前端项目搭建

1.项目搭建 首先进入到你需要创建的项目目录下面,然后输入命令vue create .创建项目 接下来选择手动搭建,然后把下面图片中的内容选上 再然后继续配置一些参数信息 接下来运行npm run serve项目就启动起来了 2.配置登录界面文件 首先修改src/router…...

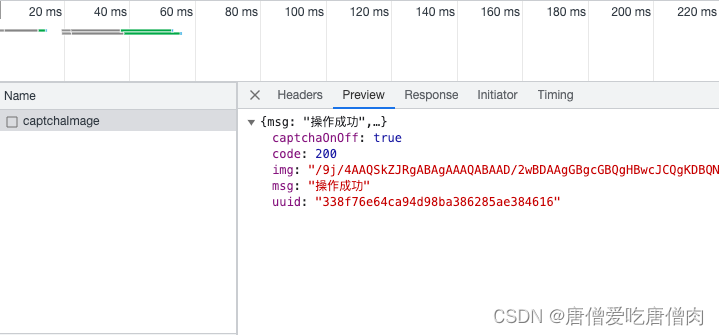

基于win32实现TB登陆滑动验证

这里写目录标题 滑动验证触发条件:失败条件:解决方法:清除cooKie 滑动验证方式一:win32 api获取窗口句柄,选择固定位置 成功率高方式二: 原自动化滑动,成功率中 案例 先谈理论,淘宝 taobao.com …...

vue学习-07todoList案例与浏览器本地存储

TodoList Todo List(任务列表)是一个简单的Web应用程序示例,用于管理任务、代办事项或清单。Vue.js 是一个非常适合构建这种类型应用程序的框架,因为它提供了数据绑定、组件化、响应式和轻松管理用户界面的能力。 以下是一个基本…...

探索智能应用的基石:多模态大模型赋能文档图像处理

目录 0 写在前面1 文档图像分析新重点2 token荒:电子文档助力大模型3 大模型赋能智能文档分析4 文档图像大模型应用可能性4.1 专有大模型4.2 多模态模型4.3 设计思路 总结 0 写在前面 中国智能产业高峰论坛(CIIS2023)旨在为政企研学各界学者专家提供同台交流的机会…...

自动化发布npm包小记

1.注册npm账号 打开npm官网,并注册自己的npm账号 2.申请AccessToken 1.登录npm官网,登录成功后,点开右上角头像,并点击Access Tokens选项 2.点开Generate New Token下拉框,点击Classic Token(和Granular Access To…...

详解机器视觉性能指标相关概念——混淆矩阵、IoU、ROC曲线、mAP等

目录 0. 前言 1. 图像分类性能指标 1.1 混淆矩阵(Confusion Matrix) 1.2 准确率(Precision) 1.3 召回率(Recall) 1.4 F1值(F1 score) 1.5 ROC曲线(接收者工作特征曲线,Receiver Operating Characteristic curve) 1.6 mAP(mean Average Precision) 2. 图像分…...

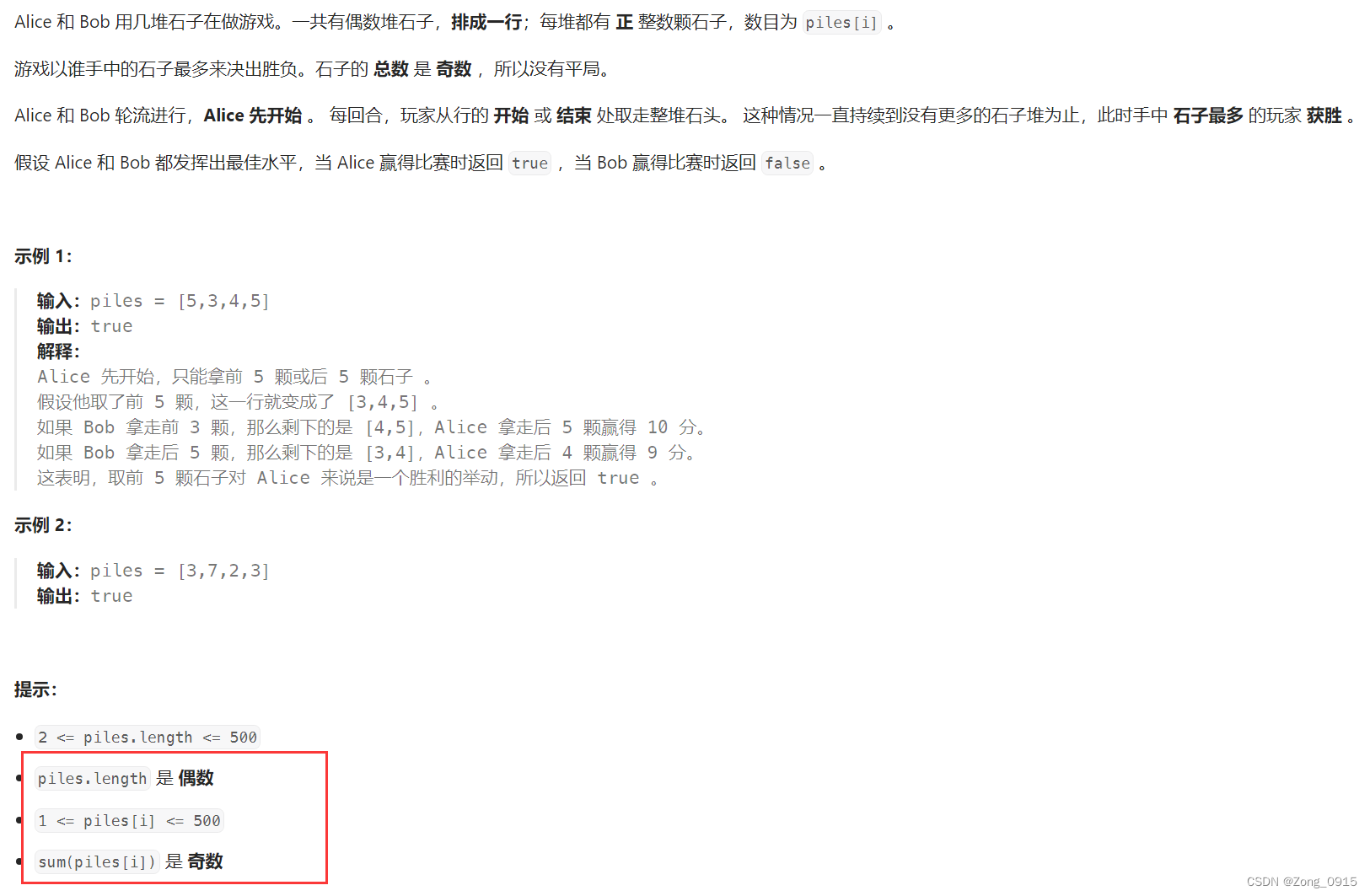

想要精通算法和SQL的成长之路 - 预测赢家

想要精通算法和SQL的成长之路 - 预测赢家 前言一. 预测赢家二. 石子游戏(预测赢家的进阶版)2.1 博弈论 前言 想要精通算法和SQL的成长之路 - 系列导航 一. 预测赢家 原题链接 主要思路: 我们定义dp[i][j]:在区间 [i, j] 之间先…...

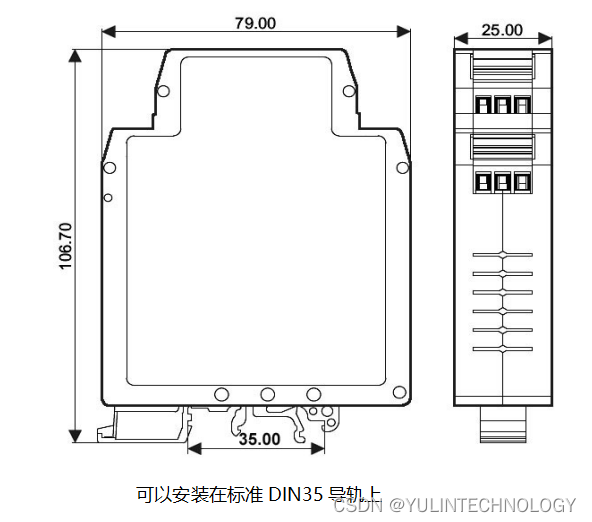

高精度PWM脉宽调制信号转模拟信号隔离变送器1Hz~10KHz转0-5V/0-10V/1-5V/0-10mA/0-20mA/4-20mA

主要特性: >>精度等级:0.1级。产品出厂前已检验校正,用户可以直接使用 >>辅助电源:8-32V 宽范围供电 >>PWM脉宽调制信号输入: 1Hz~10KHz >>输出标准信号:0-5V/0-10V/1-5V,0-10mA/0-20mA/4-20mA等&…...

Vue路由和Node.js环境搭建

文章目录 一、vue路由1.1 简介1.2 SPA1.3 实例 二、Node.js环境搭建2.1 Node.js简介2.2 npm2.3 环境搭建2.3.1 下载解压2.3.2 配置环境变量2.3.3 配置npm全局模块路径和cache默认安装位置2.3.4 修改npm镜像提高下载速度 2.4 运行项目 一、vue路由 1.1 简介 Vue 路由是 Vue.js…...

【Vue】使用vue-cli搭建SPA项目的路由,嵌套路由

一、SPA项目的构建 1、前期准备 我们的前期的准备是搭建好Node.js,测试: node -v npm -v2、利用Vue-cli来构建spa项目 2.1、什么是Vue-cli Vue CLI 是一个基于 Vue.js 的官方脚手架工具,用于自动生成vue.jswebpack的项目模板,它可以帮助开发者…...

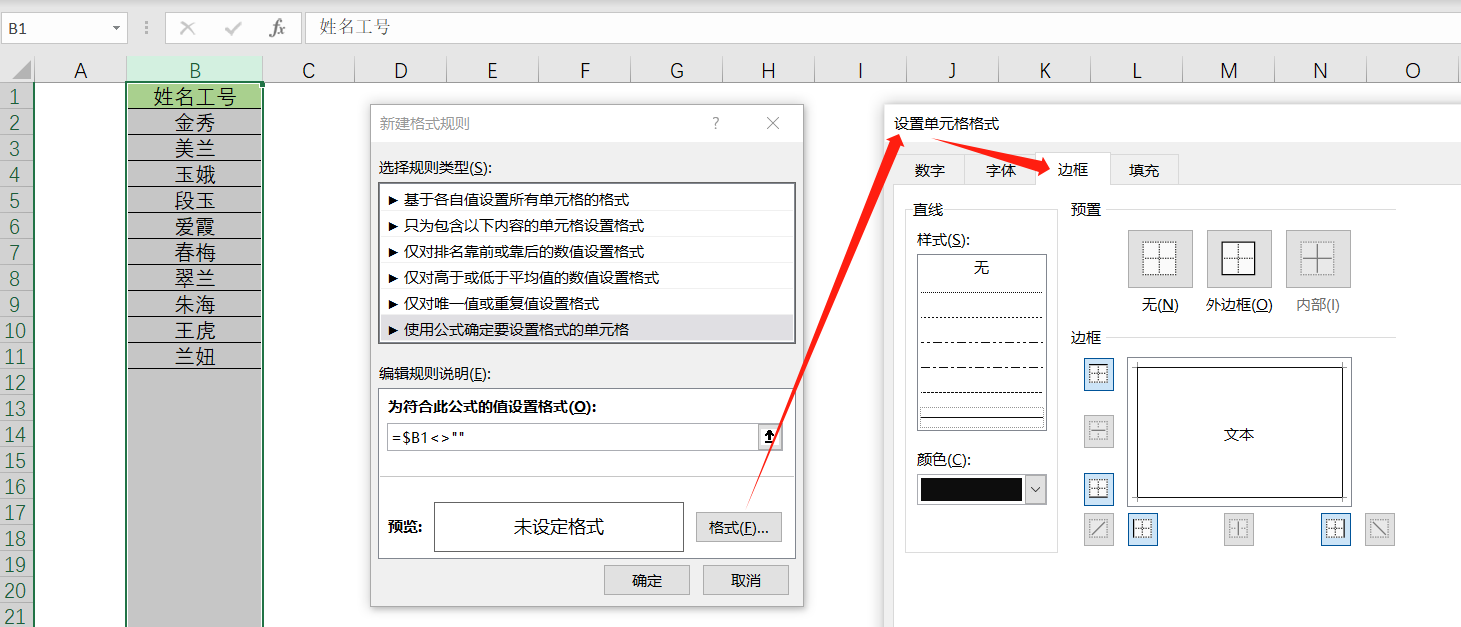

Excel 通过条件格式自动添加边框

每录入一次数据就需要手动添加一次边框,非常麻烦,这不是我们想要的。 那么有没有办法,在我们录入数据后,自动帮我们加上边框呢? 选中要自动添加边框的列,然后按箭头流程操作 ↓ ↓ ↓ ↓...

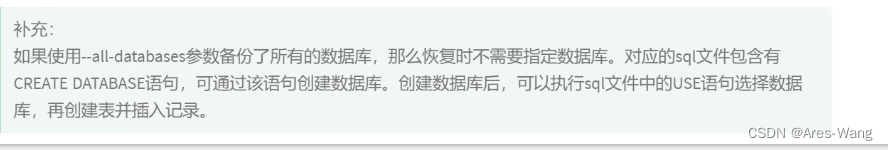

mysql 备份和还原 mysqldump

因window系统为例 在mysql安装目录中的bin目录下 cmd 备份 备份一个数据库 mysqldump -uroot -h hostname -p 数据库名 > 备份的文件名.sql 备份部分表 mysqldump -uroot -h hostname -p 数据库名 [表 [表2…]] > 备份的文件名.sql ## 多个表 空格隔开,中间…...

ELK日志分析系统+ELFK(Filebeat)

本章结构: 1、ELK日志分析系统简介 2、Elasticsearch介绍(简称ES) 3、Logstash介绍 4、Kibana介绍 5、实验,ELK部署 一、ELK日志分析系统简介 ELK平台是一套完整的日志集中处理解决方案,将 ElasticSearch、Logst…...

ULID 在 Java 中的应用: 使用 `getMonotonicUlid` 生成唯一标识符

🌷🍁 博主猫头虎 带您 Go to New World.✨🍁 🦄 博客首页——猫头虎的博客🎐 🐳《面试题大全专栏》 文章图文并茂🦕生动形象🦖简单易学!欢迎大家来踩踩~🌺 &a…...

基于物理信息神经网络与降阶模型的文物数字孪生保护框架

1. 项目概述:当文化遗产保护遇上科学计算与人工智能最近几年,我一直在关注一个交叉领域:如何用前沿的计算科学和人工智能技术,去解决那些看似传统、实则充满挑战的文物保护难题。这次分享的“基于SciML与数字孪生的文化遗产保护框…...

基于双链笔记构建个人消费知识系统:从记录到生活策展

1. 项目概述与核心价值看到“SimonsTang/xiaofei-liberal-arts”这个项目标题,我的第一反应是,这应该是一个关于“消费”与“文科”交叉领域的知识库或工具集。作为一名长期关注效率工具和知识管理的从业者,我深知在信息爆炸的时代࿰…...

抖音下载器终极指南:从零开始掌握无水印批量下载技巧

抖音下载器终极指南:从零开始掌握无水印批量下载技巧 【免费下载链接】douyin-downloader A practical Douyin downloader for both single-item and profile batch downloads, with progress display, retries, SQLite deduplication, and browser fallback suppor…...

Hermes Agent 可视化监控与文档生成工具 hermes-dashboard 详解

1. 项目概述与核心价值如果你正在使用 Hermes Agent 进行 AI 智能体开发,或者对 Agent 的内部运行状态感到好奇,那么你很可能需要一个“上帝视角”。hermes-dashboard正是这样一个工具,它为你提供了一个实时的监控仪表盘和一个自动生成的、可…...

传统认为越早进入行业越占优势,编程统计入行时间,行业红利数据,行业成熟期入行风险更低收益更稳。

“入行时间与行业红利期的匹配关系分析” 为主题,给出一套工程化、可教学、可复现的分析示例。一、实际应用场景描述(Business Context)在职业规划、行业研究与人才策略中,普遍存在一种观点:“越早进入一个行业&#x…...

Docker Desktop 快速搭建本地 Kubernetes 集群:解决镜像拉取与生态集成

1. 项目概述:在本地桌面环境快速搭建K8s生态 如果你是一名开发者或者运维工程师,想在自己的Mac或Windows电脑上快速体验和学习Kubernetes(K8s)及其周边生态,比如Istio服务网格、Helm包管理器,那么Docker D…...

的配置策略与索引选择)

告别盲选!深入解读5G NR中UCI偏置值(beta_offset)的配置策略与索引选择

5G NR中UCI偏置值配置的工程实践指南 在5G新空口(NR)系统中,上行控制信息(UCI)通过物理上行共享信道(PUSCH)传输时,其资源分配直接影响到系统性能和用户体验。作为网络优化工程师,我们经常需要面对各种复杂的配置场景,而UCI偏置值…...

从FinFET到3D-IC:2013年预测如何塑造了今天的低功耗与异构计算设计

1. 项目概述:站在2013年初的十字路口十多年前,2013年初的那个冬天,整个半导体与电子设计自动化行业弥漫着一种既兴奋又焦虑的复杂情绪。当时,我作为行业里的一名技术编辑,向数十位来自芯片设计公司、EDA工具供应商、IP…...

OpenClaw vs Hermes Agent,谁是 2026 年 AI Agent 最优解?

OpenClaw+Hermes 全集成,一键调用所有 AI 技能:https://ai-skills.ai/?inviteCode=S2JV3NCK 前言 2026 年,AI Agent 已从 “实验玩具” 迈入 “工程化落地” 关键期。GitHub 上 OpenClaw 与 Hermes Agent 两大开源项目热度飙升,均宣称解决大模型 “失忆、弱执行、难沉淀”…...

PiliPlus:如何用第三方B站客户端解锁终极观影体验?

PiliPlus:如何用第三方B站客户端解锁终极观影体验? 【免费下载链接】PiliPlus PiliPlus 项目地址: https://gitcode.com/gh_mirrors/pi/PiliPlus 你是否厌倦了官方B站客户端的广告轰炸?是否想要更纯净、更流畅的观影体验?P…...