【Verilog 教程】6.6Verilog 仿真激励

关键词:testbench,仿真,文件读写

Verilog 代码设计完成后,还需要进行重要的步骤,即逻辑功能仿真。仿真激励文件称之为 testbench,放在各设计模块的顶层,以便对模块进行系统性的例化调用进行仿真。

毫不夸张的说,对于稍微复杂的 Verilog 设计,如果不进行仿真,即便是经验丰富的老手,99.9999% 以上的设计都不会正常的工作。不能说仿真比设计更加的重要,但是一般来说,仿真花费的时间会比设计花费的时间要多。有时候,考虑到各种应用场景,testbench 的编写也会比 Verilog 设计更加的复杂。所以,数字电路行业会具体划分设计工程师和验证工程师。

下面,对 testbench 做一个简单的学习。

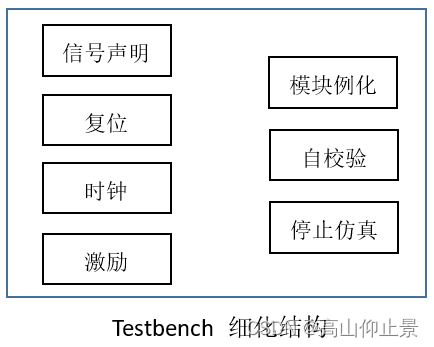

testbench 结构划分

testbench 一般结构如下:

其实 testbench 最基本的结构包括信号声明、激励和模块例化。

根据设计的复杂度,需要引入时钟和复位部分。当然更为复杂的设计,激励部分也会更加复杂。根据自己的验证需求,选择是否需要自校验和停止仿真部分。

当然,复位和时钟产生部分,也可以看做激励,所以它们都可以在一个语句块中实现。也可以拿自校验的结果,作为结束仿真的条件。

实际仿真时,可以根据自己的个人习惯来编写 testbench,这里只是做一份个人的总结。

testbench 仿真举例

前面的章节中,已经写过很多的 testbench。其实它们的结构也都大致相同。

下面,我们举一个数据拼接的简单例子,对 testbench 再做一个具体的分析。

一个 2bit 数据拼接成 8bit 数据的功能模块描述如下:

实例

module data_consolidation(input clk ,input rstn ,input [1:0] din , //data ininput din_en ,output [7:0] dout ,output dout_en //data out);// data shift and counterreg [7:0] data_r ;reg [1:0] state_cnt ;always @(posedge clk or negedge rstn) beginif (!rstn) beginstate_cnt <= 'b0 ;data_r <= 'b0 ;endelse if (din_en) beginstate_cnt <= state_cnt + 1'b1 ; //数据计数data_r <= {data_r[5:0], din} ; //数据拼接endelse beginstate_cnt <= 'b0 ;endendassign dout = data_r ;// data output enreg dout_en_r ;always @(posedge clk or negedge rstn) beginif (!rstn) begindout_en_r <= 'b0 ;end//计数为 3 且第 4 个数据输入时,同步输出数据输出使能信号else if (state_cnt == 2'd3 & din_en) begin dout_en_r <= 1'b1 ;endelse begindout_en_r <= 1'b0 ;endend//这里不直接声明dout_en为reg变量,而是用相关寄存器对其进行assign赋值assign dout_en = dout_en_r;endmodule

对应的 testbench 描述如下,增加了文件读写的语句:

实例

`timescale 1ns/1ps//============== (1) ==================//signals declaration

module test ;reg clk;reg rstn ;reg [1:0] din ;reg din_en ;wire [7:0] dout ;wire dout_en ;//============== (2) ==================//clock generatingreal CYCLE_200MHz = 5 ; //always beginclk = 0 ; #(CYCLE_200MHz/2) ;clk = 1 ; #(CYCLE_200MHz/2) ;end//============== (3) ==================//reset generatinginitial beginrstn = 1'b0 ;#8 rstn = 1'b1 ;end//============== (4) ==================//motivationint fd_rd ;reg [7:0] data_in_temp ; //for self checkreg [15:0] read_temp ; //8bit ascii data, 8bit \ninitial begindin_en = 1'b0 ; //(4.1)din = 'b0 ;open_file("../tb/data_in.dat", "r", fd_rd); //(4.2)wait (rstn) ; //(4.3)# CYCLE_200MHz ;//read data from filewhile (! $feof(fd_rd) ) begin //(4.4)@(negedge clk) ;$fread(read_temp, fd_rd);din = read_temp[9:8] ;data_in_temp = {data_in_temp[5:0], din} ;din_en = 1'b1 ;end//stop data@(posedge clk) ; //(4.5)#2 din_en = 1'b0 ;end//open tasktask open_file;input string file_dir_name ;input string rw ;output int fd ;fd = $fopen(file_dir_name, rw);if (! fd) begin$display("--- iii --- Failed to open file: %s", file_dir_name);endelse begin$display("--- iii --- %s has been opened successfully.", file_dir_name);endendtask//============== (5) ==================//module instantiationdata_consolidation u_data_process(.clk (clk),.rstn (rstn),.din (din),.din_en (din_en),.dout (dout),.dout_en (dout_en));//============== (6) ==================//auto checkreg [7:0] err_cnt ;int fd_wr ;initial beginerr_cnt = 'b0 ;open_file("../tb/data_out.dat", "w", fd_wr);forever begin@(negedge clk) ;if (dout_en) begin$fdisplay(fd_wr, "%h", dout);endendendalways @(posedge clk) begin#1 ;if (dout_en) beginif (data_in_temp != dout) beginerr_cnt = err_cnt + 1'b1 ;endendend//============== (7) ==================//simulation finishalways begin#100;if ($time >= 10000) beginif (!err_cnt) begin$display("-------------------------------------");$display("Data process is OK!!!");$display("-------------------------------------");endelse begin$display("-------------------------------------");$display("Error occurs in data process!!!");$display("-------------------------------------");end#1 ;$finish ;endendendmodule // test

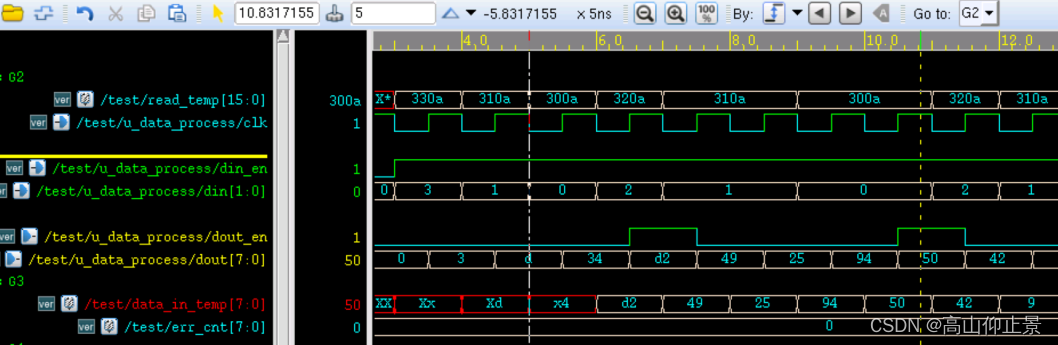

仿真结果如下。由图可知,数据整合功能的设计符合要求:加粗样式

testbench 具体分析

1)信号声明

testbench 模块声明时,一般不需要声明端口。因为激励信号一般都在 testbench 模块内部,没有外部信号。

声明的变量应该能全部对应被测试模块的端口。当然,变量不一定要与被测试模块端口名字一样。但是被测试模块输入端对应的变量应该声明为 reg 型,如 clk,rstn 等,输出端对应的变量应该声明为 wire 型,如 dout,dout_en。

2)时钟生成

生成时钟的方式有很多种,例如以下两种生成方式也可以借鉴。

实例

initial clk = 0 ;

always #(CYCLE_200MHz/2) clk = ~clk;initial beginclk = 0 ;forever begin#(CYCLE_200MHz/2) clk = ~clk;end

end

需要注意的是,利用取反方法产生时钟时,一定要给 clk 寄存器赋初值。

利用参数的方法去指定时间延迟时,如果延时参数为浮点数,该参数不要声明为 parameter 类型。例如实例中变量 CYCLE_200MHz 的值为 2.5。如果其变量类型为 parameter,最后生成的时钟周期很可能就是 4ns。当然,timescale 的精度也需要提高,单位和精度不能一样,否则小数部分的时间延迟赋值也将不起作用。

3)复位生成

复位逻辑比较简单,一般赋初值为 0,再经过一段小延迟后,复位为 1 即可。

这里大多数的仿真都是用的低有效复位。

4)激励部分

激励部分该产生怎样的输入信号,是根据被测模块的需要来设计的。

本次实例中:

(4.1) 对被测模块的输入信号进行一个初始化,防止不确定值 X 的出现。激励数据的产生,我们需要从数据文件内读入。

(4.2) 处利用一个 task 去打开一个文件,只要指定文件存在,就可以得到一个不为 0 的句柄信号 fp_rd。fp_rd 指定了文件数据的起始地址。

(4.3) 的操作是为了等待复位后,系统有一个安全稳定的可测试状态。

(4.4) 开始循环读数据、给激励。在时钟下降沿送出数据,是为了被测试模块能更好的在上升沿采样数据。

利用系统任务 $fread ,通过句柄信号 fd_rd 将读取的 16bit 数据变量送入到 read_temp 缓存。

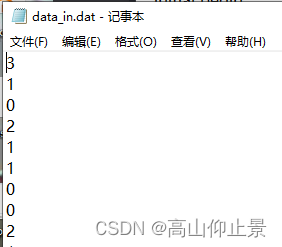

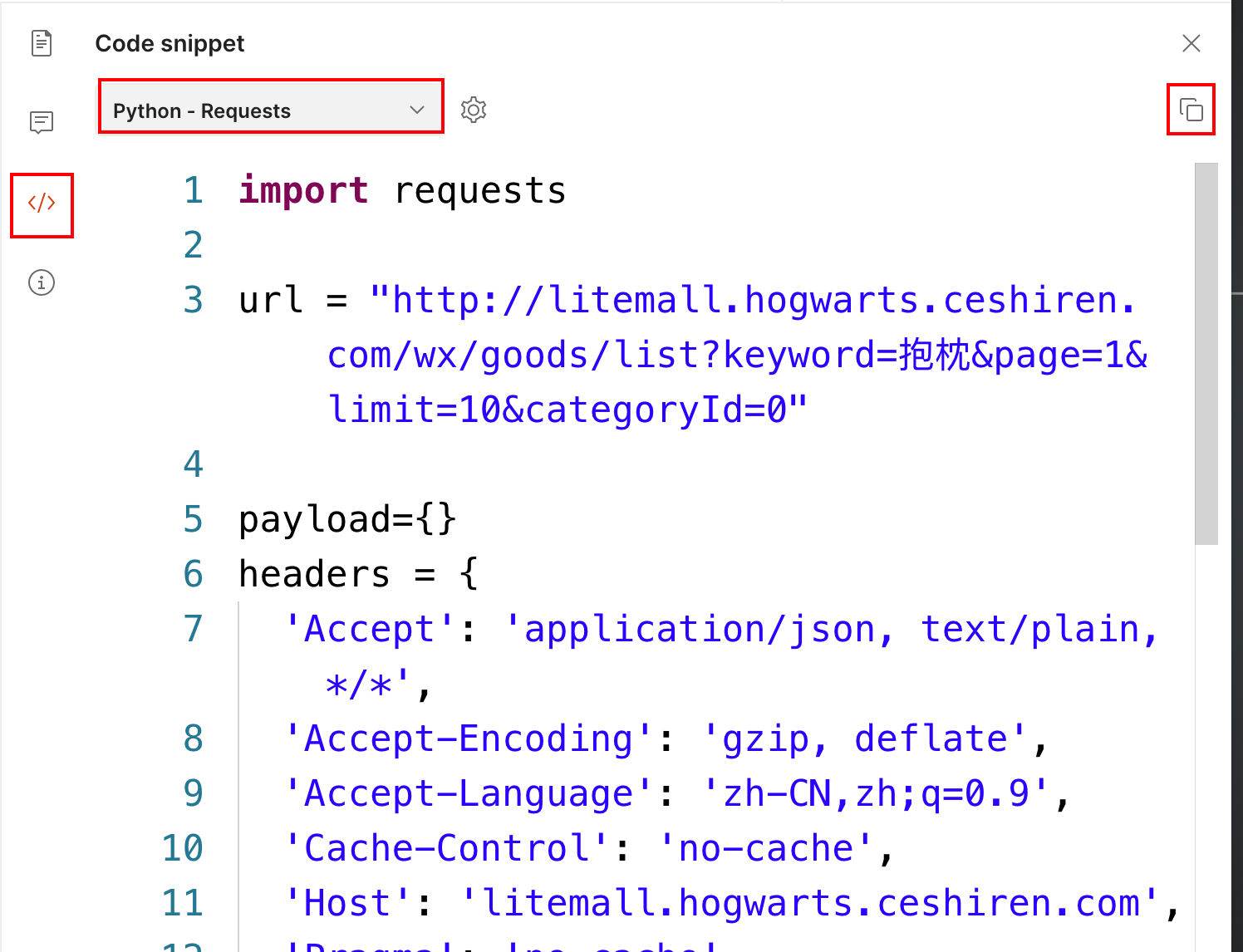

输入数据文件前几个数据截图如下。因为 $fread 只能读取 2 进制文件,所以输入文件的第一行对应的 ASCII 码应该是 330a,所以我们想要得到文件里的数据 3,应该取变量 read_temp 的第 9 到第 8bit 位的数据。

信号 data_in_temp 是对输入数据信号的一个紧随的整合,后面校验模块会以此为参考,来判断仿真是否正常,模块设计是否正确。

(4.5) 选择在时钟上升沿延迟 2 个周期后停止输入数据,是为了被测试模块能够正常的采样到最后一个数据使能信号,并对数据进行正常的整合。

当数据量相对较少时,可以利用 Verilog 中的系统任务 $readmemh 来按行直接读取 16 进制数据。保持文件 data_in.dat 内数据和格式不变,则该激励部分可以描述为:

实例

reg [1:0] data_mem [39:0] ;

reg [7:0] data_in_temp ; //for self check

integer k1 ;

initial begin

din_en = 1’b0 ;

din = 'b0 ;

$readmemh(“…/tb/data_in.dat”, data_mem);

wait (rstn) ;

# CYCLE_200MHz ;

//read data from file

for(k1=0; k1<40; k1=k1+1) begin@(negedge clk) ;din = data_mem[k1] ;data_in_temp = {data_in_temp[5:0], din} ;din_en = 1'b1 ;

end//stop data

@(posedge clk) ;

#2 din_en = 1'b0 ;

end

5)模块例化

这里利用 testbench 开始声明的信号变量,对被测试模块进行例化连接。

6)自校验

如果设计比较简单,完全可以通过输入、输出信号的波形来确定设计是否正确,此部分完全可以删除。如果数据很多,有时候拿肉眼观察并不能对设计的正确性进行一个有效判定。此时加入一个自校验模块,会大大增加仿真的效率。

实例中,我们会在数据输出使能 dout_en 有效时,对输出数据 dout 与参考数据 read_temp(激励部分产生)做一个对比,并将对比结果置于信号 err_cnt 中。最后就可以通过观察 err_cnt 信号是否为 0 来直观的对设计的正确性进行判断。

当然如实例中所示,我们也可以将数据写入到对应文件中,利用其他方式做对比。

7)结束仿真

如果我们不加入结束仿真部分,仿真就会无限制的运行下去,波形太长有时候并不方便分析。Verilog 中提供了系统任务 $finish 来停止仿真。

停止仿真之前,可以将自校验的结果,通过系统任务 $display 在终端进行显示。

文件读写选项

用于打开文件的系统任务 $fopen 格式如下:

fd = $fopen("<name_of_file>", "mode")

和 C 语言类似,打开方式的选项 “mode” 意义如下:

相关文章:

【Verilog 教程】6.6Verilog 仿真激励

关键词:testbench,仿真,文件读写 Verilog 代码设计完成后,还需要进行重要的步骤,即逻辑功能仿真。仿真激励文件称之为 testbench,放在各设计模块的顶层,以便对模块进行系统性的例化调用进行仿真…...

Win/Mac版Scitools Understand教育版申请

这里写目录标题 前言教育版申请流程教育账号申请 前言 上篇文章为大家介绍了Scitools Understand软件,通过领取的反馈来看有很多朋友都想用这个软件,但是我的网盘里只存了windows的pojie版,没有mac版的,我没有去网上找相关的资源…...

第十四届蓝桥杯大赛软件赛决赛 C/C++ 大学 B 组 试题 C: 班级活动

[蓝桥杯 2023 国 B] 班级活动 【问题描述】 小明的老师准备组织一次班级活动。班上一共有 n n n 名( n n n 为偶数)同学,老师想把所有的同学进行分组,每两名同学一组。为了公平,老师给每名同学随机分配了一个 n n …...

YOLOv8改进新颖的Gather-and-Distribute机制,低阶高阶新颖融合,增强了多尺度特征融合能力,实现了延迟和准确性的理想平衡

💡本篇内容:YOLOv8改进新颖的Gather-and-Distribute机制,低阶高阶新颖融合,增强了多尺度特征融合能力,实现了延迟和准确性的理想平衡 💡🚀🚀🚀本博客 改进源代码改进 适用于 YOLOv8 按步骤操作运行改进后的代码即可 💡本文提出改进 原创 方式:二次创新,YOL…...

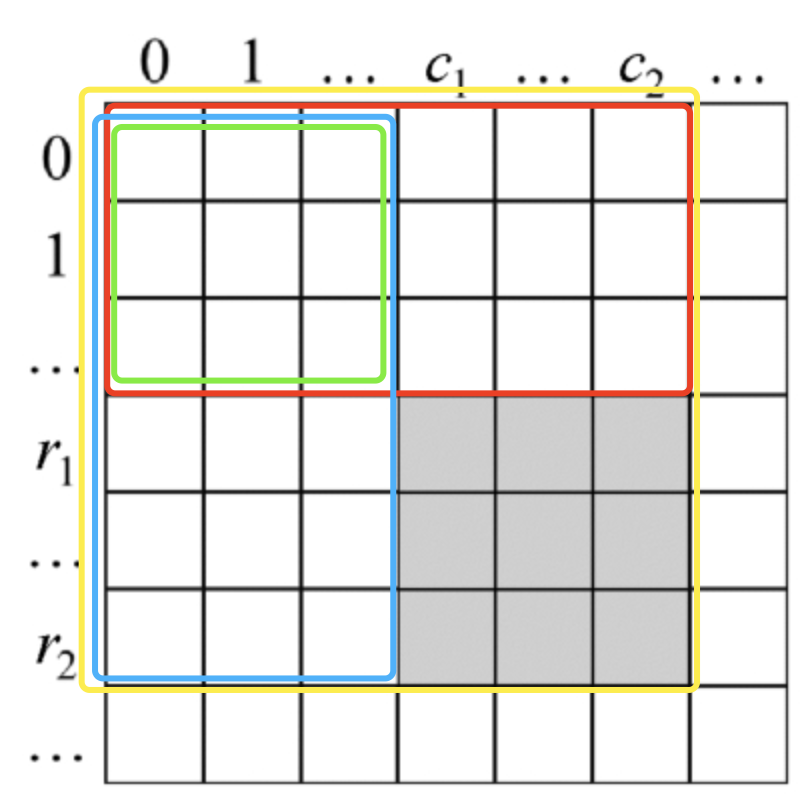

面试算法13:二维子矩阵的数字之和

题目 输入一个二维矩阵,如何计算给定左上角坐标和右下角坐标的子矩阵的数字之和?对于同一个二维矩阵,计算子矩阵的数字之和的函数可能由于输入不同的坐标而被反复调用多次。例如,输入图2.1中的二维矩阵,以及左上角坐标…...

Vue安装插件时候中遇到冲突依赖解决方案

错误如下: npm ERR! code ERESOLVE npm ERR! ERESOLVE could not resolve npm ERR! npm ERR! While resolving: vue/eslint-config-standard6.1.0 npm ERR! Found: eslint-plugin-vue8.7.1 npm ERR! node_modules/eslint-plugin-vue npm ERR! dev eslint-pl…...

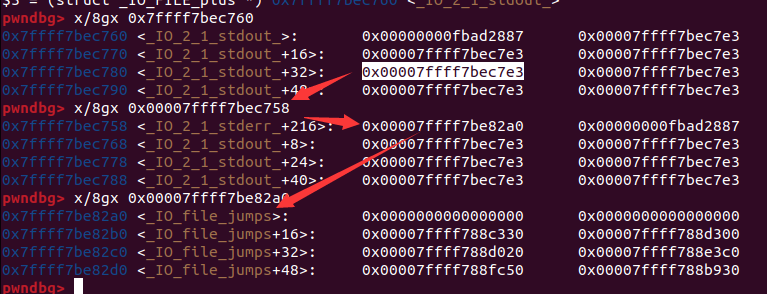

realloc函数应用IO泄露体验

本题主要介绍realloc函数,平时我们使用realloc最多便是在打malloc_hook–>onegadget的时候,使用realloc_hook调整onegadget的栈帧,从而getshell。 在realloc函数中,也能像malloc一样创建堆,并且比malloc麻烦一些&a…...

野指针)

(c语言)野指针

#include<stdio.h> //野指针 int* test() { int a 10; return &a; } int main() { //野指针一: int* p; *p 10; //非法访问内存 //p没有初始化,就意味着没有明确的指向 //一个局部变量不初始化的话ÿ…...

【Git】轻松学会 Git(一):掌握 Git 的基本操作

文章目录 前言一、创建 Git 本地仓库1.1 什么是仓库1.2 创建本地仓库1.3 .git 目录结构 二、配置 Git三、认识 Git 的工作区、暂存区和版本库3.1 什么是 Git 的工作区、暂存区和版本库3.2 工作区、暂存区和版本库之间的关系 四、添加文件4.1 添加文件到暂存区和版本库中的命令4…...

rust trait对象

在拥有继承的语言中,可以定义一个名为shape的基类,该类上有一个draw方法。其他的类比如Button、SelectBox继承shape。它们各自覆盖draw方法。调用这些子类的draw方法时,就可以把它们统一当作shape来使用。不过Rust并没有继承,如果…...

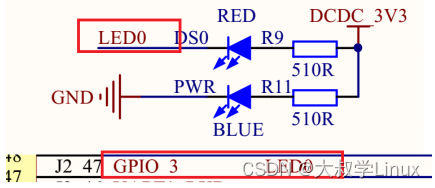

Linux学习第21天:Linux内核定时器驱动开发: 流淌的时间长河

Linux版本号4.1.15 芯片I.MX6ULL 大叔学Linux 品人间百味 思文短情长 在人类的发展进化中,时间是一个非常重要神秘的物质量。任何事物都是在时间的长河中流淌发生、发展、变化。我们进行驱动开发中对时间的定义和使用也是…...

Centos服务在服务器重启后自启

以Dolphin为例 打开rc.local文件以编辑: sudo vi /etc/rc.d/rc.local在文件中添加您的启动命令。在您的情况下,要添加的命令如下: sh /opt/dolphinscheduler/zookeeper/bin/zkServer.sh start sh /opt/dolphinscheduler/dolphinscheduler/…...

慢性疼痛治疗服务公司Kindly MD申请700万美元纳斯达克IPO上市

来源:猛兽财经 作者:猛兽财经 猛兽财经获悉,慢性疼痛治疗服务公司Kindly MD近期已向美国证券交易委员会(SEC)提交招股书,申请在纳斯达克IPO上市,股票代码为(KDLY),Kindly MD计划通过…...

代码随想录 Day6 哈希 LeetcodeT454 四数之和II T383赎金信 T15 三数之和 T18 四数之和

本文代码思路来源于: 代码随想录 前言 希望大家在刷这部分题的时候先熟悉熟悉哈希结构的基本常用api,比较方便理解. LeetCode T454 四数之和 题目链接:454. 四数相加 II - 力扣(LeetCode) 题目思路 暴力解法仍然是遍历四个数组解决此题, 哈希的思路有…...

干货速来|教你如何撰写毕业论文

撰写毕业论文对于正常大学毕业至关重要。毕业论文是对学生在大学期间所学知识的综合运用和深入研究的体现,也是对学术能力和独立思考能力的考验。 撰写毕业论文的过程需要学生投入大量的时间和精力,包括选题、文献综述、研究方法选择、数据收集和分析、…...

【ROS 2】-2 话题通信

飞书原文链接: Docs...

Unity之NetCode多人网络游戏联机对战教程(2)--简单实现联机

文章目录 1.添加基本组件2.创建NetworkManager组件3.创建Player4.创建地面5.创建GameManager6.编译运行7. 测试联机后话 1.添加基本组件 NetworkManagerPlayerScene 2.创建NetworkManager组件 创建一个空物体,命名为NetworkManager 选择刚刚创建的NetworkManager…...

makdown文法

这里写自定义目录标题 欢迎使用Markdown编辑器新的改变功能快捷键合理的创建标题,有助于目录的生成如何改变文本的样式插入链接与图片如何插入一段漂亮的代码片生成一个适合你的列表创建一个表格设定内容居中、居左、居右SmartyPants 创建一个自定义列表如何创建一个…...

新手程序员怎么接单?

程序员如何在自己年富力强的时候,最大化发挥自己的能力?将超能力转化为“钞能力”? 有人还在苦哈哈当老黄牛,一身使不完的牛劲,有人已经另辟蹊径,开创了自己的一片致富小天地。 接单找兼职,就…...

接口测试——接口协议抓包分析与mock_L2

目录: 抓包工具charles抓包工具fiddler抓包工具证书配置app抓包实战练习接口测试实战练习 1.抓包工具charles 工具介绍 支持 SSL 代理支持流量控制支持重发网络请求,方便后端调试支持修改网络请求参数支持网络请求的截获并动态修改可以自动将 json 或…...

VSCode 自动生成 Doxygen 格式注释

1. 插件下载 Visual Studio Code 上快捷生成 doxygen 格式注释需要使用插件,推荐插件:cschlosser.doxdocgen,插件名全称 :Doxygen Document Generator,如下图 插件下载地址:Doxygen Documentation Generat…...

高性能计算终极指南:使用LIKWID工具套件进行性能分析与优化

高性能计算终极指南:使用LIKWID工具套件进行性能分析与优化 【免费下载链接】likwid Performance monitoring and benchmarking suite 项目地址: https://gitcode.com/gh_mirrors/li/likwid 在当今的高性能计算(HPC)领域,性能监控与分析是提升计算…...

GraphQL-WS服务器配置:完整参数详解与最佳实践

GraphQL-WS服务器配置:完整参数详解与最佳实践 【免费下载链接】graphql-ws Coherent, zero-dependency, lazy, simple, GraphQL over WebSocket Protocol compliant server and client. 项目地址: https://gitcode.com/gh_mirrors/gr/graphql-ws GraphQL-WS…...

从架构到体验:友猫社区平台的全栈技术解析与功能体系详解

一、项目概述 友猫社区平台由宠友信息技术有限公司自主研发,是一套面向社区、社交、电商和即时通讯一体化的综合型系统。 平台采用前后端分离、Java微服务架构,配合VueUniApp多端适配方案,能够支持Web端、Android端与iOS端同步运行。 演示网…...

突然想写一些东西

---title: blogdate: 2026-05-15 02:18:57tags: ["chitchat"]about: 突然想写一些东西---马上毕业了,在写致谢的时候发现好像想写的东西挺多的,但是不知道怎么写出来了,可能是因为很久没写东西了?也可能是AI用多了自己深…...

3.【Python】Python3 数据类型转换

第一步:分析与整理数据类型转换1. 数据类型转换概述 数据类型转换分为两种: 隐式类型转换:Python 自动完成,无需干预。显式类型转换:使用内置函数手动转换。2. 隐式类型转换 规则:当不同类型的数据进行运算…...

)

千问 LeetCode 2402.会议室 III public int mostBooked(int n, int[][] meetings)

这道题是经典的会议室 III,核心是双堆模拟,一个堆管空闲会议室(按编号排序),一个堆管正在使用的会议室(按结束时间排序)。解题思路1. 排序:按会议开始时间升序排列。 2. 双堆初始化&…...

Go语言实现轻量级双向文件同步工具clawsync配置与实战

1. 项目概述:一个轻量级的文件同步利器在数据备份、多设备协同或者项目部署的场景里,文件同步是个绕不开的活儿。你可能用过rsync,功能强大但命令参数复杂;也可能试过syncthing,全平台覆盖但需要常驻后台服务。如果你在…...

京东自动抢购工具完整指南:5分钟学会Python自动化购物

京东自动抢购工具完整指南:5分钟学会Python自动化购物 【免费下载链接】autobuy-jd 使用python语言的京东平台抢购脚本 项目地址: https://gitcode.com/gh_mirrors/au/autobuy-jd 还在为京东秒杀抢不到心仪商品而烦恼吗?想要在促销活动中轻松抢购…...

BurpSuite汉化革命:打破语言壁垒,重塑中文安全测试体验

BurpSuite汉化革命:打破语言壁垒,重塑中文安全测试体验 【免费下载链接】BurpSuiteCN-Release BurpSuite汉化发布 项目地址: https://gitcode.com/gh_mirrors/bu/BurpSuiteCN-Release 在网络安全测试领域,Burp Suite无疑是渗透测试工…...