FPGA project : flash_erasure

SPI是什么:

SPI(Serial Peripheral Interface,串行外围设备接口)通讯协议,是Motorola公司提出的一种同步串行接口技术,是一种高速、全双工、同步通信总线,在芯片中只占用四根管脚用来控制及数据传输。

应用:EEPROM、Flash、RTC、ADC、DSP等。

优缺点:全双工通信,通讯方式较为简单,相对数据传输速率较快;没有应答机制确认数据是否接收,在数据可靠性上有一定缺陷(与I2C相比)。

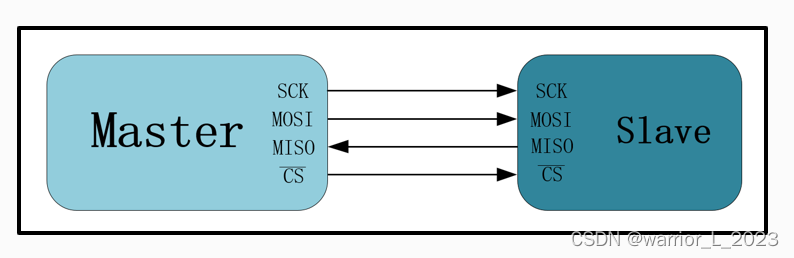

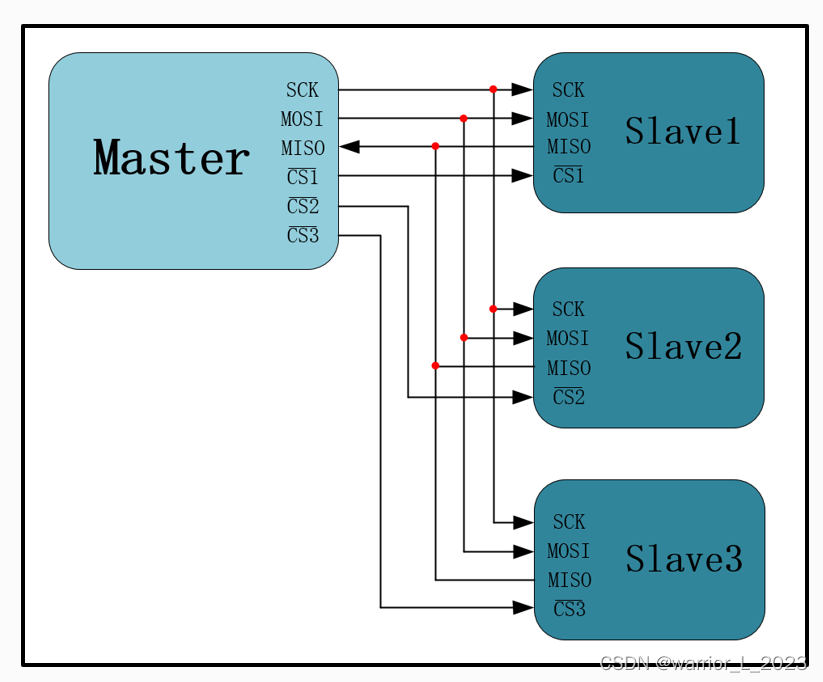

物理层:

SCK (Serial Clock):时钟信号线,用于同步通讯数据;

MOSI (Master Output, Slave Input):主设备输出/从设备输入引脚;

MISO (Master Input,Slave Output):主设备输入/从设备输出引脚;

𝐶𝑆(CS) ̅ (Chip Select):片选信号线,也称为CS_N。

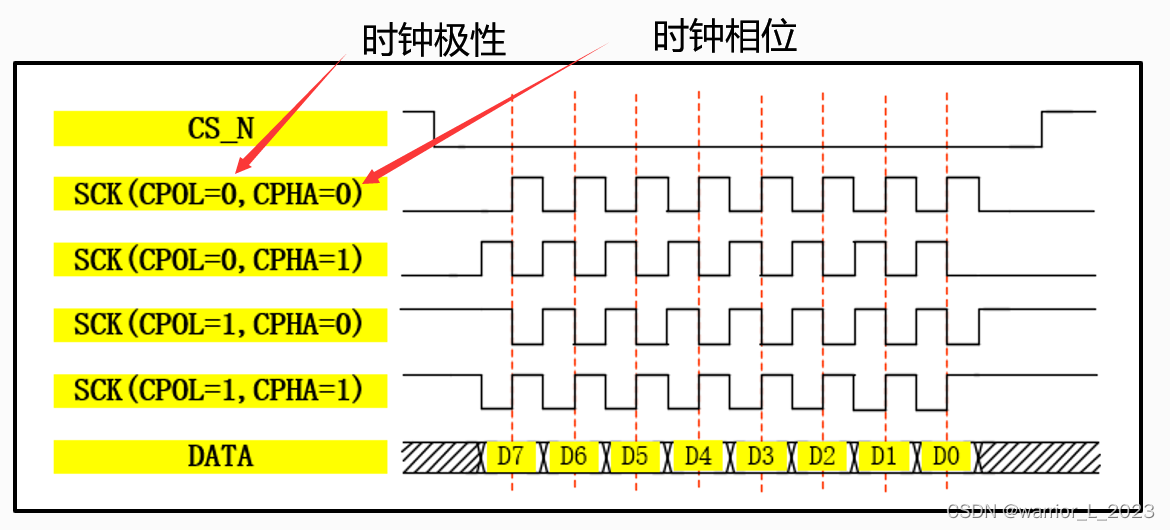

协议层:

spi通讯协议有四种模式:模式0和模式3,从设备在sck上升沿采样。

模式1和模式2在时钟下降沿采样。

模式0和模式1,在cs_n==1时,sck==0。

模式2和模式3,在cs_n==1时,sck==1。

比较常用的就是模式0和模式3。

flash相关资料:

芯片手册是必须要看的。

模块框图:

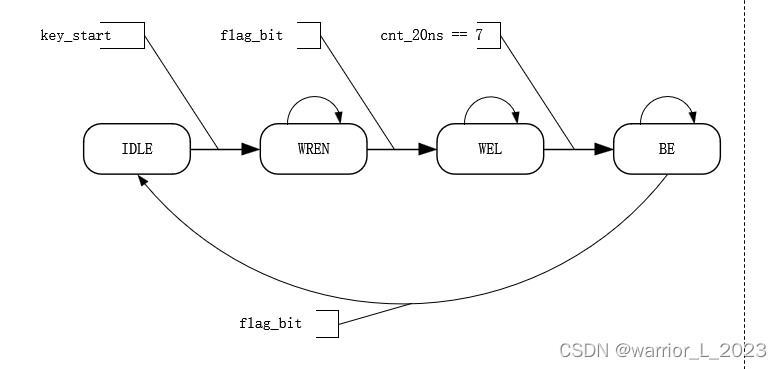

状态机:

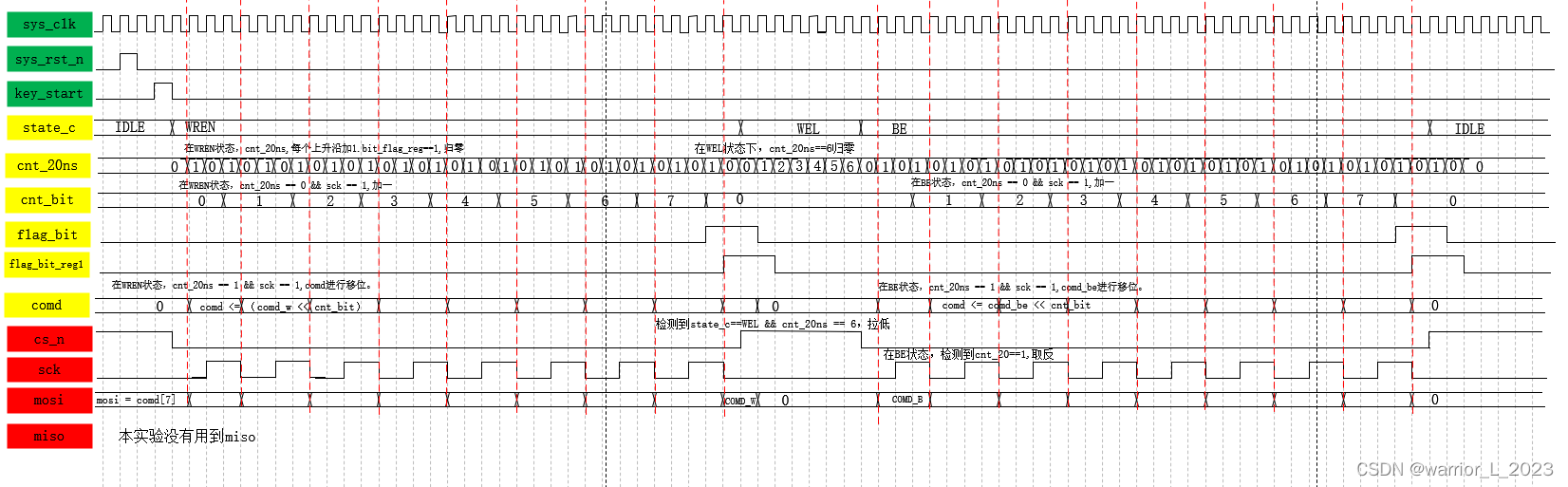

时序图:

代码:

module spi (input wire sys_clk ,input wire sys_rst_n , input wire key_start ,output wire mosi ,output wire miso ,output reg cs_n ,output reg sck

);// parameter parameter COMD_W = 8'h06 ,COMD_B = 8'hc7 ;parameter IDLE = 4'b0001 ,WREN = 4'b0010 ,WEL = 4'b0100 ,BE = 4'b1000 ;// wire signal deginewire IDLEtoWREN; wire WRENtoWEL ; wire WRENtoBE ; wire BEtoIDLE ; // reg signal definereg [3:0] state_c ;reg [3:0] state_n ;reg [3:0] cnt_20ns ;reg [3:0] cnt_bit ;reg flag_bit ;reg f_b_reg ; // flag_bit_reg的缩写reg [7:0] comd ;

/****************************************************************************/// 三段式状态机// 现态与次态描述// state_calways @(posedge sys_clk or negedge sys_rst_n) beginif(~sys_rst_n) state_c <= IDLE ;elsestate_c <= state_n ;end// state_nalways @(*) begincase (state_c)IDLE :if(IDLEtoWREN)state_n <= WREN ;else state_n <= IDLE ;WREN :if(WRENtoWEL)state_n <= WEL ;else state_n <= WREN ;WEL :if(WRENtoBE)state_n <= BE ;else state_n <= WEL ;BE :if(BEtoIDLE)state_n <= IDLE ;else state_n <= BE ;default: state_n <= IDLE ;endcaseend// 状态转移描述assign IDLEtoWREN = ( state_c == IDLE) && ( key_start ) ;assign WRENtoWEL = ( state_c == WREN) && ( f_b_reg ) ;assign WRENtoBE = ( state_c == WEL ) && ( cnt_20ns == 6 ) ;assign BEtoIDLE = ( state_c == BE ) && ( f_b_reg ) ;// 相关信号描述// reg [3:0] cnt_20ns ;always @(posedge sys_clk or negedge sys_rst_n) beginif(~sys_rst_n) cnt_20ns <= 4'd0 ;else case (state_c)IDLE : cnt_20ns <= 4'd0 ;WREN : if(cnt_20ns || f_b_reg)cnt_20ns <= 4'd0 ;else cnt_20ns <= cnt_20ns + 1'b1 ;WEL : if(cnt_20ns == 6) // 60x20ns==120nscnt_20ns <= 4'd0 ;elsecnt_20ns <= cnt_20ns + 1'b1 ;BE : if(cnt_20ns || f_b_reg)cnt_20ns <= 4'd0 ;else cnt_20ns <= cnt_20ns + 1'b1 ;default: cnt_20ns <= 4'd0 ;endcaseend// reg [3:0] cnt_bit ;always @(posedge sys_clk or negedge sys_rst_n) beginif(~sys_rst_n)cnt_bit <= 4'd0 ;else case (state_c)IDLE : cnt_bit <= 4'd0 ;WREN : if(!cnt_20ns && sck && cnt_bit == 7)cnt_bit <= 4'd0 ;else if(!cnt_20ns && sck)cnt_bit <= cnt_bit + 1'b1 ;WEL : cnt_bit <= 4'd0 ;BE : if(!cnt_20ns && sck && cnt_bit == 7)cnt_bit <= 4'd0 ;else if(!cnt_20ns && sck)cnt_bit <= cnt_bit + 1'b1 ;default: cnt_bit <= 4'd0 ;endcaseend// reg flag_bit ;always @(posedge sys_clk or negedge sys_rst_n) beginif(~sys_rst_n) flag_bit <= 1'b0 ;elsecase (state_c)IDLE : flag_bit <= 1'b0 ;WREN : if(cnt_bit == 7 && sck && !cnt_20ns)flag_bit <= 1'b1 ;else flag_bit <= flag_bit ;WEL : flag_bit <= 1'b0 ;BE : if(cnt_bit == 7 && sck && !cnt_20ns)flag_bit <= 1'b1 ;else flag_bit <= flag_bit ;default: flag_bit <= 1'b0 ;endcaseend// reg f_b_reg ;always @(posedge sys_clk or negedge sys_rst_n) beginif(~sys_rst_n) beginf_b_reg <= 1'b0 ;end else beginf_b_reg <= flag_bit ;endend// reg [7:0] comd ;always @(posedge sys_clk or negedge sys_rst_n) beginif(~sys_rst_n)comd <= 8'd0 ;elsecase (state_c)IDLE : comd <= 8'd0 ;WREN : if(cnt_20ns && sck)comd <= (COMD_W << cnt_bit) ;else if(!cnt_bit)comd <= COMD_W ;else comd <= comd ;WEL : comd <= 8'd0 ;BE : if(cnt_20ns && sck)comd <= (COMD_B << cnt_bit) ;else if(!cnt_bit)comd <= COMD_B ;else comd <= comd ;default : comd <= 8'd0 ;endcase end// output signal// wire mosi ,assign mosi = comd[7] ;// wire miso ,assign miso = 1'bz ;// reg cs_n ,always @(posedge sys_clk or negedge sys_rst_n) beginif(~sys_rst_n) begincs_n <= 1'b1 ;end else begincase (state_c)IDLE : if(key_start)cs_n <= 1'b0 ;else cs_n <= 1'b1 ;WREN : if(f_b_reg)cs_n <= 1'b1 ;else cs_n <= cs_n ;WEL : if(cnt_20ns == 6) cs_n <= 1'b0 ;else cs_n <= cs_n ;BE : if(f_b_reg)cs_n <= 1'b1 ;else cs_n <= cs_n ;default: cs_n <= 1'b1 ;endcaseendend// reg sck always @(posedge sys_clk or negedge sys_rst_n) beginif(~sys_rst_n)sck <= 1'b0 ;else case (state_c)IDLE : sck <= 1'b0 ;WREN : if(cnt_20ns)sck <= ~sck ;else sck <= sck ;WEL : sck <= 1'b0 ;BE : if(cnt_20ns)sck <= ~sck ;else sck <= sck ;default: sck <= 1'b0 ;endcaseendendmodule

module key_filter

#(parameter MAX_CNT_20MS = 20'd100_0000

)(input wire sys_clk ,input wire sys_rst_n ,input wire key_in ,output wire key_out

);reg key_r_0 ;reg key_r_1 ;wire nege ;wire pose ;reg [19:00] cnt_20ms ;wire add_cnt_20ms ;wire end_cnt_20ms ;reg add_cnt_flag ;// key_r_0 key_r_1 always @(posedge sys_clk or negedge sys_rst_n) beginif(~sys_rst_n) beginkey_r_0 <= 1'b1 ;end else beginkey_r_0 <= key_in ;endendalways @(posedge sys_clk or negedge sys_rst_n) beginif(~sys_rst_n) beginkey_r_1 <= 1'b1 ;end else beginkey_r_1 <= key_r_0 ;endend// nege poseassign nege = ~key_r_0 && key_r_1 ;assign pose = key_r_0 && ~key_r_1 ;// add_cnt_flagalways @(posedge sys_clk or negedge sys_rst_n) beginif(~sys_rst_n) beginadd_cnt_flag <= 1'b0 ;end else beginif(nege) beginadd_cnt_flag <= 1'b1 ;end else beginif( pose || end_cnt_20ms ) beginadd_cnt_flag <= 1'b0 ;end else beginadd_cnt_flag <= add_cnt_flag ;endend endend// cnt_20ms add_cnt_20ms end_cnt_20msalways @(posedge sys_clk or negedge sys_rst_n) beginif(~sys_rst_n) begincnt_20ms <= 20'd0 ;end else beginif(add_cnt_20ms) beginif(end_cnt_20ms) begincnt_20ms <= 20'd0 ;end else begincnt_20ms <= cnt_20ms + 20'd1 ;endend else begincnt_20ms <= 20'd0 ;endendendassign add_cnt_20ms = add_cnt_flag ;assign end_cnt_20ms = add_cnt_20ms && cnt_20ms == ( MAX_CNT_20MS - 1'b1 ) ;// key_out// always @(posedge sys_clk or negedge sys_rst_n) begin// // always @(*) begin // 这样的话 会综合成 数据选择器// if(~sys_rst_n) begin// key_out <= 1'b0 ;// end else begin// if(end_cnt_20ms) begin// key_out <= 1'b1 ;// end else begin// key_out <= 1'b0 ;// end// end// endassign key_out = end_cnt_20ms ;

endmodulemodule top(input wire sys_clk ,input wire sys_rst_n ,input wire key_in ,output wire cs_n ,output wire sck ,output wire mosi

);// 例化间连线wire key_flag ;key_filter key_filter_inst(.sys_clk ( sys_clk ) ,.sys_rst_n ( sys_rst_n ) ,.key_in ( key_in ) ,.key_out ( key_flag )

);spi spi_inst(.sys_clk ( sys_clk ) ,.sys_rst_n ( sys_rst_n ) ,.key_start ( key_flag ) ,.mosi ( mosi ) ,.miso ( ) ,.cs_n ( cs_n ) ,.sck ( sck )

);endmodule`timescale 1ns/1ns

module test_top();reg sys_clk ;reg sys_rst_n ;reg key_in ;wire cs_n ;wire sck ;wire mosi ;wire miso ;top top_inst(.sys_clk ( sys_clk ) ,.sys_rst_n ( sys_rst_n ) ,.key_in ( key_in ) ,.cs_n ( cs_n ) ,.sck ( sck ) ,.mosi ( mosi ) ,.miso ( miso )

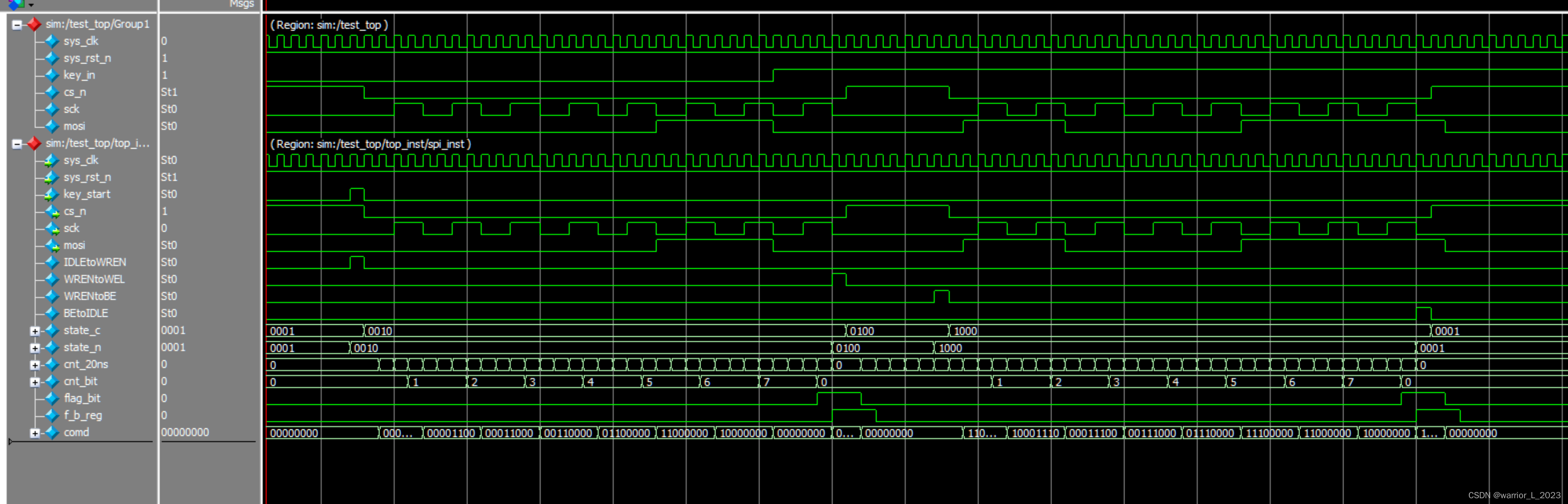

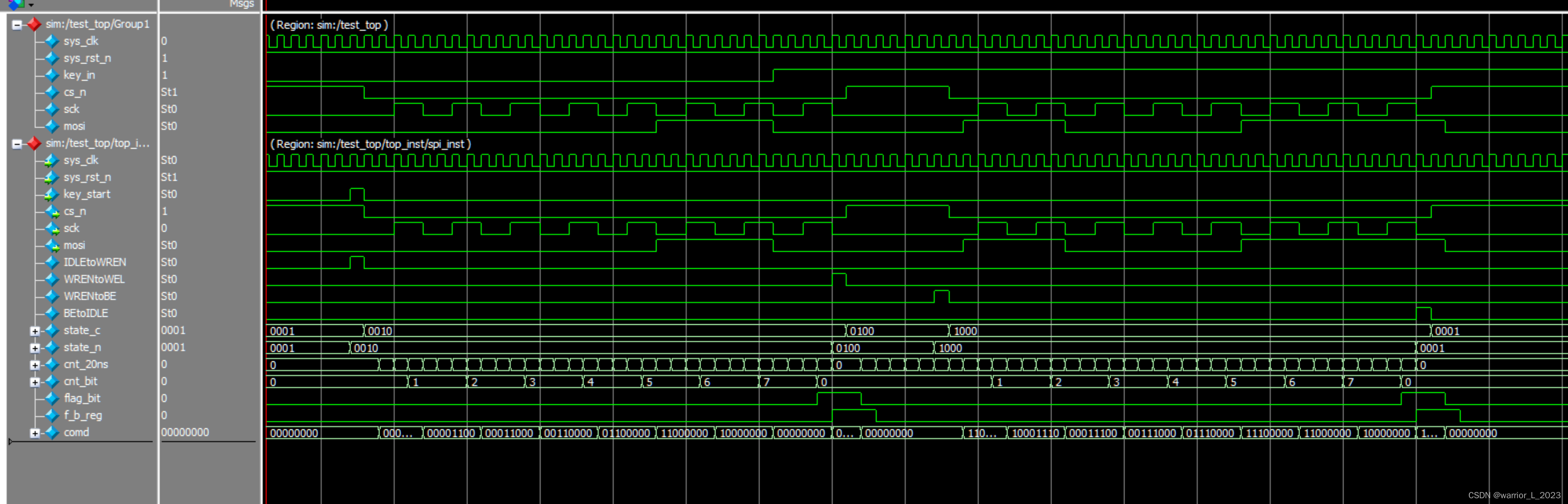

);parameter CYCLE = 20 ;defparam top_inst.key_filter_inst.MAX_CNT_20MS = 20'd100 ;initial beginsys_clk = 1'b1 ;sys_rst_n <= 1'b0 ;key_in <= 1'b1 ;#(CYCLE) ;sys_rst_n <= 1'b1 ;#(CYCLE * 30) ;key_in <= 1'b0 ;#(CYCLE * 130) ;key_in <= 1'b1 ;#(CYCLE * 100) ;$stop;endalways #(CYCLE/2) sys_clk = ~sys_clk ;endmodule仿真波形:

上板验证:

先往板子上固化一个流水灯程序,也就是把生成的.jic文件,写进flash。

重启开发板,流水灯正常工作,说明程序写进了flash。

然后把全擦除程序(.sof),写进开发板。

重启开发板,流水灯效果消失。

说明上板成功。

相关文章:

FPGA project : flash_erasure

SPI是什么: SPI(Serial Peripheral Interface,串行外围设备接口)通讯协议,是Motorola公司提出的一种同步串行接口技术,是一种高速、全双工、同步通信总线,在芯片中只占用四根管脚用来控制及数据…...

AC修炼计划(AtCoder Regular Contest 166)

传送门:AtCoder Regular Contest 166 - AtCoder 一直修炼cf,觉得遇到了瓶颈了,所以想在atcode上寻求一些突破,今天本来想尝试vp AtCoder Regular Contest 166,但结局本不是很好,被卡了半天,止步…...

Android---Android 是如何通过 Activity 进行交互的

相信对于 Android 工程师来说,startActivity 就像初恋一般。要求低,见效快,是每一个菜鸟 Android 工程师迈向高级 Android 工程师的必经阶段。经过这么多年的发展,startActivity 在 google 的调教下已经变得愈发成熟,对…...

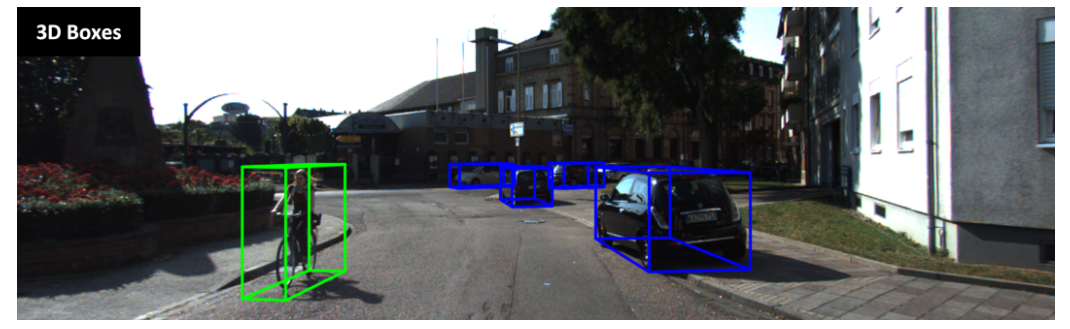

【论文解读】单目3D目标检测 MonoCon(AAAI2022)

本文分享单目3D目标检测,MonoCon模型的论文解读,了解它的设计思路,论文核心观点,模型结构,以及效果和性能。 目录 一、MonoCon简介 二、论文核心观点 三、模型框架 四、模型预测信息与3D框联系 五、损失函数 六、…...

-每天10个小知识)

Angular知识点系列(5)-每天10个小知识

目录 41. Angular的路由守卫42. 处理文件的上传和下载43. Angular的动画系统44. 使用第三方库和选择评估45. 性能优化46. AOT和JIT编译47. 处理响应式布局和适配不同屏幕尺寸48. Angular的国际化(i18n)49. Angular的PWA开发50. 使用Angular Material或其…...

基于海洋捕食者优化的BP神经网络(分类应用) - 附代码

基于海洋捕食者优化的BP神经网络(分类应用) - 附代码 文章目录 基于海洋捕食者优化的BP神经网络(分类应用) - 附代码1.鸢尾花iris数据介绍2.数据集整理3.海洋捕食者优化BP神经网络3.1 BP神经网络参数设置3.2 海洋捕食者算法应用 4…...

Lift, Splat, Shoot图像BEV安装与模型详解

1 前言 计算机视觉算法通常使用图像是作为输入并输出预测的结果,但是对结果所在的坐标系却并不关心,例如图像分类、图像分割、图像检测等任务中,输出的结果均在原始的图像坐标系中。因此这种范式不能很好的与自动驾驶契合。 在自动驾驶中,多个相机传感器的数据一起作为输…...

MySQL简介

数据库管理系统 1、关系型数据库管理系统: Oracle:Oracle是一种商业级关系型数据库管理系统,支持高可用性、高安全性以及广泛的企业级应用需求。SQL Server:SQL Server是Microsoft开发的企业级关系型数据库管理系统,广泛应用于Windows环境下的软件开发。MySQL:MySQL是一…...

php代码优化---本人的例子

直接上货: 1:数据统计 店铺数量、提现金额、收益金额、用户数量 旧: // //店铺// $storey db( store )->whereTime( addtime, yesterday )->count();//昨天// $stored db( store )->whereTime( addtime, d )->count();//今天…...

EMC Unity存储(VNXe) service Mode和Normal Mode的一些说明

本文介绍下EMC unity存储设备(也包含VNXe存储设备)的两种工作模式: Service mode:也叫做rescue mode,存储OS工作不正常或者有其他故障,就会进入这个模式,无法对外提供服务Normal modeÿ…...

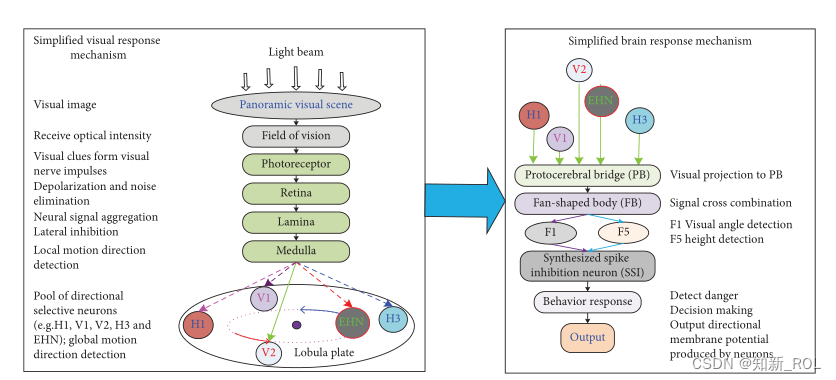

基于全景运动感知的飞行视觉脑关节神经网络全方位碰撞检测

https:/doi.org/10.1155/2023/5784720 摘要: 生物系统有大量的视觉运动检测神经元,其中一些神经元可以优先对特定的视觉区域做出反应。然而,关于如何使用它们来开发用于全向碰撞检测的神经网络模型,很少有人做过工作。为此&#…...

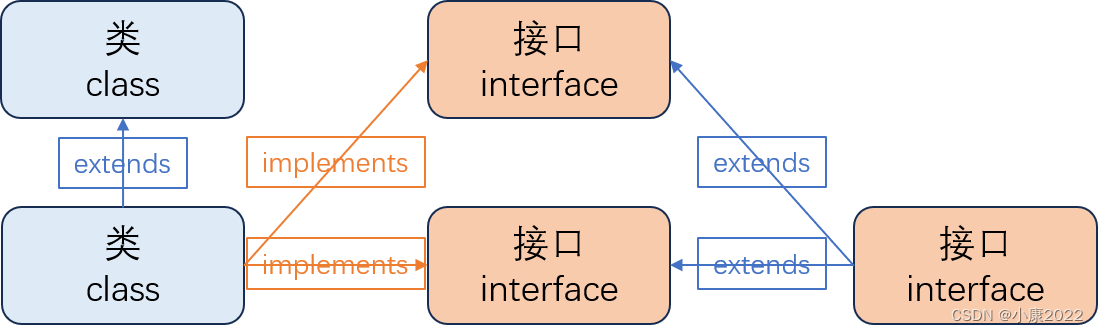

Java 继承与实现

一、继承(extends) 1.1 继承概念 继承是面向对象的基本特征,它允许子类继承父类的特征和行为,以提高代码的复用率和维护性等。下面一张图生动地展示了继承和类之间的关系: 继承图 上图中,“动物”、“食草…...

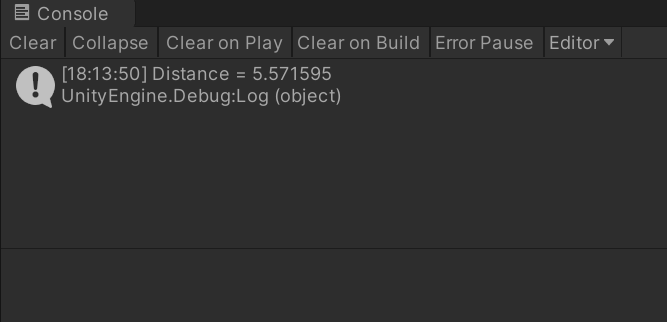

Unity 3D基础——计算两个物体之间的距离

1.在场景中新建两个 Cube 立方体,在 Scene 视图中将两个 Cude的位置错开。 2.新建 C# 脚本 Distance.cs(写完记得保存) using System.Collections; using System.Collections.Generic; using UnityEngine;public class Distance : MonoBehav…...

css常见问题处理

文章目录 1:禁止文字被复制粘贴1.1 Css 处理1.2 Js 处理 2:元素垂直水平居中2.1:方案一2.2 方案二2.3 方案三2.4 方案四2.5 方案五 1:禁止文字被复制粘贴 1.1 Css 处理 <div class"text">我不可以复制信息</div> <…...

蓝桥杯(迷宫,C++)

输入: 思路: 1、注意输入用字符串。 2、采用广度搜素的方法来求解。 3、因为最后要求字典序最小且D<L<R<U,所以在遍历四个方向的时候, 先向下,再向左、右,最后向上。 #include<iostream> #include…...

Python爬虫selenium安装谷歌驱动解决办法

驱动下载链接:CNPM Binaries Mirror (npmmirror.com) 谷歌浏览器老版本下载:Google Chrome 64bit Windows版_chrome浏览器,chrome插件,谷歌浏览器下载,谈笑有鸿儒 (chromedownloads.net) 驱动下载后解压缩直接放入python相应文件夹: 最后&a…...

)

生信教程:使用拓扑加权探索基因组进化(3)

使用 Twisst 探索整个基因组的进化关系的拓扑加权教程[1]。 简介 拓扑加权是量化不一定是单系群之间关系的一种方法。它通过考虑更简单的“分类单元拓扑”并量化与每个分类单元拓扑匹配的子树的比例,提供了复杂谱系的摘要。我们用来计算权重的方法称为 Twisst&#…...

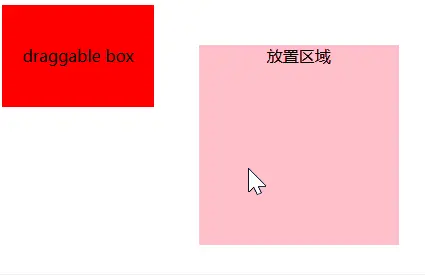

React js原生 详解 HTML 拖放 API(鼠标拖放功能)

最近碰到了个需求,大概就是要通过可视化拖拽的方式配置一个冰柜,需要把预设好的冰柜内部架子模板一个个拖到冰箱内。一开始的想法是用鼠标事件(mousedown、mouseup等)那一套去实现,能实现但是过程过于复杂,…...

LiveMedia视频中间件如何与第三方系统实现事件录像关联

一、平台简介 LiveMedia视频中间件是支持部署到本地服务器或者云服务器的纯软件服务,也提供服务器、GPU一体机全包服务,提供视频设备管理、无插件、跨平台的实时视频、历史回放、语音对讲、设备控制等基础功能,支持视频协议有海康、大华私有协…...

机器学习-有监督算法-决策树和支持向量机

目录 决策树ID3C4.5CART 支持向量积 决策树 训练:构造树,测试:从模型从上往下走一遍。建树方法:ID3,C4.5,CART ID3 以信息论为基础,以信息增益为衡量标准熵越小,混乱程度越小&…...

从温控器到无人机:PID参数整定的‘手感’秘籍,附C语言代码避坑指南

从温控器到无人机:PID参数整定的‘手感’秘籍与实战避坑指南 在工业自动化和智能硬件开发中,PID控制算法就像一位隐形的调音师,默默调节着系统的每一个细微变化。无论是缓慢升温的工业烘箱,还是高速响应的四旋翼无人机,…...

终极指南:深度实战OpenCore Legacy Patcher让老旧Mac重获新生

终极指南:深度实战OpenCore Legacy Patcher让老旧Mac重获新生 【免费下载链接】OpenCore-Legacy-Patcher Experience macOS just like before 项目地址: https://gitcode.com/GitHub_Trending/op/OpenCore-Legacy-Patcher OpenCore Legacy Patcher是一款革命…...

深入解析 vSphere 7 vMotion 迁移实战:从单中心到跨中心的无缝迁移策略

1. vMotion迁移的核心价值与场景定位 当你凌晨三点接到机房断电预警电话时,vMotion可能是你最想拥抱的技术。作为vSphere的"灵魂功能"之一,vMotion允许我们将运行中的虚拟机在不同主机间无缝迁移,就像给飞行中的飞机更换引擎——用…...

【实战】从理论到代码:用Python实现相位一致性特征提取

1. 相位一致性特征提取的核心原理 相位一致性(Phase Congruency)是计算机视觉领域一种强大的特征提取方法,它从根本上改变了传统边缘检测的思路。我第一次接触这个概念是在处理一组光照条件差异很大的工业检测图像时,当时用Sobel和…...

零基础玩转像素心智:手把手教你用情绪解码器分析用户评论

零基础玩转像素心智:手把手教你用情绪解码器分析用户评论 1. 认识像素心智情绪解码器 1.1 什么是情绪解码器 像素心智情绪解码器(Pixel Mind Decoder)是一款基于M2LOrder核心引擎构建的AI情绪识别工具。它将复杂的自然语言处理技术封装在一个充满复古游戏风格的1…...

Winhance中文版深度解析:Windows系统优化的C解决方案

Winhance中文版深度解析:Windows系统优化的C#解决方案 【免费下载链接】Winhance-zh_CN A Chinese version of Winhance. C# application designed to optimize and customize your Windows experience. 项目地址: https://gitcode.com/gh_mirrors/wi/Winhance-zh…...

)

告别杀后台!深度评测Ba-KeepAlive-U:这款UniAppX安卓保活插件到底有多强?(附多机型测试结果)

Ba-KeepAlive-U技术解析:如何为UniAppX应用实现跨机型保活方案 在移动应用开发领域,后台进程存活率一直是困扰开发者的技术难题。尤其对于需要持续运行定位、即时通讯或数据同步功能的应用,系统资源管理策略导致的"杀后台"现象直接…...

龙虾agent-browser获得chromium包问题

小龙虾非常火爆,在装agent-browser的时候,普通人往往被chromium的安装堵死了。网上的跨域安装方法一大堆,包括用镜像站点,国内所有的镜像站点都不行。但是真正能走通的,我到最后也没有试出来。最后只能自己想出一种手动…...

GyroFlow:用陀螺仪数据重塑视频稳定技术

GyroFlow:用陀螺仪数据重塑视频稳定技术 【免费下载链接】gyroflow Video stabilization using gyroscope data 项目地址: https://gitcode.com/GitHub_Trending/gy/gyroflow 在数字影像创作领域,画面稳定性直接决定作品专业度。无论是运动相机拍…...

Visio高效绘制神经网络卷积层:从基础到三维呈现

1. Visio绘制神经网络卷积层的入门指南 第一次用Visio画神经网络结构时,我盯着满屏的工具栏发懵——这玩意儿比Photoshop的图层还复杂。但摸索半天后发现,只要掌握几个核心功能,画卷积层其实比用PPT简单十倍。先说说最基础的形状选择…...