【数字IC设计/FPGA】FIFO与流控机制

流控,简单来说就是控制数据流停止发送。常见的流控机制分为带内流控和带外流控。

FIFO的流水反压机制

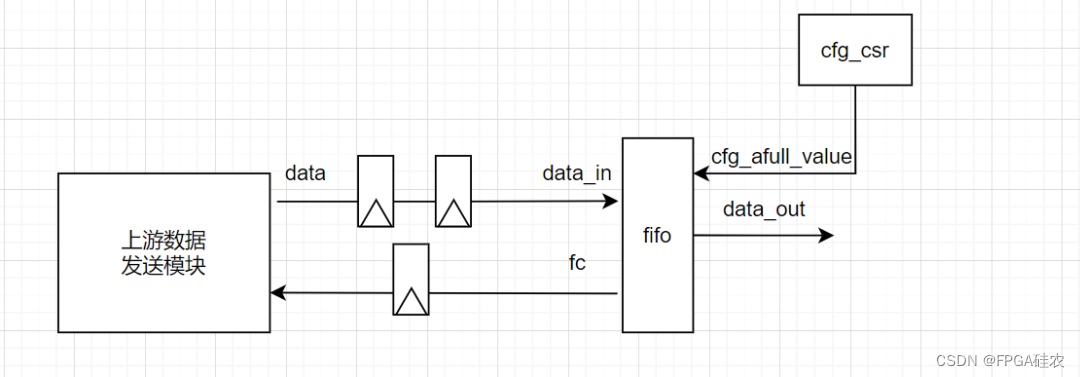

一般来说,每一个fifo都有一个将满阈值afull_value(almost full)。当fifo内的数据量达到或超过afull_value时,将满信号afull从0跳变为1。上游发送模块感知到afull为1时,则停止发送数据。在afull跳变成1后,fifo需要能够缓存路径上的data以及上游发送模块停止发流之前发出的所有data。这就是fifo的流控机制。下图是fifo流控机制的示意图。

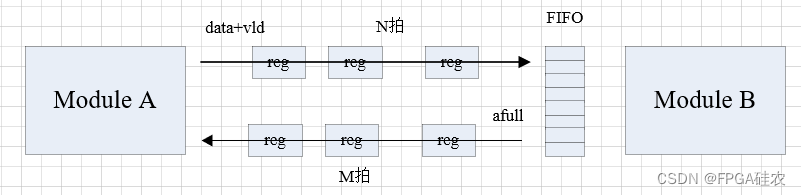

如下图所示,数据data和有效信号vld从模块A产生,经过N拍延时后,输入到FIFO,FIFO产生将满信号afull,经过M拍延时反馈到模块A。假设模块A接收到afull=1时,立即停止发送数据。假设FIFO深度为fifo_depth,每拍为一个时钟周期。

则,我们考虑以下问题:

- 为了保证FIFO不发生溢出,将满阈值afull_value至少应该设置成多少?

- 为了充分发挥FIFO的性能,FIFO深度depth应该为多少?

首先考虑第一个问题,即FIFO将满阈值如何设置:

当FIFO中的数据为afull_value时,产生afull=1,afull=1经过M拍到达模块A,此时FIFO中至多可以有(afull_value+M)个数据。afull=1到达模块A时,模块A立即停止发送数据,此时电路中还存在N拍数据将陆续送到FIFO中,所以最后FIFO中应该为(afull_value+M+N)个数据。

为了保证数据不会溢出,应满足公式fifo_depth >= afull_value+M+N,因此,将满阈值应该至多为depth_fifo - (M+N)。

为了验证上述结论,我们编写了如下代码进行实验:

delayed.sv

module delayed

#(parameter N = 5,parameter DW = 1)(input logic clk,input logic rst_n,input logic [DW-1:0] din,output logic [DW-1:0] dout);logic [N*DW-1:0] data_reg;always_ff@(posedge clk or negedge rst_n) beginif(~rst_n) begindata_reg <= (N*DW)'(0);endelse begindata_reg <= {data_reg[N*DW-DW-1:0], din};end

endassign dout = data_reg[N*DW-1:N*DW-DW];endmodule

top.sv

module top

#(parameter DATA_WIDTH = 32,parameter DEPTH = 32,parameter M = 5,parameter N = 10,parameter AF_VALUE = (M+N-1))

(

input logic clk,

input logic rst_n,

input logic wr_en,

input logic [DATA_WIDTH-1:0] wr_data,

output logic afull,

output logic [DATA_WIDTH-1:0] rd_data,

output logic empty,

input logic rd_en

);logic wr_en_dly;

logic [DATA_WIDTH-1:0] wr_data_dly;

logic almost_full;

logic error;

logic full;

//

delayed

#

(.N (N ),.DW(1 )

)

wr_en_delay_inst

(.clk (clk ),.rst_n(rst_n ),.din (wr_en ),.dout (wr_en_dly)

);

//

delayed

#

(.N (N ),.DW (DATA_WIDTH)

)

wr_data_delay_inst

(.clk (clk ),.rst_n (rst_n ),.din (wr_data ),.dout (wr_data_dly)

);

//

delayed

#

(.N (M),.DW(1)

)

almost_full_delay_inst

(.clk (clk ),.rst_n(rst_n ),.din (almost_full),.dout (afull )

);

//

DW_fifo_s1_sf

#

(.width (DATA_WIDTH ), .depth (DEPTH ), .ae_level(1 ), .af_level(AF_VALUE ), .err_mode(1 ), .rst_mode(0 )

)U (.clk (clk ), .rst_n (rst_n ), .push_req_n (~wr_en_dly ),.pop_req_n (~rd_en ), .diag_n (1 ),.data_in (wr_data_dly ), .empty (empty ),.almost_empty ( ), .half_full ( ),.almost_full (almost_full ), .full (full ),.error (error ), .data_out (rd_data ) );endmodule

tb.sv

module tb;

parameter DATA_WIDTH = 32;

parameter DEPTH = 32;

parameter M = 5;

parameter N = 10;

parameter AF_VALUE = M + N;logic rst_n;

logic clk;

logic rd_en;

logic rd_en_r;

logic wr_en;

logic wr_en_r;

logic empty;

logic afull;

logic [DATA_WIDTH-1:0] wr_data;

logic [DATA_WIDTH-1:0] rd_data;

logic [DATA_WIDTH-1:0] ref_data;

logic error;assign error = (rd_en && ~empty && (ref_data != rd_data)) ? 1'b1 : 1'b0;always_ff@(posedge clk or negedge rst_n) beginif(~rst_n) beginref_data <= '0;endelse if(rd_en && ~empty) beginref_data <= ref_data + 1'b1;end

end//rd_en

always_ff@(posedge clk or negedge rst_n) beginif(~rst_n) beginrd_en_r <= 1'b0;endelse if($urandom % 100 < 1) beginrd_en_r <= 1'b1;endelse beginrd_en_r <= 1'b0;end

endassign rd_en = rd_en_r && ~empty;

//wr_data

always_ff@(posedge clk or negedge rst_n) beginif(~rst_n) beginwr_data <= '0;endelse if(wr_en && ~afull) beginwr_data <= wr_data + 1'b1;end

end//wr_en

always_ff@(posedge clk or negedge rst_n) beginif(~rst_n) beginwr_en_r <= 1'b0;endelse if($urandom % 100 < 100) beginwr_en_r <= 1'b1;endelse beginwr_en_r <= 1'b0;end

endassign wr_en = wr_en_r && ~afull;//clk

initial

beginclk = 1'b0;forever begin#5 clk = ~clk;end

end//rst

initial

beginrst_n = 1'b0;#100rst_n = 1'b1;

end//

initial

begin#20000$finish;

end//

initial begin$fsdbDumpfile("./top.fsdb");$fsdbDumpvars(0);

end//inst

top

#(.DATA_WIDTH(DATA_WIDTH),.DEPTH (DEPTH ),.M (M ),.N (N ),.AF_VALUE (AF_VALUE ))

U(.*);endmodule

以及makefile脚本:

all: listfile com sim verdi cleanlistfile:find -name "*.sv" > filelist.fcom:vcs -full64 -cpp g++-4.8 -cc gcc-4.8 -LDFLAGS -Wl,--no-as-needed -sverilog -debug_access -timescale=1ns/10ps \-f filelist.f -l com.log -kdb -lca -y ${SYNOPSYS}/dw/sim_ver +libext+.v +incdir+${SYNOPSYS}/dw/sim_ver+sim:./simv -l sim.logverdi:verdi -sv -f filelist.f -ssf *.fsdb -nologo &clean:rm -rf csrc *.log *.key *simv* *.vpd *DVE*rm -rf verdiLog *.fsdb *.bak *.conf *.rc *.f

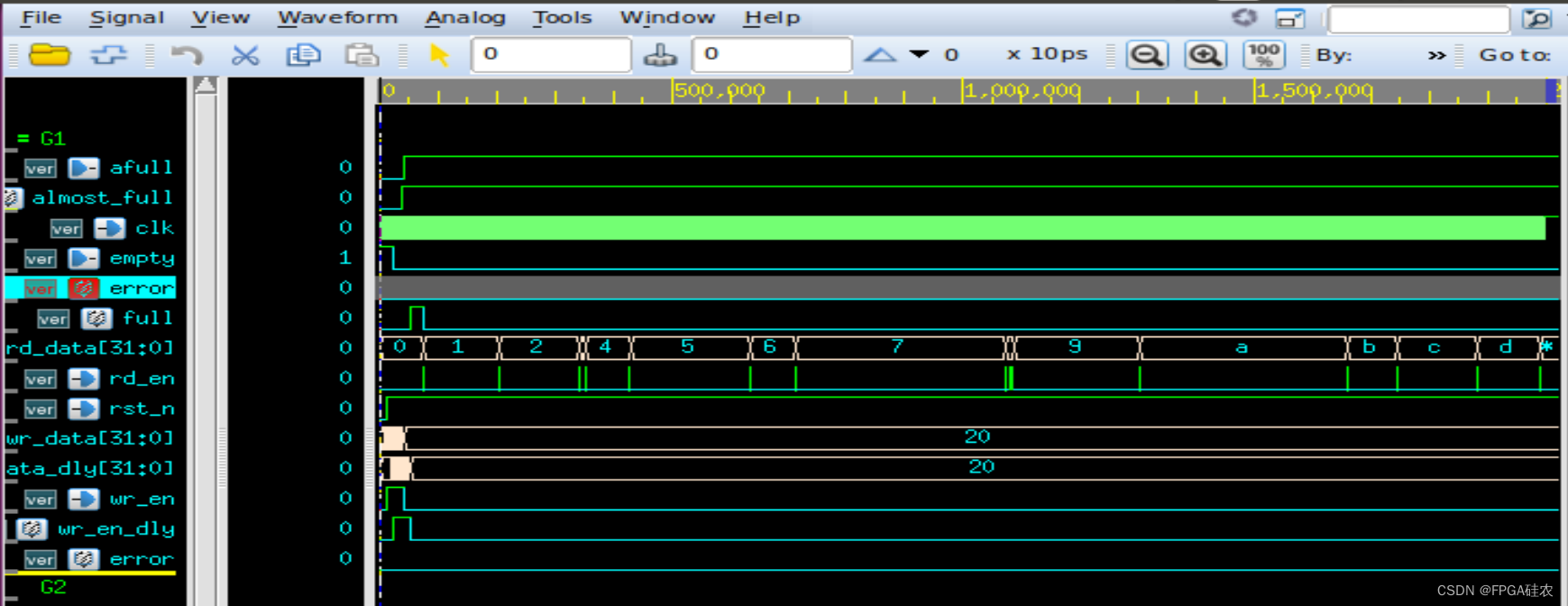

当设置fifo的将满阈值为M+N时,fifo不会丢失数据,流控正确。(注:dw fifo中的将满阈值afull的定义为:当fifo中还有小于等于afull个空位置时,拉高afull信号)

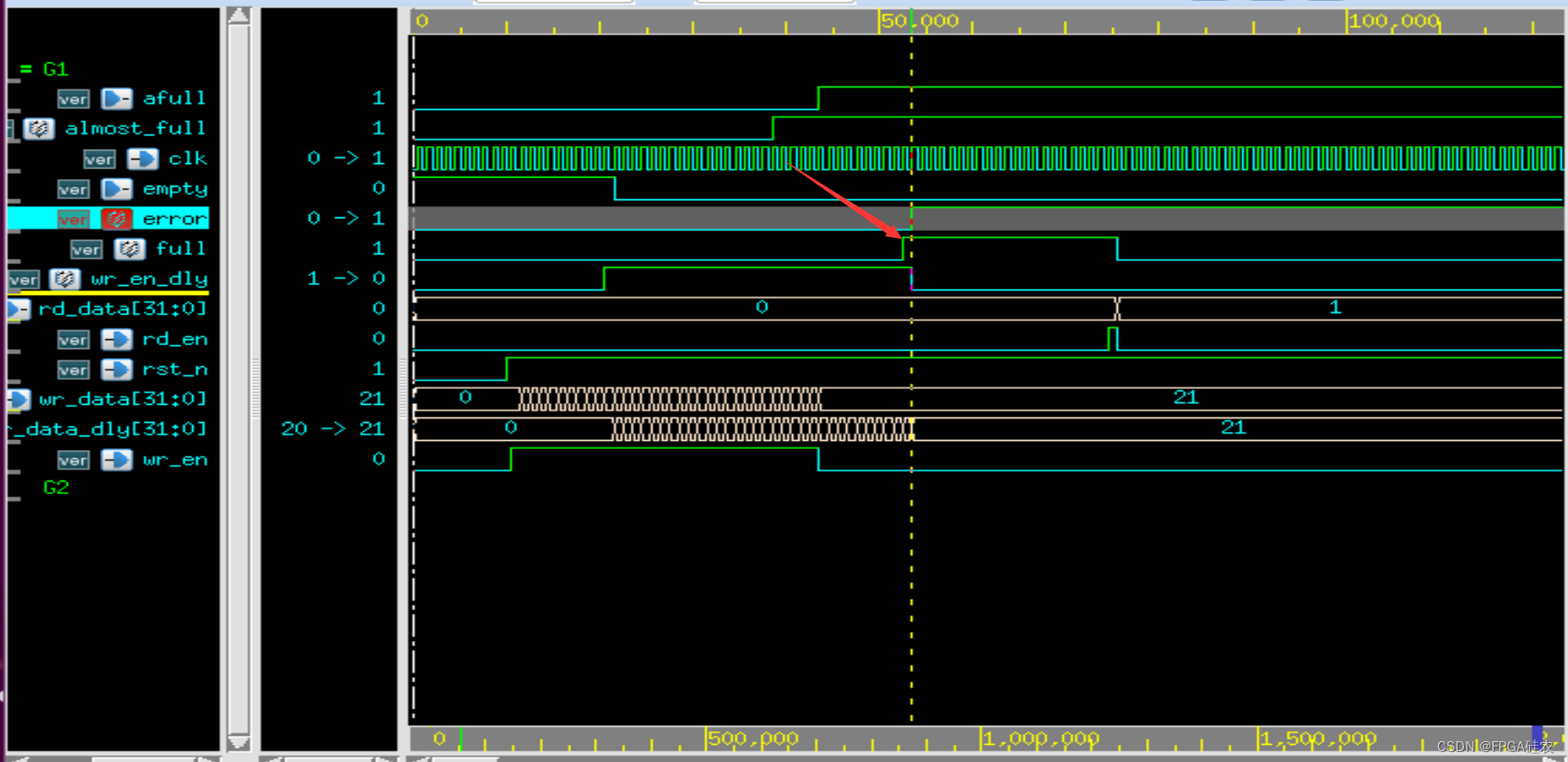

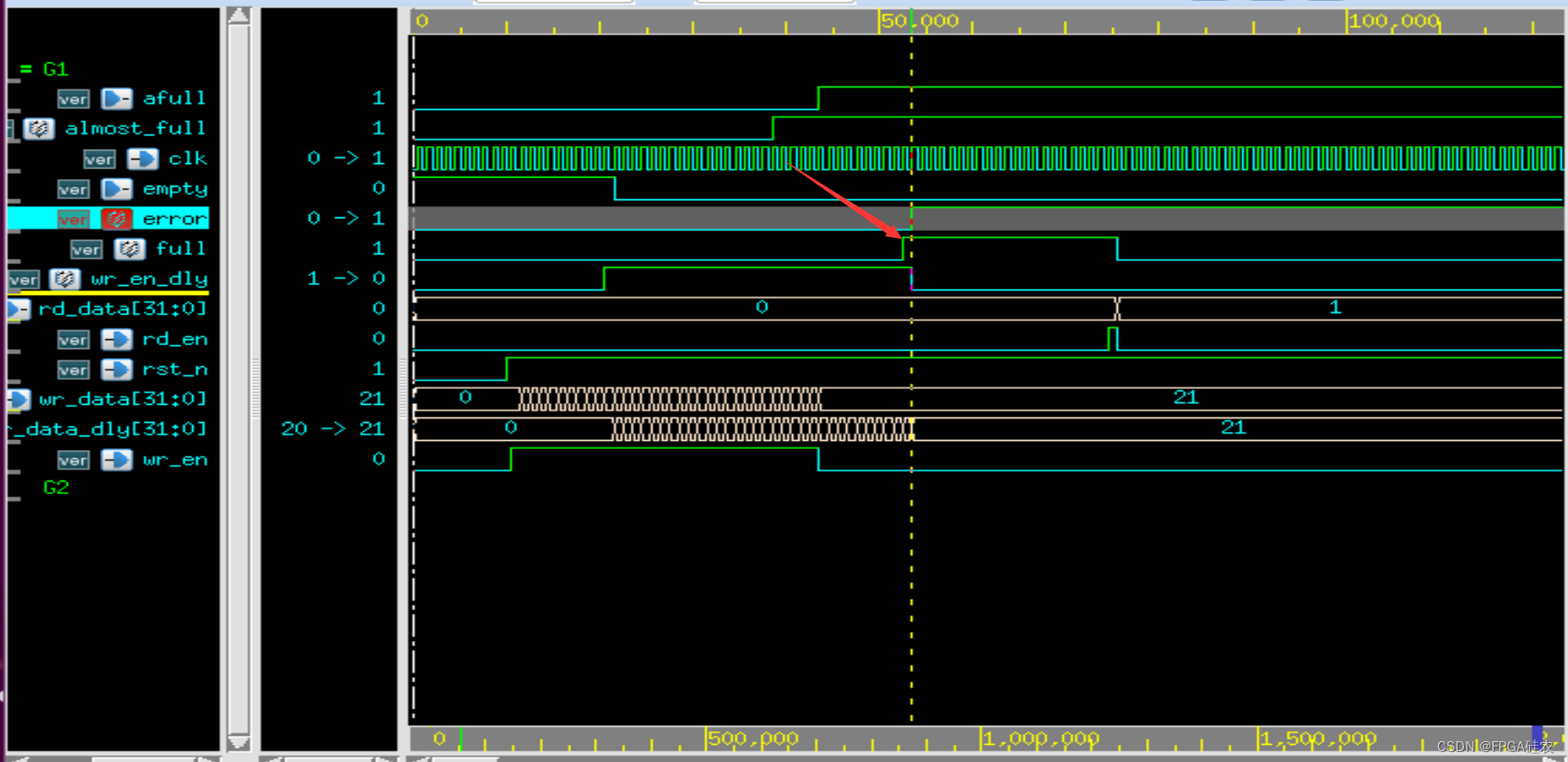

当设置fifo的将满阈值为M+N-1时,fifo会丢失数据,流控出错。如下图所示:

现在考虑第二个问题,即FIFO深度depth应该为多少?

分析:若fifo_depth过小,afull有效之后,fifo中存储的数据将很快被下游读取,而新的数据又无法及时到达FIFO,因此会造成流水气泡,影响电路的性能。

假设M=5, N=10,且fifo_depth=20,则afull_value=5。在T时刻,fifo中存了5个数据后afull=1会变为有效,在之后的15个周期内会陆续存入15个数据。假设下游模块B每个周期读取FIFO中的一个数据,因为当FIFO内的数据data_cnt小于5时,afull才会无效(为0),因此在T+15和T+30的时刻内,下游电路B只能读5个数据,从而造成数据断流,影响电路性能。

为了保证电路性能,在T+15到T+30这个时间段内应该有15个数据可读,因此afull_value应该不小于15(=M+N)。故FIFO深度应该不小于2*(M+N)。

相关文章:

【数字IC设计/FPGA】FIFO与流控机制

流控,简单来说就是控制数据流停止发送。常见的流控机制分为带内流控和带外流控。 FIFO的流水反压机制 一般来说,每一个fifo都有一个将满阈值afull_value(almost full)。当fifo内的数据量达到或超过afull_value时,将满…...

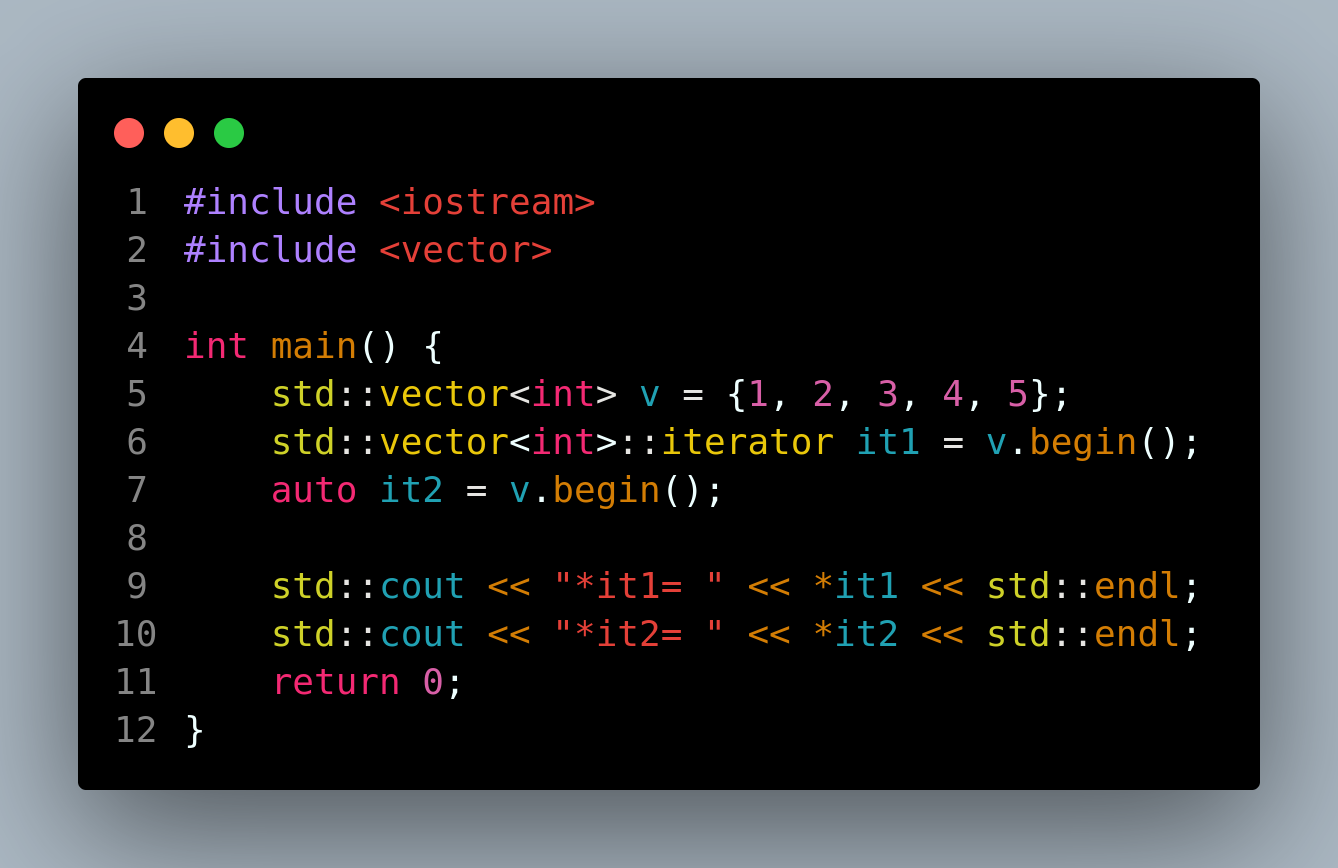

C++笔记之遍历vector的所有方式

C笔记之遍历vector的所有方式 —— 2023年4月15日 上海 code review 文章目录 C笔记之遍历vector的所有方式1.普通for循环2.迭代器版3.const迭代器4.C11引入的范围for循环5.使用auto关键字和迭代器6.使用std::for_each算法7.使用std::for_each和lambda表达式8.普通版vector::at…...

OpenCV 笔记(2):图像的属性以及像素相关的操作

Part11. 图像的属性 11.1 Mat 的主要属性 在前文中,我们大致了解了 Mat 的基本结构以及它的创建与赋值。接下来我们通过一个例子,来看看 Mat 所包含的常用属性。 先创建一个 3*4 的四通道的矩阵,并打印出其相关的属性,稍后会详细…...

基于指数分布优化的BP神经网络(分类应用) - 附代码

基于指数分布优化的BP神经网络(分类应用) - 附代码 文章目录 基于指数分布优化的BP神经网络(分类应用) - 附代码1.鸢尾花iris数据介绍2.数据集整理3.指数分布优化BP神经网络3.1 BP神经网络参数设置3.2 指数分布算法应用 4.测试结果…...

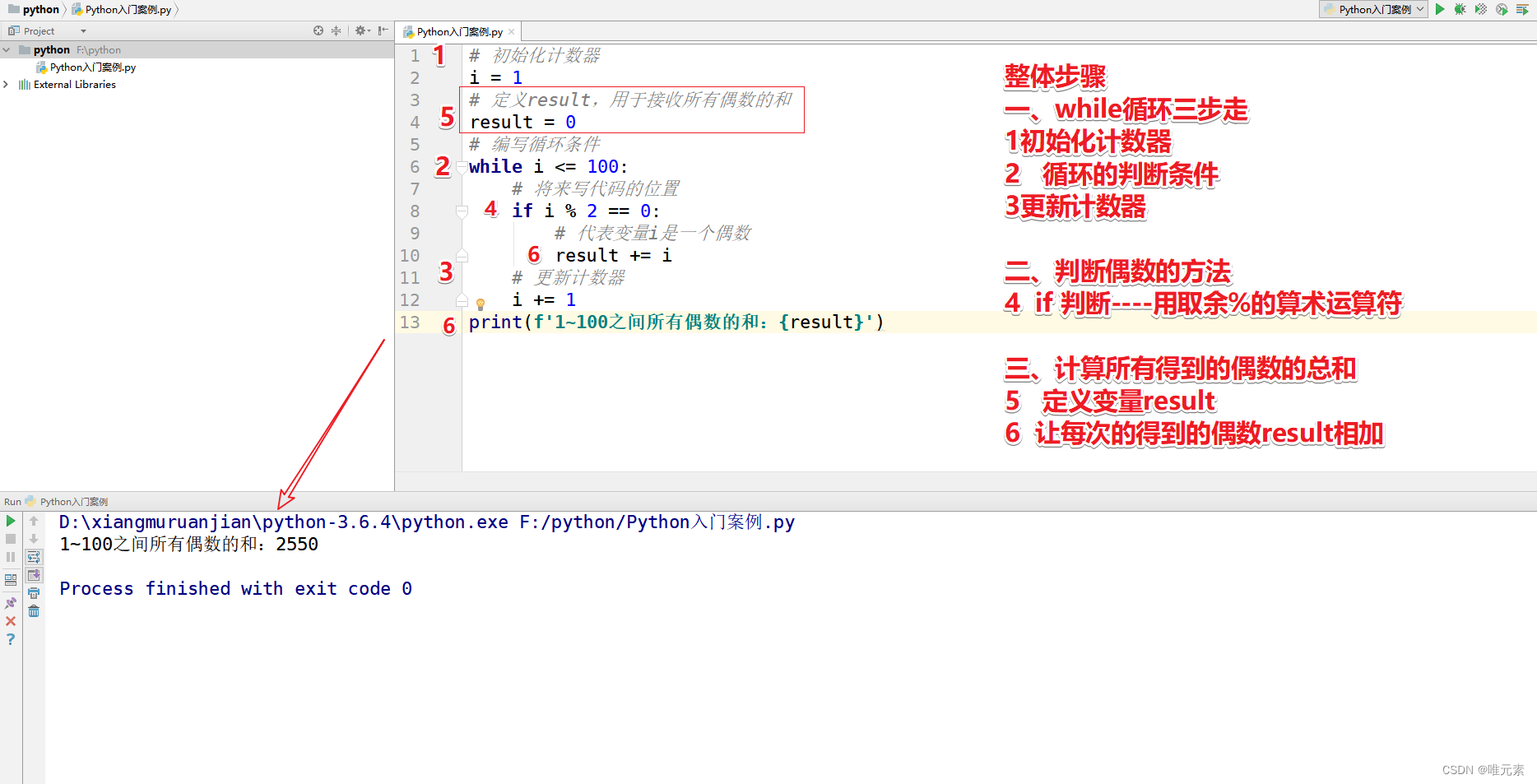

Python--练习:使用while循环求1~100之间,所有偶数的和(涉及if判断是不是偶数)

案例:求1~100之间,所有偶数的和 思考: 先套用原有基础模式,之后再思考其他的。 其实就是在之前文章 Python--练习:使用while循环求1..100的和-CSDN博客 的基础上,再判断如果获取到里面的全部偶数&#…...

带温度的softmax

用pytorch写一下使用带有温度的softmax的demo import torch import torch.nn.functional as F# 定义带有温度的softmax函数 def temperature_softmax(logits, temperature1.0):return F.softmax(logits / temperature, dim-1)# 输入logits logits torch.tensor([[1.0, 2.0, 3.…...

js函数调用的方式有几种

在 JavaScript 中,函数可以通过不同的方式进行调用。以下是常见的几种函数调用方式: 函数调用:使用函数名称后跟一对小括号来调用函数,这是最基本的调用方式。 functionName(); 方法调用:函数可以作为对象的方法进行调…...

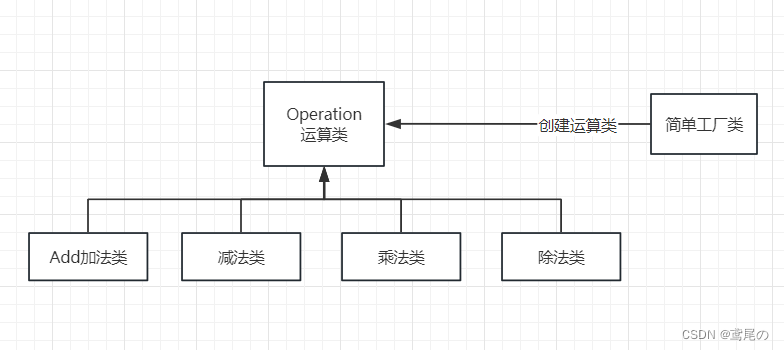

聊聊设计模式--简单工厂模式

简单工厂模式 前面也学了很多各种微服务架构的组件,包括后续的服务部署、代码管理、Docker等技术,那么作为后端人员,最重要的任务还是代码编写能力,如何让你的代码写的漂亮、易扩展,让别人一看赏心悦目,…...

Python基础教程:内置函数之字典函数的使用方法

嗨喽~大家好呀,这里是魔王呐 ❤ ~! python更多源码/资料/解答/教程等 点击此处跳转文末名片免费获取 len(字典名): 返回键的个数,即字典的长度 # len(字典名): # 返回键的个数,即字典的长度dic {a:123,b:456,c:789…...

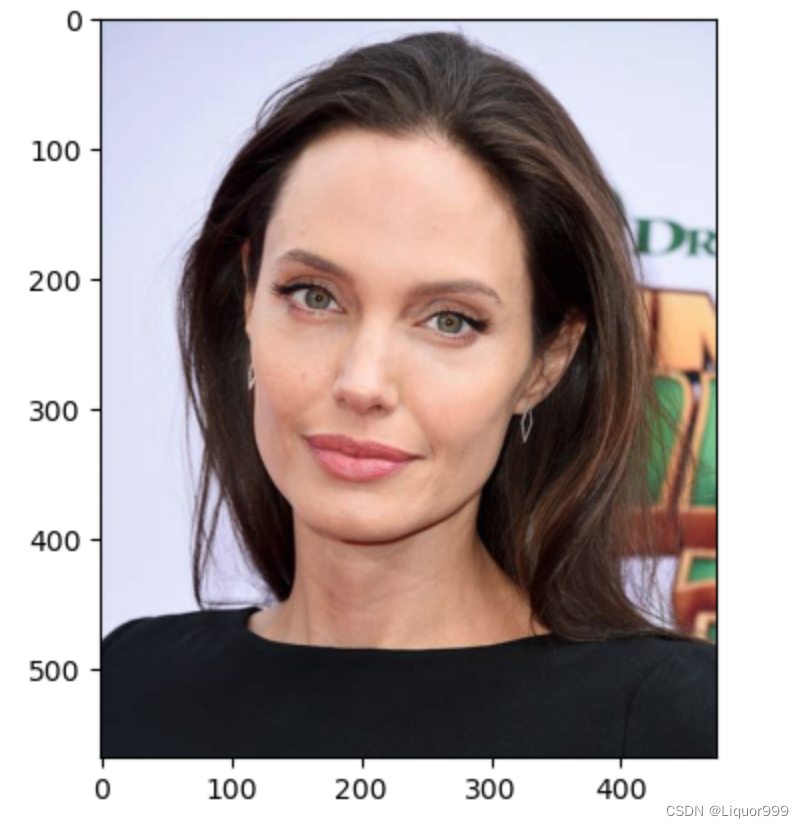

Pytorch从零开始实战06

Pytorch从零开始实战——明星识别 本系列来源于365天深度学习训练营 原作者K同学 文章目录 Pytorch从零开始实战——明星识别环境准备数据集模型选择开始训练模型可视化模型预测总结 环境准备 本文基于Jupyter notebook,使用Python3.8,Pytorch2.0.1c…...

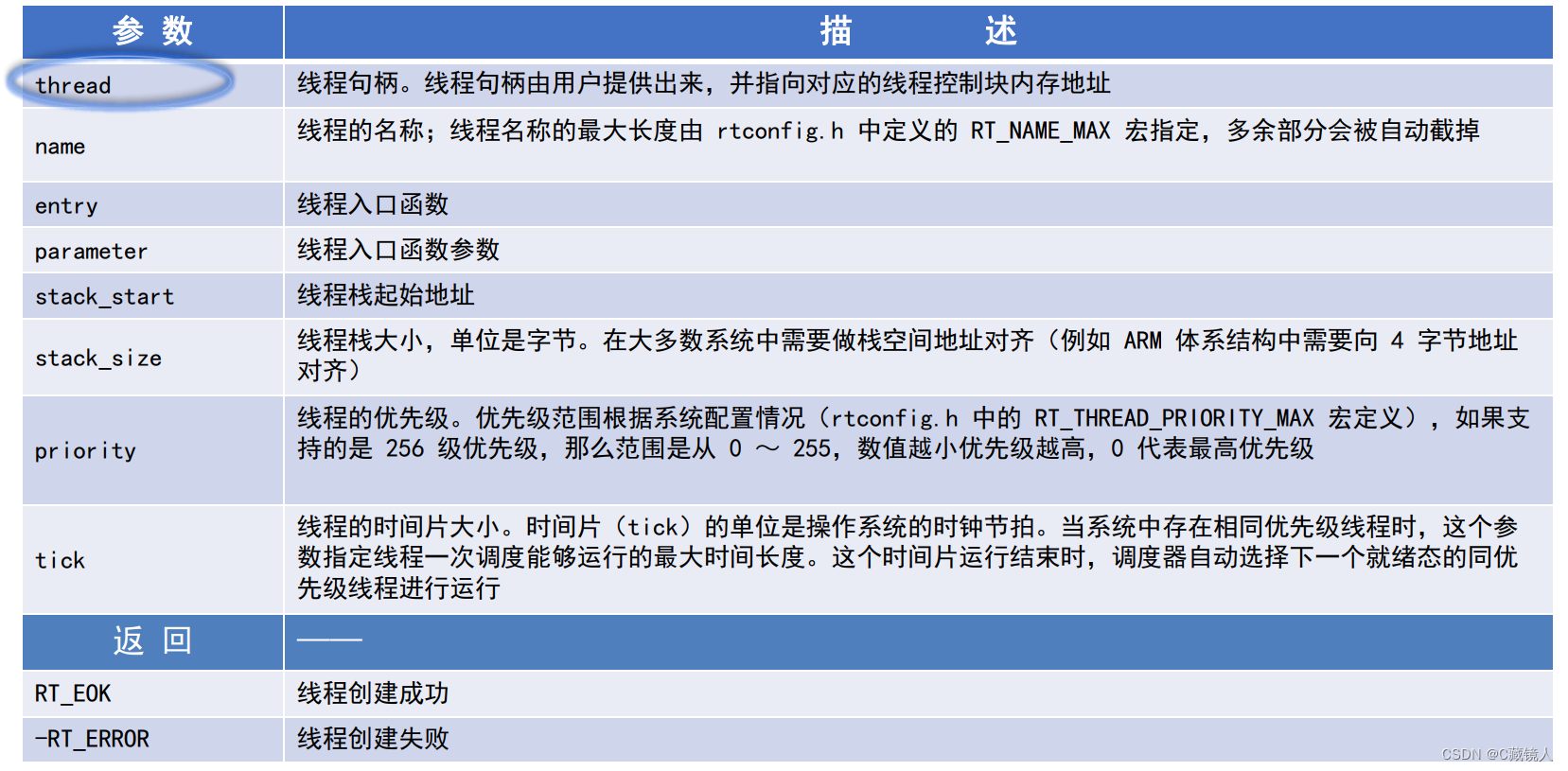

RT-Thread学习笔记(三):线程管理

线程管理 线程管理相关概念什么是时间片轮转调度器锁线程运行机制线程的五种状态 动态和静态创建线程区别动态和静态创建线程优缺点RT-Thread动态线程管理函数动态创建线程动态删除线程 RT-Thread静态线程管理函数静态创建线程 线程其他操作线程启动线程延时获得当前执行的线程…...

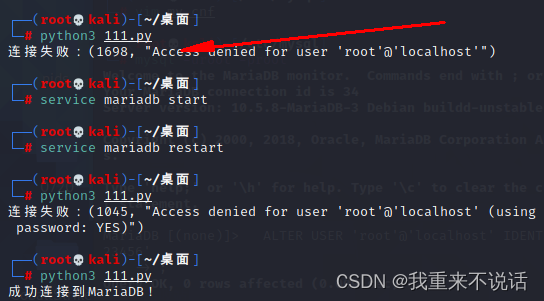

pymysql连接Mariadb/Mysql出现错误(配置正确情况下)解决办法

场景:在kali中使用python中pymysql对Mariadb进行连接,在整个过程中配置全部正确,但是就是无法进行连接,提示结果如下: Access denied for user rootlocalhost解决办法:进入数据库中,将默认密码…...

数据仓库扫盲系列(1):数据仓库诞生原因、基本特点、和数据库的区别

数据仓库的诞生原因 随着互联网的普及,信息技术已经深入到各行各业,并逐步融入到企业的日常运营中。然而,当前企业在信息化建设过程中遇到了一些困境与挑战。 1、历史数据积存。 过去企业的业务系统往往是在较长时间内建设的,很…...

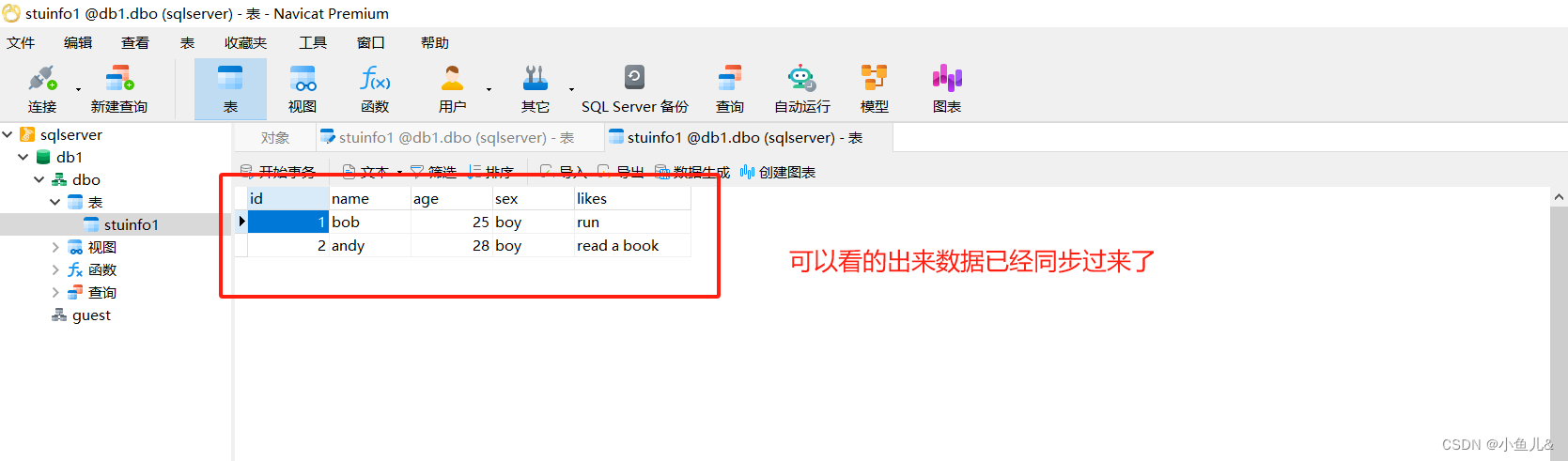

DataX-web安装部署和使用

DataX-web的环境准备 MySQL (5.5) 必选,对应客户端可以选装, Linux服务上若安装mysql的客户端可以通过部署脚本快速初始化数据库 JDK (1.8.0_xxx) 必选 DataX 必选 Python (2.x) (支持Python3需要修改替换datax/bin下面的三个python文件,替换文件在do…...

sqlmap防御以及文件读写

一.防御 过滤 1.使用过滤函数 $email filter_var($_POST[email], FILTER_VALIDATE_EMAIL); if ($email) { // input is a valid email address } else { // input is not a valid email address 使用 filter_var() 函数和 FILTER_VALIDATE_EMAIL 过滤器来验证用户输…...

【源码】C/C++运动会计分系统 期末设计源码

文章目录 题目介绍功能源码效果展示带报告(内容) 题目介绍 使用语言: 两个版本都会发: 版本1:C语言 版本2: C 代码量: 500 题目介绍: 要求:初始化输入:N-参赛…...

Ubuntu安装Docker

卸载官方库中之前的旧版本 sudo apt-get remove docker docker-engine docker-ce docker.io更新安装包列表 sudo apt-get update安装以下包以使apt可以通过HTTPS使用存储库 sudo apt-get install -y apt-transport-https ca-certificates curl software-properties-common添…...

useReducer+createContext真的可以代替Redux吗?

概念 useReducer useReducer 是 React 提供的一个状态管理钩子,通常用于管理组件的复杂状态逻辑。它采用两个参数:reducer 函数和初始状态。Reducer 函数接受当前状态和一个操作(action),并返回一个新的状态。这有点…...

)

Mysql忘记登入密码找回 方法(超详细)

如果你找不到 MySQL 的安装路径,可以尝试以下几种方法: 检查环境变量:打开命令提示符,并运行以下命令: echo %PATH% 这会显示系统的环境变量。查找其中是否包含 MySQL 相关的路径,例如 C:\Program Files…...

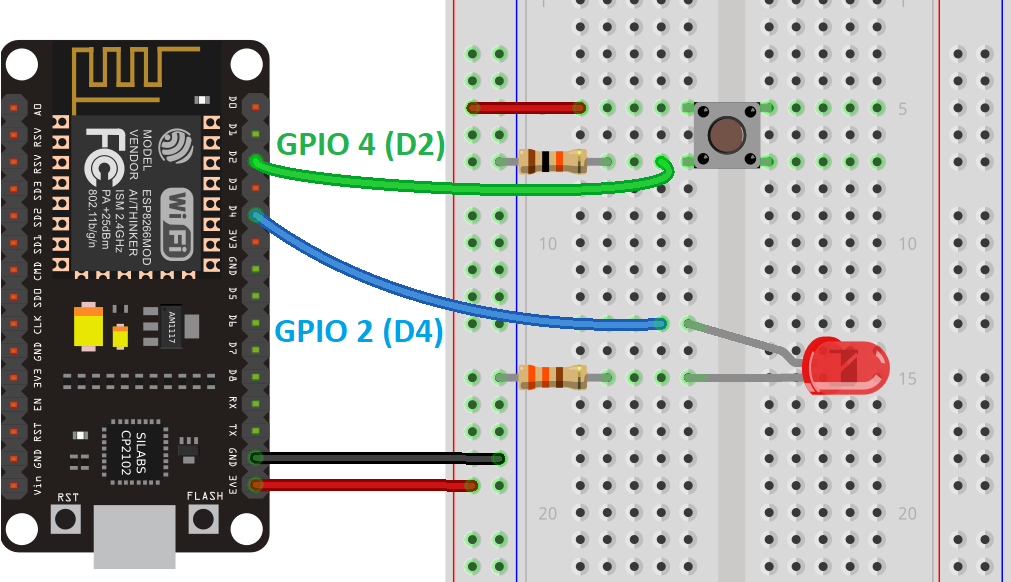

NodeMCU ESP8266 读取按键外部输入信号详解(图文并茂)

NodeMCU ESP8266 读取按键外部输入信号教程(图文并茂) 文章目录 NodeMCU ESP8266 读取按键外部输入信号教程(图文并茂)前言按键输入常用接口pinModedigitalRead 示例代码结论 前言 ESP8266如何检测外部信号的输入,通常…...

)

告别复制粘贴!程序员必备的Markdown表情符号速查表(附分类与使用场景)

程序员效率革命:Markdown表情符号分类与应用实战指南 在GitHub README中看到一个恰到好处的🚀能瞬间传达项目活跃度,技术博客里的💡比十行文字更能突出核心创意——这就是Emoji在现代技术文档中的魔力。作为数字时代的象形文字&am…...

魔兽争霸III终极兼容性修复指南:让经典游戏在Windows 11上焕发新生

魔兽争霸III终极兼容性修复指南:让经典游戏在Windows 11上焕发新生 【免费下载链接】WarcraftHelper Warcraft III Helper , support 1.20e, 1.24e, 1.26a, 1.27a, 1.27b 项目地址: https://gitcode.com/gh_mirrors/wa/WarcraftHelper 还在为《魔兽争霸III》…...

学会学习总结

最近学习英语,在这个过程接触了一些关于如何学习的学习方法,很有感触,进行总结整理 文章目录一、学习概念理解1.1 学习的目标---构建自己的知识体系1.2 学习的组成---学习学(模仿)习(创造)1.3 学…...

丹青识画入门必学:中文多模态提示词设计与意境引导技巧

丹青识画入门必学:中文多模态提示词设计与意境引导技巧 1. 理解多模态提示词的核心价值 多模态提示词是连接视觉内容与语言描述的关键桥梁。在丹青识画这样的智能影像雅鉴系统中,提示词的质量直接决定了生成描述的准确性和艺术性。 传统的图像识别系统…...

)

Loom协程的“幽灵权限”有多危险?——基于Banking系统压测发现的3类零日上下文泄露漏洞(附ASM字节码级防护补丁)

第一章:Loom协程安全转型的底层认知与风险全景Java Loom 项目引入的虚拟线程(Virtual Threads)并非语法糖,而是JVM运行时层面的结构性演进。其核心在于将调度权从操作系统线程移交至用户态调度器,从而解耦“并发逻辑单…...

终极PoeCharm指南:如何用中文版Path of Building轻松打造流放之路最强角色

终极PoeCharm指南:如何用中文版Path of Building轻松打造流放之路最强角色 【免费下载链接】PoeCharm Path of Building Chinese version 项目地址: https://gitcode.com/gh_mirrors/po/PoeCharm 还在为《流放之路》复杂的装备搭配和天赋选择头疼吗ÿ…...

5分钟快速修复损坏MP4视频:untrunc终极指南

5分钟快速修复损坏MP4视频:untrunc终极指南 【免费下载链接】untrunc Restore a truncated mp4/mov. Improved version of ponchio/untrunc 项目地址: https://gitcode.com/gh_mirrors/un/untrunc 你是否因为相机突然断电、存储卡故障或传输中断而丢失了珍贵…...

咸鱼淘来的树莓派3B,配上3.5寸屏和Volumio,打造桌面数播的完整避坑记录

咸鱼淘来的树莓派3B,配上3.5寸屏和Volumio,打造桌面数播的完整避坑记录 在二手市场淘硬件就像寻宝,每次成功点亮屏幕的瞬间都充满成就感。最近我以210元的价格在咸鱼收了一台树莓派3B,搭配Volumio系统和3.5寸触摸屏,打…...

用HLS在Zynq上实现图像缩放IP:从720P到1080P,一个工程搞定OV5640摄像头适配

Zynq平台HLS图像缩放实战:从OV5640采集到HDMI输出的全链路解析 在嵌入式视觉系统中,实时图像缩放是一个常见但极具挑战性的需求。当使用Xilinx Zynq SoC搭配OV5640摄像头时,开发者往往需要处理不同分辨率间的转换——比如将摄像头采集的720P图…...

三步彻底解决惠普OMEN游戏本性能限制:OmenSuperHub终极方案实践指南

三步彻底解决惠普OMEN游戏本性能限制:OmenSuperHub终极方案实践指南 【免费下载链接】OmenSuperHub 使用 WMI BIOS控制性能和风扇速度,自动解除DB功耗限制。 项目地址: https://gitcode.com/gh_mirrors/om/OmenSuperHub 对于追求极致性能的惠普OM…...