【Verilog 教程】7.3 Verilog 串行 FIR 滤波器设计

串行 FIR 滤波器设计

设计说明

设计参数不变,与并行 FIR 滤波器参数一致。即,输入频率为 7.5 MHz 和 250 KHz 的正弦波混合信号,经过 FIR 滤波器后,高频信号 7.5MHz 被滤除,只保留 250KMHz 的信号。

输入频率: 7.5MHz 和 250KHz

采样频率: 50MHz

阻带: 1MHz-6MHz

阶数: 15 (N=15)串行设计,就是在 16 个时钟周期内对 16 个延时数据分时依次进行乘法、加法运算,然后在时钟驱动下输出滤波值。考虑到 FIR 滤波器系数的对称性,计算一个滤波输出值的周期可以减少到 8 个。串行设计时每个周期只进行一次乘法运算,所以设计中只需一个乘法器即可。此时数据需要每 8 个时钟周期有效输入一次,但是为了保证输出信号频率的正确性,工作时钟需要为采样频率的 8 倍,即 400MHz。这种方法的优点是资源耗费少,但是工作频率要求高,数据不能持续输出。

串行设计

设计中使用到的乘法器模块代码,可参考之前流水线式设计的乘法器。

为方便快速仿真,也可以直接使用乘号 * 完成乘法运算,设计中加入宏定义 SAFE_DESIGN 来选择使用哪种乘法器。

FIR 滤波器系数可由 matlab 生成,具体见附录。

/**********************************************************

>> Description : fir study with serial tech

>> V190403 : Fs:50Mhz, fstop:1-6Mhz, order:16, sys clk:400MHz

***********************************************************/

`define SAFE_DESIGNmodule fir_serial_low(input rstn,input clk, // 系统工作时钟,400MHzinput en , // 输入数据有效信号input [11:0] xin, // 输入混合频率的信号数据output valid, // 输出数据有效信号output [28:0] yout // 输出数据);//delay of input data enablereg [11:0] en_r ;always @(posedge clk or negedge rstn) beginif (!rstn) beginen_r[11:0] <= 'b0 ;endelse beginen_r[11:0] <= {en_r[10:0], en} ;endend//fir coeficientwire [11:0] coe[7:0] ;assign coe[0] = 12'd11 ;assign coe[1] = 12'd31 ;assign coe[2] = 12'd63 ;assign coe[3] = 12'd104 ;assign coe[4] = 12'd152 ;assign coe[5] = 12'd198 ;assign coe[6] = 12'd235 ;assign coe[7] = 12'd255 ;//(1) 输入数据移位部分 reg [2:0] cnt ;integer i, j ;always @(posedge clk or negedge rstn) beginif (!rstn) begincnt <= 3'b0 ;endelse if (en || cnt != 0) begincnt <= cnt + 1'b1 ; //8个周期计数endendreg [11:0] xin_reg[15:0];always @(posedge clk or negedge rstn) beginif (!rstn) beginfor (i=0; i<16; i=i+1) beginxin_reg[i] <= 12'b0;endendelse if (cnt == 3'd0 && en) begin //每8个周期读入一次有效数据xin_reg[0] <= xin ;for (j=0; j<15; j=j+1) beginxin_reg[j+1] <= xin_reg[j] ; // 数据移位endendend//(2) 系数对称,16个移位寄存器数据进行首位相加reg [11:0] add_a, add_b ;reg [11:0] coe_s ;wire [12:0] add_s ;wire [2:0] xin_index = cnt>=1 ? cnt-1 : 3'd7 ;always @(posedge clk or negedge rstn) beginif (!rstn) beginadd_a <= 13'b0 ;add_b <= 13'b0 ;coe_s <= 12'b0 ;endelse if (en_r[xin_index]) begin //from en_r[1]add_a <= xin_reg[xin_index] ;add_b <= xin_reg[15-xin_index] ;coe_s <= coe[xin_index] ;endendassign add_s = {add_a} + {add_b} ; //(3) 乘法运算,只用一个乘法reg [24:0] mout ;

`ifdef SAFE_DESIGNwire en_mult ;wire [3:0] index_mult = cnt>=2 ? cnt-1 : 4'd7 + cnt[0] ;mult_man #(13, 12) u_mult_single //例化自己设计的流水线乘法器(.clk (clk),.rstn (rstn),.data_rdy (en_r[index_mult]), //注意数据时序对应.mult1 (add_s),.mult2 (coe_s),.res_rdy (en_mult), .res (mout));`elsealways @(posedge clk or negedge rstn) beginif (!rstn) beginmout <= 25'b0 ;endelse if (|en_r[8:1]) beginmout <= coe_s * add_s ; //直接乘endendwire en_mult = en_r[2];

`endif//(4) 积分累加,8组25bit数据 -> 1组 29bit 数据reg [28:0] sum ;reg valid_r ;//mult output en counterreg [4:0] cnt_acc_r ;always @(posedge clk or negedge rstn) beginif (!rstn) begincnt_acc_r <= 'b0 ;endelse if (cnt_acc_r == 5'd7) begin //计时8个周期cnt_acc_r <= 'b0 ;endelse if (en_mult || cnt_acc_r != 0) begin //只要en有效,计时不停cnt_acc_r <= cnt_acc_r + 1'b1 ;endendalways @(posedge clk or negedge rstn) beginif (!rstn) beginsum <= 29'd0 ;valid_r <= 1'b0 ;endelse if (cnt_acc_r == 5'd7) begin //在第8个累加周期输出滤波值sum <= sum + mout;valid_r <= 1'b1 ;endelse if (en_mult && cnt_acc_r == 0) begin //初始化sum <= mout ;valid_r <= 1'b0 ;endelse if (cnt_acc_r != 0) begin //acculating between cyclessum <= sum + mout ;valid_r <= 1'b0 ;endend//时钟锁存有效的输出数据,为了让输出信号不是那么频繁的变化reg [28:0] yout_r ;always @(posedge clk or negedge rstn) beginif (!rstn) beginyout_r <= 'b0 ;endelse if (valid_r) beginyout_r <= sum ;endendassign yout = yout_r ;//(5) 输出数据有效延迟,即滤波数据丢掉前15个滤波值reg [4:0] cnt_valid ;always @(posedge clk or negedge rstn) beginif (!rstn) begincnt_valid <= 'b0 ;endelse if (valid_r && cnt_valid != 5'd16) begincnt_valid <= cnt_valid + 1'b1 ;endendassign valid = (cnt_valid == 5'd16) & valid_r ;endmodule

testbench

testbench 编写如下,主要功能就是不间断连续的输入 250KHz 与 7.5MHz 的正弦波混合信号数据。输入的混合信号数据也可由 matlab 生成,具体见附录。

其中,工作频率为 400MHz,但输入数据和输入数据有效信号应当都保持 50MHz 的频率输入。

module test ;//inputreg clk ;reg rst_n ;reg en ;reg [11:0] xin ;//outputwire [28:0] yout ;wire valid ;parameter SIMU_CYCLE = 64'd1000 ;parameter SIN_DATA_NUM = 200 ;//=====================================

// 8*50MHz clk generatinglocalparam TCLK_HALF = (10_000 >>3);initial beginclk = 1'b0 ;forever begin# TCLK_HALF clk = ~clk ;endend//============================

// reset and finishinitial beginrst_n = 1'b0 ;# 30 rst_n = 1'b1 ;# (TCLK_HALF * 2 * 8 * SIMU_CYCLE) ;$finish ;end//=======================================

// read cos data into registerreg [11:0] stimulus [0: SIN_DATA_NUM-1] ;integer i ;initial begin$readmemh("../tb/cosx0p25m7p5m12bit.txt", stimulus) ;en = 0 ;i = 0 ;xin = 0 ;# 200 ;forever beginrepeat(7) @(negedge clk) ; //空置7个周期,第8个周期给数据en = 1 ;xin = stimulus[i] ;@(negedge clk) ;en = 0 ; //输入数据有效信号只持续一个周期即可if (i == SIN_DATA_NUM-1) i = 0 ;else i = i + 1 ;end end fir_serial_low u_fir_serial (.clk (clk),.rstn (rst_n),.en (en),.xin (xin),.valid (valid),.yout (yout));endmodule

仿真结果

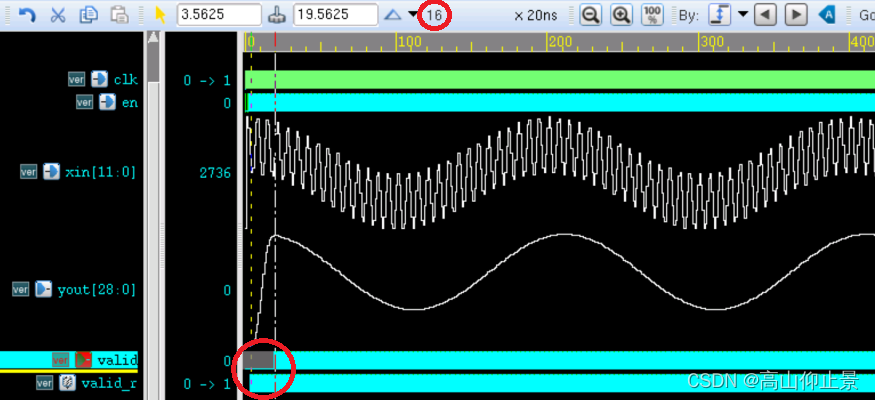

由下图仿真结果可知,经过 FIR 滤波器后的信号只有一种低频率信号(250KHz),高频信号(7.5MHz)被滤除了。为了波形更加的美观,取 16 个之后的滤波数据作为有效输出。

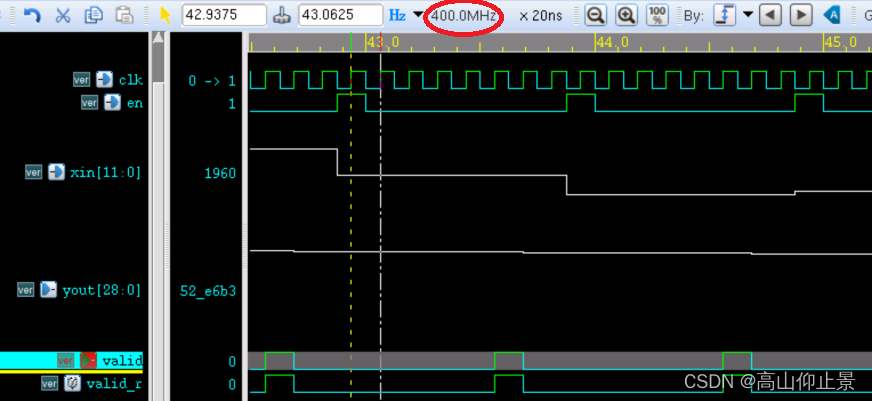

波形局部放大后如下图所示,此时输入数据有效信号 en 与输出数据有效信号 valid 是周期(50MHz)相同的脉冲信号,不是持续有效的。但工作时钟为 400MHz,所以输出也会呈现为 50MHz 采样频率下的 250KHz 频率的正弦波信号。

附录:matlab 使用(与《并行 FIR 滤波器设计》一致)

生成 FIR 滤波器系数

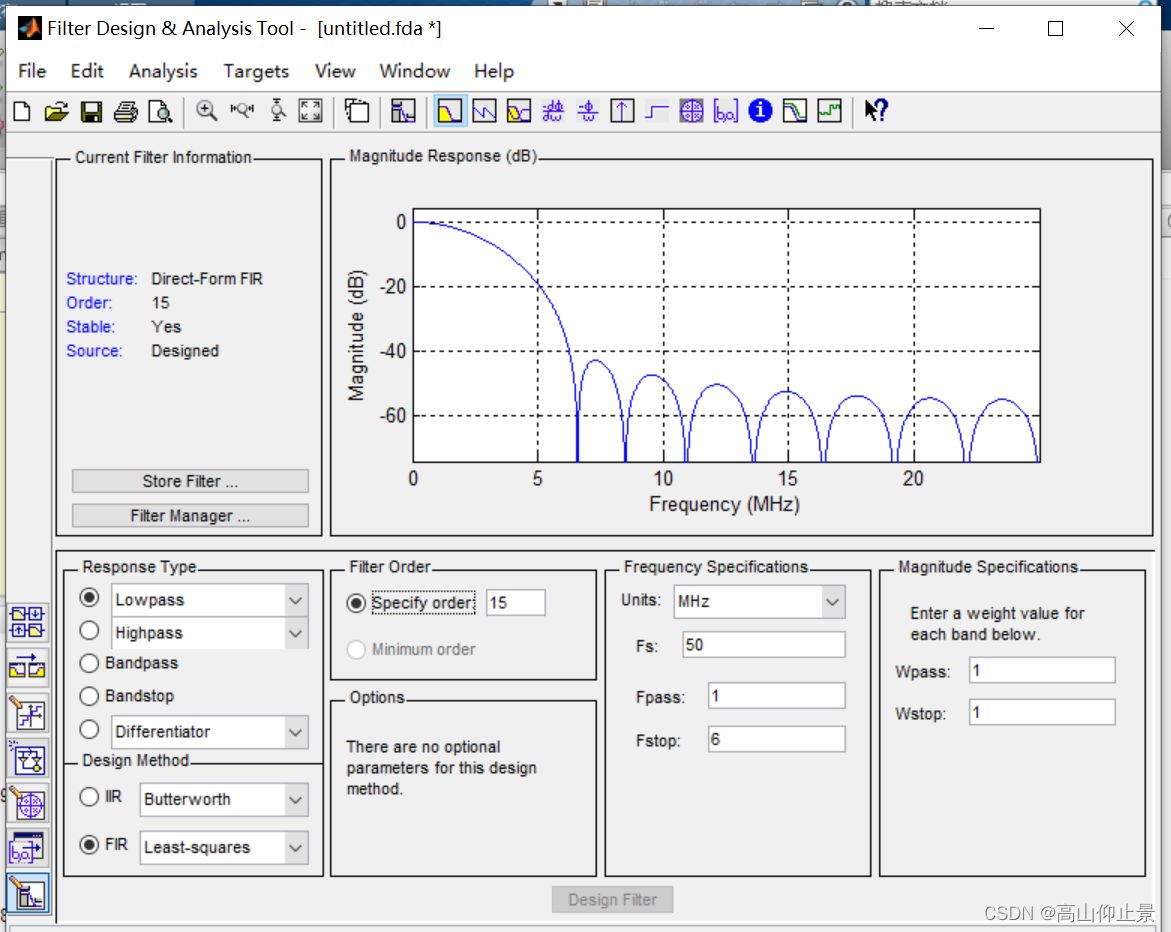

打开 matlab,在命令窗口输入命令: fdatool。

然后会打开如下窗口,按照 FIR 滤波器参数进行设置,如下所示。

这里选择的 FIR 实现方法是最小二乘法(Least-squares),不同的实现方式滤波效果也不同。

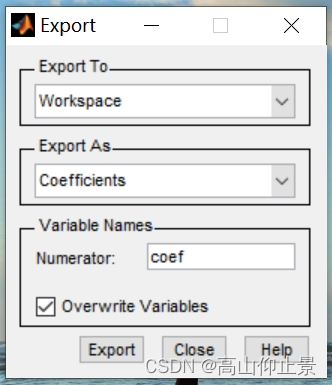

点击 File -> Export

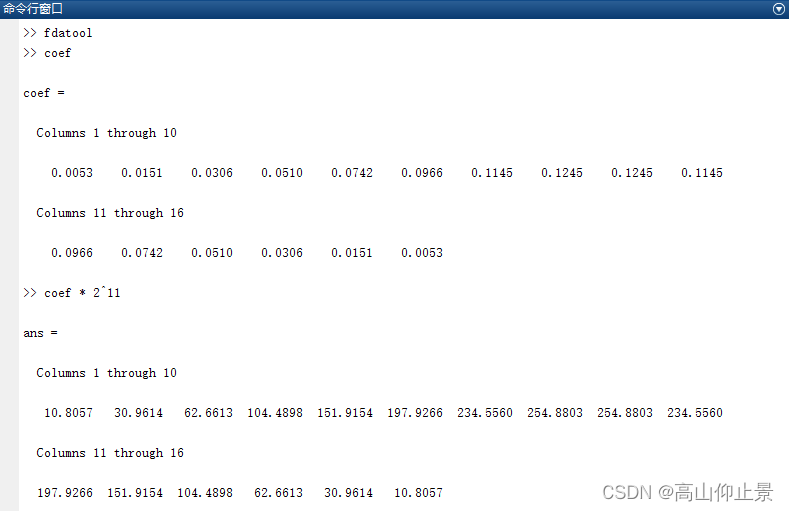

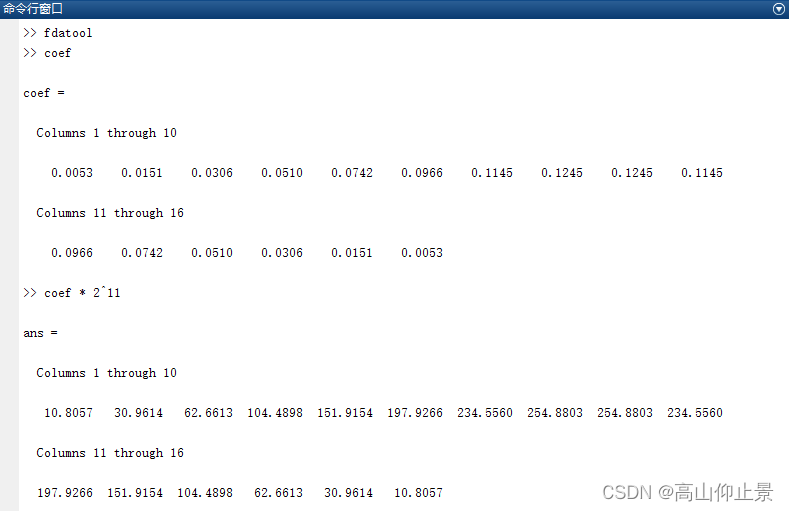

将滤波器参数输出,存到变量 coef 中,如下图所示。

此时 coef 变量应该是浮点型数据。对其进行一定倍数的相乘扩大,然后取其近似的定点型数据作为设计中的 FIR 滤波器参数。这里取扩大倍数为 2048,结果如下所示。

生成输入的混合信号

利用 matlab 生成混合的输入信号参考代码如下。

信号为无符号定点型数据,位宽宽度为 12bit,存于文件 cosx0p25m7p5m12bit.txt 。

clear all;close all;clc;

%=======================================================

% generating a cos wave data with txt hex format

%=======================================================fc = 0.25e6 ; % 中心频率

fn = 7.5e6 ; % 杂波频率

Fs = 50e6 ; % 采样频率

T = 1/fc ; % 信号周期

Num = Fs * T ; % 周期内信号采样点数

t = (0:Num-1)/Fs ; % 离散时间

cosx = cos(2*pi*fc*t) ; % 中心频率正弦信号

cosn = cos(2*pi*fn*t) ; % 杂波信号

cosy = mapminmax(cosx + cosn) ; %幅值扩展到(-1,1) 之间

cosy_dig = floor((2^11-1) * cosy + 2^11) ; %幅值扩展到 0~4095

fid = fopen('cosx0p25m7p5m12bit.txt', 'wt') ; %写数据文件

fprintf(fid, '%x\n', cosy_dig) ;

fclose(fid) ;%时域波形

figure(1);

subplot(121);plot(t,cosx);hold on ;

plot(t,cosn) ;

subplot(122);plot(t,cosy_dig) ;%频域波形

fft_cosy = fftshift(fft(cosy, Num)) ;

f_axis = (-Num/2 : Num/2 - 1) * (Fs/Num) ;

figure(5) ;

plot(f_axis, abs(fft_cosy)) ;

相关文章:

【Verilog 教程】7.3 Verilog 串行 FIR 滤波器设计

串行 FIR 滤波器设计 设计说明 设计参数不变,与并行 FIR 滤波器参数一致。即,输入频率为 7.5 MHz 和 250 KHz 的正弦波混合信号,经过 FIR 滤波器后,高频信号 7.5MHz 被滤除,只保留 250KMHz 的信号。 输入频率&#x…...

用golang实现一个基于interface的多态示例,展示其使用场景和优劣性。

以下是一个简单的基于interface的多态示例,该示例展示了如何通过使用interface来实现多个不同类型的结构体的共同行为。具体示例如下: package mainimport "fmt"type Animal interface {Speak() string }type Dog struct {Name string }func …...

ArcGIS for Android 禁止地图旋转

ArcGIS for Android 禁止地图旋转 话不多说,直接上代码!!! public class LoadMap extends AppCompatActivity {// 地图private MapView mapView;private ArcGISMap map;Overrideprotected void onCreate(Bundle savedInstanceSta…...

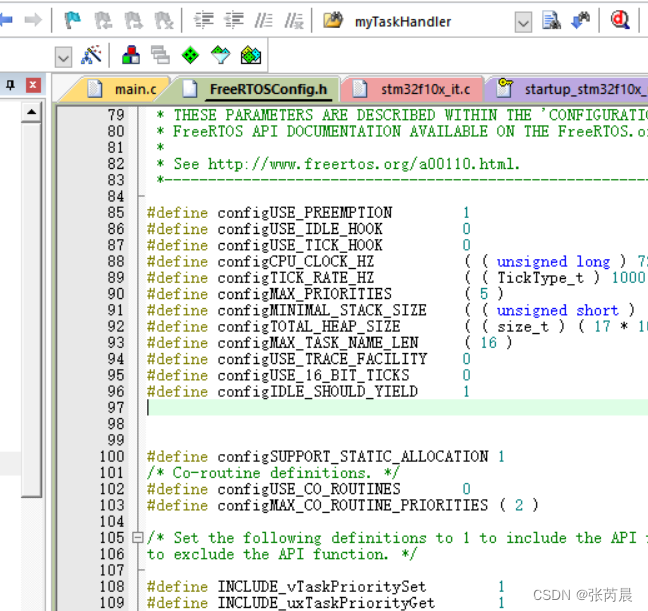

freertos静态创建任务

在开始前先有个小插曲,我的keil的自动补全代码功能使用不了,经过查找是因为之前装51把有的文件覆盖了,照这篇博客就可以解决。 然后之前那份代码我们是动态创建任务,先来说一下动态创建任务和静态创建任务的区别: Fre…...

VBA根据Excel内容快速创建PPT

示例需求:根据Excel中选中的单元格内容(3列)如下图所示,在已打卡的PowerPoint文件中创建页面。 新增PPT Slide页面使用第二个模板页面,其中包含两个文本占位符,和一个图片占位符。将Excel选中区域中前两列写…...

服务器操作系统有哪些

服务器操作系统有哪些 电脑想要运行就离不开操作系统,而服务器想要正常运行同样也离不开操作系统,那你知道服务器系统有哪些?服务器系统与电脑系统有什么区别?这些问题就由壹基比小鑫在下文中来告诉大家。 服务器系统有哪些&…...

泄漏检测与修复(LDAR)过程管控平台(销售出租)VOCs便携式总烃分析仪(销售出租)

LDAR是Leak Detection and Repair(泄漏检测与修复)的缩写,也是国际上较先进的化工废气检测技术。LDAR主要通过检测化工企业原料输送管道、泵、阀门、法兰等易产生易产生挥发性有机物(简称VOCs)泄漏的部位,并…...

VueX 模块化和namespace

当我们的项目很大的时候,VueX中的代码会越来越多,会有处理数据的,处理人员列表的,处理订单的... 如果我们将这些东西都写在一个state、actions和mutations中的话,就非常不方便后期的维护。 所以我们引入了VueX的模块…...

7-4 修理牧场 分数 15

#include<iostream> #include<queue> using namespace std; #define maxn 10005int main() {int n 0, data 0;cin >> n;//建小堆: //上调建堆中用greater: 父大子小 父子交换 小的上去 大的下去 priority_queue<int, vector<int>, greater<int…...

自定义element-ui plus 函数式调用,在API,js中直接使用全局组件

npm方式: npm install -D unplugin-vue-components unplugin-auto-import yarn 方式 : yarn add unplugin-vue-components; yarn add unplugin-auto-import; 使用官方的这个: vite.config.js中配置 plugins: [vue(),AutoImport({resolvers: [ElementPlusResolve…...

[LeetCode]-876.链表的中间结点-206.反转链表-21.合并两个有序链表-203.移除链表元素

目录 876.链表的中间结点 题目 思路 代码 206.反转链表 题目 思路 代码 21.合并两个有序链表 题目 思路 代码 203.移除链表元素 题目 思路 代码 876.链表的中间结点 876. 链表的中间结点 - 力扣(LeetCode)https://leetcode.cn/problems/mi…...

通过git多人协调开发

多人协调开发过程中的问题解决。 1.新建远程的仓库分支; 2.拉取线上代码,并在VScode中打开; 3 拉完之后,打开VScode之后的左下角显示的就是当前分支的名称,点击之后即可随意切换; 4 创建本地分支࿰…...

)

CentOS 7 通过 yum 安装 MariaDB(Mysql)

这一版取消了修改配置的操作,改成每次创建数据库时手动指定字符集编码;这一版取消了修改密码的操作,保留 MariaDB 使用无密码的情况,即密码是 ""。 安装步骤: 以下操作都以 root 用户进行操作 以下操作都以 …...

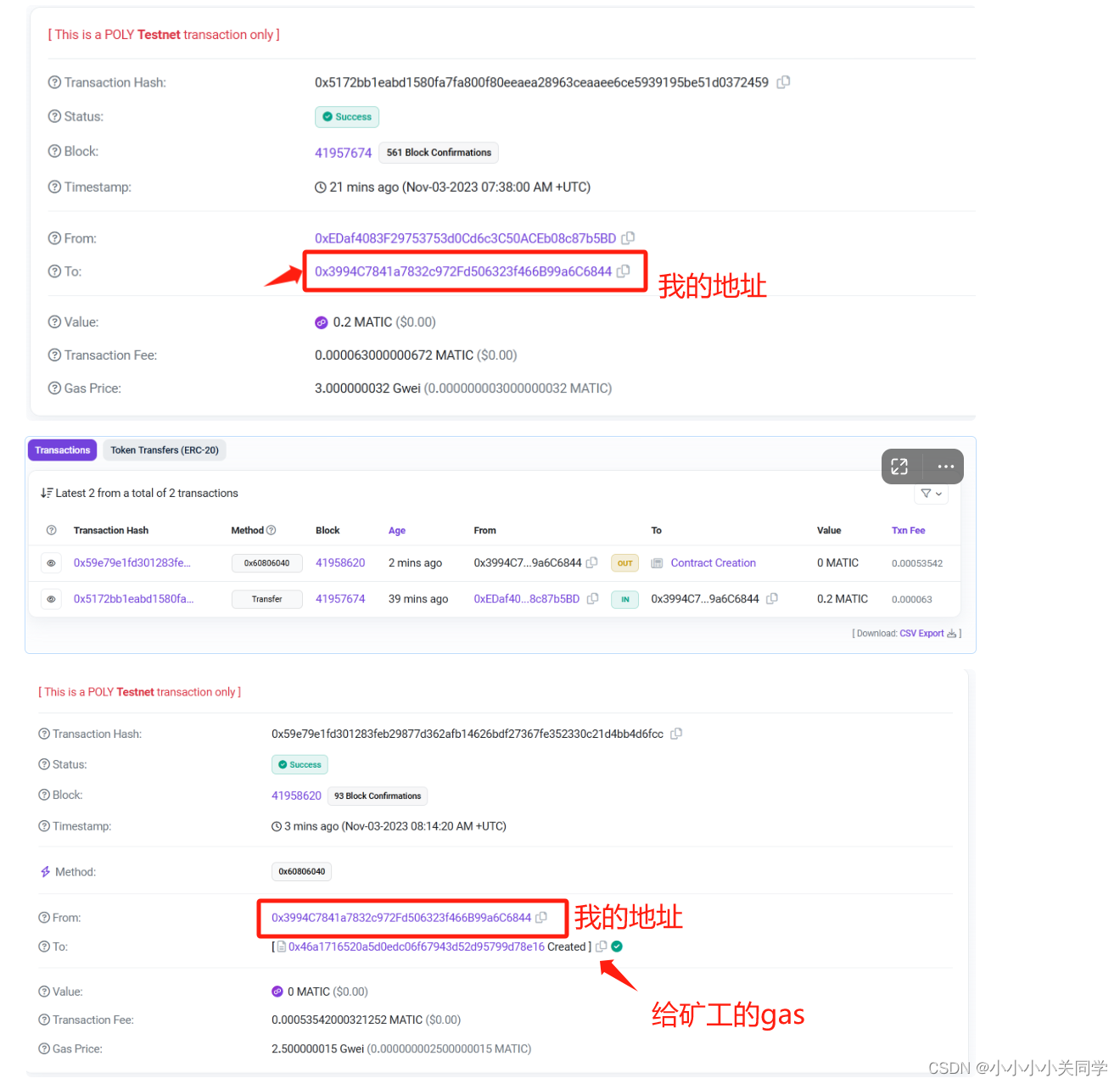

【Solidity】Remix在线环境及钱包申请

好久没有学习区块链方面的知识了,目前通过自学大致掌握了Fabric联盟链的搭建,链码编写、部署,api调用,可以独立开发出一些基于fabric的应用,感觉开发出去中心化的应用还是很有意思的,因为他与之前开发的ssm…...

ARFoundation系列讲解 - 92 涂鸦效果

--- 视频来源于网络,如有侵权必删 --- 案例中使用的软件版本 Unity2023.1.17.f1c1ARFoundtaion 5.1.0Apple ARKit XR Plugin 5.1.0 Google ARCore XR Plugin 5.1.0技术分析 我们可以实时检测用户手指触摸的屏幕位置,从触摸位置投射一条射线(Raycast),再射线命中的目标位置…...

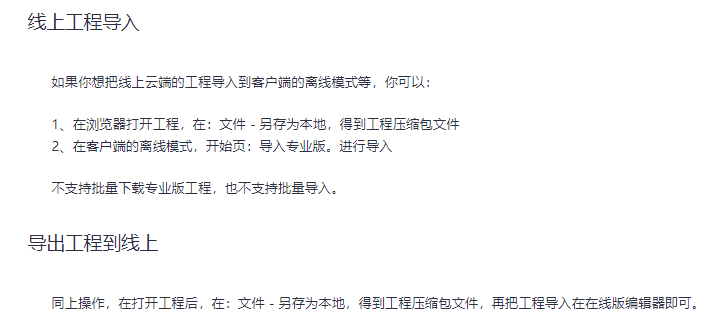

立创eda专业版学习笔记(8)(运行模式)

以前没注意过这个问题,我有2台电脑,都能登录eda专业版,但是一台是全在线模式,另外一台是半离线模式,虽然是同一个账号,但是打开里面的工程会发现,两边的工程完全不同,因为一台的工程…...

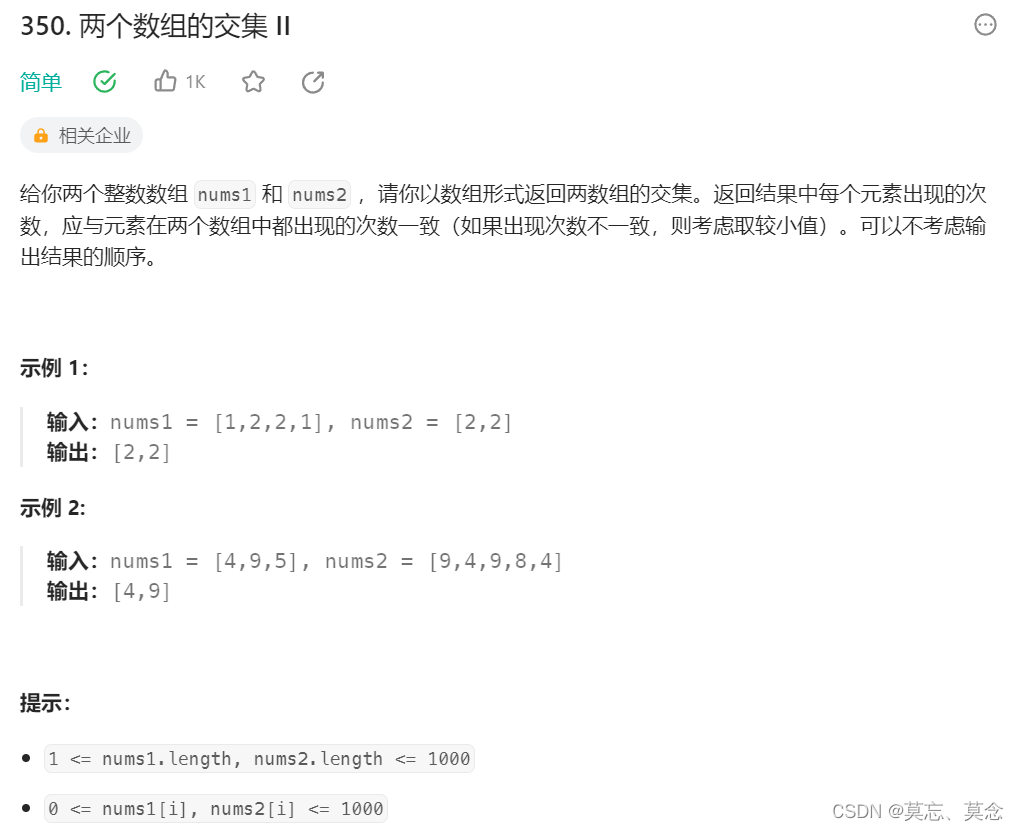

349.两个数组的交集+350.两个数组的交集II(set/multiset)

目录 一、349.两个数组的交集 二、350.两个数组的交集II 一、349.两个数组的交集 349. 两个数组的交集 - 力扣(LeetCode) class Solution { public:vector<int> intersection(vector<int>& nums1, vector<int>& nums2) {//…...

)

数据结构与算法之排序: 桶排序 (Javascript版)

排序 排序:把某个乱序的数组变成升序或降序的数组 (这里用数组来做举例) 桶排序 根据元素的取值范围,创建多个桶, 每个桶代表一个区间范围 创建桶的数量和范围需要尽可能保证元素能够被均匀分布 接下来将元素放进对应的桶中,分别对每个桶中…...

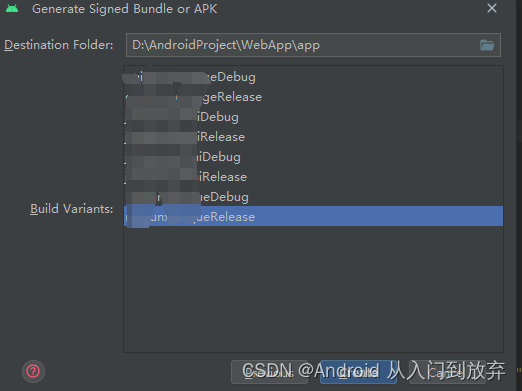

Android studio新版本多渠道打包配置

最近公司套壳app比较多 功能也都一样只有地址,和app名字还有icon不一样 签名文件也是一样的,所以就研究了多渠道打包 配置如下: 在app下build.gradle配置 因为最新版as中禁用了BuildConfig 所以我们需要手动配置一下 android { //TODO 其他省略buildFe…...

PTA:后序和中序构造二叉树

后序和中序构造二叉树 题目输入格式输出格式输入样例(及其对应的二叉树) 代码 题目 本题目要求用后序序列和中序序列构造一棵二叉树(树中结点个数不超过10个),并输出其先序序列。 输入格式 在第一行中输入元素个数…...

Easypoi导出Excel时,如何优雅地处理‘未知’或‘空值’?一个replace动态替换的实战技巧

Easypoi动态替换Excel导出中的未知值与空值:实战技巧与最佳实践 在数据导出场景中,我们经常遇到数据库枚举值与Excel展示不匹配的问题。比如性别字段,除了标准的"男"、"女"外,还可能存在空值或超出预设范围的…...

FireRedASR Pro在微信小程序开发中的应用:实时语音输入与转写

FireRedASR Pro在微信小程序开发中的应用:实时语音输入与转写 不知道你有没有这样的经历:用手机打字回复长消息时,手指按得发酸;或者在线听课时,想快速记下老师的重点,手速却跟不上语速。在移动优先的今天…...

颠覆中文字体困境:思源宋体CN 7字重开源方案深度解析

颠覆中文字体困境:思源宋体CN 7字重开源方案深度解析 【免费下载链接】source-han-serif-ttf Source Han Serif TTF 项目地址: https://gitcode.com/gh_mirrors/so/source-han-serif-ttf 价值主张:破解中文字体的"三重枷锁" 在数字设计…...

无人值守智能图书借阅系统 Java 后端开发实战

在无人值守智能图书借阅系统的Java后端开发实战中,需围绕系统架构设计、核心功能实现、关键技术选型及部署优化等核心环节展开,以下为具体开发方案:一、系统架构设计分层架构体系:采用经典的四层架构设计,包括表现层、…...

foobar2000皮肤焕新:用foobox-cn打造沉浸式音乐体验

foobar2000皮肤焕新:用foobox-cn打造沉浸式音乐体验 【免费下载链接】foobox-cn DUI 配置 for foobar2000 项目地址: https://gitcode.com/GitHub_Trending/fo/foobox-cn 作为音乐爱好者,你是否也曾因foobar2000默认界面的单调乏味而却步…...

实战指南:在CentOS 8上部署与配置BIND DNS权威服务器

1. 为什么要在CentOS 8上搭建DNS服务器? 想象一下这样的场景:公司内部有几十台服务器,每次新同事入职都要发一份IP地址对照表;开发团队每次联调测试都要反复确认服务地址;运维人员排查问题时要在记事本里翻找各种192.1…...

3步完成系统深度净化:Win11Debloat工具让旧电脑性能提升60%

3步完成系统深度净化:Win11Debloat工具让旧电脑性能提升60% 【免费下载链接】Win11Debloat 一个简单的PowerShell脚本,用于从Windows中移除预装的无用软件,禁用遥测,从Windows搜索中移除Bing,以及执行各种其他更改以简…...

GSE-Advanced-Macro-Compiler:重新定义魔兽世界技能自动化的开发实践

GSE-Advanced-Macro-Compiler:重新定义魔兽世界技能自动化的开发实践 【免费下载链接】GSE-Advanced-Macro-Compiler GSE is an alternative advanced macro editor and engine for World of Warcraft. It uses Travis for UnitTests, Coveralls to report on test …...

告别90%重复劳动:psd2fgui工具实战指南

告别90%重复劳动:psd2fgui工具实战指南 【免费下载链接】psd2fgui A tool for converting psd file to fairygui package. 项目地址: https://gitcode.com/gh_mirrors/ps/psd2fgui 价值定位:UI开发中哪些环节正在吞噬你的效率? 作为游…...

组织结构,让我逐一解释每个层级及其相互关系)

SAP中的核算架构体系。这是一个复杂的会计科目表(Chart of Accounts)组织结构,让我逐一解释每个层级及其相互关系

SAP中的核算架构体系。这是一个复杂的会计科目表(Chart of Accounts)组织结构,让我逐一解释每个层级及其相互关系。SAP核算架构全景图┌─────────────────────────────────────────────────…...